### Computer Architecture

Lecture 3a: Memory Trends, Challenges, Opportunities

Prof. Onur Mutlu

ETH Zürich

Fall 2019

26 September 2019

### Four Key Directions

Fundamentally Secure/Reliable/Safe Architectures

- Fundamentally Energy-Efficient Architectures

- Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency Architectures

Architectures for Genomics, Medicine, Health

# A Motivating Detour: Genome Sequence Analysis

### Our Dream (circa 2007)

- An embedded device that can perform comprehensive genome analysis in real time (within a minute)

- Which of these DNAs does this DNA segment match with?

- What is the likely genetic disposition of this patient to this drug?

- **.**..

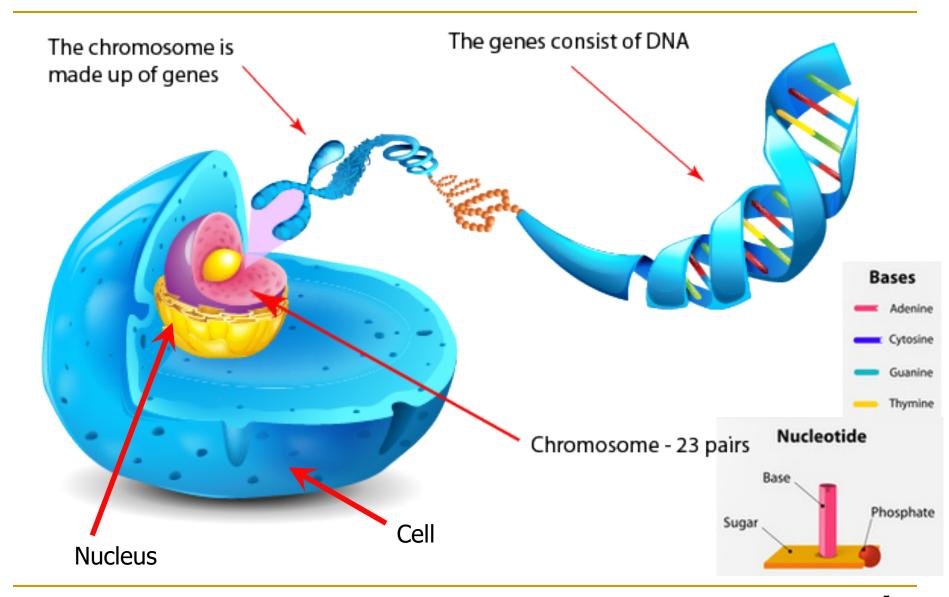

### What Is a Genome Made Of?

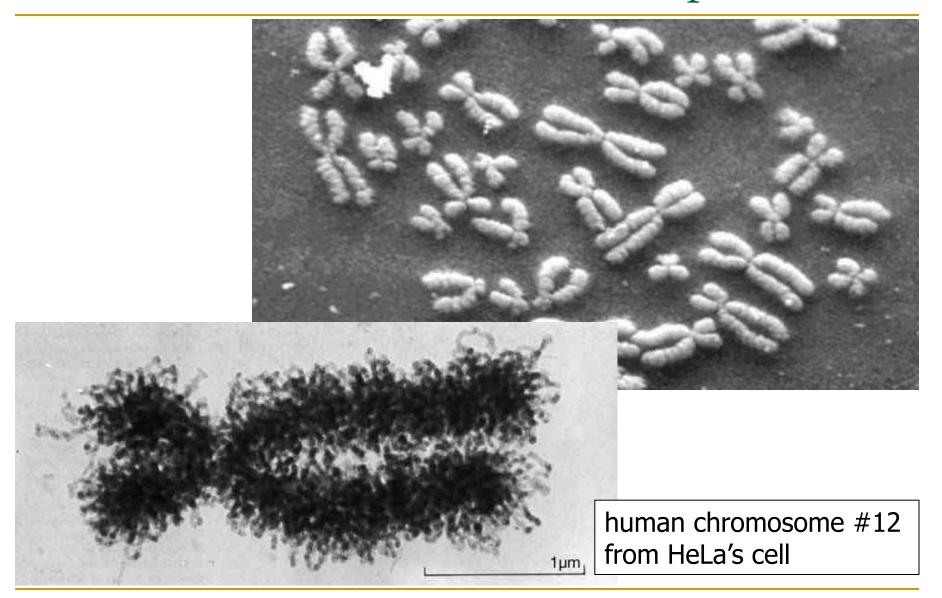

### DNA Under Electron Microscope

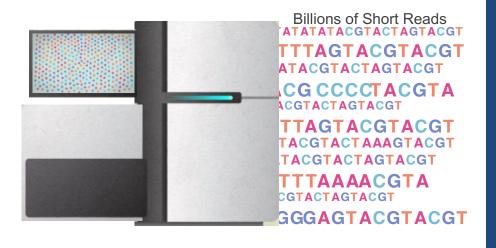

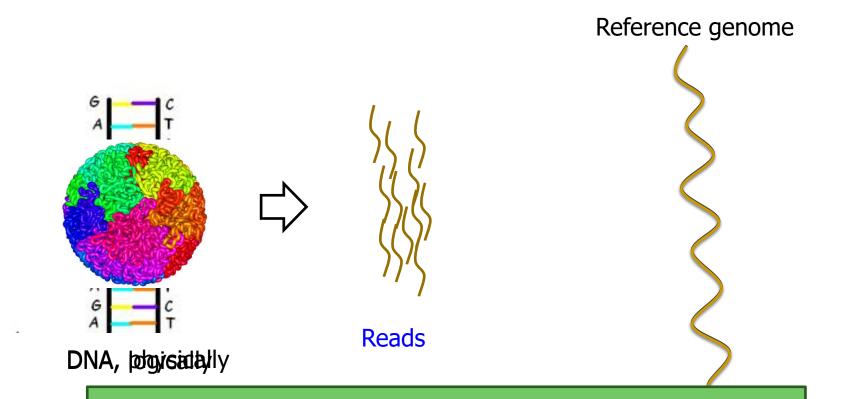

### DNA Sequencing

### Goal:

Find the complete sequence of A, C, G, T's in DNA.

### Challenge:

- There is no machine that takes long DNA as an input, and gives the complete sequence as output

- All sequencing machines chop DNA into pieces and identify relatively small pieces (but not how they fit together)

### Untangling Yarn Balls & DNA Sequencing

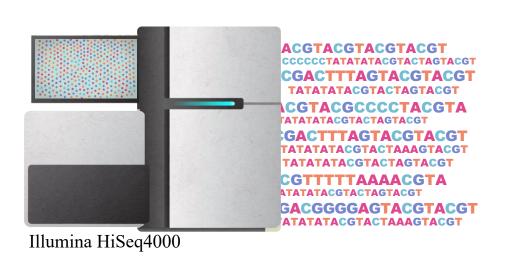

### Genome Sequencers

Roche/454

Illumina HiSeq2000

Pacific Biosciences RS

**Ion Torrent Proton**

Illumina MiSeq

Complete Genomics

Oxford Nanopore MinION

Illumina NovaSeq 6000

Oxford Nanopore GridION

... and more! All produce data with different properties.

Ion Torrent PGM

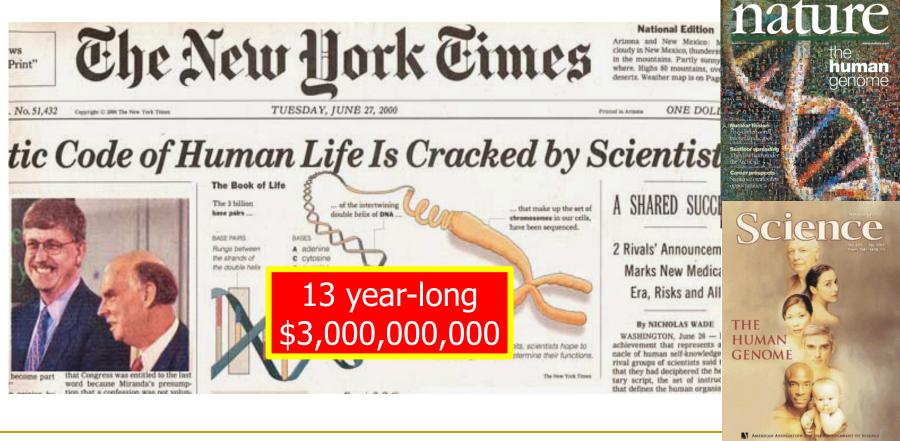

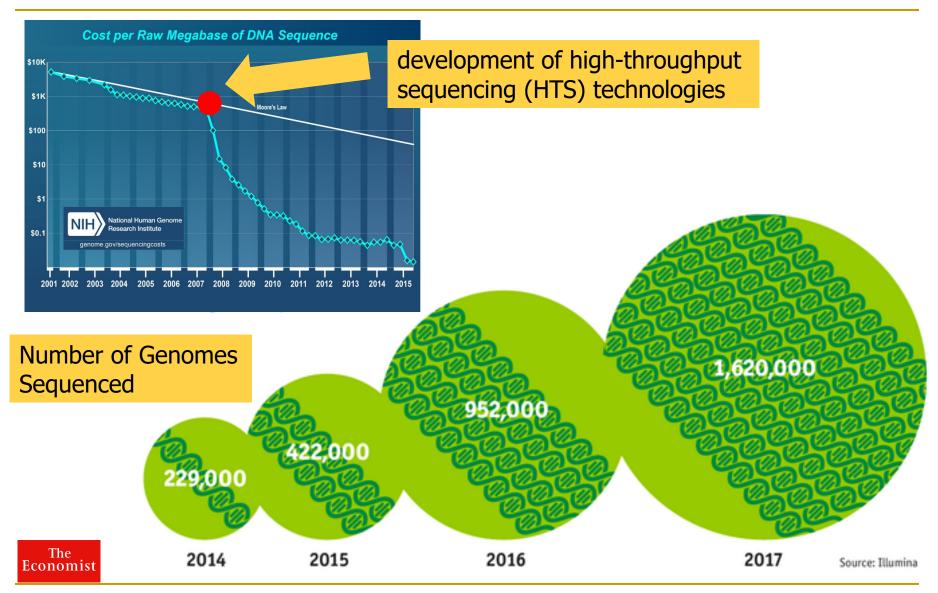

### The Genomic Era

1990-2003: The Human Genome Project (HGP) provides a complete and accurate sequence of all **DNA base pairs** that make up the human genome and finds 20,000 to 25,000 human genes.

### The Genomic Era (continued)

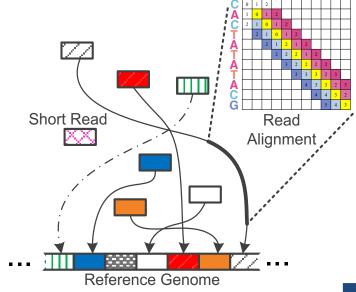

**Read Mapping**

### 1 Sequencing

**Genome Analysis**

reference: TTTATCGCTTCCATGACGCAG

read1: ATCGCATCC read2: TATCGCATC

read3: CATCCATGA

read4: CGCTTCCAT

read5: CCATGACGC

read6: TTCCATGAC

**Variant Calling**

### Multiple sequence alignment

```

PHDHt.m.

MMMMMMMMMMMMMMM-

16082665

T acid

----MASDRKSEGFOSGAGLIRYFEEEEIKGPALDPKLVVYMGIAVAIIVEIAKIFWPF

(55)

----masdkksegFOSGAGLIRYFERERIKGPALDPKLVVYIGIAVAIMVELAKIFWPP-

13541150

T volc

(55)

-MTSMAKDNONENFQSGAGLIRYFNDEDIKGPAIDPKLIIYIGIAMGVIVELAKVFWP

RFAC01077

F acid

(58)

----mssgonsggLMSSAGLVRYFDSEDSNALGIDPRSVVAVGAFFGLVVLLAOFFA

15791336

(53)

H NRC1

MAKAPKGKAKTPPLMSSAGIMRYFER-EKTOINVSPKTILAAGIVTGVLIIILNAYYGLWP-

RAG22196

A fula

(68)

-----MAKEKTTLPPTGAGLMRFFDE-DTRAIKITPKGAVALTLILIIFEIILHVVGPRIFG

RP001000

(56)

P abys

---makekttlpptgAg<mark>lmrff</mark>dE-<mark>dtraikitpkgAialvliliifeillhvv</mark>gpr<mark>i</mark>fg

RPH01741

(56)

P hori

--makkdkktlppsgag<mark>lvryf</mark>e<mark>r-d</mark>tkg<mark>fkl</mark>tpe<mark>qvvvmsiilavfclvl</mark>r<mark>fs</mark>g

AE000914

M ther

(52)

----MSKRESTGLATSAGLIRYMDE-TFSK<mark>IRV</mark>KPEHVIGVTVAFVIIEAILTYGRF

RMJ09857

M jann

(53)

-MPSSKKKKETUPLASMAGLIRYYED-PNEKIMISPKLLIIISIIMVAGVIVASILIP

(58)

15920503

S toko

AE006662

S solf

-MPSSKKKKETVPVMSMAGLIRYYEE-PNEKVMISPKIVIGASLALTIIVIVITKLF

(55)

--MARRKYEGINPFVAAGLIKFSEEGELEKIKLTPRAAVVISLAIIGLLIAINLLLPPL--

RPK02491

(58)

P aero

RAP00437

-MSVRRRERRATPVTAAGLLSFYEE-YEGKIKISPTIVVGAAILVSAVVAAA: IFLPAVP-

(59)

A pern

-----SAGTGGMWRFYTE-DSPGLWVGPVPVLVMSLLFIASVFMLHIWGKYTRS

5803165

(96)

H sapi

13324684

M musc

-SAGTGGMWRFYTR-DSPGLWVGPVPVLVMSLLFIAAVFMLUIWGKYTRS

(96)

-----GAGTGGMWRFYTD-DSPGINVGPVPVLVMSLLFIASVFMLHIWGKYNRS

6002114

D mela

(100)

----ggnngg<mark>lwrfy</mark>t<mark>e-d</mark>stg<mark>lwigevpvlvmslvfiasvfvlhiwgkft</mark>rs

14574310

C elea

(81)

----GGSSSTMLKLYTD-ESQGLK

Y lipo

10697176

DPVVVMVLSLGFIFSVVALEILAKVSTK

(91)

-----GGSSSS<mark>ILKLYTD-D</mark>ANGFRVDSLVVLFLSVGFIFSVIALHLLTKFTHI

6320857

(88)

6320932

S cere

-TNSNNS<mark>ILKIYSD-D</mark>ATG<mark>LRV</mark>DPLVVLFLAVGFIFSVVAL<mark>H</mark>VISK<mark>VA</mark>GK

(82)

```

Example Question: If I give you a bunch of sequences, tell me where they are the same and where they are different.

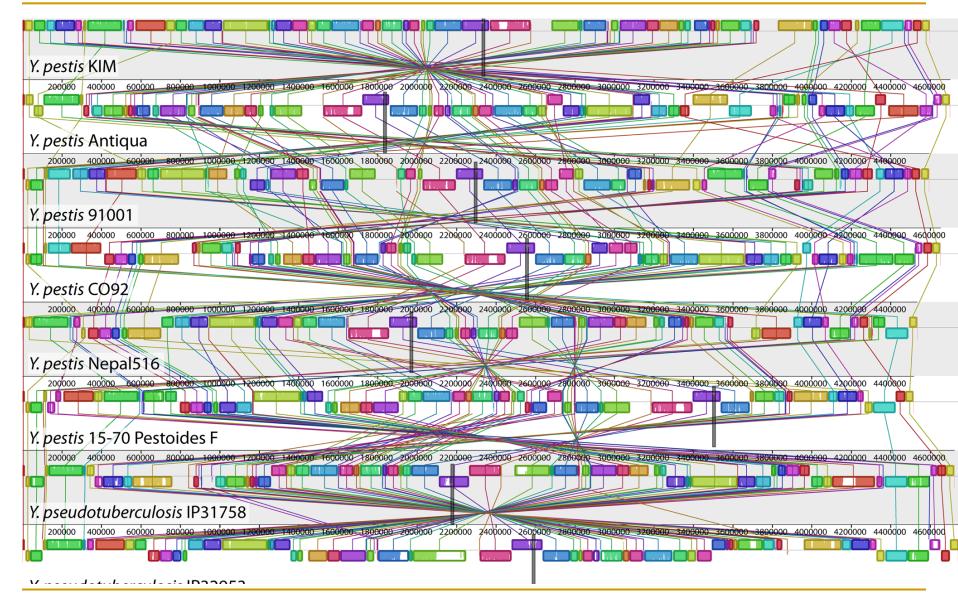

### Genome Sequence Alignment: Example

### The Genetic Similarity Between Species

Human ~ Chimpanzee 96%

Human ~ Cat 90%

Human ~ Cow 80%

Human ~ Banana 50-60%

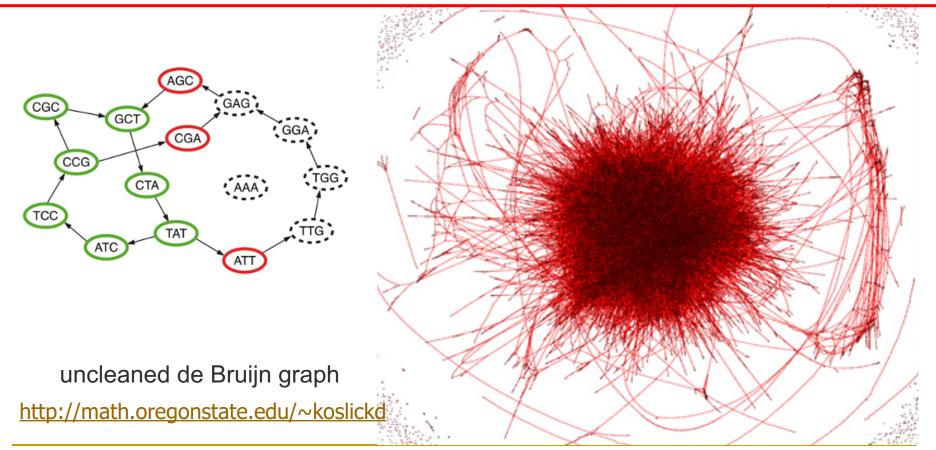

### Metagenomics, genome assembly, de novo sequencing

Question 2: Given a bunch of short sequences, Can you identify the approximate species cluster for genomically unknown organisms?

**Read Mapping**

### **Sequencing**

### Bottlenecked in Mapping!!

# Need to construct the entire genome from many reads

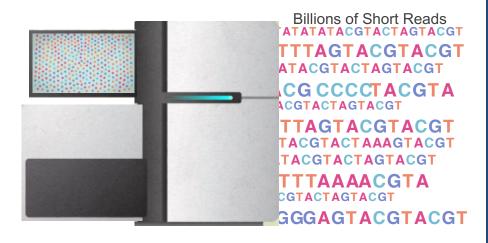

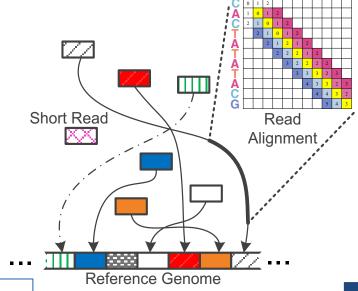

### Read Mapping

Map many short DNA fragments (reads) to a known reference genome with some differences allowed

Mapping short reads to reference genome is challenging (billions of 50-300 base pair reads)

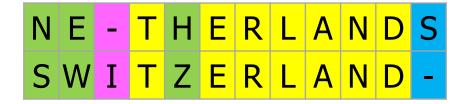

### Read Alignment/Verification

Edit distance is defined as the minimum number of edits (i.e. insertions, deletions, or substitutions) needed to make the read exactly match the reference segment.

#### NETHERLANDS x SWITZERLAND

match

deletion

insertion

mismatch

### Challenges in Read Mapping

- Need to find many mappings of each read

- How can we find all mappings efficiently?

- Need to tolerate small variances/errors in each read

- Each individual is different: Subject's DNA may slightly differ from the reference (Mismatches, insertions, deletions)

- How can we efficiently map each read with up to e errors present?

- Need to map each read very fast (i.e., performance is important)

- □ Human DNA is 3.2 billion base pairs long → Millions to billions of reads (State-of-the-art mappers take weeks to map a human's DNA)

- How can we design a much higher performance read mapper?

### Our First Step: Comprehensive Mapping

- + Guaranteed to find all mappings → sensitive

- + Can tolerate up to e errors

### nature genetics

http://mrfast.sourceforge.net/

### Personalized copy number and segmental duplication maps using next-generation sequencing

Can Alkan<sup>1,2</sup>, Jeffrey M Kidd<sup>1</sup>, Tomas Marques-Bonet<sup>1,3</sup>, Gozde Aksay<sup>1</sup>, Francesca Antonacci<sup>1</sup>, Fereydoun Hormozdiari<sup>4</sup>, Jacob O Kitzman<sup>1</sup>, Carl Baker<sup>1</sup>, Maika Malig<sup>1</sup>, Onur Mutlu<sup>5</sup>, S Cenk Sahinalp<sup>4</sup>, Richard A Gibbs<sup>6</sup> & Evan E Eichler<sup>1,2</sup>

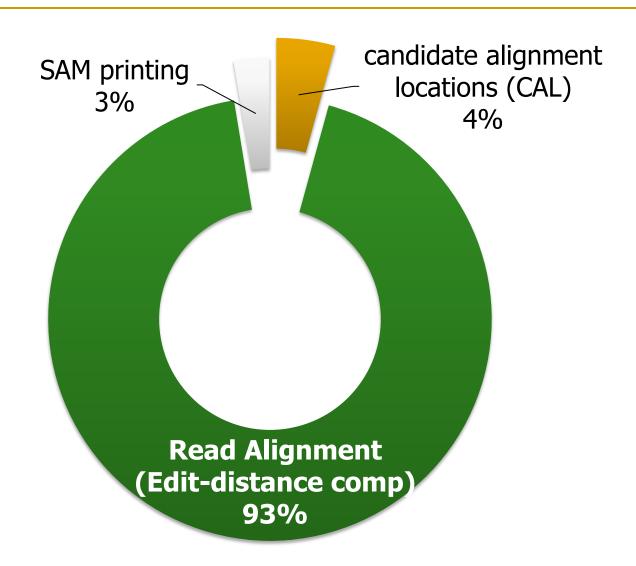

### Read Mapping Execution Time Breakdown

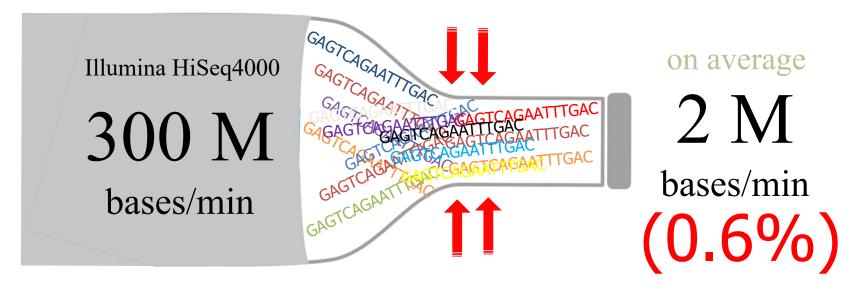

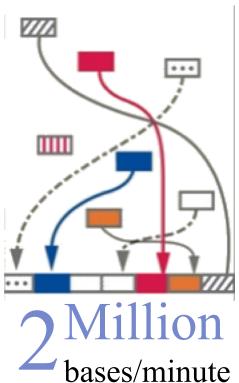

### The Read Mapping Bottleneck

300 Million bases/minute

### Filter fast before you align

Minimize costly "approximate string comparisons"

### Our First Filter: Pure Software Approach

- Download the source code and try for yourself

- Download link to FastHASH

Xin et al. BMC Genomics 2013, **14**(Suppl 1):S13 http://www.biomedcentral.com/1471-2164/14/S1/S13

#### **PROCEEDINGS**

**Open Access**

### Accelerating read mapping with FastHASH

Hongyi Xin<sup>1</sup>, Donghyuk Lee<sup>1</sup>, Farhad Hormozdiari<sup>2</sup>, Samihan Yedkar<sup>1</sup>, Onur Mutlu<sup>1\*</sup>, Can Alkan<sup>3\*</sup>

From The Eleventh Asia Pacific Bioinformatics Conference (APBC 2013) Vancouver, Canada. 21-24 January 2013

### Shifted Hamming Distance: SIMD Acceleration

https://github.com/CMU-SAFARI/Shifted-Hamming-Distance

Bioinformatics, 31(10), 2015, 1553-1560

doi: 10.1093/bioinformatics/btu856

Advance Access Publication Date: 10 January 2015

**Original Paper**

Sequence analysis

## Shifted Hamming distance: a fast and accurate SIMD-friendly filter to accelerate alignment verification in read mapping

Hongyi Xin<sup>1,\*</sup>, John Greth<sup>2</sup>, John Emmons<sup>2</sup>, Gennady Pekhimenko<sup>1</sup>, Carl Kingsford<sup>3</sup>, Can Alkan<sup>4,\*</sup> and Onur Mutlu<sup>2,\*</sup>

Xin+, "Shifted Hamming Distance: A Fast and Accurate SIMD-friendly Filter to Accelerate Alignment Verification in Read Mapping", Bioinformatics 2015.

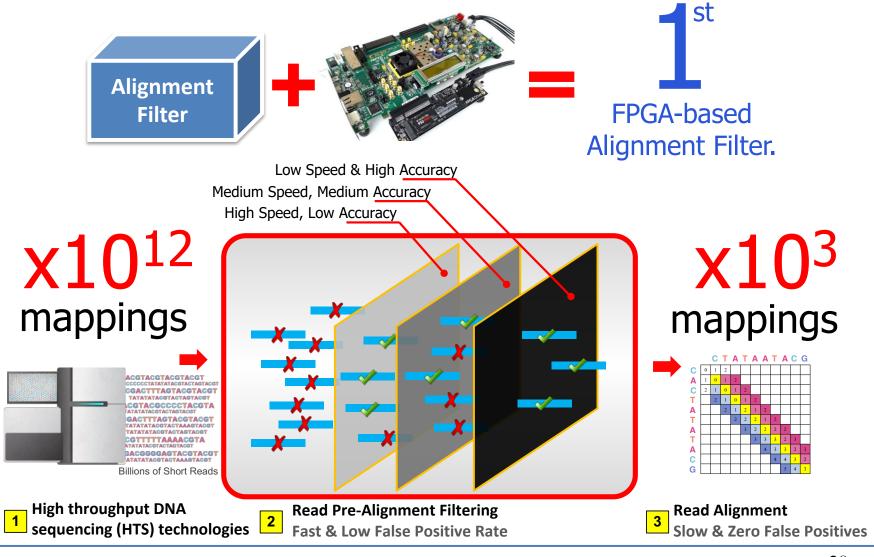

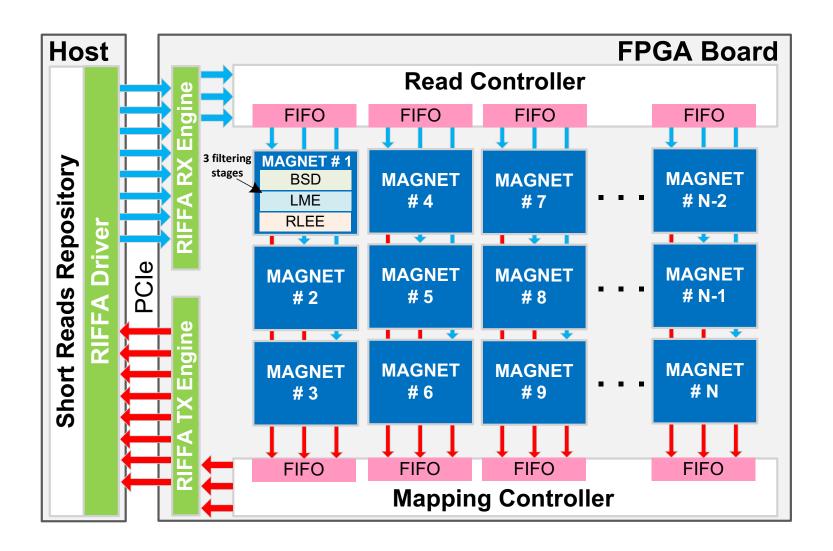

### GateKeeper: FPGA-Based Alignment Filtering

### GateKeeper: FPGA-Based Alignment Filtering

Mohammed Alser, Hasan Hassan, Hongyi Xin, Oguz Ergin, Onur Mutlu, and Can Alkan

"GateKeeper: A New Hardware Architecture for Accelerating Pre-Alignment in DNA Short Read Mapping" Bioinformatics, [published online, May 31], 2017.

Source Code

[Online link at Bioinformatics Journal]

### GateKeeper: a new hardware architecture for accelerating pre-alignment in DNA short read mapping

Mohammed Alser ™, Hasan Hassan, Hongyi Xin, Oğuz Ergin, Onur Mutlu ™, Can Alkan ™

Bioinformatics, Volume 33, Issue 21, 1 November 2017, Pages 3355–3363,

https://doi.org/10.1093/bioinformatics/btx342

Published: 31 May 2017 Article history ▼

### MAGNET Accelerator [Alser+, TIR 2017]

### Newest Work: Shouji [Alser+, Bioinformatics 2019]

Mohammed Alser, Hasan Hassan, Akash Kumar, Onur Mutlu, and Can Alkan, "Shouji: A Fast and Efficient Pre-Alignment Filter for Sequence Alignment" Bioinformatics, [published online, March 28], 2019.

Source Code

Online link at Bioinformatics Journal

Bioinformatics, 2019, 1–9 doi: 10.1093/bioinformatics/btz234 Advance Access Publication Date: 28 March 2019 Original Paper

#### Sequence alignment

### Shouji: a fast and efficient pre-alignment filter for sequence alignment

Mohammed Alser<sup>1,2,3,\*</sup>, Hasan Hassan<sup>1</sup>, Akash Kumar<sup>2</sup>, Onur Mutlu<sup>1,3,\*</sup> and Can Alkan<sup>3,\*</sup>

<sup>1</sup>Computer Science Department, ETH Zürich, Zürich 8092, Switzerland, <sup>2</sup>Chair for Processor Design, Center For Advancing Electronics Dresden, Institute of Computer Engineering, Technische Universität Dresden, 01062 Dresden, Germany and <sup>3</sup>Computer Engineering Department, Bilkent University, 06800 Ankara, Turkey

Associate Editor: Inanc Birol

SAFARI

<sup>\*</sup>To whom correspondence should be addressed.

### DNA Read Mapping & Filtering

- Problem: Heavily bottlenecked by Data Movement

- GateKeeper FPGA performance limited by DRAM bandwidth [Alser+, Bioinformatics 2017]

- Ditto for SHD on SIMD [Xin+, Bioinformatics 2015]

- Solution: Processing-in-memory can alleviate the bottleneck

- However, we need to design mapping & filtering algorithms to fit processing-in-memory

### In-Memory DNA Sequence Analysis

Jeremie S. Kim, Damla Senol Cali, Hongyi Xin, Donghyuk Lee, Saugata Ghose, Mohammed Alser, Hasan Hassan, Oguz Ergin, Can Alkan, and Onur Mutlu, "GRIM-Filter: Fast Seed Location Filtering in DNA Read Mapping Using Processing-in-Memory Technologies" <u>BMC Genomics</u>, 2018.

Proceedings of the <u>16th Asia Pacific Bioinformatics Conference</u> (**APBC**), Yokohama, Japan, January 2018. arxiv.org Version (pdf)

# GRIM-Filter: Fast seed location filtering in DNA read mapping using processing-in-memory technologies

Jeremie S. Kim<sup>1,6\*</sup>, Damla Senol Cali<sup>1</sup>, Hongyi Xin<sup>2</sup>, Donghyuk Lee<sup>3</sup>, Saugata Ghose<sup>1</sup>, Mohammed Alser<sup>4</sup>, Hasan Hassan<sup>6</sup>, Oguz Ergin<sup>5</sup>, Can Alkan<sup>4\*</sup> and Onur Mutlu<sup>6,1\*</sup>

From The Sixteenth Asia Pacific Bioinformatics Conference 2018 Yokohama, Japan. 15-17 January 2018

### Quick Note: Key Principles and Results

### Two key principles:

- Exploit the structure of the genome to minimize computation

- Morph and exploit the structure of the underlying hardware to maximize performance and efficiency

- Algorithm-architecture co-design for DNA read mapping

- Speeds up read mapping by ~300X (sometimes more)

- Improves accuracy of read mapping in the presence of errors

Xin et al., "Accelerating Read Mapping with FastHASH," BMC Genomics 2013.

Xin et al., "Shifted Hamming Distance: A Fast and Accurate SIMD-friendly Filter to Accelerate Alignment Verification in Read Mapping," Bioinformatics 2015.

Alser et al., "GateKeeper: A New Hardware Architecture for Accelerating Pre-Alignment in DNA Short Read Mapping," Bioinformatics 2017.

Kim et al., "Genome Read In-Memory (GRIM) Filter," BMC Genomics 2018.

### New Genome Sequencing Technologies

### Nanopore sequencing technology and tools for genome assembly: computational analysis of the current state, bottlenecks and future directions

Damla Senol Cali ™, Jeremie S Kim, Saugata Ghose, Can Alkan, Onur Mutlu

Briefings in Bioinformatics, bby017, https://doi.org/10.1093/bib/bby017

Published: 02 April 2018 Article history ▼

Oxford Nanopore MinION

Senol Cali+, "Nanopore Sequencing Technology and Tools for Genome Assembly: Computational Analysis of the Current State, Bottlenecks and Future Directions," Briefings in Bioinformatics, 2018.

[Preliminary arxiv.org version]

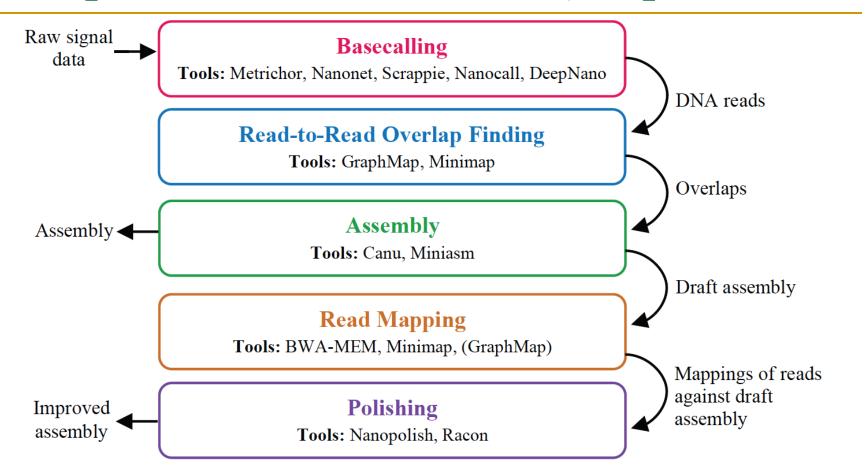

### Nanopore Genome Assembly Pipeline

Figure 1. The analyzed genome assembly pipeline using nanopore sequence data, with its five steps and the associated tools for each

#### Recall Our Dream

- An embedded device that can perform comprehensive genome analysis in real time (within a minute)

- Still a long ways to go

- Energy efficiency

- Performance (latency)

- Security

- Huge memory bottleneck

#### More on Genome Analysis: Another Talk

Onur Mutlu,

"Accelerating Genome Analysis: A Primer on an Ongoing Journey"

Keynote talk at 2nd Workshop on Accelerator Architecture in Computational Biology and Bioinformatics (AACBB), Washington, DC, USA, February 2019.

[Slides (pptx)(pdf)]

[Video]

#### Accelerating Genome Analysis

A Primer on an Ongoing Journey

Onur Mutlu

omutlu@gmail.com

https://people.inf.ethz.ch/omutlu

16 February 2019

AACBB Keynote Talk

SAFARI

Carnegie Mellon

#### Four Key Directions

Fundamentally Secure/Reliable/Safe Architectures

Fundamentally Energy-Efficient Architectures

Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency Architectures

Architectures for Genomics, Medicine, Health

### Memory & Storage

## Why Is Memory So Important? (Especially Today)

#### Importance of Main Memory

The Performance Perspective

The Energy Perspective

The Scaling/Reliability/Security Perspective

Trends/Challenges/Opportunities in Main Memory

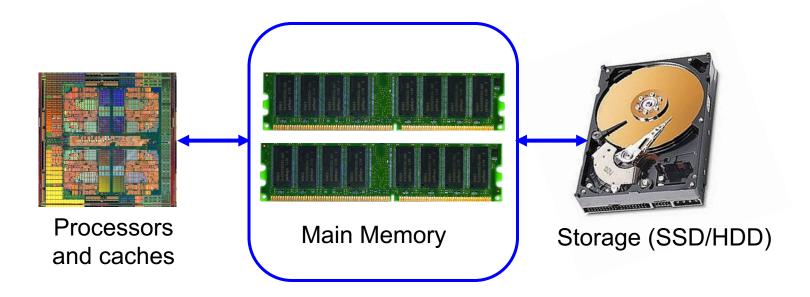

#### The Main Memory System

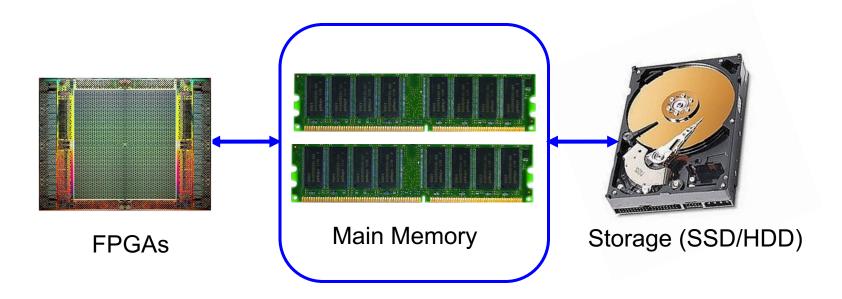

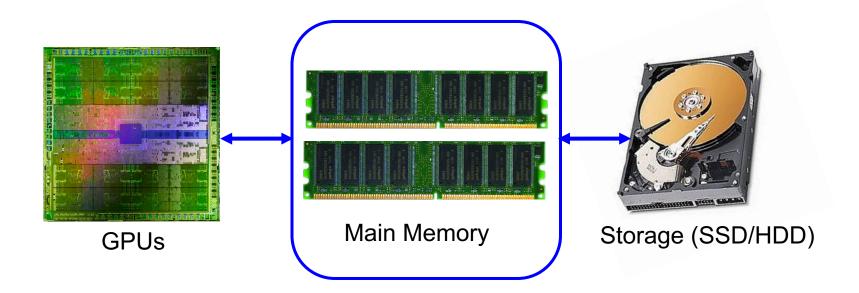

- Main memory is a critical component of all computing systems: server, mobile, embedded, desktop, sensor

- Main memory system must scale (in size, technology, efficiency, cost, and management algorithms) to maintain performance growth and technology scaling benefits

#### The Main Memory System

- Main memory is a critical component of all computing systems: server, mobile, embedded, desktop, sensor

- Main memory system must scale (in size, technology, efficiency, cost, and management algorithms) to maintain performance growth and technology scaling benefits

#### The Main Memory System

- Main memory is a critical component of all computing systems: server, mobile, embedded, desktop, sensor

- Main memory system must scale (in size, technology, efficiency, cost, and management algorithms) to maintain performance growth and technology scaling benefits

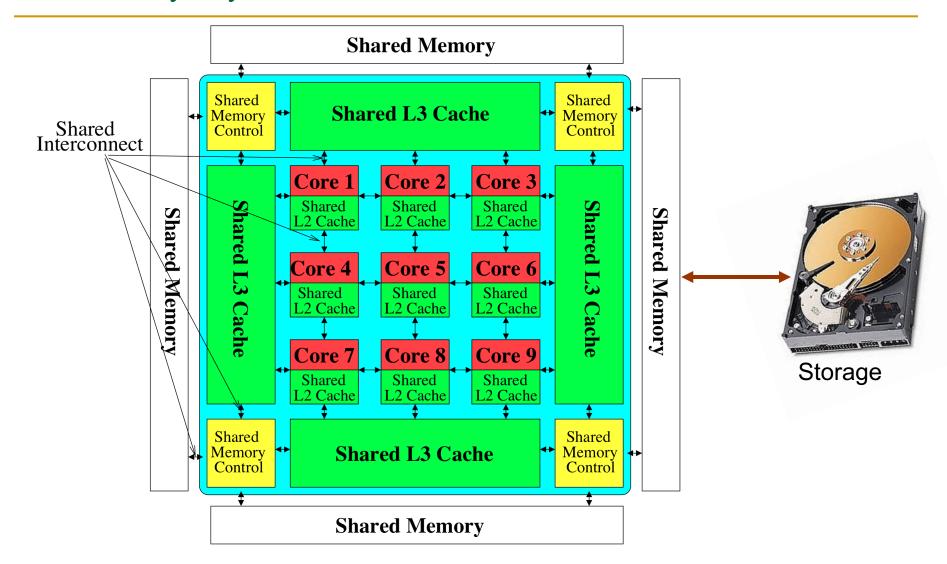

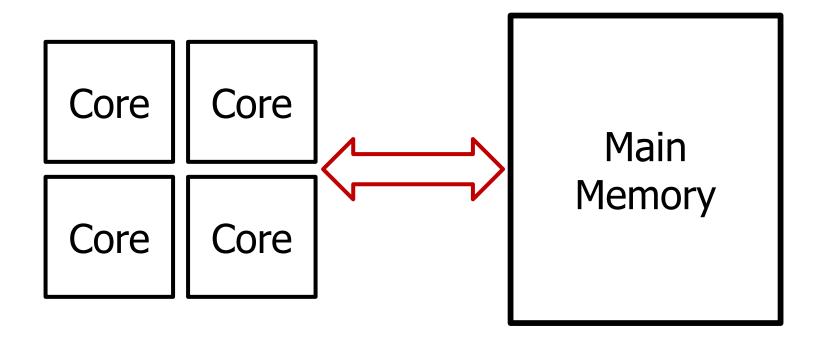

#### Memory System: A *Shared Resource* View

Most of the system is dedicated to storing and moving data

#### State of the Main Memory System

- Recent technology, architecture, and application trends

- lead to new requirements

- exacerbate old requirements

- DRAM and memory controllers, as we know them today, are (will be) unlikely to satisfy all requirements

- Some emerging non-volatile memory technologies (e.g., PCM) enable new opportunities: memory+storage merging

- We need to rethink the main memory system

- to fix DRAM issues and enable emerging technologies

- to satisfy all requirements

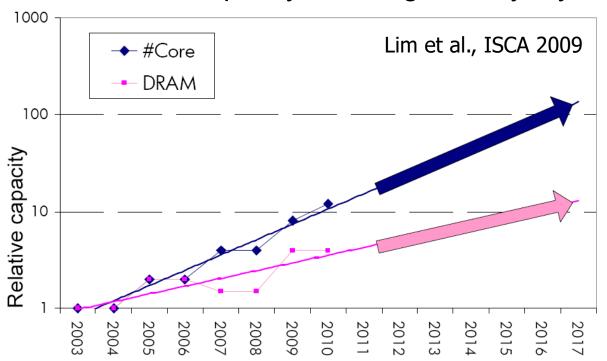

#### Major Trends Affecting Main Memory (I)

Need for main memory capacity, bandwidth, QoS increasing

Main memory energy/power is a key system design concern

DRAM technology scaling is ending

#### Major Trends Affecting Main Memory (II)

- Need for main memory capacity, bandwidth, QoS increasing

- Multi-core: increasing number of cores/agents

- Data-intensive applications: increasing demand/hunger for data

- Consolidation: cloud computing, GPUs, mobile, heterogeneity

Main memory energy/power is a key system design concern

DRAM technology scaling is ending

#### Consequence: The Memory Capacity Gap

Core count doubling ~ every 2 years

DRAM DIMM capacity doubling ~ every 3 years

- Memory capacity per core expected to drop by 30% every two years

- Trends worse for memory bandwidth per core!

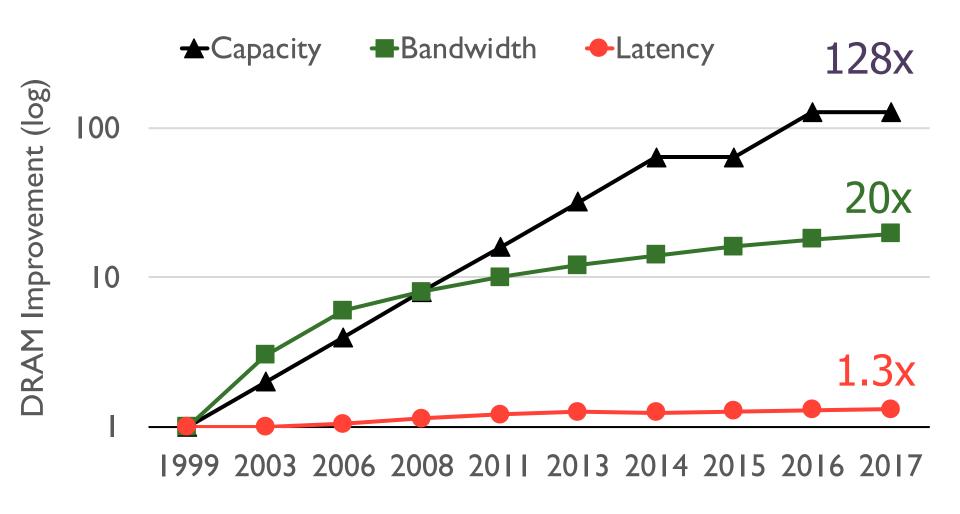

#### DRAM Capacity, Bandwidth & Latency

#### **In-memory Databases**

[Mao+, EuroSys'12; Clapp+ (Intel), IISWC'15]

#### **In-Memory Data Analytics**

[Clapp+ (Intel), IISWC'15; Awan+, BDCloud'15]

#### **Graph/Tree Processing**

[Xu+, IISWC'12; Umuroglu+, FPL'15]

#### **Datacenter Workloads**

[Kanev+ (Google), ISCA'15]

**In-memory Databases**

**Graph/Tree Processing**

#### Memory → performance bottleneck

#### **In-Memory Data Analytics**

[Clapp+ (Intel), IISWC'15; Awan+, BDCloud'15]

#### **Datacenter Workloads**

[Kanev+ (Google), ISCA' 15]

#### **Chrome**

Google's web browser

#### **TensorFlow Mobile**

Google's machine learning framework

Google's video codec

Google's video codec

**TensorFlow Mobile**

#### Memory → performance bottleneck

VP9

VouTube

Video Playback

Google's video codec

Google's video codec

#### Memory Bottleneck

I expect that over the coming decade memory subsystem design will be the *only* important design issue for microprocessors.

"It's the Memory, Stupid!" (Richard Sites, MPR, 1996)

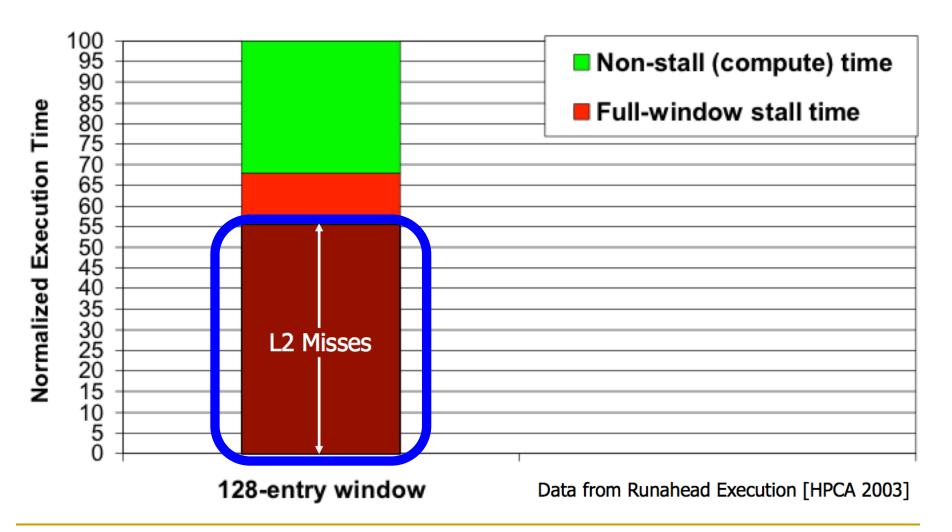

#### The Memory Bottleneck

Onur Mutlu, Jared Stark, Chris Wilkerson, and Yale N. Patt,

"Runahead Execution: An Alternative to Very Large Instruction

Windows for Out-of-order Processors"

Proceedings of the 9th International Symposium on High-Performance

Computer Architecture (HPCA), pages 129-140, Anaheim, CA, February 2003. Slides (pdf)

#### Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors

Onur Mutlu § Jared Stark † Chris Wilkerson ‡ Yale N. Patt §

§ECE Department

The University of Texas at Austin

{onur,patt}@ece.utexas.edu

†Microprocessor Research Intel Labs jared.w.stark@intel.com

‡Desktop Platforms Group Intel Corporation chris.wilkerson@intel.com

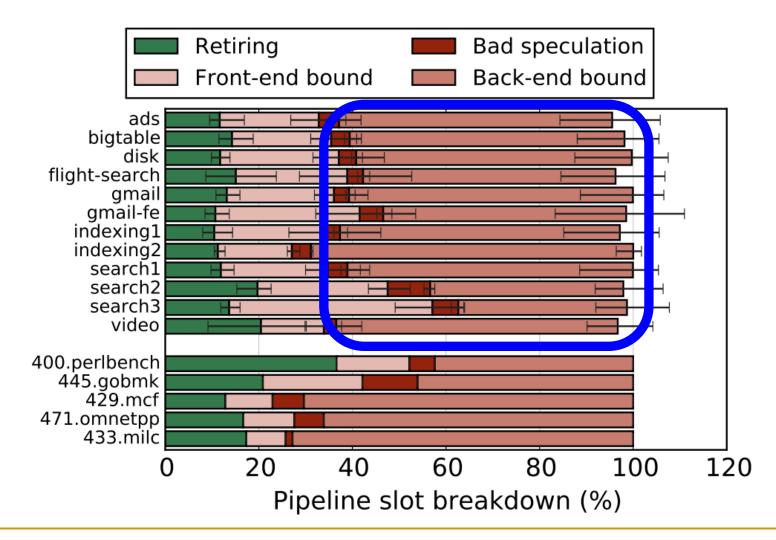

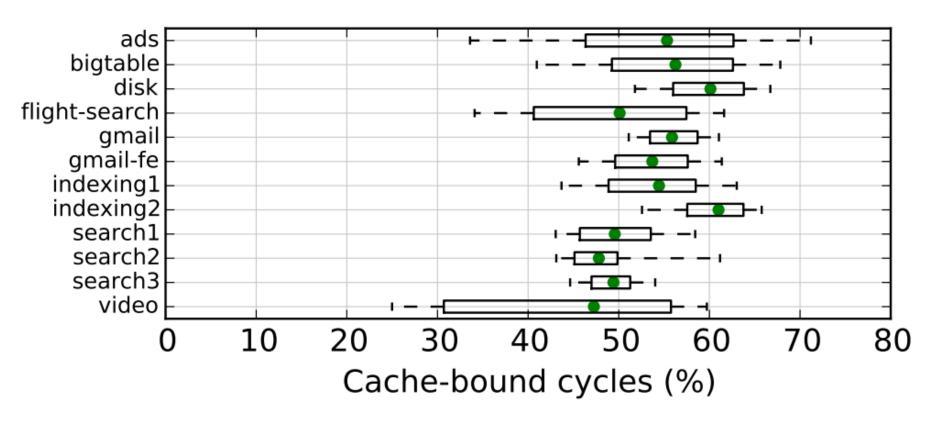

#### The Memory Bottleneck

All of Google's Data Center Workloads (2015):

#### The Memory Bottleneck

All of Google's Data Center Workloads (2015):

Figure 11: Half of cycles are spent stalled on caches.

#### Major Trends Affecting Main Memory (III)

Need for main memory capacity, bandwidth, QoS increasing

- Main memory energy/power is a key system design concern

- ~40-50% energy spent in off-chip memory hierarchy [Lefurgy,

IEEE Computer'03] >40% power in DRAM [Ware, HPCA'10][Paul,ISCA'15]

- DRAM consumes power even when not used (periodic refresh)

- DRAM technology scaling is ending

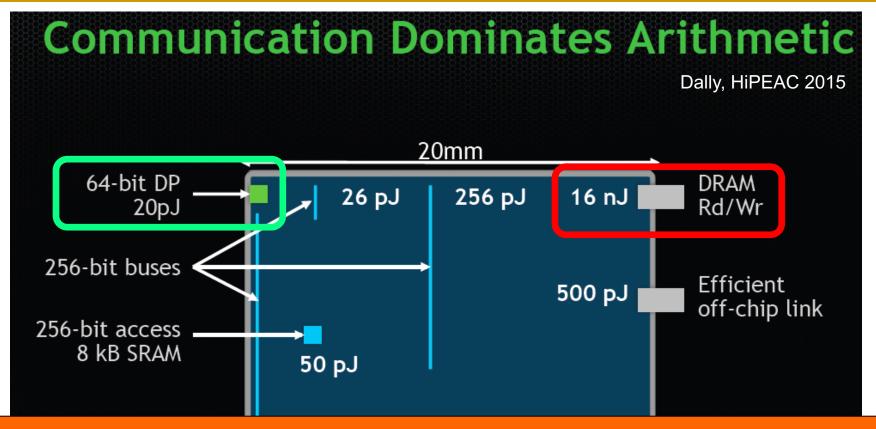

#### Energy Cost of Data Movement

A memory access consumes ~1000X the energy of a complex addition

#### Energy Waste in Mobile Devices

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the 23rd International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Williamsburg, VA, USA, March 2018.

### 62.7% of the total system energy is spent on data movement

#### Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup> Saugata Ghose<sup>1</sup> Youngsok Kim<sup>2</sup> Rachata Ausavarungnirun<sup>1</sup> Eric Shiu<sup>3</sup> Rahul Thakur<sup>3</sup> Daehyun Kim<sup>4,3</sup> Aki Kuusela<sup>3</sup> Allan Knies<sup>3</sup> Parthasarathy Ranganathan<sup>3</sup> Onur Mutlu<sup>5,1</sup>

SAFARI

#### Major Trends Affecting Main Memory (IV)

Need for main memory capacity, bandwidth, QoS increasing

Main memory energy/power is a key system design concern

- DRAM technology scaling is ending

- ITRS projects DRAM will not scale easily below X nm

- Scaling has provided many benefits:

- higher capacity (density), lower cost, lower energy

#### The DRAM Scaling Problem

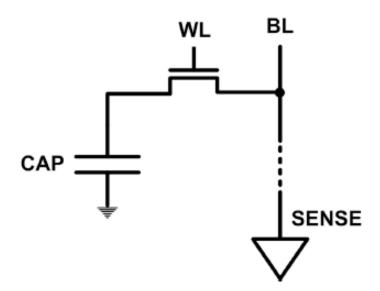

- DRAM stores charge in a capacitor (charge-based memory)

- Capacitor must be large enough for reliable sensing

- Access transistor should be large enough for low leakage and high retention time

- Scaling beyond 40-35nm (2013) is challenging [ITRS, 2009]

DRAM capacity, cost, and energy/power hard to scale

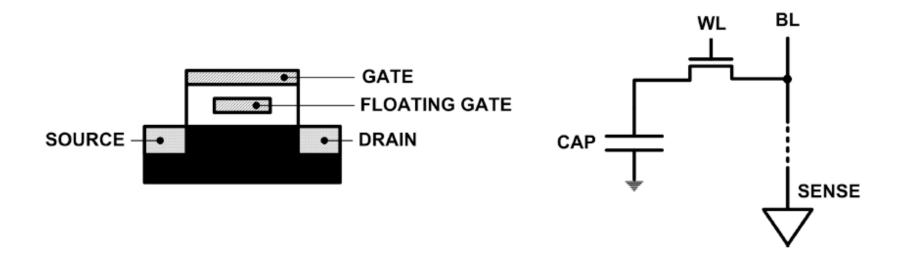

#### Limits of Charge Memory

- Difficult charge placement and control

- Flash: floating gate charge

- DRAM: capacitor charge, transistor leakage

- Reliable sensing becomes difficult as charge storage unit size reduces

#### As Memory Scales, It Becomes Unreliable

- Data from all of Facebook's servers worldwide

- Meza+, "Revisiting Memory Errors in Large-Scale Production Data Centers," DSN'15.

#### Large-Scale Failure Analysis of DRAM Chips

- Analysis and modeling of memory errors found in all of Facebook's server fleet

- Justin Meza, Qiang Wu, Sanjeev Kumar, and Onur Mutlu, "Revisiting Memory Errors in Large-Scale Production Data Centers: Analysis and Modeling of New Trends from the Field" Proceedings of the 45th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Rio de Janeiro, Brazil, June 2015.

[Slides (pptx) (pdf)] [DRAM Error Model]

#### Revisiting Memory Errors in Large-Scale Production Data Centers: Analysis and Modeling of New Trends from the Field

Justin Meza Qiang Wu\* Sanjeev Kumar\* Onur Mutlu Carnegie Mellon University \* Facebook, Inc.

67

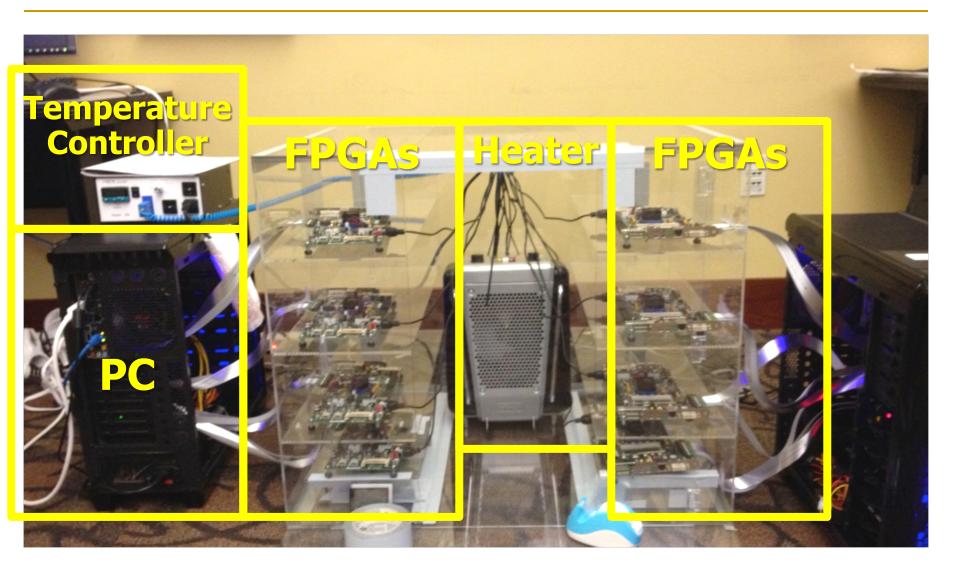

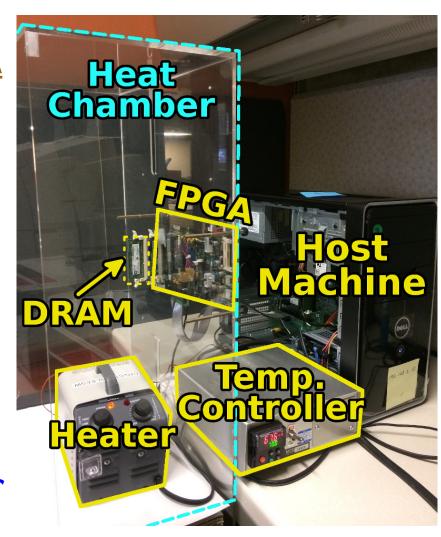

#### Infrastructures to Understand Such Issues

#### SoftMC: Open Source DRAM Infrastructure

Hasan Hassan et al., "SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies," HPCA 2017.

- Flexible

- Easy to Use (C++ API)

- Open-source github.com/CMU-SAFARI/SoftMC

#### SoftMC

https://github.com/CMU-SAFARI/SoftMC

### SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

```

Hasan Hassan Nandita Vijaykumar Samira Khan Saugata Ghose Kevin Chang Gennady Pekhimenko Donghyuk Lee^{6,3} Oguz Ergin Onur Mutlu Onur Mutlu

```

```

<sup>1</sup>ETH Zürich <sup>2</sup>TOBB University of Economics & Technology <sup>3</sup>Carnegie Mellon University <sup>4</sup>University of Virginia <sup>5</sup>Microsoft Research <sup>6</sup>NVIDIA Research

```

#### A Curious Discovery [Kim et al., ISCA 2014]

# One can predictably induce errors in most DRAM memory chips

#### DRAM RowHammer

## A simple hardware failure mechanism can create a widespread system security vulnerability

Forget Software—Now Hackers Are Exploiting Physics

BUSINESS CULTURE DESIGN GEAR SCIENCE

SHARE

ANDY GREENBERG SECURITY 08.31.16 7:00 AM

## FORGET SOFTWARE—NOW HACKERS ARE EXPLOITING PHYSICS

## The Reliability & Security Perspectives

Onur Mutlu,

"The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser"

Invited Paper in Proceedings of the <u>Design, Automation, and Test in</u> <u>Europe Conference</u> (**DATE**), Lausanne, Switzerland, March 2017. [Slides (pptx) (pdf)]

## The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser

Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

https://people.inf.ethz.ch/omutlu

## A RowHammer Retrospective

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

<u>IEEE Transactions on Computer-Aided Design of Integrated</u>

<u>Circuits and Systems</u> (TCAD) Special Issue on Top Picks in Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

## RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> §ETH Zürich <sup>‡</sup>Carnegie Mellon University

SAFARI (14

## Major Trends Affecting Main Memory (V)

- DRAM scaling has already become increasingly difficult

- Increasing cell leakage current, reduced cell reliability, increasing manufacturing difficulties [Kim+ ISCA 2014], [Liu+ ISCA 2013], [Mutlu IMW 2013], [Mutlu DATE 2017]

- Difficult to significantly improve capacity, energy

- Emerging memory technologies are promising

75

## Major Trends Affecting Main Memory (V)

- DRAM scaling has already become increasingly difficult

- Increasing cell leakage current, reduced cell reliability, increasing manufacturing difficulties [Kim+ ISCA 2014], [Liu+ ISCA 2013], [Mutlu IMW 2013], [Mutlu DATE 2017]

- Difficult to significantly improve capacity, energy

- Emerging memory technologies are promising

| 3D-Stacked DRAM                                                       | higher bandwidth | smaller capacity                                          |

|-----------------------------------------------------------------------|------------------|-----------------------------------------------------------|

| Reduced-Latency DRAM<br>(e.g., RL/TL-DRAM, FLY-RAM)                   | lower latency    | higher cost                                               |

| Low-Power DRAM<br>(e.g., LPDDR3, LPDDR4, Voltron)                     | lower power      | higher latency<br>higher cost                             |

| Non-Volatile Memory (NVM)<br>(e.g., PCM, STTRAM, ReRAM, 3D<br>Xpoint) | larger capacity  | higher latency<br>higher dynamic power<br>lower endurance |

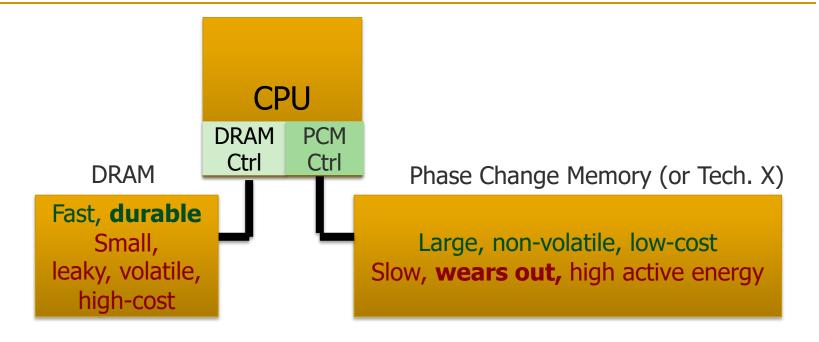

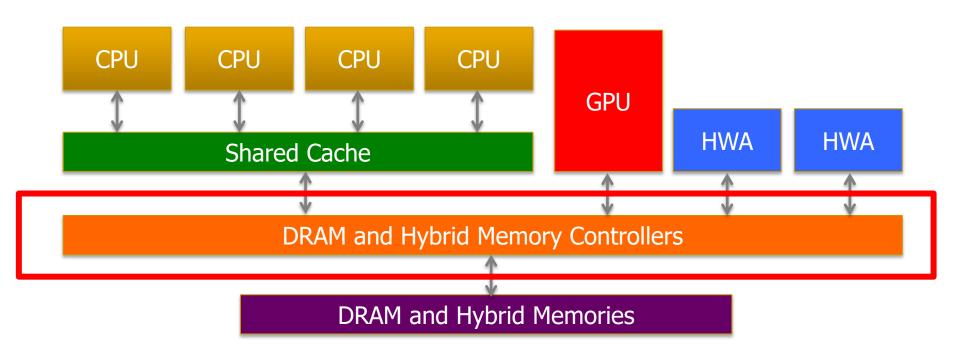

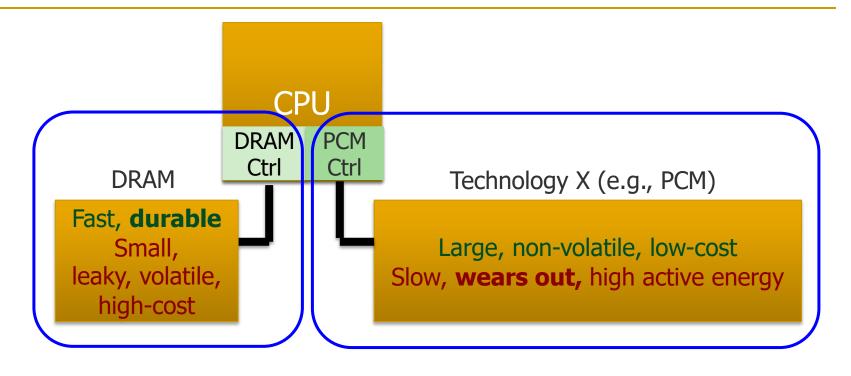

## Major Trend: Hybrid Main Memory

Hardware/software manage data allocation and movement to achieve the best of multiple technologies

Meza+, "Enabling Efficient and Scalable Hybrid Memories," IEEE Comp. Arch. Letters, 2012. Yoon+, "Row Buffer Locality Aware Caching Policies for Hybrid Memories," ICCD 2012 Best Paper Award.

# Main Memory Needs Intelligent Controllers

## Industry Is Writing Papers About It, Too

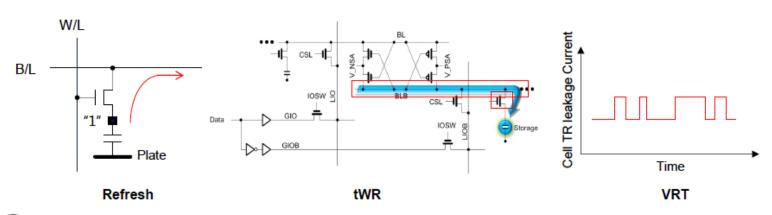

#### DRAM Process Scaling Challenges

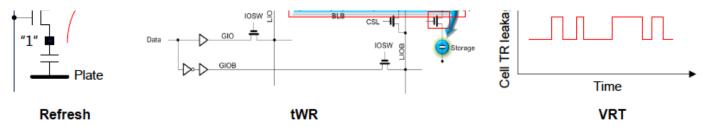

#### Refresh

- Difficult to build high-aspect ratio cell capacitors decreasing cell capacitance

- · Leakage current of cell access transistors increasing

#### tWR

- Contact resistance between the cell capacitor and access transistor increasing

- · On-current of the cell access transistor decreasing

- Bit-line resistance increasing

#### VRT

· Occurring more frequently with cell capacitance decreasing

3 / 12

## Call for Intelligent Memory Controllers

#### **DRAM Process Scaling Challenges**

#### Refresh

Difficult to build high-aspect ratio cell capacitors decreasing cell capacitance

THE MEMORY FORUM 2014

## Co-Architecting Controllers and DRAM to Enhance DRAM Process Scaling

Uksong Kang, Hak-soo Yu, Churoo Park, \*Hongzhong Zheng, \*\*John Halbert, \*\*Kuljit Bains, SeongJin Jang, and Joo Sun Choi

Samsung Electronics, Hwasung, Korea / \*Samsung Electronics, San Jose / \*\*Intel

## An Orthogonal Issue: Memory Interference

Cores' interfere with each other when accessing shared main memory Uncontrolled interference leads to many problems (QoS, performance)

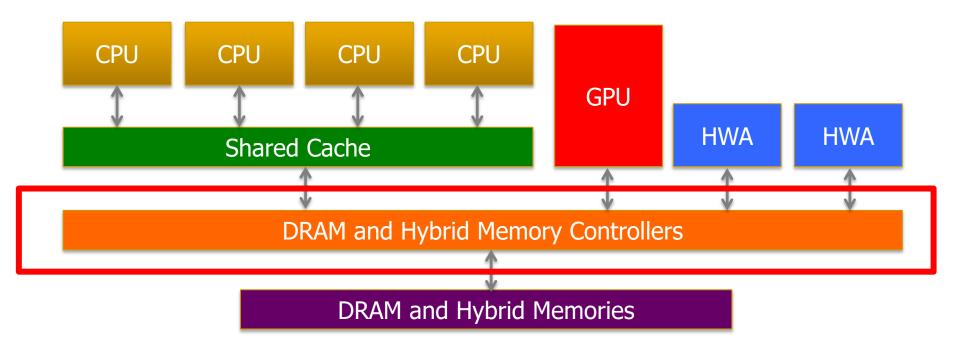

### Goal: Predictable Performance in Complex Systems

- Heterogeneous agents: CPUs, GPUs, and HWAs

- Main memory interference between CPUs, GPUs, HWAs

How to allocate resources to heterogeneous agents to mitigate interference and provide predictable performance?

## Main Memory Needs Intelligent Controllers

## Trends, Challenges, and Opportunities in Main Memory

## How Do We Solve The Memory Problem?

- Fix it: Make memory and controllers more intelligent

- New interfaces, functions, architectures: system-mem codesign

- Eliminate or minimize it: Replace or (more likely) augment

DRAM with a different technology

- New technologies and system-wide rethinking of memory & storage

- Embrace it: Design heterogeneous memories (none of which are perfect) and map data intelligently across them

- New models for data management and maybe usage

...

## How Do We Solve The Memory Problem?

- Fix it: Make memory and controllers more intelligent

- New interfaces, functions, architectures: system-mem codesign

- Eliminate or minimize it: Replace or (more likely) augment DRAM with a different technology

- New technologies and system-wide rethinking of memory & storage

- Embrace it: Design heterogeneous memories (none of which are perfect) and map data intelligently across them

- New models for data management and maybe usage

Solutions (to memory scaling) require software/hardware/device cooperation

## How Do We Solve The Memory Problem?

- Fix it: Make men Problems pllers more intelligent New interfaces, tectures: system-mem codesign **Algorithms** User **Programs** Eliminate or minimize it: Replace or (more likely) augment DRAM with a different technology Runtime System New technologies and ethinking of memory & (VM, OS, MM) storage ISA Microarchitecture

- Embrace it: Design he Logic nemories (none of which are perfect) and map Devices

- New models for data management and maybe usage

Solutions (to memory scaling) require software/hardware/device cooperation

## Solution 1: New Memory Architectures

- Overcome memory shortcomings with

- Memory-centric system design

- Novel memory architectures, interfaces, functions

- Better waste management (efficient utilization)

- Key issues to tackle

- □ Enable reliability at low cost → high capacity

- Reduce energy

- Reduce latency

- Improve bandwidth

- Reduce waste (capacity, bandwidth, latency)

- Enable computation close to data

## Solution 1: New Memory Architectures

Liu+, "RAIDR: Retention-Aware Intelligent DRAM Refresh," ISCA 2012. Kim+, "A Case for Exploiting Subarray-Level Parallelism in DRAM," ISCA 2012. Lee+, "Tiered-Latency DRAM: A Low Latency and Low Cost DRAM Architecture," HPCA 2013. Liu+, "An Experimental Study of Data Retention Behavior in Modern DRAM Devices," ISCA 2013. Seshadri+, "RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data," MICRO 2013. Pekhimenko+, "Linearly Compressed Pages: A Main Memory Compression Framework," MICRO 2013. Chang+, "Improving DRAM Performance by Parallelizing Refreshes with Accesses," HPCA 2014. Khan+, "The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study," SIGMETRICS 2014. Luo+, "Characterizing Application Memory Error Vulnerability to Optimize Data Center Cost." DSN 2014. Kim+, "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," ISCA 2014. Lee+, "Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case," HPCA 2015. Oureshi+, "AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems," DSN 2015. Meza+, "Revisiting Memory Errors in Large-Scale Production Data Centers; Analysis and Modeling of New Trends from the Field," DSN 2015. Kim+, "Ramulator: A Fast and Extensible DRAM Simulator," IEEE CAL 2015. Seshadri+, "Fast Bulk Bitwise AND and OR in DRAM," IEEE CAL 2015. Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing," ISCA 2015. Ahn+, "PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture," ISCA 2015. Lee+, "Decoupled Direct Memory Access: Isolating CPU and IO Traffic by Leveraging a Dual-Data-Port DRAM," PACT 2015. Seshadri+, "Gather-Scatter DRAM: In-DRAM Address Translation to Improve the Spatial Locality of Non-unit Strided Accesses," MICRO 2015. Lee+, "Simultaneous Multi-Laver Access: Improving 3D-Stacked Memory Bandwidth at Low Cost." TACO 2016. Hassan+, "ChargeCache: Reducing DRAM Latency by Exploiting Row Access Locality," HPCA 2016. Chang+, "Low-Cost Inter-Linked Subarrays (LISA): Enabling Fast Inter-Subarray Data Migration in DRAM," HPCA 2016. Chang+, "Understanding Latency Variation in Modern DRAM Chips Experimental Characterization, Analysis, and Optimization," SIGMETRICS 2016. Khan+, "PARBOR: An Efficient System-Level Technique to Detect Data Dependent Failures in DRAM," DSN 2016. Hsieh+, "Transparent Offloading and Mapping (TOM): Enabling Programmer-Transparent Near-Data Processing in GPU Systems," ISCA 2016. Hashemi+, "Accelerating Dependent Cache Misses with an Enhanced Memory Controller," ISCA 2016. Boroumand+, "LazyPIM: An Efficient Cache Coherence Mechanism for Processing-in-Memory," IEEE CAL 2016. Pattnaik+, "Scheduling Techniques for GPU Architectures with Processing-In-Memory Capabilities," PACT 2016. Hsieh+, "Accelerating Pointer Chasing in 3D-Stacked Memory: Challenges, Mechanisms, Evaluation," ICCD 2016. Hashemi+, "Continuous Runahead: Transparent Hardware Acceleration for Memory Intensive Workloads," MICRO 2016. Khan+, "A Case for Memory Content-Based Detection and Mitigation of Data-Dependent Failures in DRAM"," IEEE CAL 2016. Hassan+, "SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies," HPCA 2017. Mutlu, "The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser," DATE 2017. Lee+, "Design-Induced Latency Variation in Modern DRAM Chips: Characterization, Analysis, and Latency Reduction Mechanisms," SIGMETRICS 2017. Chang+, "Understanding Reduced-Voltage Operation in Modern DRAM Devices: Experimental Characterization, Analysis, and Mechanisms," SIGMETRICS 2017. Patel+, "The Reach Profiler (REAPER): Enabling the Mitigation of DRAM Retention Failures via Profiling at Aggressive Conditions," ISCA 2017. Seshadri and Mutlu, "Simple Operations in Memory to Reduce Data Movement," ADCOM 2017. Liu+, "Concurrent Data Structures for Near-Memory Computing," SPAA 2017. Khan+, "Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content," MICRO 2017. Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology," MICRO 2017. Kim+, "GRIM-Filter: Fast Seed Location Filtering in DNA Read Mapping Using Processing-in-Memory Technologies," BMC Genomics 2018. Kim+, "The DRAM Latency PUF: Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern DRAM Devices," HPCA 2018. Boroumand+, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks," ASPLOS 2018. Das+, "VRL-DRAM: Improving DRAM Performance via Variable Refresh Latency," DAC 2018. Ghose+, "What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study," SIGMETRICS 2018. Kim+, "Solar-DRAM: Reducing DRAM Access Latency by Exploiting the Variation in Local Bitlines," ICCD 2018. Wang+, "Reducing DRAM Latency via Charge-Level-Aware Look-Ahead Partial Restoration," MICRO 2018. Kim+, "D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput," HPCA 2019. Singh+, "NAPEL: Near-Memory Computing Application Performance Prediction via Ensemble Learning," DAC 2019. Ghose+, "Demystifying Workload-DRAM Interactions: An Experimental Study," SIGMETRICS 2019. Patel+, "Understanding and Modeling On-Die Error Correction in Modern DRAM; An Experimental Study Using Real Devices," DSN 2019. Boroumand+, "CoNDA: Efficient Cache Coherence Support for Near-Data Accelerators," ISCA 2019. Hassan+, "CROW: A Low-Cost Substrate for Improving DRAM Performance, Energy Efficiency, and Reliability," ISCA 2019. Mutlu and Kim, "RowHammer: A Retrospective," TCAD 2019. Mutlu+, "Processing Data Where It Makes Sense: Enabling In-Memory Computation," MICPRO 2019. Seshadri and Mutlu, "In-DRAM Bulk Bitwise Execution Engine," ADCOM 2020. Koppula+, "EDEN: Energy-Efficient, High-Performance Neural Network Inference Using Approximate DRAM," MICRO 2019. Avoid DRAM: Seshadri+, "The Evicted-Address Filter: A Unified Mechanism to Address Both Cache Pollution and Thrashing," PACT 2012. Pekhimenko+, "Base-Delta-Immediate Compression: Practical Data Compression for On-Chip Caches," PACT 2012. Seshadri+, "The Dirty-Block Index," ISCA 2014. Pekhimenko+, "Exploiting Compressed Block Size as an Indicator of Future Reuse," HPCA 2015.

Vijaykumar+, "A Case for Core-Assisted Bottleneck Acceleration in GPUs: Enabling Flexible Data Compression with Assist Warps," ISCA 2015.

Pekhimenko+, "Toggle-Aware Bandwidth Compression for GPUs," HPCA 2016.

SAFARI

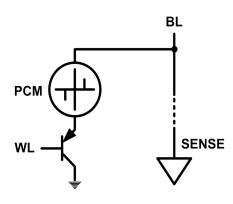

## Solution 2: Emerging Memory Technologies

- Some emerging resistive memory technologies seem more scalable than DRAM (and they are non-volatile)

- Example: Phase Change Memory

- Data stored by changing phase of material

- Data read by detecting material's resistance

- Expected to scale to 9nm (2022 [ITRS 2009])

- Prototyped at 20nm (Raoux+, IBM JRD 2008)

- But, emerging technologies have (many) shortcomings

- Can they be enabled to replace/augment/surpass DRAM?

## Solution 2: Emerging Memory Technologies

- Lee+, "Architecting Phase Change Memory as a Scalable DRAM Alternative," ISCA'09, CACM'10, IEEE Micro'10.

- Meza+, "Enabling Efficient and Scalable Hybrid Memories," IEEE Comp. Arch. Letters 2012.

- Yoon, Meza+, "Row Buffer Locality Aware Caching Policies for Hybrid Memories," ICCD 2012.

- Kultursay+, "Evaluating STT-RAM as an Energy-Efficient Main Memory Alternative," ISPASS 2013.

- Meza+, "A Case for Efficient Hardware-Software Cooperative Management of Storage and Memory," WEED 2013.

- Lu+, "Loose Ordering Consistency for Persistent Memory," ICCD 2014.

- Zhao+, "FIRM: Fair and High-Performance Memory Control for Persistent Memory Systems," MICRO 2014.

- Yoon, Meza+, "Efficient Data Mapping and Buffering Techniques for Multi-Level Cell Phase-Change Memories," TACO 2014.

- Ren+, "ThyNVM: Enabling Software-Transparent Crash Consistency in Persistent Memory Systems," MICRO 2015.

- Chauhan+, "NVMove: Helping Programmers Move to Byte-Based Persistence," INFLOW 2016.

- Li+, "Utility-Based Hybrid Memory Management," CLUSTER 2017.

- Yu+, "Banshee: Bandwidth-Efficient DRAM Caching via Software/Hardware Cooperation," MICRO 2017.

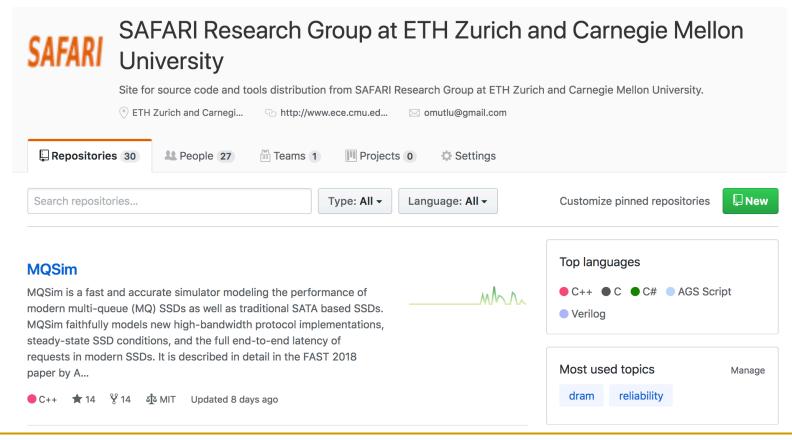

- Tavakkol+, "MQSim: A Framework for Enabling Realistic Studies of Modern Multi-Queue SSD Devices," FAST 2018.

- Tavakkol+, "FLIN: Enabling Fairness and Enhancing Performance in Modern NVMe Solid State Drives," ISCA 2018.

- Sadrosadati+. "LTRF: Enabling High-Capacity Register Files for GPUs via Hardware/Software Cooperative Register Prefetching," ASPLOS 2018.

- Salkhordeh+, "An Analytical Model for Performance and Lifetime Estimation of Hybrid DRAM-NVM Main Memories," TC 2019.

- Wang+, "Panthera: Holistic Memory Management for Big Data Processing over Hybrid Memories," PLDI 2019.

- Song+, "Enabling and Exploiting Partition-Level Parallelism (PALP) in Phase Change Memories," CASES 2019.

- Liu+, "Binary Star: Coordinated Reliability in Heterogeneous Memory Systems for High Performance and Scalability," MICRO'19.

## Combination: Hybrid Memory Systems

Hardware/software manage data allocation and movement to achieve the best of multiple technologies

Meza+, "Enabling Efficient and Scalable Hybrid Memories," IEEE Comp. Arch. Letters, 2012. Yoon, Meza et al., "Row Buffer Locality Aware Caching Policies for Hybrid Memories," ICCD 2012 Best Paper Award.

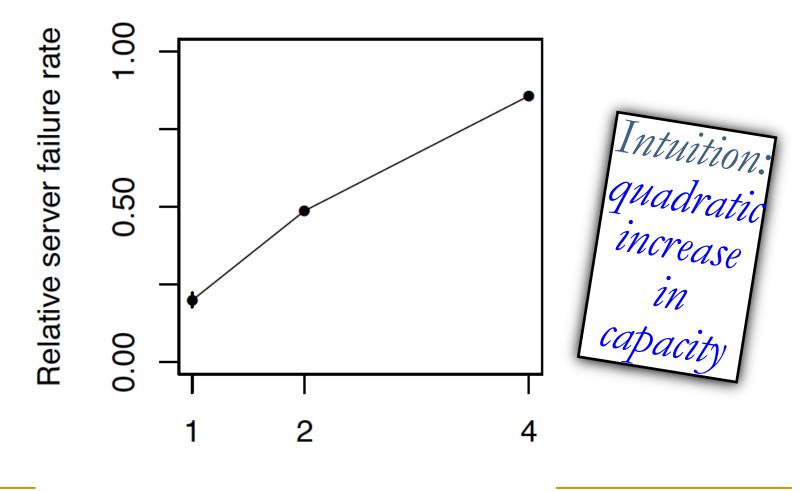

## Exploiting Memory Error Tolerance with Hybrid Memory Systems

Vulnerable data

Tolerant data

Reliable memory

Low-cost memory

On Microsoft's Web Search workload Reduces server hardware cost by 4.7 % Achieves single server availability target of 99.90 %

Heterogeneous-Reliability Memory [DSN 2014]

## More on Heterogeneous Reliability Memory

Yixin Luo, Sriram Govindan, Bikash Sharma, Mark Santaniello, Justin Meza, Aman Kansal, Jie Liu, Badriddine Khessib, Kushagra Vaid, and Onur Mutlu, "Characterizing Application Memory Error Vulnerability to Optimize Data Center Cost via Heterogeneous-Reliability Memory"

Proceedings of the 44th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Atlanta, GA, June 2014. [Summary]

[Slides (pptx) (pdf)] [Coverage on ZDNet]

## Characterizing Application Memory Error Vulnerability to Optimize Datacenter Cost via Heterogeneous-Reliability Memory

Yixin Luo Sriram Govindan\* Bikash Sharma\* Mark Santaniello\* Justin Meza Aman Kansal\* Jie Liu\* Badriddine Khessib\* Kushagra Vaid\* Onur Mutlu Carnegie Mellon University, yixinluo@cs.cmu.edu, {meza, onur}@cmu.edu

\*Microsoft Corporation, {srgovin, bsharma, marksan, kansal, jie.liu, bkhessib, kvaid}@microsoft.com

## An Orthogonal Issue: Memory Interference

- Problem: Memory interference between cores is uncontrolled

- → unfairness, starvation, low performance

- → uncontrollable, unpredictable, vulnerable system

- Solution: QoS-Aware Memory Systems

- Hardware designed to provide a configurable fairness substrate

- Application-aware memory scheduling, partitioning, throttling

- Software designed to configure the resources to satisfy different QoS goals

- QoS-aware memory systems can provide predictable performance and higher efficiency

## Strong Memory Service Guarantees

Goal: Satisfy performance/SLA requirements in the presence of shared main memory, heterogeneous agents, and hybrid memory/storage

#### Approach:

- Develop techniques/models to accurately estimate the performance loss of an application/agent in the presence of resource sharing

- Develop mechanisms (hardware and software) to enable the resource partitioning/prioritization needed to achieve the required performance levels for all applications

- All the while providing high system performance

- Subramanian et al., "MISE: Providing Performance Predictability and Improving Fairness in Shared Main Memory Systems," HPCA 2013.

- Subramanian et al., "The Application Slowdown Model," MICRO 2015.

## **DRAM Controllers**

## It All Started with FSB Controllers (2001)

#### Method and apparatus to control memory accesses

#### Abstract

A method and apparatus for accessing memory comprising monitoring memory accesses from a hardware prefetcher and determining whether the memory accesses from the hardware prefetcher are used by an out-of-order core. A front side bus controller switches memory access modes from a minimize memory access latency mode to a maximize memory bus bandwidth mode if a percentage of the memory accesses generated by the hardware prefetcher are used by the out-of-order core.

#### Images (6)

#### Classifications

G06F12/0215 Addressing or allocation; Relocation with look ahead addressing means

#### US6799257B2

**United States**

Download PDF

Find Prior Art Similar

Inventor: Eric A. Sprangle, Onur Mutlu

**Current Assignee: Intel Corp**

#### Worldwide applications

2002 • US 2003 • AU JP DE KR CN WO GB TW 2004 • US 2005 • HK

Application US10/079,967 events ②

2002-02-21 • Application filed by Intel Corp

2002-02-21 • Priority to US10/079,967

2002-04-25 • Assigned to INTEL CORPORATION ②

## Memory Performance Attacks [usenix sec'07]

Thomas Moscibroda and Onur Mutlu, "Memory Performance Attacks: Denial of Memory Service in Multi-Core Systems" Proceedings of the 16th USENIX Security Symposium (USENIX SECURITY), pages 257-274, Boston, MA, August 2007. Slides (ppt)

## Memory Performance Attacks: Denial of Memory Service in Multi-Core Systems

Thomas Moscibroda Onur Mutlu

Microsoft Research

{moscitho,onur}@microsoft.com

### STFM [MICRO'07]

Onur Mutlu and Thomas Moscibroda,

"Stall-Time Fair Memory Access Scheduling for Chip Multiprocessors"

Proceedings of the <u>40th International Symposium on</u> <u>Microarchitecture</u> (**MICRO**), pages 146-158, Chicago, IL, December 2007. [Summary] [Slides (ppt)]

#### Stall-Time Fair Memory Access Scheduling for Chip Multiprocessors

Onur Mutlu Thomas Moscibroda

Microsoft Research {onur,moscitho}@microsoft.com

### PAR-BS [ISCA'08]

Onur Mutlu and Thomas Moscibroda,

"Parallelism-Aware Batch Scheduling: Enhancing both

Performance and Fairness of Shared DRAM Systems"

Proceedings of the 35th International Symposium on Computer

Architecture (ISCA), pages 63-74, Beijing, China, June 2008.

[Summary] [Slides (ppt)]

### Parallelism-Aware Batch Scheduling: Enhancing both Performance and Fairness of Shared DRAM Systems

Onur Mutlu Thomas Moscibroda Microsoft Research {onur,moscitho}@microsoft.com

### On PAR-BS

Variants implemented in Samsung SoC memory controllers

Effective platform level approach and DRAM accesses are crucial to system performance. This paper touches this topics and suggest a superior approach to current known techniques.

Review from ISCA 2008

## ATLAS Memory Scheduler [HPCA'10]

Yoongu Kim, Dongsu Han, Onur Mutlu, and Mor Harchol-Balter, "ATLAS: A Scalable and High-Performance Scheduling Algorithm for Multiple Memory Controllers" Proceedings of the 16th International Symposium on High-Performance Computer Architecture (HPCA), Bangalore, India, January 2010. Slides (pptx)

## ATLAS: A Scalable and High-Performance Scheduling Algorithm for Multiple Memory Controllers

Yoongu Kim Dongsu Han Onur Mutlu Mor Harchol-Balter Carnegie Mellon University

## Thread Cluster Memory Scheduling [MICRO'10]

Yoongu Kim, Michael Papamichael, Onur Mutlu, and Mor Harchol-Balter,

"Thread Cluster Memory Scheduling: Exploiting Differences in Memory Access Behavior"

Proceedings of the <u>43rd International Symposium on</u>

Microarchitecture (MICRO), pages 65-76, Atlanta, GA,

December 2010. Slides (pptx) (pdf)

#### Thread Cluster Memory Scheduling: Exploiting Differences in Memory Access Behavior

Yoongu Kim yoonguk@ece.cmu.edu

Michael Papamichael papamix@cs.cmu.edu

Onur Mutlu onur@cmu.edu

Mor Harchol-Balter harchol@cs.cmu.edu

Carnegie Mellon University

### BLISS [ICCD'14, TPDS'16]

Lavanya Subramanian, Donghyuk Lee, Vivek Seshadri, Harsha Rastogi, and Onur Mutlu,

"The Blacklisting Memory Scheduler: Achieving High Performance and Fairness at Low Cost"

Proceedings of the <u>32nd IEEE International Conference on Computer Design</u> (ICCD), Seoul, South Korea, October 2014.

[Slides (pptx) (pdf)]

## The Blacklisting Memory Scheduler: Achieving High Performance and Fairness at Low Cost

Lavanya Subramanian, Donghyuk Lee, Vivek Seshadri, Harsha Rastogi, Onur Mutlu Carnegie Mellon University {lsubrama,donghyu1,visesh,harshar,onur}@cmu.edu

## Staged Memory Scheduling: CPU-GPU [ISCA'12]

Rachata Ausavarungnirun, Kevin Chang, Lavanya Subramanian, Gabriel Loh, and Onur Mutlu,

"Staged Memory Scheduling: Achieving High

Performance and Scalability in Heterogeneous Systems"

Proceedings of the 39th International Symposium on Computer

Architecture (ISCA), Portland, OR, June 2012. Slides (pptx)

## Staged Memory Scheduling: Achieving High Performance and Scalability in Heterogeneous Systems

Rachata Ausavarungnirun<sup>†</sup> Kevin Kai-Wei Chang<sup>†</sup> Lavanya Subramanian<sup>†</sup> Gabriel H. Loh<sup>‡</sup> Onur Mutlu<sup>†</sup>

<sup>†</sup>Carnegie Mellon University

<sup>†</sup>Advanced Micro Devices, Inc.

{rachata,kevincha,lsubrama,onur}@cmu.edu

<sup>‡</sup>Advanced Micro Devices, Inc.

gabe.loh@amd.com

## DASH: Heterogeneous Systems [TACO'16]

Hiroyuki Usui, Lavanya Subramanian, Kevin Kai-Wei Chang, and Onur Mutlu,

"DASH: Deadline-Aware High-Performance Memory Scheduler for Heterogeneous Systems with Hardware Accelerators"

ACM Transactions on Architecture and Code Optimization (TACO),

Vol. 12, January 2016.

Presented at the <u>11th HiPEAC Conference</u>, Prague, Czech Republic, January 2016.

[Slides (pptx) (pdf)]

Source Code

## DASH: Deadline-Aware High-Performance Memory Scheduler for Heterogeneous Systems with Hardware Accelerators

HIROYUKI USUI, LAVANYA SUBRAMANIAN, KEVIN KAI-WEI CHANG, and ONUR MUTLU, Carnegie Mellon University

#### SAFARI

### MISE: Predictable Performance [HPCA'13]

Lavanya Subramanian, Vivek Seshadri, Yoongu Kim, Ben Jaiyen, and Onur Mutlu,

"MISE: Providing Performance Predictability and Improving Fairness in Shared Main Memory Systems"

Proceedings of the <u>19th International Symposium on High-</u> <u>Performance Computer Architecture</u> (**HPCA**), Shenzhen, China, February 2013. <u>Slides (pptx)</u>

## MISE: Providing Performance Predictability and Improving Fairness in Shared Main Memory Systems

Lavanya Subramanian Vivek Seshadri Yoongu Kim Ben Jaiyen Onur Mutlu Carnegie Mellon University

### ASM: Predictable Performance [MICRO'15]

Lavanya Subramanian, Vivek Seshadri, Arnab Ghosh, Samira Khan, and Onur Mutlu,

"The Application Slowdown Model: Quantifying and Controlling the Impact of Inter-Application Interference at Shared Caches and Main Memory"

Proceedings of the <u>48th International Symposium on Microarchitecture</u> (**MICRO**), Waikiki, Hawaii, USA, December 2015.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Poster (pptx) (pdf)]

Source Code

# The Application Slowdown Model: Quantifying and Controlling the Impact of Inter-Application Interference at Shared Caches and Main Memory

Lavanya Subramanian\*§ Vivek Seshadri\* Arnab Ghosh\*†

Samira Khan\*‡ Onur Mutlu\*

\*Carnegie Mellon University §Intel Labs †IIT Kanpur ‡University of Virginia

#### SAFARI

# Memory Controllers are critical to research

They will become even more important

# Memory Control is Getting More Complex

- Heterogeneous agents: CPUs, GPUs, and HWAs

- Main memory interference between CPUs, GPUs, HWAs

Many goals, many constraints, many metrics ...

## Memory Control w/ Machine Learning [ISCA'08]

Engin Ipek, Onur Mutlu, José F. Martínez, and Rich Caruana,

"Self Optimizing Memory Controllers: A Reinforcement Learning Approach"

Proceedings of the <u>35th International Symposium on Computer Architecture</u> (**ISCA**), pages 39-50, Beijing, China, June 2008. <u>Slides (pptx)</u>

Self-Optimizing Memory Controllers: A Reinforcement Learning Approach

Engin İpek<sup>1,2</sup> Onur Mutlu<sup>2</sup> José F. Martínez<sup>1</sup> Rich Caruana<sup>1</sup>

<sup>1</sup>Cornell University, Ithaca, NY 14850 USA

<sup>2</sup> Microsoft Research, Redmond, WA 98052 USA

# Memory Controllers: Many New Problems

# Main Memory Needs Intelligent Controllers

# What We Will Cover In The Next Few Lectures

# Agenda for The Next Few Lectures

- Memory Importance and Trends

- RowHammer: Memory Reliability and Security

- In-Memory Computation

- Low-Latency Memory

- Data-Driven and Data-Aware Architectures

- Guiding Principles & Conclusion

# An "Early" Position Paper [IMW'13]

Onur Mutlu,

"Memory Scaling: A Systems Architecture Perspective"

Proceedings of the <u>5th International Memory</u>

Workshop (IMW), Monterey, CA, May 2013. <u>Slides</u>

(pptx) (pdf)

EETimes Reprint

### Memory Scaling: A Systems Architecture Perspective

Onur Mutlu

Carnegie Mellon University

onur@cmu.edu

http://users.ece.cmu.edu/~omutlu/

# Challenges in DRAM Scaling

- Refresh

- Latency

- Bank conflicts/parallelism

- Reliability and vulnerabilities

- Energy & power

- Memory's inability to do more than store data

# A Recent Retrospective Paper [TCAD'19]

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

IEEE Transactions on Computer-Aided Design of Integrated

Circuits and Systems (TCAD) Special Issue on Top Picks in Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

# RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> §ETH Zürich <sup>‡</sup>Carnegie Mellon University

SAFARI 119

# Computer Architecture

Lecture 3a: Memory Trends, Challenges, Opportunities

Prof. Onur Mutlu

ETH Zürich

Fall 2019

6 Soptombor 2010

26 September 2019

# Backup Slides

# Readings, Videos, Reference Materials

# Accelerated Memory Course (~6.5 hours)

#### ACACES 2018

- Memory Systems and Memory-Centric Computing Systems

- Taught by Onur Mutlu July 9-13, 2018

- □ ~6.5 hours of lectures

- Website for the Course including Videos, Slides, Papers

- https://safari.ethz.ch/memory\_systems/ACACES2018/

- https://www.youtube.com/playlist?list=PL5Q2soXY2Zi-HXxomthrpDpMJm05P6J9x

#### All Papers are at:

- https://people.inf.ethz.ch/omutlu/projects.htm

- Final lecture notes and readings (for all topics)

# Longer Memory Course (~18 hours)

#### Tu Wien 2019

- Memory Systems and Memory-Centric Computing Systems

- Taught by Onur Mutlu June 12-19, 2019

- □ ~18 hours of lectures

- Website for the Course including Videos, Slides, Papers

- https://safari.ethz.ch/memory\_systems/TUWien2019

- https://www.youtube.com/playlist?list=PL5Q2soXY2Zi\_gntM55 VoMlKlw7YrXOhbl

#### All Papers are at:

- https://people.inf.ethz.ch/omutlu/projects.htm

- Final lecture notes and readings (for all topics)

### Some Overview Talks

https://www.youtube.com/watch?v=kgiZISOcGFM&list=PL5Q2soXY2Zi8D 5MGV6EnXEJHnV2YFBJl

### Future Computing Architectures

https://www.youtube.com/watch?v=kgiZlSOcGFM&list=PL5Q2soXY2Zi8D\_5MG V6EnXEJHnV2YFBJl&index=1

### Enabling In-Memory Computation

https://www.youtube.com/watch?v=oHqsNbxgdzM&list=PL5Q2soXY2Zi8D\_5M GV6EnXEJHnV2YFBJl&index=7

### Accelerating Genome Analysis

https://www.youtube.com/watch?v=hPnSmfwu2-A&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=9

### Rethinking Memory System Design

https://www.youtube.com/watch?v=F7xZLNMIY1E&list=PL5Q2soXY2Zi8D\_5MG V6EnXEJHnV2YFBJl&index=3

# Reference Overview Paper I

### Processing Data Where It Makes Sense: Enabling In-Memory Computation

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>b,c</sup>

<sup>a</sup>ETH Zürich

<sup>b</sup>Carnegie Mellon University

<sup>c</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, <a href="Processing Data Where It Makes Sense: Enabling In-Memory">Processing Data Where It Makes Sense: Enabling In-Memory</a>

<a href="Computation">Computation</a>

Invited paper in <u>Microprocessors and Microsystems</u> (**MICPRO**), June 2019. [arXiv version]

SAFARI

# Reference Overview Paper II

# **Enabling the Adoption of Processing-in-Memory: Challenges, Mechanisms, Future Research Directions**

SAUGATA GHOSE, KEVIN HSIEH, AMIRALI BOROUMAND, RACHATA AUSAVARUNGNIRUN

Carnegie Mellon University

ONUR MUTLU

ETH Zürich and Carnegie Mellon University

Saugata Ghose, Kevin Hsieh, Amirali Boroumand, Rachata Ausavarungnirun, Onur Mutlu, "Enabling the Adoption of Processing-in-Memory: Challenges, Mechanisms, Future Research Directions"

Invited Book Chapter, to appear in 2018.

[Preliminary arxiv.org version]

# Reference Overview Paper III

Onur Mutlu and Lavanya Subramanian,

"Research Problems and Opportunities in Memory Systems"

Invited Article in <u>Supercomputing Frontiers and Innovations</u> (**SUPERFRI**), 2014/2015.

Research Problems and Opportunities in Memory Systems

Onur Mutlu<sup>1</sup>, Lavanya Subramanian<sup>1</sup>

# Reference Overview Paper IV

Onur Mutlu,

"The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser"

Invited Paper in Proceedings of the <u>Design, Automation, and Test in</u> <u>Europe Conference</u> (**DATE**), Lausanne, Switzerland, March 2017. [Slides (pptx) (pdf)]

# The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser

Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

https://people.inf.ethz.ch/omutlu

# Reference Overview Paper V

Onur Mutlu,

"Memory Scaling: A Systems Architecture

Perspective"

Technical talk at <u>MemCon 2013</u> (**MEMCON**), Santa Clara, CA, August 2013. [Slides (pptx) (pdf)]

[Video] [Coverage on StorageSearch]

### Memory Scaling: A Systems Architecture Perspective

Onur Mutlu

Carnegie Mellon University

onur@cmu.edu

http://users.ece.cmu.edu/~omutlu/

### Reference Overview Paper VI

Proceedings of the IEEE, Sept. 2017

# Error Characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives

This paper reviews the most recent advances in solid-state drive (SSD) error characterization, mitigation, and data recovery techniques to improve both SSD's reliability and lifetime.

By Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu

# Reference Overview Paper VII

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

<u>IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems</u> (TCAD) Special Issue on Top Picks in Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

# RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> §ETH Zürich <sup>‡</sup>Carnegie Mellon University

SAFARI 132

# Reference Overview Paper VIII

#### A Workload and Programming Ease Driven Perspective of Processing-in-Memory

Saugata Ghose<sup>†</sup> Amirali Boroumand<sup>†</sup> Jeremie S. Kim<sup>†</sup> Juan Gómez-Luna<sup>§</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

Saugata Ghose, Amirali Boroumand, Jeremie S. Kim, Juan Gomez-Luna, and Onur Mutlu, "Processing-in-Memory: A Workload-Driven Perspective"

Invited Article in IBM Journal of Research & Development, Special Issue on Hardware for Artificial Intelligence, to appear in November 2019.

[Preliminary arXiv version]

# Reference Overview Paper IX

Vivek Seshadri and Onur Mutlu, "In-DRAM Bulk Bitwise Execution Engine" Invited Book Chapter in Advances in Computers, to appear in 2020.

[Preliminary arXiv version]

### In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

# Related Videos and Course Materials (I)

- Undergraduate Computer Architecture Course Lecture

Videos (2015, 2014, 2013)

- Undergraduate Computer Architecture Course

Materials (2015, 2014, 2013)

- Graduate Computer Architecture Course Lecture

Videos (2018, 2017, 2015, 2013)

- Graduate Computer Architecture Course

Materials (2018, 2017, 2015, 2013)

- Parallel Computer Architecture Course Materials (Lecture Videos)

# Related Videos and Course Materials (II)

- Freshman Digital Circuits and Computer Architecture

Course Lecture Videos (2018, 2017)

- Freshman Digital Circuits and Computer Architecture

Course Materials (2018)

- Memory Systems Short Course Materials

(Lecture Video on Main Memory and DRAM Basics)

# Some Open Source Tools (I)

- Rowhammer Program to Induce RowHammer Errors

- https://github.com/CMU-SAFARI/rowhammer

- Ramulator Fast and Extensible DRAM Simulator

- https://github.com/CMU-SAFARI/ramulator

- MemSim Simple Memory Simulator

- https://github.com/CMU-SAFARI/memsim

- NOCulator Flexible Network-on-Chip Simulator

- https://github.com/CMU-SAFARI/NOCulator

- SoftMC FPGA-Based DRAM Testing Infrastructure

- https://github.com/CMU-SAFARI/SoftMC

- Other open-source software from my group

- https://github.com/CMU-SAFARI/

- http://www.ece.cmu.edu/~safari/tools.html

# Some Open Source Tools (II)

- MQSim A Fast Modern SSD Simulator

- https://github.com/CMU-SAFARI/MQSim

- Mosaic GPU Simulator Supporting Concurrent Applications

- https://github.com/CMU-SAFARI/Mosaic

- IMPICA Processing in 3D-Stacked Memory Simulator

- https://github.com/CMU-SAFARI/IMPICA

- SMLA Detailed 3D-Stacked Memory Simulator

- https://github.com/CMU-SAFARI/SMLA

- HWASim Simulator for Heterogeneous CPU-HWA Systems

- https://github.com/CMU-SAFARI/HWASim

- Other open-source software from my group

- https://github.com/CMU-SAFARI/

- http://www.ece.cmu.edu/~safari/tools.html

# More Open Source Tools (III)

- A lot more open-source software from my group

- https://github.com/CMU-SAFARI/

- http://www.ece.cmu.edu/~safari/tools.html

# Referenced Papers

All are available at

https://people.inf.ethz.ch/omutlu/projects.htm

http://scholar.google.com/citations?user=7XyGUGkAAAAJ&hl=en

https://people.inf.ethz.ch/omutlu/acaces2018.html

# Ramulator: A Fast and Extensible DRAM Simulator

[IEEE Comp Arch Letters'15]

### Ramulator Motivation

- DRAM and Memory Controller landscape is changing

- Many new and upcoming standards

- Many new controller designs

- A fast and easy-to-extend simulator is very much needed

| Segment     | DRAM Standards & Architectures                                                                                                                                                                                               |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Commodity   | DDR3 (2007) [14]; DDR4 (2012) [18]                                                                                                                                                                                           |

| Low-Power   | LPDDR3 (2012) [17]; LPDDR4 (2014) [20]                                                                                                                                                                                       |

| Graphics    | GDDR5 (2009) [15]                                                                                                                                                                                                            |

| Performance | eDRAM [28], [32]; RLDRAM3 (2011) [29]                                                                                                                                                                                        |

| 3D-Stacked  | WIO (2011) [16]; WIO2 (2014) [21]; MCDRAM (2015) [13];<br>HBM (2013) [19]; HMC1.0 (2013) [10]; HMC1.1 (2014) [11]                                                                                                            |

| Academic    | SBA/SSA (2010) [38]; Staged Reads (2012) [8]; RAIDR (2012) [27]; SALP (2012) [24]; TL-DRAM (2013) [26]; RowClone (2013) [37]; Half-DRAM (2014) [39]; Row-Buffer Decoupling (2014) [33]; SARP (2014) [6]; AL-DRAM (2015) [25] |

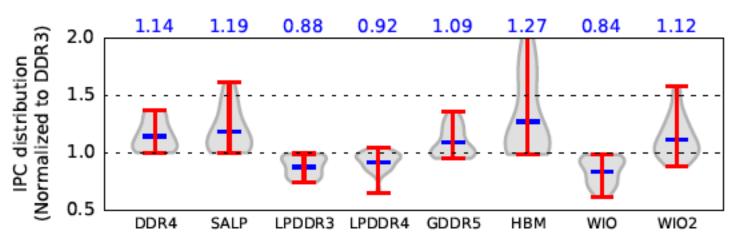

### Ramulator

- Provides out-of-the box support for many DRAM standards:

- DDR3/4, LPDDR3/4, GDDR5, WIO1/2, HBM, plus new proposals (SALP, AL-DRAM, TLDRAM, RowClone, and SARP)

- ~2.5X faster than fastest open-source simulator

- Modular and extensible to different standards

| Simulator   | Cycles (10 <sup>6</sup> ) |        | Runtime (sec.) |        | Reg/sec (10 <sup>3</sup> ) |        | Memory  |  |

|-------------|---------------------------|--------|----------------|--------|----------------------------|--------|---------|--|

| (clang -03) | Random                    | Stream | Random         | Stream | Random                     | Stream | (MB)    |  |

| Ramulator   | 652                       | 411    | 752            | 249    | 133                        | 402    | 2.1     |  |

| DRAMSim2    | 645                       | 413    | 2,030          | 876    | 49                         | 114    | 1.2     |  |

| USIMM       | 661                       | 409    | 1,880          | 750    | 53                         | 133    | 4.5     |  |

| DrSim       | 647                       | 406    | 18,109         | 12,984 | 6                          | 8      | 1.6     |  |

| NVMain      | 666                       | 413    | 6,881          | 5,023  | 15                         | 20     | 4,230.0 |  |

Table 3. Comparison of five simulators using two traces

### Case Study: Comparison of DRAM Standards

| Standard          | Rate<br>(MT/s) | Timing<br>(CL-RCD-RP) | Data-Bus<br>(Width×Chan.) | Rank-per-Chan | BW<br>(GB/s) |

|-------------------|----------------|-----------------------|---------------------------|---------------|--------------|

| DDR3              | 1,600          | 11-11-11              | 64-bit × 1                | 1             | 11.9         |

| DDR4              | 2,400          | 16-16-16              | $64$ -bit $\times 1$      | 1             | 17.9         |

| SALP <sup>†</sup> | 1,600          | 11-11-11              | $64$ -bit $\times 1$      | 1             | 11.9         |

| LPDDR3            | 1,600          | 12-15-15              | $64$ -bit $\times 1$      | 1             | 11.9         |

| LPDDR4            | 2,400          | 22-22-22              | $32$ -bit $\times 2^*$    | 1             | 17.9         |

| GDDR5 [12]        | 6,000          | 18-18-18              | $64$ -bit $\times 1$      | 1             | 44.7         |

| HBM               | 1,000          | 7-7-7                 | $128$ -bit $\times$ $8$ * | 1             | 119.2        |

| WIO               | 266            | 7-7-7                 | $128$ -bit $\times 4^*$   | 1             | 15.9         |

| WIO2              | 1,066          | 9-10-10               | $128$ -bit $\times$ $8*$  | 1             | 127.2        |

Across 22 workloads, simple CPU model

Figure 2. Performance comparison of DRAM standards

# Ramulator Paper and Source Code

- Yoongu Kim, Weikun Yang, and Onur Mutlu,

"Ramulator: A Fast and Extensible DRAM Simulator"

IEEE Computer Architecture Letters (CAL), March 2015.

[Source Code]

- Source code is released under the liberal MIT License

- https://github.com/CMU-SAFARI/ramulator

### Ramulator: A Fast and Extensible DRAM Simulator

Yoongu Kim<sup>1</sup> Weikun Yang<sup>1,2</sup> Onur Mutlu<sup>1</sup>

<sup>1</sup>Carnegie Mellon University <sup>2</sup>Peking University

# Optional Assignment

- Review the Ramulator paper

- Email me your review (<u>omutlu@gmail.com</u>)

- Download and run Ramulator

- Compare DDR3, DDR4, SALP, HBM for the libquantum benchmark (provided in Ramulator repository)

- Email me your report (<u>omutlu@gmail.com</u>)

This will help you get into memory systems research

# End of Backup Slides