## Computer Architecture

Lecture 6b: Computation in Memory I

Prof. Onur Mutlu

ETH Zürich

Fall 2019

4 October 2019

#### Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Minimally Changing Memory Chips

- Exploiting 3D-Stacked Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

#### Three Key Systems Trends

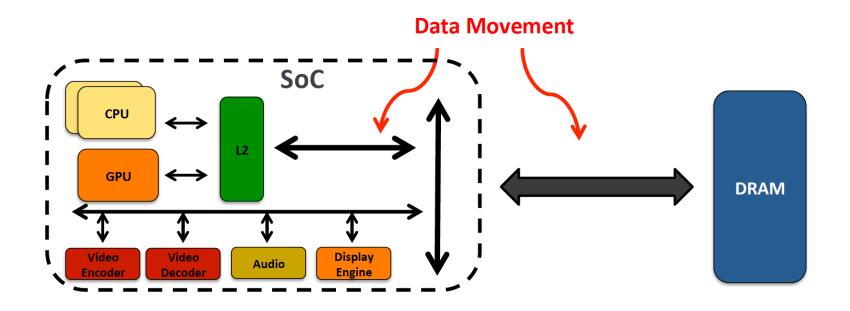

#### 1. Data access is a major bottleneck

Applications are increasingly data hungry

#### 2. Energy consumption is a key limiter

#### 3. Data movement energy dominates compute

Especially true for off-chip to on-chip movement

#### Observation and Opportunity

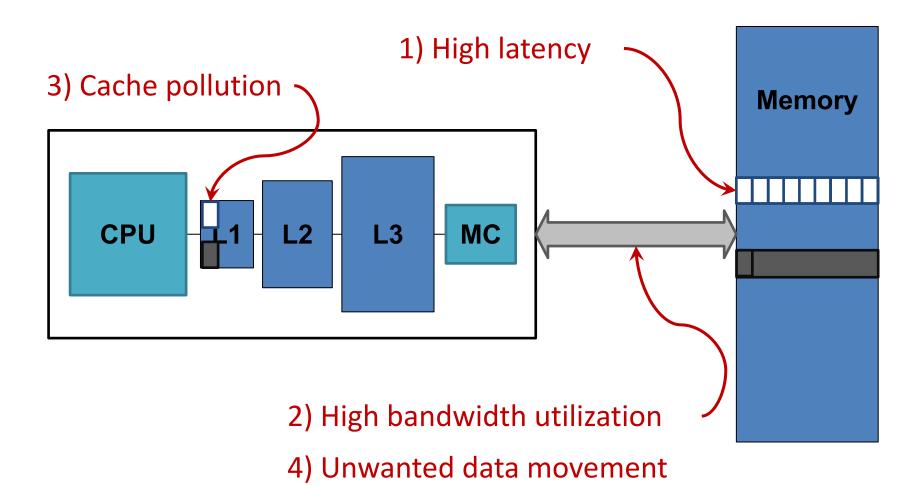

- High latency and high energy caused by data movement

- Long, energy-hungry interconnects

- Energy-hungry electrical interfaces

- Movement of large amounts of data

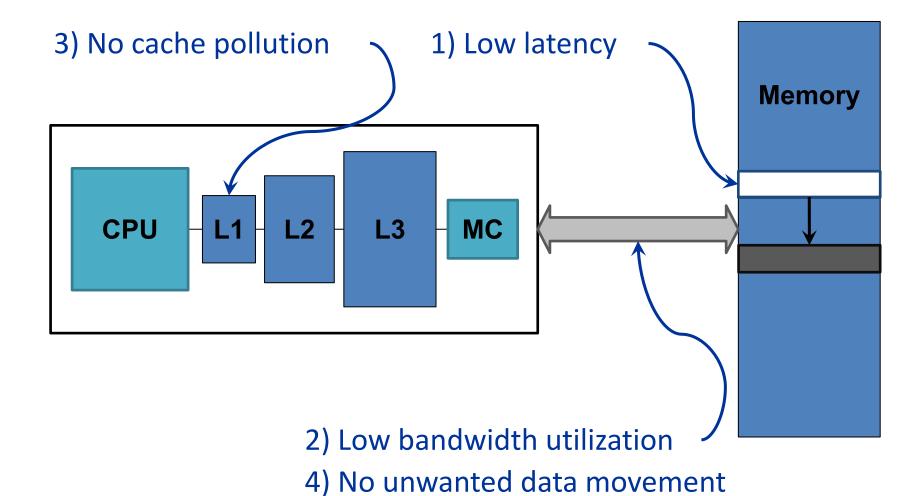

- Opportunity: Minimize data movement by performing computation directly (near) where the data resides

- Processing in memory (PIM)

- In-memory computation/processing

- Near-data processing (NDP)

- General concept applicable to any data storage & movement unit (caches, SSDs, main memory, network, controllers)

#### Four Key Issues in Future Platforms

Fundamentally Secure/Reliable/Safe Architectures

- Fundamentally Energy-Efficient Architectures

- Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency Architectures

Architectures for Genomics, Medicine, Health

#### Maslow's (Human) Hierarchy of Needs, Revisited

Maslow, "A Theory of Human Motivation," Psychological Review, 1943.

Maslow, "Motivation and Personality," Book, 1954-1970.

#### Do We Want This?

7

#### Or This?

**SAFARI**

8

#### Challenge and Opportunity for Future

# High Performance, Energy Efficient, Sustainable

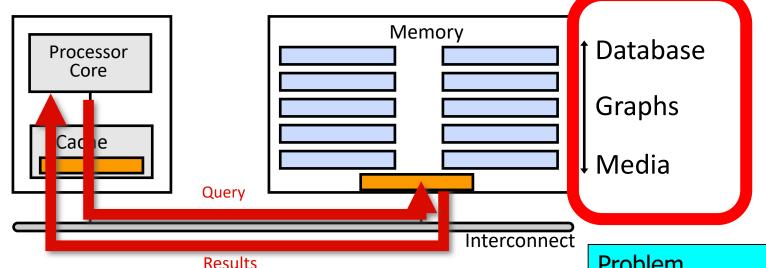

#### The Problem

Data access is the major performance and energy bottleneck

# Our current design principles cause great energy waste

(and great performance loss)

# Processing of data is performed far away from the data

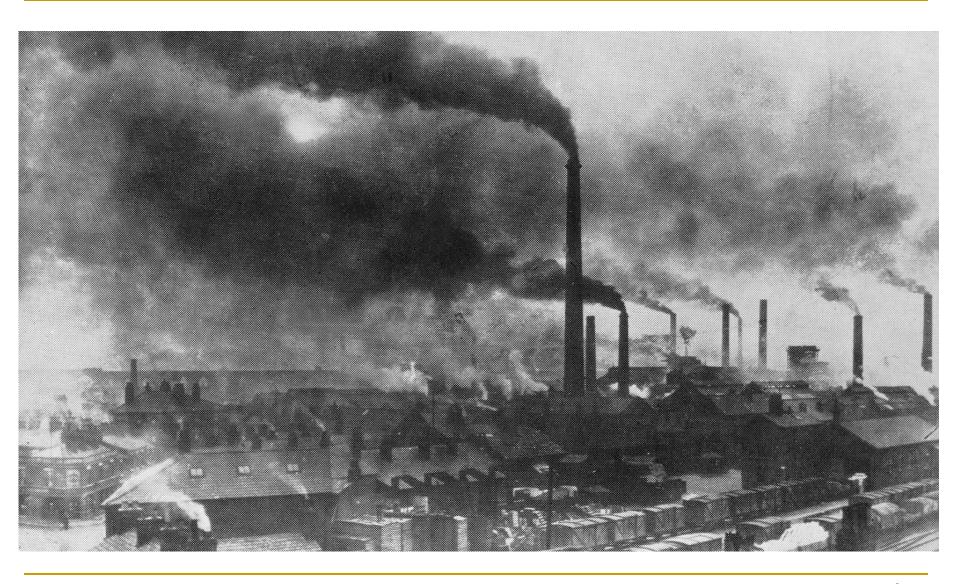

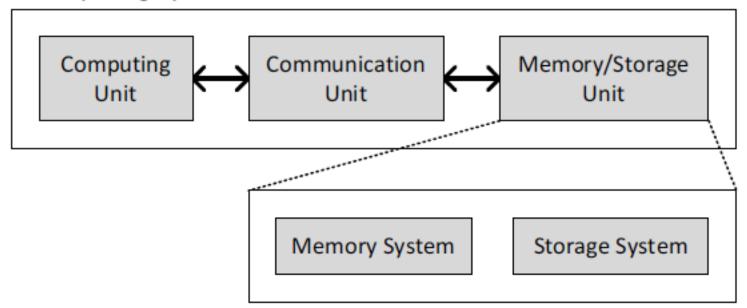

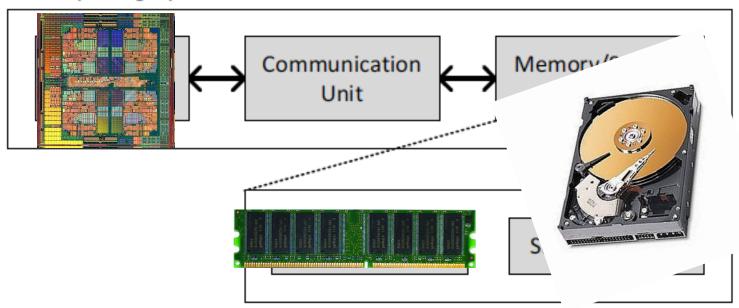

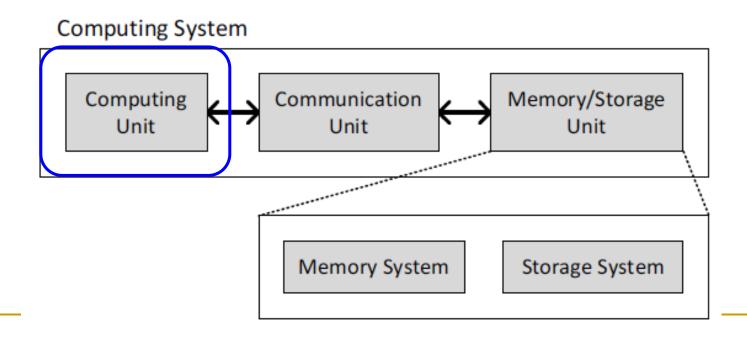

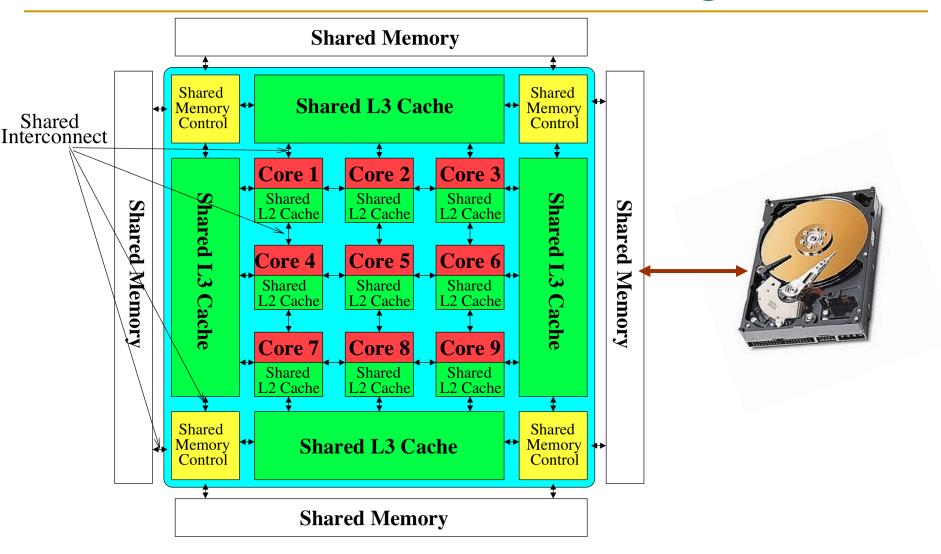

#### A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### Computing System

### A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### Computing System

#### Today's Computing Systems

- Are overwhelmingly processor centric

- All data processed in the processor → at great system cost

- Processor is heavily optimized and is considered the master

- Data storage units are dumb and are largely unoptimized (except for some that are on the processor die)

I expect that over the coming decade memory subsystem design will be the *only* important design issue for microprocessors.

"It's the Memory, Stupid!" (Richard Sites, MPR, 1996)

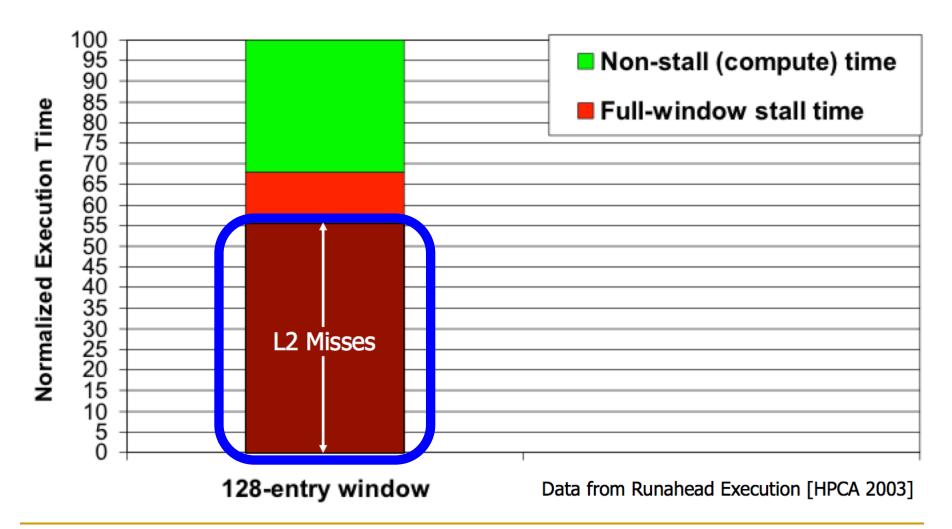

### The Performance Perspective

Onur Mutlu, Jared Stark, Chris Wilkerson, and Yale N. Patt,

"Runahead Execution: An Alternative to Very Large Instruction

Windows for Out-of-order Processors"

Proceedings of the 9th International Symposium on High-Performance

Computer Architecture (HPCA), pages 129-140, Anaheim, CA, February

2003. Slides (pdf)

#### Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors

Onur Mutlu § Jared Stark † Chris Wilkerson ‡ Yale N. Patt §

§ECE Department

The University of Texas at Austin

{onur,patt}@ece.utexas.edu

†Microprocessor Research Intel Labs jared.w.stark@intel.com

‡Desktop Platforms Group Intel Corporation chris.wilkerson@intel.com

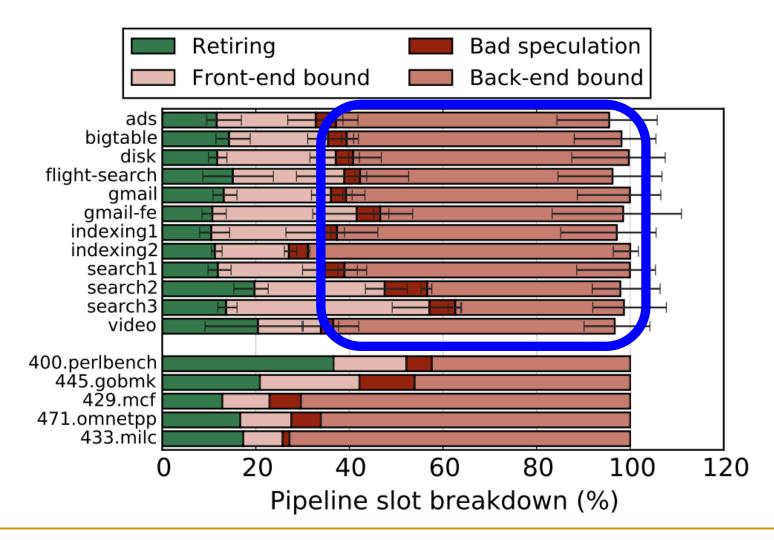

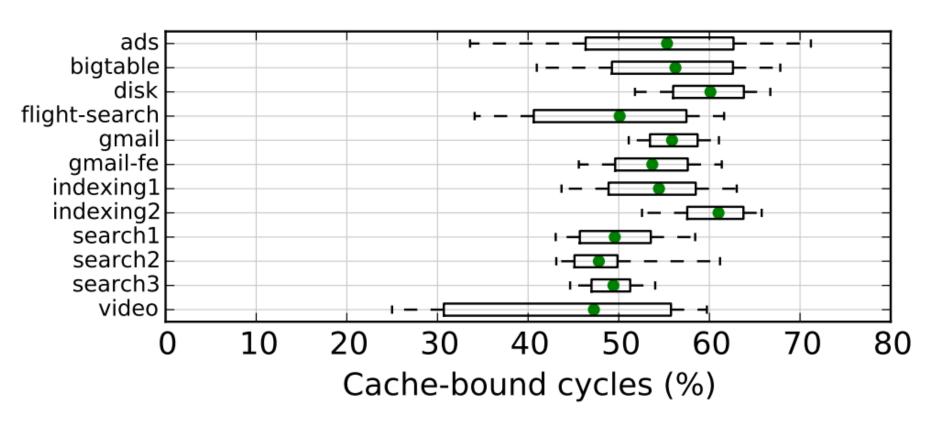

#### The Performance Perspective (Today)

All of Google's Data Center Workloads (2015):

#### The Performance Perspective (Today)

All of Google's Data Center Workloads (2015):

Figure 11: Half of cycles are spent stalled on caches.

#### Perils of Processor-Centric Design

- Grossly-imbalanced systems

- Processing done only in one place

- Everything else just stores and moves data: data moves a lot

- → Energy inefficient

- → Low performance

- → Complex

- Overly complex and bloated processor (and accelerators)

- To tolerate data access from memory

- Complex hierarchies and mechanisms

- → Energy inefficient

- → Low performance

- → Complex

#### Perils of Processor-Centric Design

Most of the system is dedicated to storing and moving data

#### The Energy Perspective

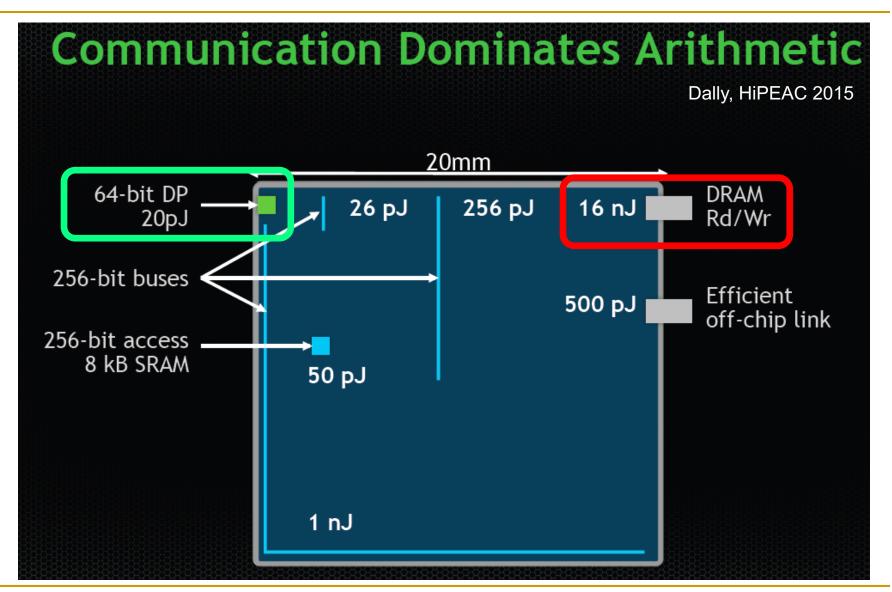

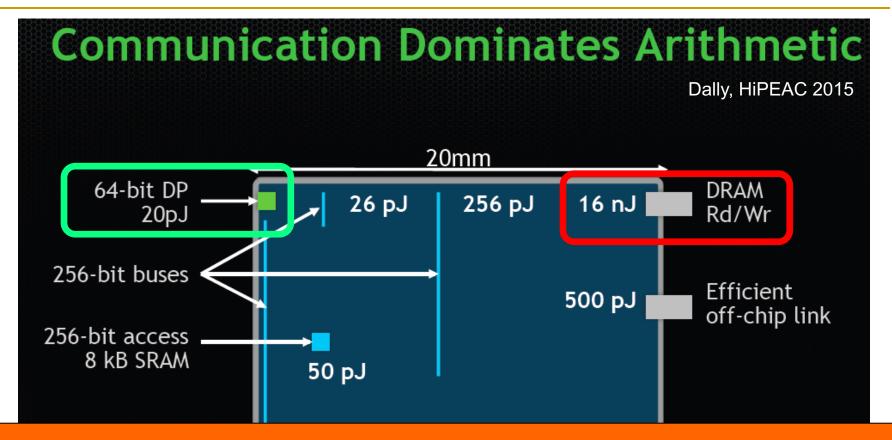

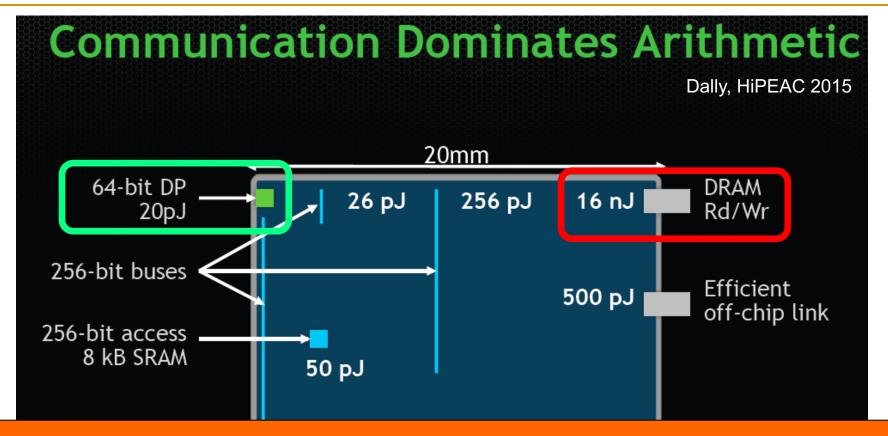

#### Data Movement vs. Computation Energy

A memory access consumes ~100-1000X the energy of a complex addition

#### Data Movement vs. Computation Energy

- Data movement is a major system energy bottleneck

- Comprises 41% of mobile system energy during web browsing [2]

- Costs ~115 times as much energy as an ADD operation [1, 2]

[1]: Reducing data Movement Energy via Online Data Clustering and Encoding (MICRO'16)

[2]: Quantifying the energy cost of data movement for emerging smart phone workloads on mobile platforms (IISWC'14)

#### Energy Waste in Mobile Devices

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the 23rd International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Williamsburg, VA, USA, March 2018.

# 62.7% of the total system energy is spent on data movement

#### Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup> Saugata Ghose<sup>1</sup> Youngsok Kim<sup>2</sup> Rachata Ausavarungnirun<sup>1</sup> Eric Shiu<sup>3</sup> Rahul Thakur<sup>3</sup> Daehyun Kim<sup>4,3</sup> Aki Kuusela<sup>3</sup> Allan Knies<sup>3</sup> Parthasarathy Ranganathan<sup>3</sup> Onur Mutlu<sup>5,1</sup>

SAFARI

#### We Do Not Want to Move Data!

A memory access consumes ~100-1000X the energy of a complex addition

#### We Need A Paradigm Shift To ...

Enable computation with minimal data movement

Compute where it makes sense (where data resides)

Make computing architectures more data-centric

#### Goal: Processing Inside Memory

- Many questions ... How do we design the:

- compute-capable memory & controllers?

- processor chip and in-memory units?

- software and hardware interfaces?

- system software, compilers, languages?

- algorithms and theoretical foundations?

**Problem**

Aigorithm

Program/Language

System Software

SW/HW Interface

Micro-architecture

Logic

Electrons

#### Why In-Memory Computation Today?

- Pull from Systems and Applications

- Data access is a major system and application bottleneck

- Systems are energy limited

- Data movement much more energy-hungry than computation

# We Need to Think Differently from the Past Approaches

#### Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Minimally Changing Memory Chips

- Exploiting 3D-Stacked Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

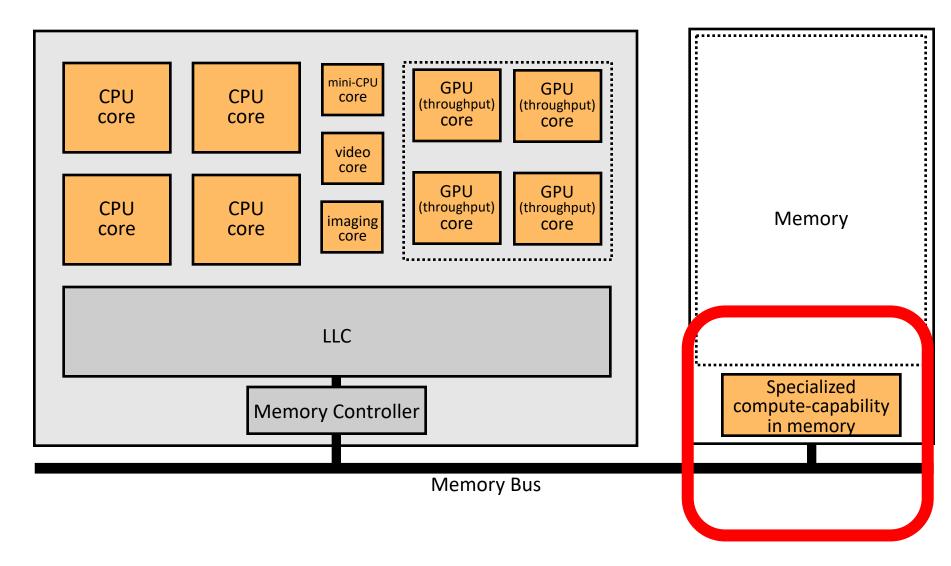

# Processing in Memory: Two Approaches

- 1. Minimally changing memory chips

- 2. Exploiting 3D-stacked memory

#### Approach 1: Minimally Changing DRAM

- DRAM has great capability to perform bulk data movement and computation internally with small changes

- Can exploit internal connectivity to move data

- Can exploit analog computation capability

- **-** ...

- Examples: RowClone, In-DRAM AND/OR, Gather/Scatter DRAM

- RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data (Seshadri et al., MICRO 2013)

- Fast Bulk Bitwise AND and OR in DRAM (Seshadri et al., IEEE CAL 2015)

- Gather-Scatter DRAM: In-DRAM Address Translation to Improve the Spatial Locality of Non-unit Strided Accesses (Seshadri et al., MICRO 2015)

- "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity

DRAM Technology" (Seshadri et al., MICRO 2017)

#### Starting Simple: Data Copy and Initialization

## Bulk Data Copy

# **Bulk Data Initialization**

## Bulk Data Copy and Initialization

## The Impact of Architectural Trends on Operating System Performance

Mendel Rosenblum, Edouard Bugnion, Stephen Alan Herrod,

#### Hardware Support for Bulk Data Movement in Server Platforms

Li Zhao<sup>†</sup>, Ravi Iyer<sup>‡</sup> Srihari Makineni<sup>‡</sup>, Laxmi Bhuyan<sup>†</sup> and Don Newell<sup>‡</sup>

Department of Computer Science and Engineering, University of California, Riverside, CA 92521

Email: {zhao, bhuyan}@cs.ucr.edu

Communications Technology Lab Intel-Communications Technology Lab Intel-Communications

#### TM

#### Architecture Support for Improving Bulk Memory Copying and Initialization Performance

Xiaowei Jiang, Yan Solihin

Dept. of Electrical and Computer Engineering

North Carolina State University

Raleigh, USA

Li Zhao, Ravishankar Iyer Intel Labs Intel Corporation Hillsboro, USA

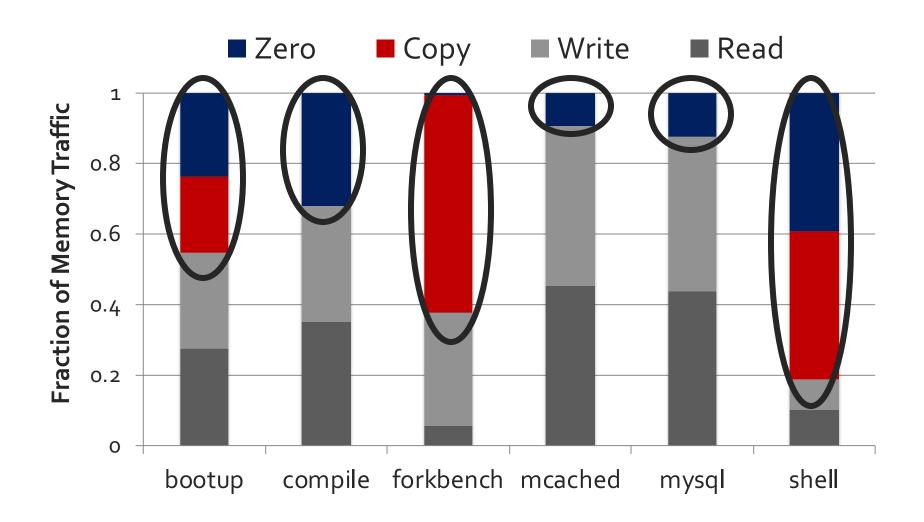

#### Starting Simple: Data Copy and Initialization

memmove & memcpy: 5% cycles in Google's datacenter [Kanev+ ISCA'15]

**Page Migration**

### Today's Systems: Bulk Data Copy

1046ns, 3.6uJ (for 4KB page copy via DMA)

#### Future Systems: In-Memory Copy

1046ns, 3.6uJ

→ 90ns, 0.04uJ

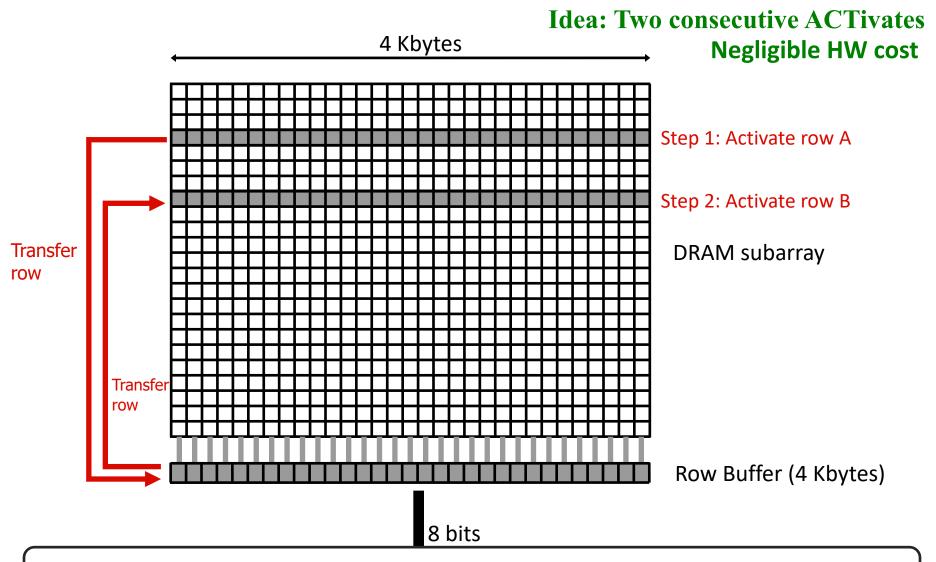

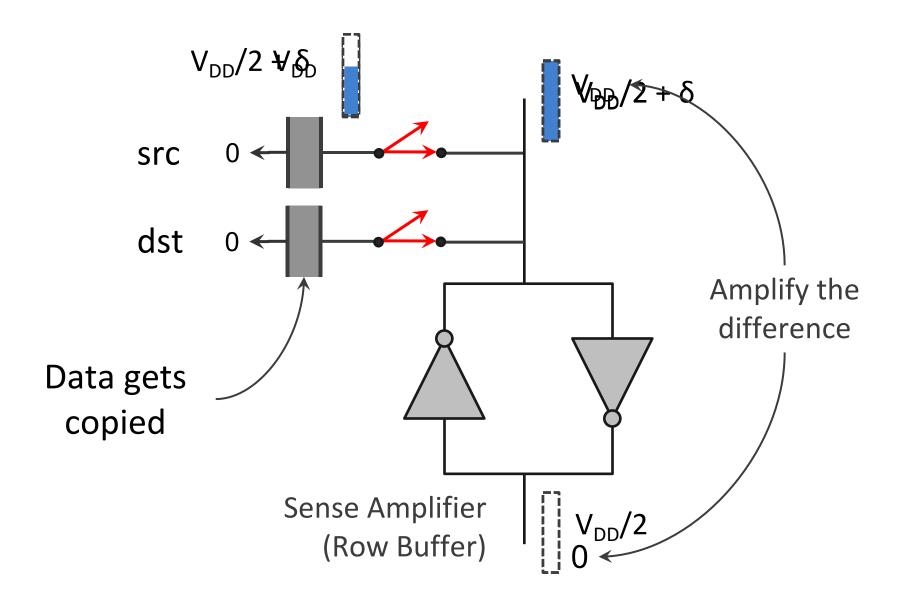

#### RowClone: In-DRAM Row Copy

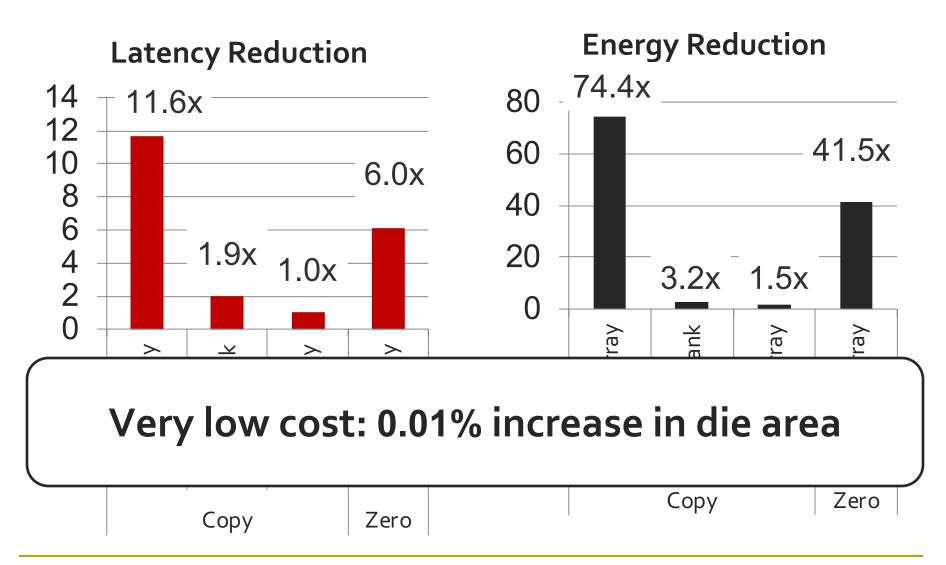

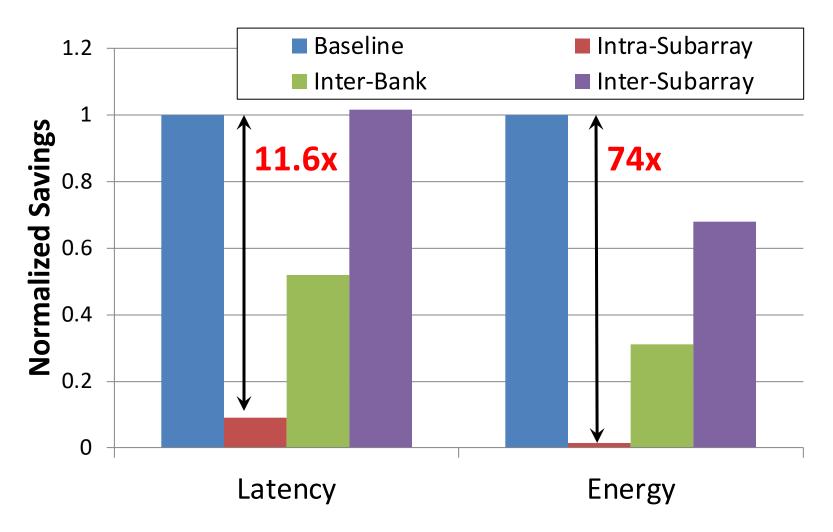

11.6X latency reduction, 74X energy reduction

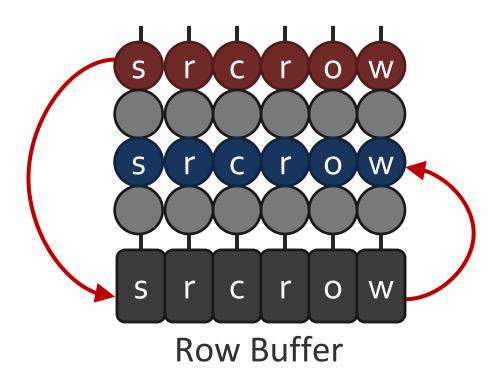

#### RowClone: Intra-Subarray

#### RowClone: Intra-Subarray (II)

- 1. Activate src row (copy data from src to row buffer)

- 2. **Activate** dst row (disconnect src from row buffer, connect dst copy data from row buffer to dst)

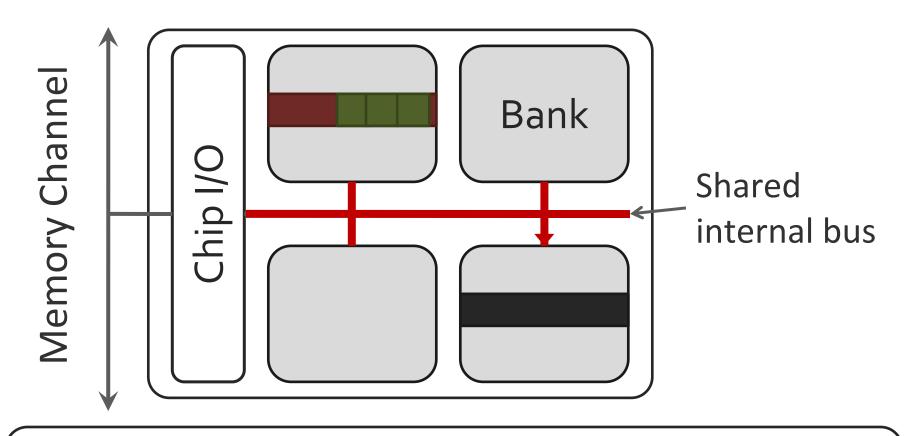

#### RowClone: Inter-Bank

Overlap the latency of the read and the write 1.9X latency reduction, 3.2X energy reduction

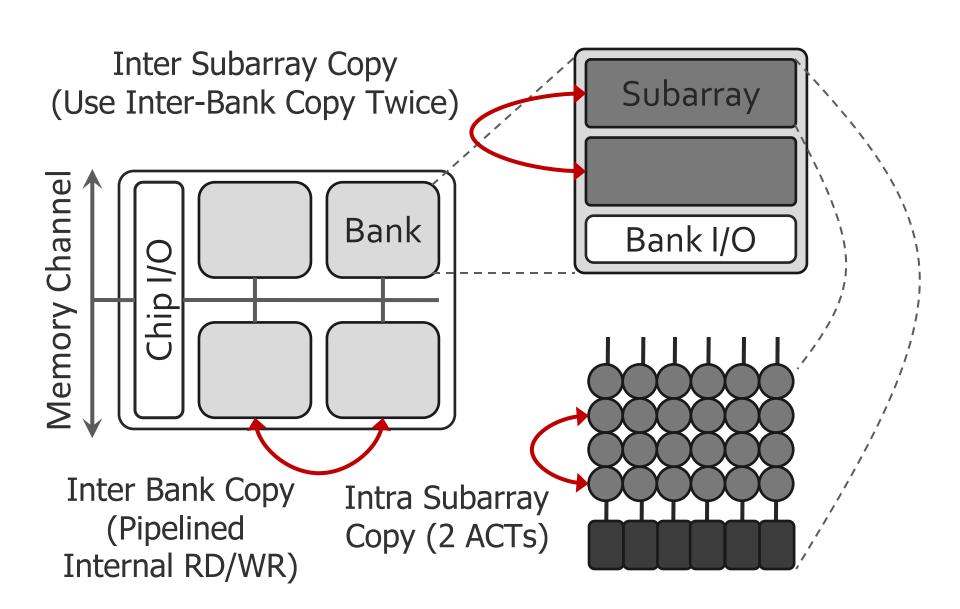

#### Generalized RowClone

#### 0.01% area cost

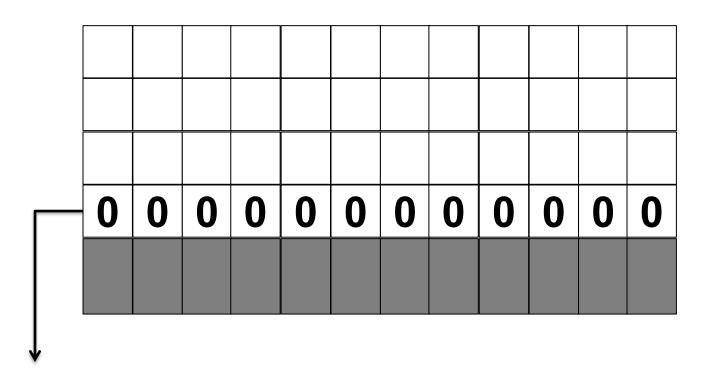

#### RowClone: Fast Row Initialization

Fix a row at Zero (0.5% loss in capacity)

#### RowClone: Bulk Initialization

- Initialization with arbitrary data

- Initialize one row

- Copy the data to other rows

- Zero initialization (most common)

- Reserve a row in each subarray (always zero)

- Copy data from reserved row (FPM mode)

- 6.0X lower latency, 41.5X lower DRAM energy

- □ 0.2% loss in capacity

#### RowClone: Latency & Energy Benefits

#### Copy and Initialization in Workloads

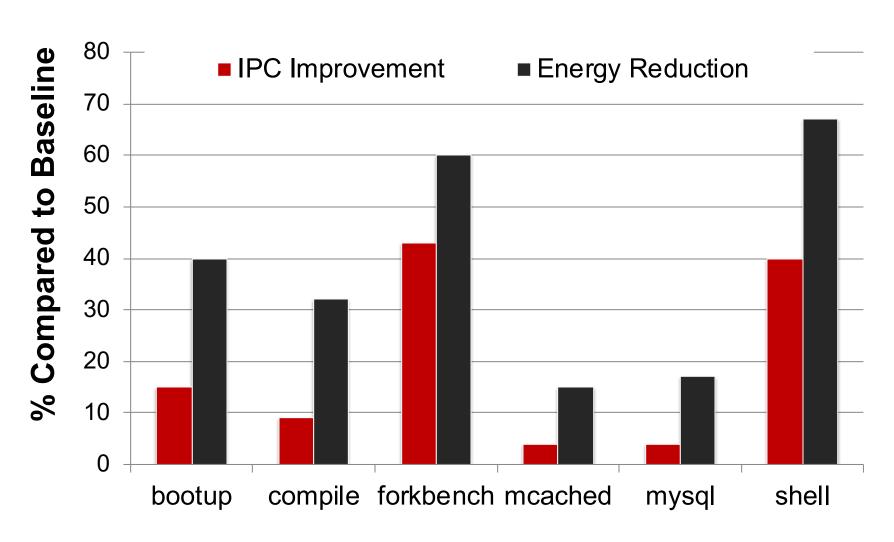

#### RowClone: Application Performance

#### End-to-End System Design

**Application**

**Operating System**

ISA

Microarchitecture

DRAM (RowClone)

How to communicate occurrences of bulk copy/initialization across layers?

How to ensure cache coherence?

How to maximize latency and energy savings?

How to handle data reuse?

#### RowClone: Latency and Energy Savings

Seshadri et al., "RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data," MICRO 2013.

#### More on RowClone

Vivek Seshadri, Yoongu Kim, Chris Fallin, Donghyuk Lee, Rachata

Ausavarungnirun, Gennady Pekhimenko, Yixin Luo, Onur Mutlu, Michael A.

Kozuch, Phillip B. Gibbons, and Todd C. Mowry,

"RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization"

Proceedings of the <u>46th International Symposium on Microarchitecture</u> (**MICRO**), Davis, CA, December 2013. [<u>Slides (pptx) (pdf)</u>] [<u>Lightning Session Slides (pptx) (pdf)</u>] [<u>Poster (pptx) (pdf)</u>]

### RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization

Vivek Seshadri Yoongu Kim Chris Fallin\* Donghyuk Lee vseshadr@cs.cmu.edu yoongukim@cmu.edu cfallin@c1f.net donghyuk1@cmu.edu

Rachata Ausavarungnirun Gennady Pekhimenko Yixin Luo rachata@cmu.edu gpekhime@cs.cmu.edu yixinluo@andrew.cmu.edu

Onur Mutlu Phillip B. Gibbons† Michael A. Kozuch† Todd C. Mowry onur@cmu.edu phillip.b.gibbons@intel.com michael.a.kozuch@intel.com tcm@cs.cmu.edu

Carnegie Mellon University †Intel Pittsburgh

#### Memory as an Accelerator

Memory similar to a "conventional" accelerator

#### Computer Architecture

Lecture 6b: Computation in Memory I

Prof. Onur Mutlu

ETH Zürich

Fall 2019

4 October 2019

### We Did Not Cover The Later Slides. They Are For Your Benefit.

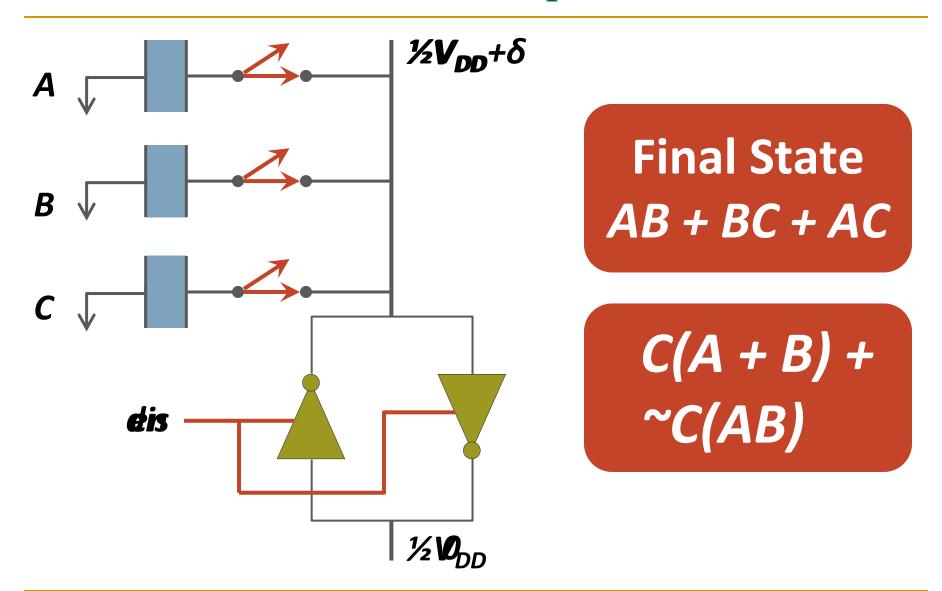

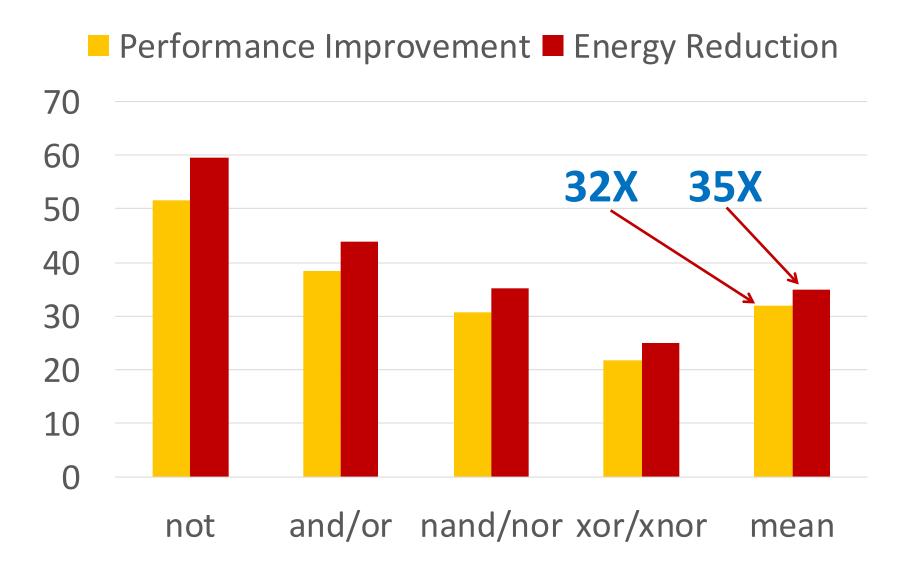

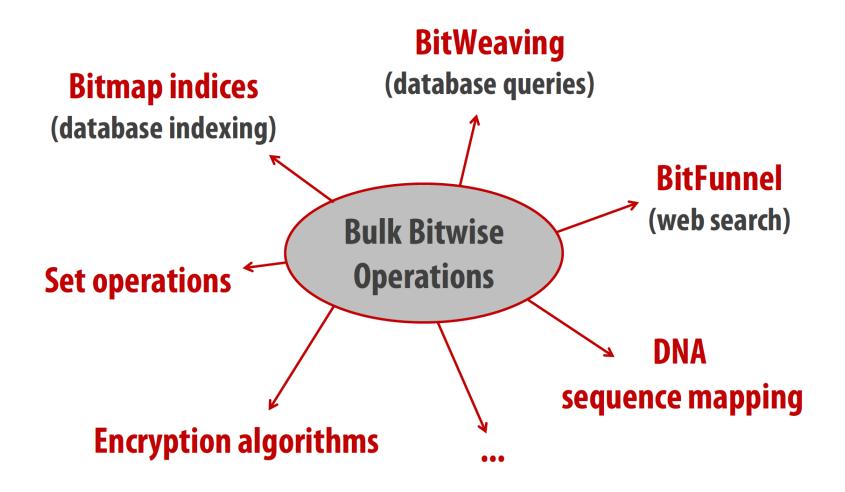

#### In-Memory Bulk Bitwise Operations

- We can support in-DRAM COPY, ZERO, AND, OR, NOT, MAJ

- At low cost

- Using analog computation capability of DRAM

- Idea: activating multiple rows performs computation

- 30-60X performance and energy improvement

- Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology," MICRO 2017.

- New memory technologies enable even more opportunities

- Memristors, resistive RAM, phase change mem, STT-MRAM, ...

- Can operate on data with minimal movement

#### In-DRAM AND/OR: Triple Row Activation

#### In-DRAM Bulk Bitwise AND/OR Operation

- BULKAND A, B  $\rightarrow$  C

- Semantics: Perform a bitwise AND of two rows A and B and store the result in row C

- R0 reserved zero row, R1 reserved one row

- D1, D2, D3 Designated rows for triple activation

- 1. RowClone A into D1

- 2. RowClone B into D2

- 3. RowClone R0 into D3

- 4. ACTIVATE D1,D2,D3

- 5. RowClone Result into C

#### More on In-DRAM Bulk AND/OR

Vivek Seshadri, Kevin Hsieh, Amirali Boroumand, Donghyuk Lee, Michael A. Kozuch, Onur Mutlu, Phillip B. Gibbons, and Todd C. Mowry,

"Fast Bulk Bitwise AND and OR in DRAM"

IEEE Computer Architecture Letters (CAL), April 2015.

#### Fast Bulk Bitwise AND and OR in DRAM

Vivek Seshadri\*, Kevin Hsieh\*, Amirali Boroumand\*, Donghyuk Lee\*, Michael A. Kozuch<sup>†</sup>, Onur Mutlu\*, Phillip B. Gibbons<sup>†</sup>, Todd C. Mowry\*

\*Carnegie Mellon University <sup>†</sup>Intel Pittsburgh

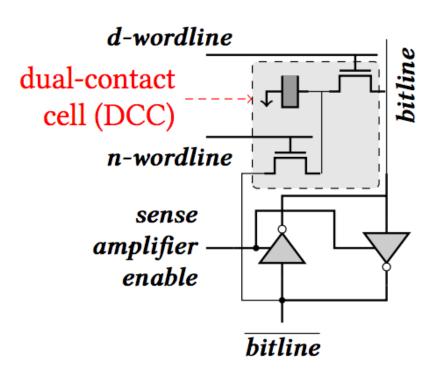

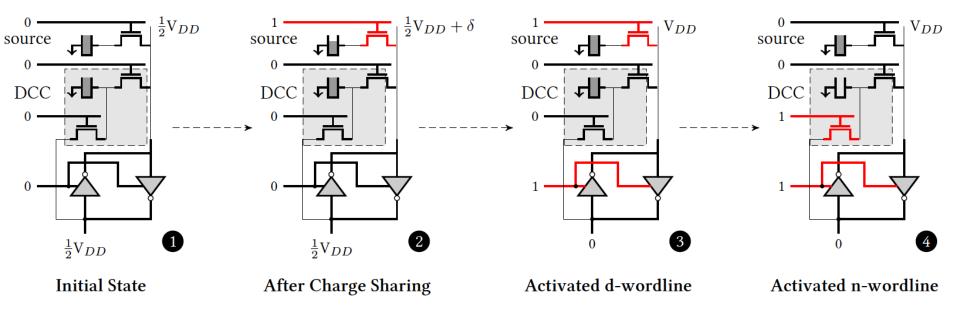

#### In-DRAM NOT: Dual Contact Cell

Figure 5: A dual-contact cell connected to both ends of a sense amplifier

Idea:

Feed the

negated value

in the sense amplifier

into a special row

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

#### In-DRAM NOT Operation

Figure 5: Bitwise NOT using a dual contact capacitor

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

#### Performance: In-DRAM Bitwise Operations

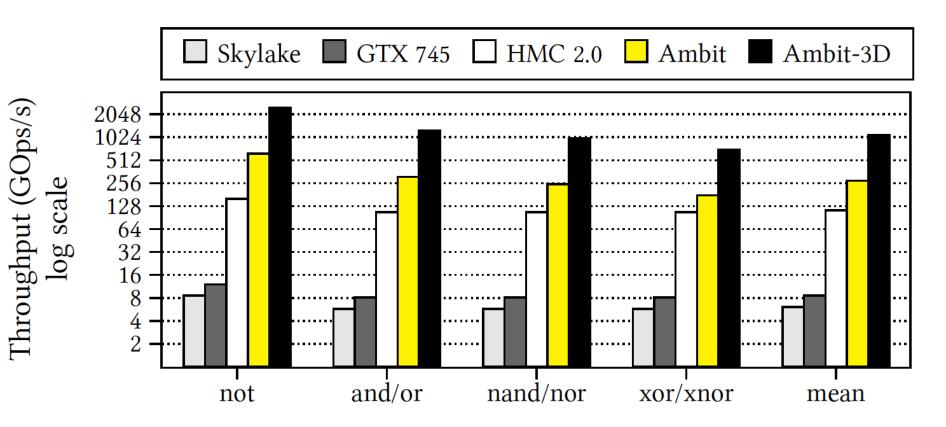

Figure 9: Throughput of bitwise operations on various systems.

#### Energy of In-DRAM Bitwise Operations

|                | Design         | not   | and/or | nand/nor | xor/xnor |

|----------------|----------------|-------|--------|----------|----------|

| DRAM &         | DDR3           | 93.7  | 137.9  | 137.9    | 137.9    |

| Channel Energy | Ambit          | 1.6   | 3.2    | 4.0      | 5.5      |

| (nJ/KB)        | $(\downarrow)$ | 59.5X | 43.9X  | 35.1X    | 25.1X    |

Table 3: Energy of bitwise operations.  $(\downarrow)$  indicates energy reduction of Ambit over the traditional DDR3-based design.

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

#### **Ambit vs. DDR3: Performance and Energy**

#### Bulk Bitwise Operations in Workloads

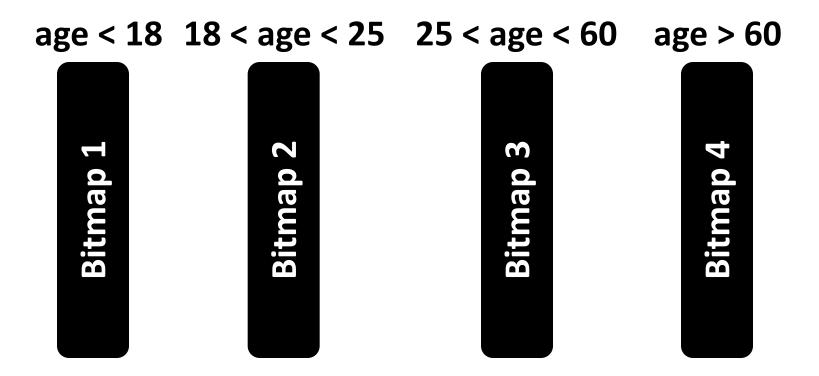

#### Example Data Structure: Bitmap Index

- Alternative to B-tree and its variants

- Efficient for performing range queries and joins

- Many bitwise operations to perform a query

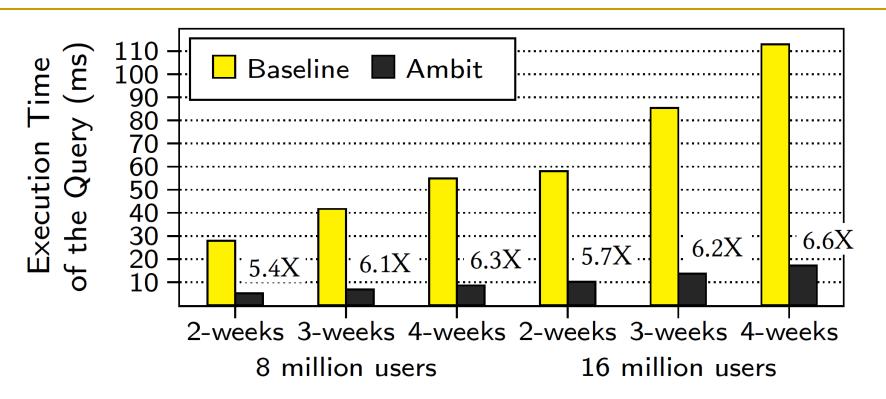

#### Performance: Bitmap Index on Ambit

Figure 10: Bitmap index performance. The value above each bar indicates the reduction in execution time due to Ambit.

>5.4-6.6X Performance Improvement

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

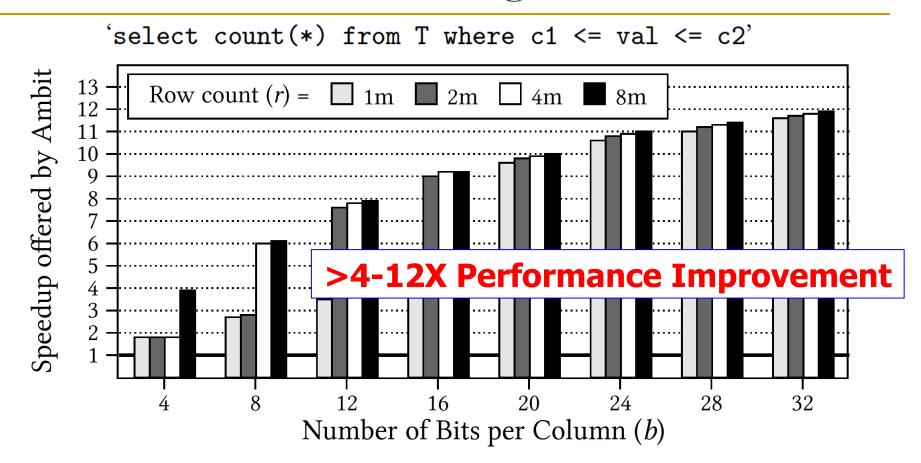

#### Performance: BitWeaving on Ambit

Figure 11: Speedup offered by Ambit over baseline CPU with SIMD for BitWeaving

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

#### More on In-DRAM Bulk AND/OR

Vivek Seshadri, Kevin Hsieh, Amirali Boroumand, Donghyuk Lee, Michael A. Kozuch, Onur Mutlu, Phillip B. Gibbons, and Todd C. Mowry,

"Fast Bulk Bitwise AND and OR in DRAM"

IEEE Computer Architecture Letters (CAL), April 2015.

#### Fast Bulk Bitwise AND and OR in DRAM

Vivek Seshadri\*, Kevin Hsieh\*, Amirali Boroumand\*, Donghyuk Lee\*, Michael A. Kozuch<sup>†</sup>, Onur Mutlu\*, Phillip B. Gibbons<sup>†</sup>, Todd C. Mowry\*

\*Carnegie Mellon University <sup>†</sup>Intel Pittsburgh

#### More on In-DRAM Bitwise Operations

Vivek Seshadri et al., "<u>Ambit: In-Memory Accelerator</u> for Bulk Bitwise Operations Using Commodity DRAM <u>Technology</u>," MICRO 2017.

Ambit: In-Memory Accelerator for Bulk Bitwise Operations

Using Commodity DRAM Technology

```

Vivek Seshadri^{1,5} Donghyuk Lee^{2,5} Thomas Mullins^{3,5} Hasan Hassan^4 Amirali Boroumand^5 Jeremie Kim^{4,5} Michael A. Kozuch^3 Onur Mutlu^{4,5} Phillip B. Gibbons^5 Todd C. Mowry^5

```

$^1$ Microsoft Research India  $^2$ NVIDIA Research  $^3$ Intel  $^4$ ETH Zürich  $^5$ Carnegie Mellon University

#### More on In-DRAM Bulk Bitwise Execution

Vivek Seshadri and Onur Mutlu, "In-DRAM Bulk Bitwise Execution Engine" Invited Book Chapter in Advances in Computers, to appear in 2020.

[Preliminary arXiv version]

#### In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

#### Challenge: Intelligent Memory Device

## Does memory have to be dumb?

#### Challenge and Opportunity for Future

# Computing Architectures with Minimal Data Movement

## A Detour on the Review Process

# Ambit Sounds Good, No?

#### **Paper summary**

## **Review from ISCA 2016**

The paper proposes to extend DRAM to include bulk, bit-wise logical

operations directly between rows within the DRAM.

#### **Strengths**

- Very clever/novel idea.

- Great potential speedup and efficiency gains.

#### Weaknesses

- Probably won't ever be built. Not practical to assume DRAM manufacturers with change DRAM in this way.

## Another Review

#### **Another Review from ISCA 2016**

#### **Strengths**

The proposed mechanisms effectively exploit the operation of the DRAM to perform efficient bitwise operations across entire rows of the DRAM.

#### Weaknesses

This requires a modification to the DRAM that will only help this type of bitwise operation. It seems unlikely that something like that will be adopted.

## Yet Another Review

#### **Yet Another Review from ISCA 2016**

#### Weaknesses

The core novelty of Buddy RAM is almost all circuits-related (by exploiting sense amps). I do not find architectural innovation even though the circuits technique benefits architecturally by mitigating memory bandwidth and relieving cache resources within a subarray. The only related part is the new ISA support for bitwise operations at DRAM side and its induced issue on cache coherence.

# The Reviewer Accountability Problem

# **Acknowle** gments

We thank the reviewers of ISCA 2016/2017, MICRO 2016/2017, and HPCA 2017 for their valuable comments. We

## We Have a Mindset Issue...

- There are many other similar examples from reviews...

- For many other papers...

- And, we are not even talking about JEDEC yet...

- How do we fix the mindset problem?

- By doing more research, education, implementation in alternative processing paradigms

## We need to work on enabling the better future...

## Aside: A Recommended Book

Raj Jain, "The Art of **Computer Systems** Performance Analysis," Wiley, 1991.

WILEY

#### DECISION MAKER'S GAMES

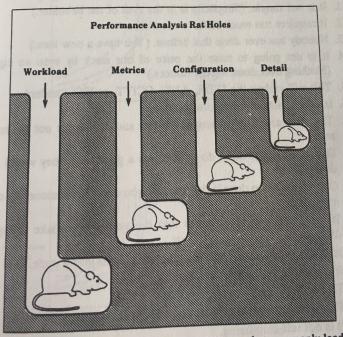

Even if the performance analysis is correctly done and presented, it may not be enough to persuade your audience—the decision makers—to follow your recommendations. The list shown in Box 10.2 is a compilation of reasons for rejection heard at various performance analysis presentations. You can use the list by presenting it immediately and pointing out that the reason for rejection is not new and that the analysis deserves more consideration. Also, the list is helpful in getting the competing proposals rejected!

There is no clear end of an analysis. Any analysis can be rejected simply on the grounds that the problem needs more analysis. This is the first reason listed in Box 10.2. The second most common reason for rejection of an analysis and for endless debate is the workload. Since workloads are always based on the past measurements, their applicability to the current or future environment can always be questioned. Actually workload is one of the four areas of discussion that lead a performance presentation into an endless debate. These "rat holes" and their relative sizes in terms of time consumed are shown in Figure 10.26. Presenting this cartoon at the beginning of a presentation helps to avoid these areas.

Raj Jain, "The Art of Computer Systems Performance Analysis," Wiley, 1991.

FIGURE 10.26 Four issues in performance presentations that commonly lead to endless discussion.

#### Box 10.2 Reasons for Not Accepting the Results of an Analysis

- This needs more analysis.

You need a better understanding of the workload.

- You need a better discovered and provided and solution of the I/O's, packets, jobs, and files are short.

- 4. It improves performance only for short I/O's, packets, jobs, and files, but who cares for the performance of short I/O's, packets, jobs, and files; its the long ones that impact the system.

- 5. It needs too much memory/CPU/bandwidth and memory/CPU/bandwidth isn't free.

- 6. It only saves us memory/CPU/bandwidth and memory/CPU/bandwidth is cheap.

- 7. There is no point in making the networks (similarly, CPUs/disks/...) faster; our CPUs/disks (any component other than the one being discussed) aren't fast enough to use them.

- 8. It improves the performance by a factor of x, but it doesn't really matter at the user level because everything else is so slow.

- 9. It is going to increase the complexity and cost.

- 10. Let us keep it simple stupid (and your idea is not stupid).

- 11. It is not simple. (Simplicity is in the eyes of the beholder.)

- 12. It requires too much state.

- 13. Nobody has ever done that before. (You have a new idea.)

- 14. It is not going to raise the price of our stock by even an eighth. (Nothing ever does, except rumors.)

- 15. This will violate the IEEE, ANSI, CCITT, or ISO standard.

- 16. It may violate some future standard.

- 17. The standard says nothing about this and so it must not be important.

- 18. Our competitors don't do it. If it was a good idea, they would have done it.

- 19. Our competition does it this way and you don't make money by copying others.

- It will introduce randomness into the system and make debugging difficult.

- 21. It is too deterministic; it may lead the system into a cycle.

- 22. It's not interoperable.

- 23. This impacts hardware.

- 24. That's beyond today's technology.

- 23. It is not soil billiain

- 26. Why change—it's working OK.

Raj Jain, "The Art of Computer Systems Performance Analysis," Wiley, 1991.

# Suggestion to Community

# We Need to Fix the Reviewer Accountability Problem

# Main Memory Needs Intelligent Controllers

# Research Community Needs

Accountable Reviewers

# Suggestions to Reviewers

- Be fair; you do not know it all

- Be open-minded; you do not know it all

- Be accepting of diverse research methods: there is no single way of doing research

- Be constructive, not destructive

- Do not have double standards...

#### Do not block or delay scientific progress for non-reasons

# RowClone & Bitwise Ops in Real DRAM Chips

# ComputeDRAM: In-Memory Compute Using Off-the-Shelf DRAMs

Fei Gao feig@princeton.edu Department of Electrical Engineering Princeton University Georgios Tziantzioulis georgios.tziantzioulis@princeton.edu Department of Electrical Engineering Princeton University David Wentzlaff wentzlaf@princeton.edu Department of Electrical Engineering Princeton University

# Pinatubo: RowClone and Bitwise Ops in PCM

# Pinatubo: A Processing-in-Memory Architecture for Bulk Bitwise Operations in Emerging Non-volatile Memories

Shuangchen Li<sup>1</sup>\*, Cong Xu<sup>2</sup>, Qiaosha Zou<sup>1,5</sup>, Jishen Zhao<sup>3</sup>, Yu Lu<sup>4</sup>, and Yuan Xie<sup>1</sup>

University of California, Santa Barbara<sup>1</sup>, Hewlett Packard Labs<sup>2</sup> University of California, Santa Cruz<sup>3</sup>, Qualcomm Inc.<sup>4</sup>, Huawei Technologies Inc.<sup>5</sup> {shuangchenli, yuanxie}ece.ucsb.edu<sup>1</sup>

# Another Example

### Initial RowHammer Reviews

# Disturbance Errors in DRAM: Demonstration, Characterization, and Prevention

Rejected (R2)

863kB Friday 31 May 2013 2:00:53pm PDT

b9bf06021da54cddf4cd0b3565558a181868b972

You are an author of this paper.

+ Abstract + Authors

Review #66A

Review #66B

Review #66C

Review #66D

Review #66E

Review #66F

| OveMer | Nov | WriQua | RevExp |

|--------|-----|--------|--------|

| 1      | 4   | 4      | 4      |

| 5      | 4   | 5      | 3      |

| 2      | 3   | 5      | 4      |

| 1      | 2   | 3      | 4      |

| 4      | 4   | 4      | 3      |

| 2      | 4   | 4      | 3      |

SAFARI

# Missing the Point Reviews from Micro 2013

#### PAPER WEAKNESSES

This is an excellent test methodology paper, but there is no micro-architectural or architectural content.

#### PAPER WEAKNESSES

- Whereas they show disturbance may happen in DRAM array, authors don't show it can be an issue in realistic DRAM usage scenario

- Lacks architectural/microarchitectural impact on the DRAM disturbance analysis

#### PAPER WEAKNESSES

The mechanism investigated by the authors is one of many well known disturb mechanisms. The paper does not discuss the root causes to sufficient depth and the importance of this mechanism compared to others. Overall the length of the sections restating known information is much too long in relation to new work.

# Experimental DRAM Testing Infrastructure

# Tested DRAM Modules

(129 total)

| 16                     | Module                                | Date*          | $Timing^{\dagger}$ |                      | Organization |       | Chip                   |            |                          | Victims-per-Module                     |                                            |                                        | RI <sub>th</sub> (ms) |

|------------------------|---------------------------------------|----------------|--------------------|----------------------|--------------|-------|------------------------|------------|--------------------------|----------------------------------------|--------------------------------------------|----------------------------------------|-----------------------|

| Manufacturer           |                                       | (yy-ww)        | Freq (MT/s)        | t <sub>RC</sub> (ns) | Size (GB)    | Chips | Size (Gb) <sup>‡</sup> | Pins       | Die Version <sup>§</sup> | Average                                | Minimum                                    | Maximum                                | Min                   |

|                        | $A_1$                                 | 10-08          | 1066               | 50.625               | 0.5          | 4     | 1                      | ×16        | В                        | 0                                      | 0                                          | 0                                      | -                     |

|                        | $A_2$                                 | 10-20          | 1066               | 50.625               | 1            | 8     | 1                      | ×8         | F                        | 0                                      | 0                                          | 0                                      | -                     |

|                        | A <sub>3-5</sub>                      | 10-20          | 1066               | 50.625               | 0.5          | 4     | 1                      | ×16        | В                        | 0                                      | 0                                          | 0                                      | -                     |

|                        | A <sub>6-7</sub>                      | 11-24          | 1066               | 49.125               | 1            | 4     | 2                      | ×16        | $\mathcal{D}$            | $7.8 \times 10^{1}$                    | $5.2 \times 10^{1}$                        | $1.0 \times 10^2$                      | 21.3                  |

|                        | A <sub>8-12</sub>                     | 11-26          | 1066               | 49.125               | 1            | 4     | 2                      | ×16        | $\mathcal{D}$            | $2.4 \times 10^{2}$                    | $5.4 \times 10^{1}$                        | $4.4 \times 10^{2}$                    | 16.4                  |

| Α                      | A <sub>13-14</sub>                    | 11-50          | 1066               | 49.125               | 1            | 4     | 2                      | ×16        | $\mathcal{D}$            | $8.8 \times 10^{1}$                    | $1.7 \times 10^{1}$                        | $1.6 \times 10^{2}$                    | 26.2                  |

| ^                      | A <sub>15-16</sub>                    | 12-22          | 1600               | 50.625               | 1            | 4     | 2                      | ×16        |                          | 9.5                                    | 9                                          | $1.0 \times 10^{1}$                    | 34.4                  |

| Total of<br>43 Modules | A <sub>17-18</sub>                    | 12-26          | 1600               | 49.125               | 2 2          | 8     | 2 2                    | ×8         | M<br>K                   | $1.2 \times 10^2$<br>$8.6 \times 10^6$ | $3.7 \times 10^{1}$<br>$7.0 \times 10^{6}$ | $2.0 \times 10^2$<br>$1.0 \times 10^7$ | 21.3<br>8.2           |

|                        | A <sub>19-30</sub>                    | 12-40<br>13-02 | 1600<br>1600       | 48.125<br>48.125     | 2            | 8     | 2                      | ×8<br>×8   | _                        | $1.8 \times 10^{6}$                    | $1.0 \times 10^6$ $1.0 \times 10^6$        | $3.5 \times 10^6$                      | 11.5                  |

|                        | A <sub>31-34</sub>                    | 13-02          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | _                        | $4.0 \times 10^{1}$                    | $1.0 \times 10^{1}$ $1.9 \times 10^{1}$    |                                        | 21.3                  |

|                        | A <sub>35-36</sub>                    | 13-14          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | ĸ                        | $1.7 \times 10^6$                      | $1.4 \times 10^{6}$                        | $2.0 \times 10^{6}$                    | 9.8                   |

|                        | Α <sub>37-38</sub>                    | 13-28          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | K                        | $5.7 \times 10^4$                      |                                            |                                        | 16.4                  |

|                        | A <sub>39-40</sub>                    | 14-04          | 1600               | 49.125               | 2            | 8     | 2                      | ×8         | _                        | $2.7 \times 10^{5}$                    | $2.7 \times 10^5$                          |                                        | 18.0                  |

|                        | A <sub>41</sub><br>A <sub>42-43</sub> | 14-04          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | K                        | 0.5                                    | 0                                          | 1                                      | 62.3                  |

|                        | B <sub>1</sub>                        | 08-49          | 1066               | 50.625               | 1            | 8     | 1                      | ×8         | $\mathcal{D}$            | 0                                      | 0                                          | 0                                      |                       |

|                        | B <sub>2</sub>                        | 09-49          | 1066               | 50.625               | 1            | 8     | 1                      | ×8         | ε                        | 0                                      | 0                                          | 0                                      | _                     |

|                        | B <sub>2</sub>                        | 10-19          | 1066               | 50.625               | 1            | 8     | 1                      | ×8         | F                        | 0                                      | 0                                          | 0                                      | _                     |

|                        | B <sub>4</sub>                        | 10-31          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | c                        | 0                                      | 0                                          | 0                                      | -                     |

|                        | B <sub>5</sub>                        | 11-13          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | c                        | 0                                      | 0                                          | 0                                      | _                     |

|                        | B <sub>6</sub>                        | 11-16          | 1066               | 50.625               | 1            | 8     | 1                      | ×8         | F                        | 0                                      | 0                                          | 0                                      | -                     |

|                        | B <sub>7</sub>                        | 11-19          | 1066               | 50.625               | 1            | 8     | 1                      | ×8         | F                        | 0                                      | 0                                          | 0                                      | _                     |

|                        | B <sub>8</sub>                        | 11-25          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | С                        | 0                                      | 0                                          | 0                                      | -                     |

| В                      | B <sub>9</sub>                        | 11-37          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | $\mathcal{D}$            | $1.9 \times 10^{6}$                    | $1.9 \times 10^{6}$                        | $1.9 \times 10^{6}$                    | 11.5                  |

|                        | B <sub>10-12</sub>                    | 11-46          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | $\mathcal{D}$            | $2.2 \times 10^{6}$                    | $1.5 \times 10^{6}$                        | $2.7 \times 10^{6}$                    | 11.5                  |

| Total of               | B <sub>13</sub>                       | 11-49          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | C                        | 0                                      | 0                                          | 0                                      | -                     |

| 54 Modules             | B <sub>14</sub>                       | 12-01          | 1866               | 47.125               | 2            | 8     | 2                      | ×8         | $\mathcal{D}$            | $9.1 \times 10^{5}$                    | $9.1 \times 10^{5}$                        | $9.1 \times 10^{5}$                    | 9.8                   |

|                        | B <sub>15-31</sub>                    | 12-10          | 1866               | 47.125               | 2            | 8     | 2                      | ×8         | $\mathcal{D}$            | $9.8 \times 10^{5}$                    | $7.8 \times 10^{5}$                        | $1.2 \times 10^{6}$                    | 11.5                  |

|                        | B <sub>32</sub>                       | 12-25          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | ${\cal E}$               | $7.4 \times 10^{5}$                    | $7.4 \times 10^{5}$                        | $7.4 \times 10^{5}$                    | 11.5                  |

|                        | B <sub>33-42</sub>                    | 12-28          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | $\mathcal{E}$            | $5.2 \times 10^{5}$                    | $1.9 \times 10^{5}$                        | $7.3 \times 10^{5}$                    | 11.5                  |

|                        | B <sub>43-47</sub>                    | 12-31          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | $\mathcal E$             | $4.0 \times 10^{5}$                    | $2.9 \times 10^{5}$                        | $5.5 \times 10^{5}$                    | 13.1                  |

|                        | B <sub>48-51</sub>                    | 13-19          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | $\mathcal E$             | $1.1 \times 10^{5}$                    | $7.4 \times 10^{4}$                        | $1.4 \times 10^{5}$                    | 14.7                  |

|                        | B <sub>52-53</sub>                    | 13-40          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | $\mathcal{D}$            | $2.6 \times 10^{4}$                    | $2.3 \times 10^{4}$                        | $2.9 \times 10^{4}$                    | 21.3                  |

|                        | B <sub>54</sub>                       | 14-07          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | $\mathcal{D}$            | $7.5 \times 10^{3}$                    | $7.5 \times 10^{3}$                        | $7.5 \times 10^{3}$                    | 26.2                  |

|                        | Cı                                    | 10-18          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | $\mathcal{A}$            | 0                                      | 0                                          | 0                                      | -                     |

|                        | C <sub>2</sub>                        | 10-20          | 1066               | 50.625               | 2            | 8     | 2                      | ×8         | $\mathcal{A}$            | 0                                      | 0                                          | 0                                      | -                     |

|                        | $G_3$                                 | 10-22          | 1066               | 50.625               | 2            | 8     | 2                      | ×8         | $\mathcal{A}$            | 0                                      | 0                                          | 0                                      | -                     |

|                        | C                                     | 10-26          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | $\mathcal{B}$            | $8.9 \times 10^{2}$                    | $6.0 \times 10^{2}$                        | $1.2 \times 10^{3}$                    | 29.5                  |

|                        | $C_6$                                 | 10-43          | 1333               | 49.125               | 1            | 8     | 1                      | ×8         | au                       | 0                                      | 0                                          | 0                                      | -                     |

|                        | U <sub>7</sub>                        | 10-51          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | В                        |                                        | $4.0 \times 10^{2}$                        |                                        | 29.5                  |

|                        | C <sub>8</sub>                        | 11-12          | 1333               | 46.25                | 2            | 8     | 2                      | ×8         | В                        | $6.9 \times 10^{2}$                    |                                            |                                        | 21.3                  |

|                        | C <sub>9</sub>                        | 11-19          | 1333               | 46.25                | 2            | 8     | 2                      | ×8         | В                        |                                        | $9.2 \times 10^{2}$                        |                                        | 27.9                  |

|                        | C <sub>10</sub>                       | 11-31          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | В                        | 3                                      | 3                                          | 3                                      | 39.3                  |

| С                      | C11                                   | 11-42          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | В                        | $1.6 \times 10^{2}$                    | $1.6 \times 10^{2}$                        | $1.6 \times 10^{2}$                    | 39.3                  |

| 9                      | C <sub>12</sub>                       | 11-48          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | С                        |                                        | $7.1 \times 10^4$                          |                                        | 19.7                  |

| Total of               | C <sub>13</sub>                       | 12-08          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | С                        |                                        | $3.9 \times 10^{4}$                        |                                        | 21.3                  |

| 32 Modules             | C <sub>14-15</sub>                    | 12-12          | 1333               | 49.125               | 2            | 8     | 2                      | ×8         | С                        |                                        | $2.1 \times 10^{4}$                        |                                        | 21.3                  |

|                        | G16 10                                | 12-20          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | С                        |                                        | $1.2 \times 10^{3}$                        |                                        | 27.9                  |

|                        | C <sub>10</sub>                       | 12-23          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | ε                        |                                        | $1.4 \times 10^{5}$                        |                                        | 18.0                  |

|                        | C <sub>20</sub>                       | 12-24          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | С                        | $6.5 \times 10^4$                      | $6.5 \times 10^4$                          |                                        | 21.3                  |

|                        | $O_{21}$                              | 12-26          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | С                        |                                        | $2.3 \times 10^4$                          |                                        | 24.6                  |

|                        | C <sub>22</sub>                       | 12-32          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | С                        |                                        | $1.7 \times 10^4$                          |                                        | 22.9                  |

|                        | C <sub>23-24</sub>                    | 12-37          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | С                        |                                        | $1.1 \times 10^{4}$                        |                                        | 18.0                  |

|                        | G <sub>25-30</sub>                    | 12-41          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | С                        | $2.0 \times 10^4$                      | $1.1 \times 10^{4}$                        |                                        | 19.7                  |

|                        | C <sub>31</sub>                       | 13-11          | 1600               | 48.125               | 2            | 8     | 2                      | ×8         | С                        |                                        | $3.3 \times 10^{5}$                        |                                        | 14.7                  |

|                        | $C_{32}$                              | 13-35          | 1600               | 48.125               | 2            | 8     | 2                      | $\times 8$ | С                        | $3.7 \times 10^4$                      | $3.7 \times 10^{4}$                        | $3.7 \times 10^4$                      | 21.3                  |

<sup>\*</sup> We report the manufacture date marked on the chip packages, which is more accurate than other dates that can be gleaned from a module.

† We report timing constraints stored in the module's on-board ROM [33], which is read by the system BIOS to calibrate the memory controller.

‡ The maximum DRAM chip size supported by our testing platform is 2Gb.

$<sup>\</sup>S$  We report DRAM die versions marked on the chip packages, which typically progress in the following manner:  $\mathcal{M} \to \mathring{\mathcal{A}} \to \mathcal{B} \to \mathcal{C} \to \cdots$ .

# Fast Forward 6 Months

# More Reviews... Reviews from ISCA 2014

#### PAPER WEAKNESSES

- 1) The disturbance error (a.k.a coupling or cross-talk noise induced error) is a known problem to the DRAM circuit community.

- 2) What you demonstrated in this paper is so called DRAM row hammering issue you can even find a Youtube video showing this! <a href="http://www.youtube.com/watch?v=i3-gQSnBcdo">http://www.youtube.com/watch?v=i3-gQSnBcdo</a>

- Ine architectural contribution of this study is too insignificant.

#### PAPER WEAKNESSES

- Row Hammering appears to be well-known, and solutions have already been proposed by industry to address the issue.

- The paper only provides a qualitative analysis of solutions to the problem. A more robust evaluation is really needed to know whether the proposed solution is necessary.

### Final RowHammer Reviews

# Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Accepted

639kB 21 Nov 2013 10:53:11pm CST | f039be2735313b39304ae1c6296523867a485610

You are an **author** of this paper.

|             | OveMer | Nov | WriQua | RevConAnd |

|-------------|--------|-----|--------|-----------|

| Review #41A | 8      | 4   | 5      | 3         |

| Review #41B | 7      | 4   | 4      | 3         |

| Review #41C | 6      | 4   | 4      | 3         |

| Review #41D | 2      | 2   | 5      | 4         |

| Review #41E | 3      | 2   | 3      | 3         |

| Review #41F | 7      | 4   | 4      | 3         |

# RowHammer: Hindsight & Impact (I)

# Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Abstract. Memory isolation is a key property of a reliable and secure computing system — an access to one memory address should not have unintended side effects on data stored in other addresses. However, as DRAM process technology

# Project Zero

Flipping Bits in Memory Without Accessing Them:

An Experimental Study of DRAM Disturbance Errors

(Kim et al., ISCA 2014)

News and updates from the Project Zero team at Google

Exploiting the DRAM rowhammer bug to gain kernel privileges (Seaborn, 2015)

Monday, March 9, 2015

Exploiting the DRAM rowhammer bug to gain kernel privileges

# RowHammer: Hindsight & Impact (II)

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

<u>IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems</u> (TCAD) Special Issue on Top Picks in Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> §ETH Zürich <sup>‡</sup>Carnegie Mellon University

SAFARI 9

Suggestion to Researchers: Principle: Passion

# Follow Your Passion (Do not get derailed by naysayers)

Suggestion to Researchers: Principle: Resilience

# Be Resilient

Principle: Learning and Scholarship

# Focus on learning and scholarship

Principle: Learning and Scholarship

# The quality of your work defines your impact

# Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Minimally Changing Memory Chips

- Exploiting 3D-Stacked Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

# We Need to Think Differently from the Past Approaches