# **Computer Architecture** Lecture 19a: Multiprocessors

Prof. Onur Mutlu ETH Zürich Fall 2021 2 December 2021

# Readings: Multiprocessing

- Required

- Amdahl, "Validity of the single processor approach to achieving large scale computing capabilities," AFIPS 1967.

- Recommended

- Mike Flynn, "Very High-Speed Computing Systems," Proc. of IEEE, 1966

- Hill, Jouppi, Sohi, "Multiprocessors and Multicomputers," pp. 551-560 in Readings in Computer Architecture.

- Hill, Jouppi, Sohi, "Dataflow and Multithreading," pp. 309-314 in Readings in Computer Architecture.

# Memory Consistency

- Required

- Lamport, "How to Make a Multiprocessor Computer That Correctly Executes Multiprocess Programs," IEEE Transactions on Computers, 1979

# Readings: Cache Coherence

- Required

- Papamarcos and Patel, "A low-overhead coherence solution for multiprocessors with private cache memories," ISCA 1984.

- Recommended:

- Culler and Singh, Parallel Computer Architecture

- Chapter 5.1 (pp 269 283), Chapter 5.3 (pp 291 305)

- □ P&H, *Computer Organization and Design*

- Chapter 5.8 (pp 534 538 in 4<sup>th</sup> and 4<sup>th</sup> revised eds.)

Multiprocessors and Issues in Multiprocessing

#### Remember: Flynn's Taxonomy of Computers

- Mike Flynn, "Very High-Speed Computing Systems," Proc. of IEEE, 1966

- SISD: Single instruction operates on single data element

- SIMD: Single instruction operates on multiple data elements

Array processor

- Vector processor

- MISD: Multiple instructions operate on single data element

Closest form: systolic array processor, streaming processor

- MIMD: Multiple instructions operate on multiple data elements (multiple instruction streams)

- Multiprocessor

- Multithreaded processor

# Why Parallel Computers?

- Parallelism: Doing multiple things at a time

- Things: instructions, operations, tasks

- Main (or Original) Goal

- Improve performance (Execution time or task throughput)

- Execution time of a program governed by Amdahl's Law

- Other Goals

- Reduce power consumption

- (4N units at freq F/4) consume less power than (N units at freq F)

- Why?

- Improve cost efficiency and scalability, reduce complexity

- Harder to design a single unit that performs as well as N simpler units

- Improve dependability: Redundant execution in space

### Types of Parallelism and How to Exploit Them

- Instruction Level Parallelism

- Different instructions within a stream can be executed in parallel

- Pipelining, out-of-order execution, speculative execution, VLIW

- Dataflow

- Data Parallelism

- Different pieces of data can be operated on in parallel

- SIMD: Vector processing, array processing

- Systolic arrays, streaming processors

- Task Level Parallelism

- Different "tasks/threads" can be executed in parallel

- Multithreading

- Multiprocessing (multi-core)

## Task-Level Parallelism: Creating Tasks

- Partition a single problem into multiple related tasks (threads)

- Explicitly: Parallel programming

- Easy when tasks are natural in the problem

- Web/database queries

- Difficult when natural task boundaries are unclear

- Transparently/implicitly: Thread level speculation

- Partition a single thread speculatively

- Run many independent tasks (processes) together

- Easy when there are many processes

- Batch simulations, different users, cloud computing workloads

- Does not improve the performance of a single task

# Multiprocessing Fundamentals

# Multiprocessor Types

- Loosely coupled multiprocessors

- No shared global memory address space

- Multicomputer network

- Network-based multiprocessors

- Usually programmed via message passing

- Explicit calls (send, receive) for communication

- Tightly coupled multiprocessors

- Shared global memory address space

- Traditional multiprocessing: symmetric multiprocessing (SMP)

- Existing multi-core processors, multithreaded processors

- Programming model similar to uniprocessors (i.e., multitasking uniprocessor) except

- Operations on shared data require synchronization

# Main Design Issues in Tightly-Coupled MP

- Shared memory synchronization

- How to handle locks, atomic operations

- Cache coherence

- How to ensure correct operation in the presence of private caches keeping the same memory address cached

- Memory consistency: Ordering of all memory operations

What should the programmer expect the hardware to provide?

- Shared resource management

- Communication: Interconnects

#### Main Programming Issues in Tightly-Coupled MP

#### Load imbalance

How to partition a single task into multiple tasks

#### Synchronization

- How to synchronize (efficiently) between tasks

- How to communicate between tasks

- Locks, barriers, pipeline stages, condition variables, semaphores, atomic operations, ...

- Contention

- Maximizing parallelism

- Ensuring correct operation while optimizing for performance

# Aside: Hardware-based Multithreading

- Coarse grained

- Quantum based

- Event based (switch-on-event multithreading), e.g., switch on L3 miss

- Fine grained

- Cycle by cycle

- □ Thornton, "CDC 6600: Design of a Computer," 1970.

- Burton Smith, "A pipelined, shared resource MIMD computer," ICPP 1978.

#### Simultaneous

- Can dispatch instructions from multiple threads at the same time

- Good for improving execution unit utilization

# Limits of Parallel Speedup

### Parallel Speedup Example

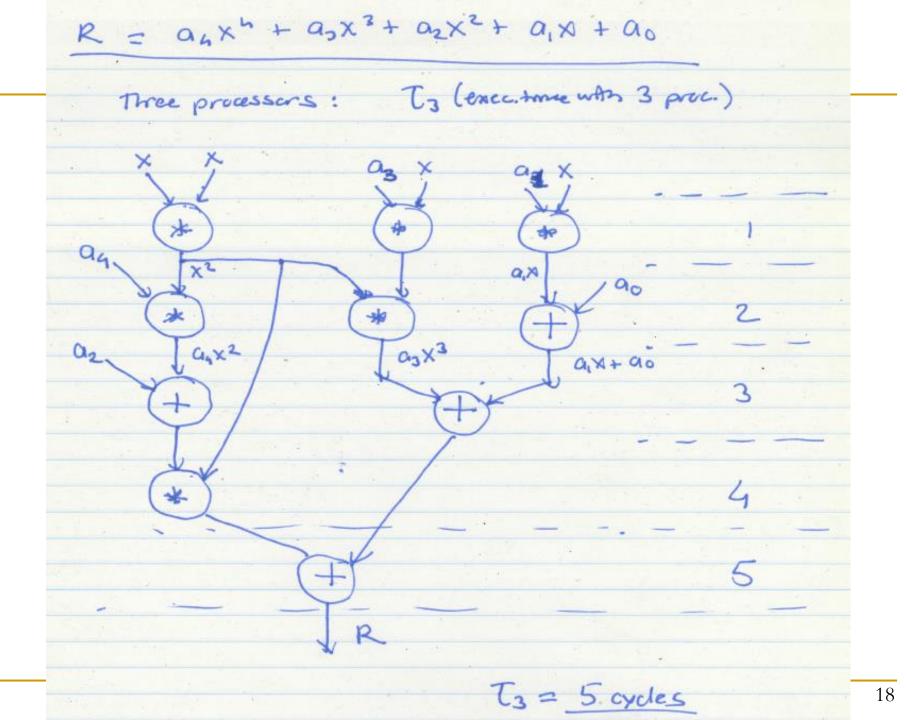

- $a_4 x^4 + a_3 x^3 + a_2 x^2 + a_1 x + a_0$

- Assume given inputs: x and each a<sub>i</sub>

- Assume each operation 1 cycle, no communication cost, each op can be executed in a different processor

- How fast is this with a single processor?

Assume no pipelining or concurrent execution of instructions

- How fast is this with 3 processors?

$R = a_4 x^4 + a_3 x^3 + a_2 x^2 + a_1 x + a_0$ Single processor: 11 operations (date How graph) a. \* 0, 20 03 q4 ¥ \* 43X3 ayxu Ozxt \* Q,X' Q4X4+03X3 ao T1 = 11 cycles

## Speedup with 3 Processors

T3 = 5. cycles Speedup with 3 precessors = 11  $\left(\frac{T_1}{T}\right)$ Is this a four composison?

# Revisiting the Single-Processor Algorithm

Revisit TI Better single-processor algorithm:  $R = a_1 x^4 + a_3 x^3 + a_2 x^2 + a_1 x + a_0$  $R = (((a_4x + a_3)x + a_2)x + a_1)x + a_0$ (Horner's method)

Horner, "A new method of solving numerical equations of all orders, by continuous approximation," Philosophical Transactions of the Royal Society, 1819.

an X J. a3 \* a, T1 = 8 cycles X Speedup with 3 pras. \_best 8 = 1.6 a Z3 best NO (not 2.2)

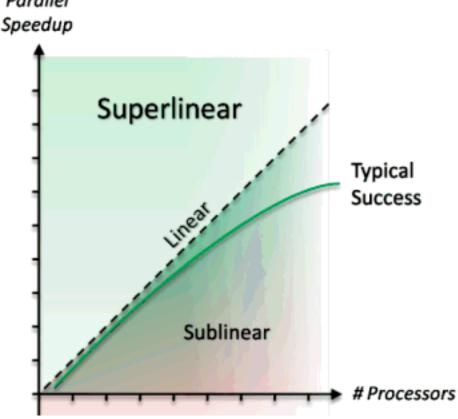

# Superlinear Speedup

- Can speedup be greater than P with P processing elements?

Parallel

- Unfair comparisons

Compare best parallel algorithm to wimpy serial algorithm  $\rightarrow$  unfair

Cache/memory effects

More processors  $\rightarrow$ more cache or memory  $\rightarrow$ fewer misses in cache/mem

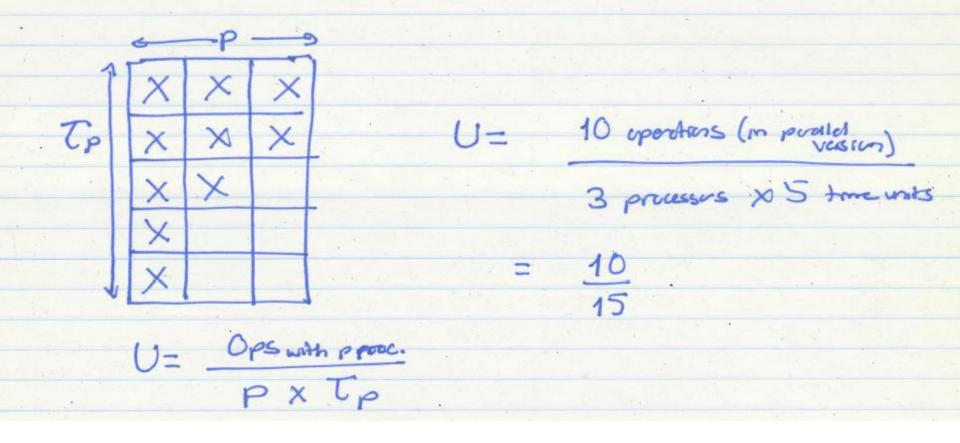

# Utilization, Redundancy, Efficiency

#### Traditional metrics

- Assume all P processors are tied up for parallel computation

- Utilization: How much processing capability is used

- U = (# Operations in parallel version) / (processors x Time)

- Redundancy: how much extra work is done with parallel processing

- R = (# of operations in parallel version) / (# operations in best single processor algorithm version)

Efficiency

- $\Box$  E = (Time with 1 processor) / (processors x Time with P processors)

- □ E = U/R

## Utilization of a Multiprocessor

Multiprocessor metrics.

Utilization: How much processing apololity we use

Redundary: How much extra work due to multipreasing R = Ops was proc. best = 10 Ops with 1 proc. best 8 R is always > 1 How much resource we use compared to how Efficiency: much resource we can get away with E = 1. Tibest (tyms up 1 procfor Typ time units) (typing up p prec for Tp tme units) p. Tpest  $= \frac{8}{15}$  $\left( \frac{E=U}{R} \right)$

5

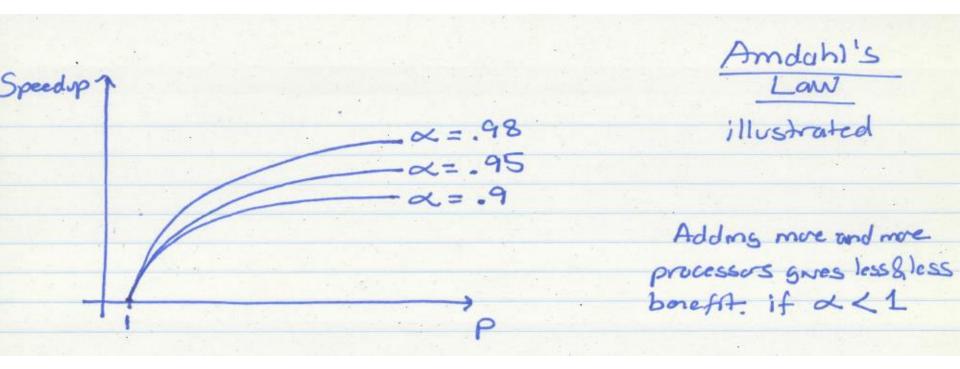

# Amdahl's Law and Caveats of Parallelism

#### Caveats of Parallelism (I)

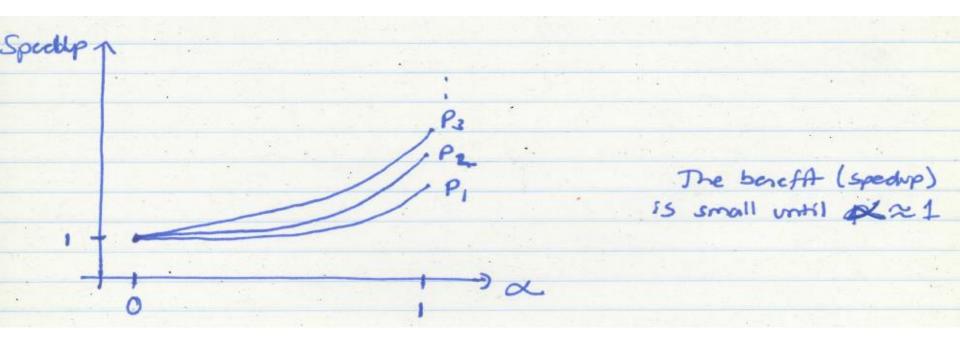

Speedup 1 Superimer restur Imeor speedup reality P(# cf processors) Why the really? (dominishing relims) X.\_[1 (1-a). T1 pon-porallelizeble pa purallelizable purt/fractions of the single-processor program

#### Amdahl's Law

peedup -d Speedup 00 thereck for probled

Amdahl, "Validity of the single processor approach to achieving large scale computing capabilities," AFIPS 1967.

### Amdahl's Law Implication 1

#### Amdahl's Law Implication 2

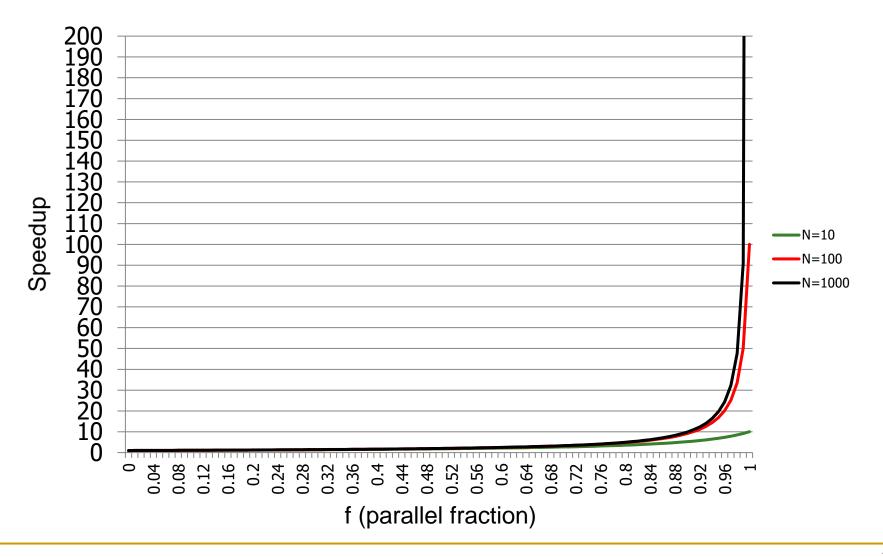

# Caveats of Parallelism (II)

- Amdahl' s Law

- f: Parallelizable fraction of a program

- N: Number of processors

Speedup =

$$\frac{1}{1 - f} + \frac{f}{N}$$

- Amdahl, "Validity of the single processor approach to achieving large scale computing capabilities," AFIPS 1967.

- Maximum speedup limited by serial portion: Serial bottleneck

- Parallel portion is usually not perfectly parallel

- Synchronization overhead (e.g., updates to shared data)

- Load imbalance overhead (imperfect parallelization)

- Resource sharing overhead (contention among N processors)

### Sequential Bottleneck

### Why the Sequential Bottleneck?

- Parallel machines have the sequential bottleneck

- Main cause: Non-parallelizable operations on data (e.g. nonparallelizable loops) for (i = 0; i < N; i++) A[i] = (A[i] + A[i-1]) / 2

- There are other causes as well:

- Single thread prepares data and spawns parallel tasks (usually sequential)

#### Another Example of Sequential Bottleneck (I)

Suleman+, "Accelerating Critical Section Execution with Asymmetric Multi-Core Architectures," ASPLOS 2009. 34

#### Another Example of Sequential Bottleneck (II)

Suleman+, "Accelerating Critical Section Execution with Asymmetric Multi-Core Architectures," ASPLOS 2009. 35

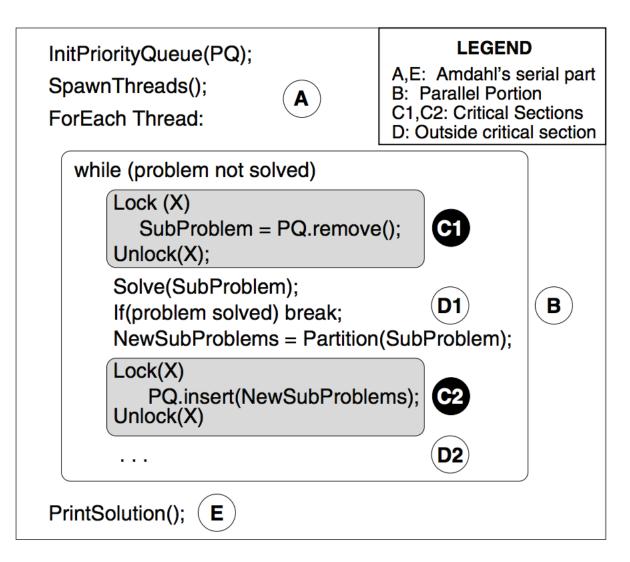

### Bottlenecks in Parallel Portion

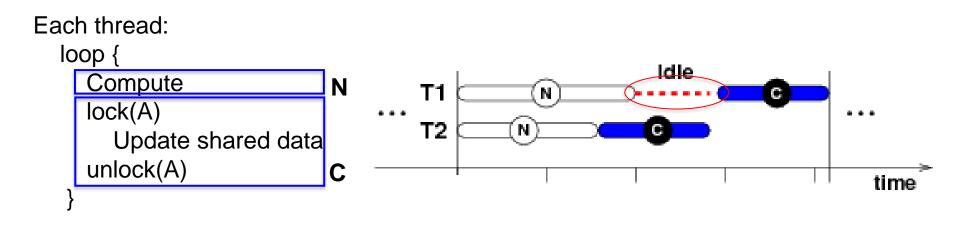

- Synchronization: Operations manipulating shared data cannot be parallelized

- Locks, mutual exclusion, barrier synchronization

- Communication: Tasks may need values from each other

- Causes thread serialization when shared data is contended

#### Load Imbalance: Parallel tasks may have different lengths

- Due to imperfect parallelization or microarchitectural effects

- Reduces speedup in parallel portion

- Resource Contention: Parallel tasks can share hardware resources, delaying each other

- Replicating all resources (e.g., memory) expensive

- Additional latency not present when each task runs alone

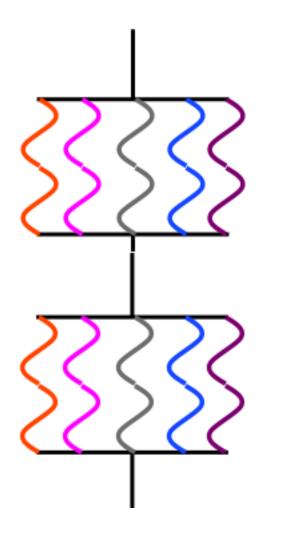

#### Bottlenecks in Parallel Portion: Another View

- Threads in a multi-threaded application can be interdependent

- As opposed to threads from different applications

- Such threads can synchronize with each other

Locks, barriers, pipeline stages, condition variables, semaphores, ...

- Some threads can be on the critical path of execution due to synchronization; some threads are not

- Even within a thread, some "code segments" may be on the critical path of execution; some are not

### Remember: Critical Sections

- Enforce mutually exclusive access to shared data

- Only one thread can be executing it at a time

- Contended critical sections make threads wait → threads causing serialization can be on the critical path

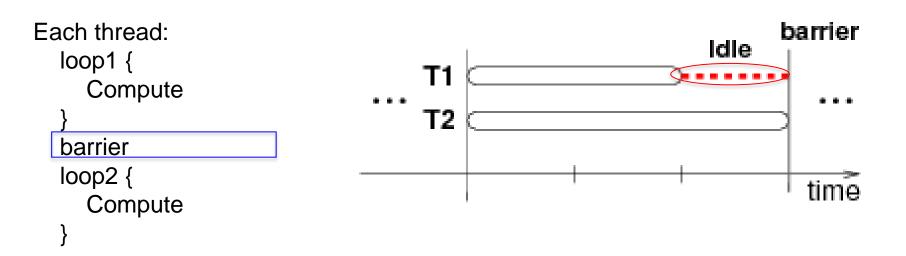

## Remember: Barriers

- Synchronization point

- Threads have to wait until all threads reach the barrier

- Last thread arriving to the barrier is on the critical path

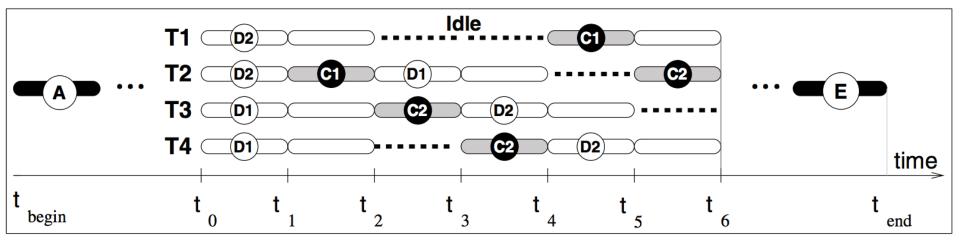

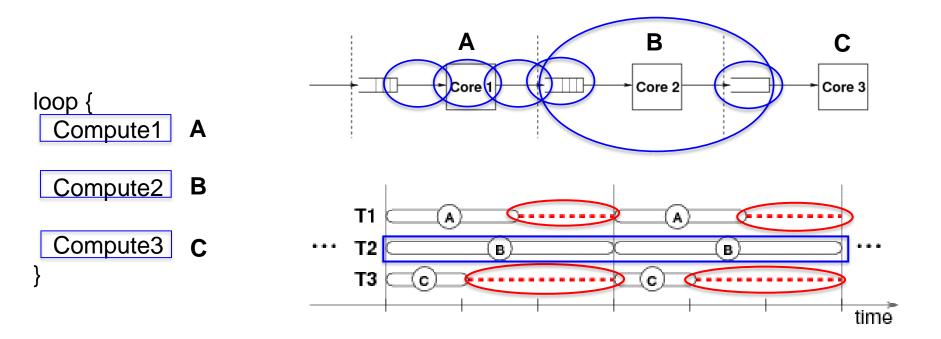

# Remember: Stages of Pipelined Programs

- Loop iterations are statically divided into code segments called *stages*

- Threads execute stages on different cores

- Thread executing the slowest stage is on the critical path

# Difficulty in Parallel Programming

- Little difficulty if parallelism is natural

- "Embarrassingly parallel" applications

- Multimedia, physical simulation, graphics

- Large web servers, databases?

- Difficulty is in

- Getting parallel programs to work correctly

- Optimizing performance in the presence of bottlenecks

#### Much of parallel computer architecture is about

- Designing machines that overcome the sequential and parallel bottlenecks to achieve higher performance and efficiency

- Making programmer's job easier in writing correct and highperformance parallel programs

# We Have Already Seen Examples

#### In Previous Two Lectures

- Lecture 17b: Parallelism and Heterogeneity

- https://www.youtube.com/watch?v=GLzG\_rEDn9A&list=PL5Q 2soXY2Zi-Mnk1PxjEIG32HAGILkTOF&index=18

- Lecture 18a: Bottleneck Acceleration

- https://www.youtube.com/watch?v=P8I3SMAbyYw&list=PL5Q 2soXY2Zi-Mnk1PxjEIG32HAGILkTOF&index=19

## More on Accelerated Critical Sections

M. Aater Suleman, Onur Mutlu, Moinuddin K. Qureshi, and Yale N. Patt, <u>"Accelerating Critical Section Execution with Asymmetric</u> <u>Multi-Core Architectures"</u>

Proceedings of the <u>14th International Conference on Architectural</u> <u>Support for Programming Languages and Operating</u> <u>Systems</u> (**ASPLOS**), pages 253-264, Washington, DC, March 2009. <u>Slides (ppt)</u> **One of the 13 computer architecture papers of 2009 selected as Top Picks by IEEE Micro.**

#### Accelerating Critical Section Execution with Asymmetric Multi-Core Architectures

M. Aater Suleman University of Texas at Austin suleman@hps.utexas.edu Onur Mutlu Carnegie Mellon University onur@cmu.edu Moinuddin K. Qureshi IBM Research mkquresh@us.ibm.com Yale N. Patt University of Texas at Austin patt@ece.utexas.edu

#### More on Bottleneck Identification & Scheduling

Jose A. Joao, M. Aater Suleman, Onur Mutlu, and Yale N. Patt, <u>"Bottleneck Identification and Scheduling in Multithreaded</u> <u>Applications"</u>

Proceedings of the <u>17th International Conference on Architectural</u> <u>Support for Programming Languages and Operating</u> <u>Systems</u> (**ASPLOS**), London, UK, March 2012. <u>Slides (ppt) (pdf)</u>

#### Bottleneck Identification and Scheduling in Multithreaded Applications

José A. Joao

ECE Department The University of Texas at Austin joao@ece.utexas.edu

#### M. Aater Suleman

Calxeda Inc. aater.suleman@calxeda.com

#### Onur Mutlu

Computer Architecture Lab. Carnegie Mellon University onur@cmu.edu Yale N. Patt

ECE Department The University of Texas at Austin patt@ece.utexas.edu

### More on Utility-Based Acceleration

Jose A. Joao, M. Aater Suleman, Onur Mutlu, and Yale N. Patt, "Utility-Based Acceleration of Multithreaded Applications on Asymmetric CMPs" Proceedings of the <u>40th International Symposium on Computer</u> Architecture (ISCA), Tel-Aviv, Israel, June 2013. <u>Slides (ppt)</u>

<u>Slides (pdf)</u>

#### Utility-Based Acceleration of Multithreaded Applications on Asymmetric CMPs

José A. Joao † M. Aater Suleman <sup>‡†</sup> Onur Mutlu <sup>§</sup> Yale N. Patt <sup>†</sup>

<sup>†</sup> ECE Department The University of Texas at Austin Austin, TX, USA {joao, patt}@ece.utexas.edu

<sup>‡</sup> Flux7 Consulting Austin, TX, USA suleman@hps.utexas.edu <sup>§</sup> Computer Architecture Laboratory Carnegie Mellon University Pittsburgh, PA, USA onur@cmu.edu

# More on Data Marshaling

M. Aater Suleman, Onur Mutlu, Jose A. Joao, Khubaib, and Yale N. Patt, "Data Marshaling for Multi-core Architectures" Proceedings of the <u>37th International Symposium on Computer</u> <u>Architecture</u> (ISCA), pages 441-450, Saint-Malo, France, June 2010. <u>Slides (ppt)</u> One of the 11 computer architecture papers of 2010 selected as Top Picks by IEEE Micro.

#### **Data Marshaling for Multi-core Architectures**

M. Aater Suleman<sup>†</sup> Onur Mutlu§ José A. Joao<sup>†</sup> Khubaib<sup>†</sup> Yale N. Patt<sup>†</sup>

†The University of Texas at Austin {suleman, joao, khubaib, patt}@hps.utexas.edu §Carnegie Mellon University

onur@cmu.edu

# **Computer Architecture** Lecture 19a: Multiprocessors

Prof. Onur Mutlu ETH Zürich Fall 2021 26 December 2021