# Computer Architecture

Lecture 7: Processing using Memory II

Dr. Juan Gómez Luna Prof. Onur Mutlu ETH Zürich Fall 2021 21 October 2021

## Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Processing using Memory

- Processing near Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

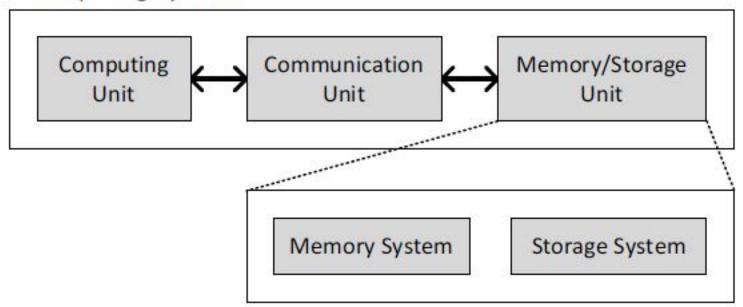

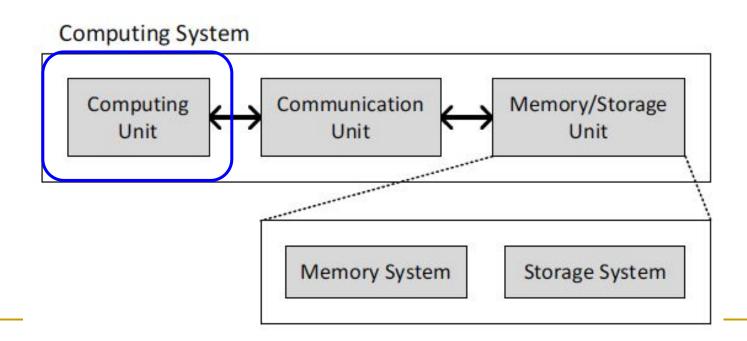

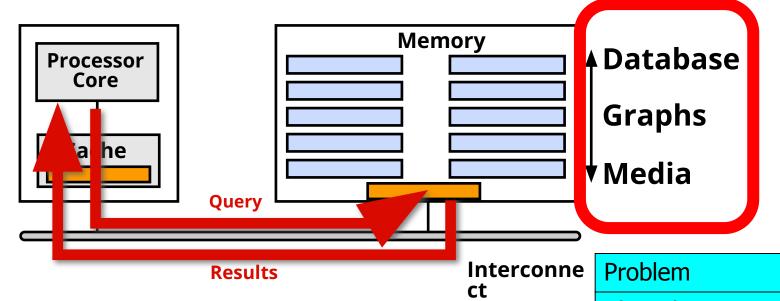

## A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### Computing System

# A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### Computing System

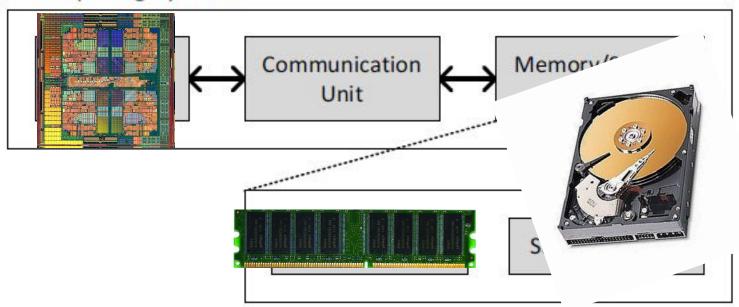

## Today's Computing Systems

- Are overwhelmingly processor centric

- All data processed in the processor □ at great system cost

- Processor is heavily optimized and is considered the master

- Data storage units are dumb and are largely unoptimized (except for some that are on the processor die)

I expect that over the coming decade memory subsystem design will be the *only* important design issue for microprocessors.

### "It's the Memory, Stupid!" (Richard Sites, MPR, 1996)

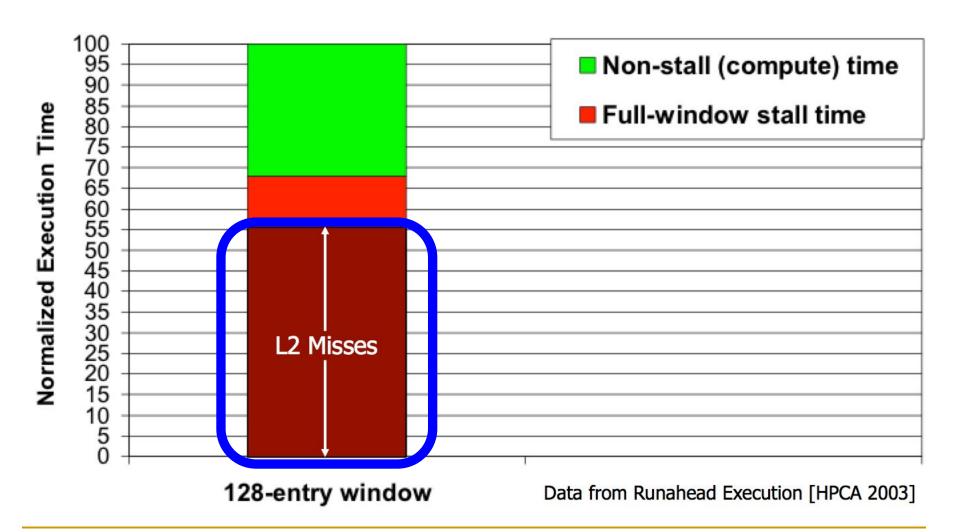

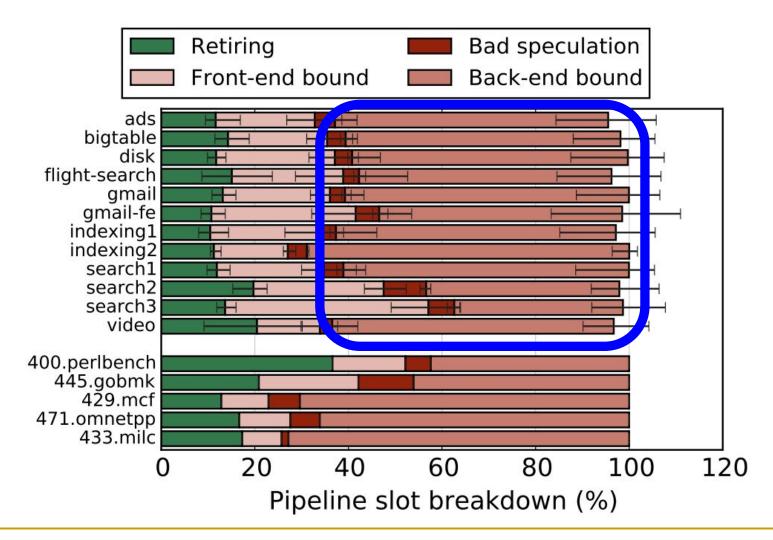

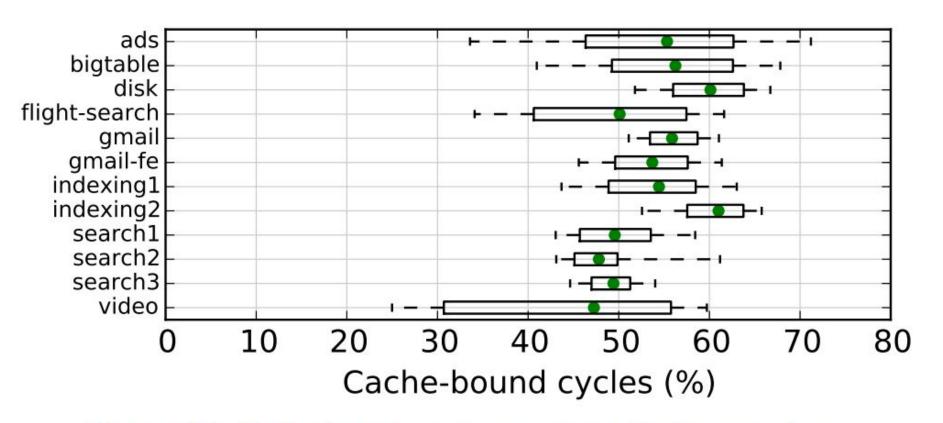

## The Performance Perspective (Today)

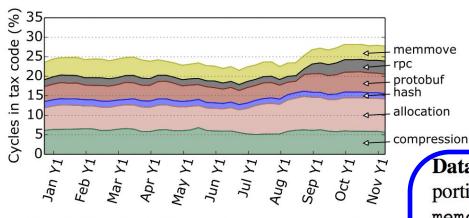

All of Google's Data Center Workloads (2015):

## The Performance Perspective (Today)

All of Google's Data Center Workloads (2015):

Figure 11: Half of cycles are spent stalled on caches.

## The Energy Perspective

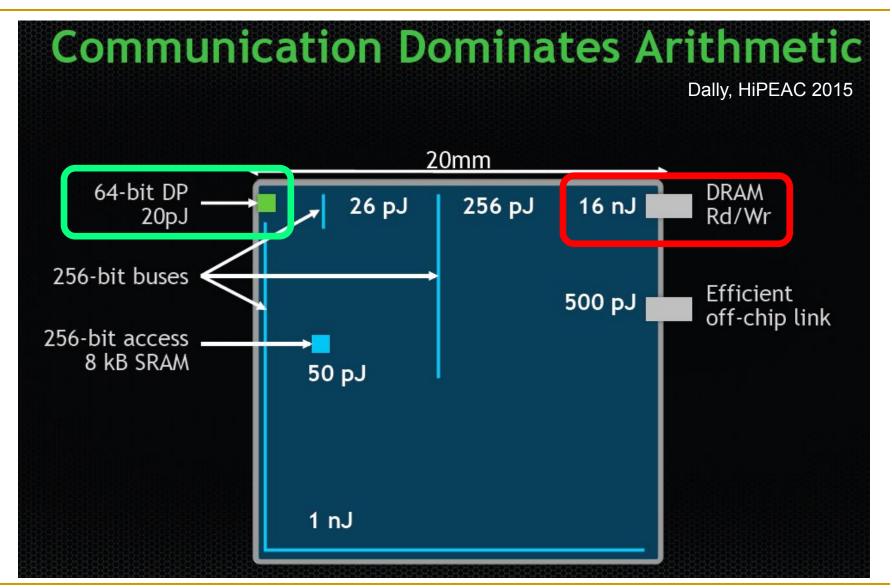

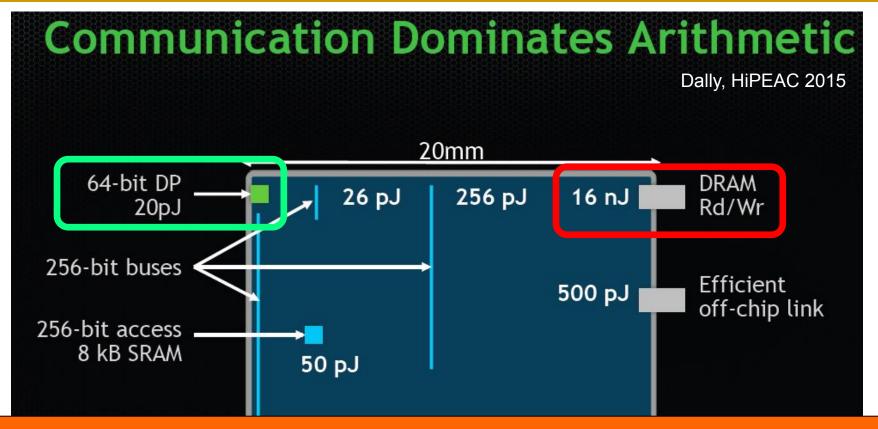

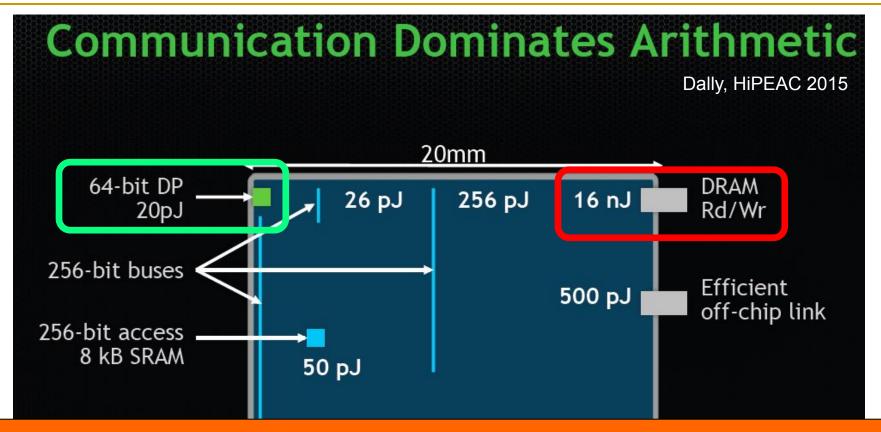

## Data Movement vs. Computation Energy

A memory access consumes ~100-1000X the energy of a complex addition

## Data Movement vs. Computation Energy

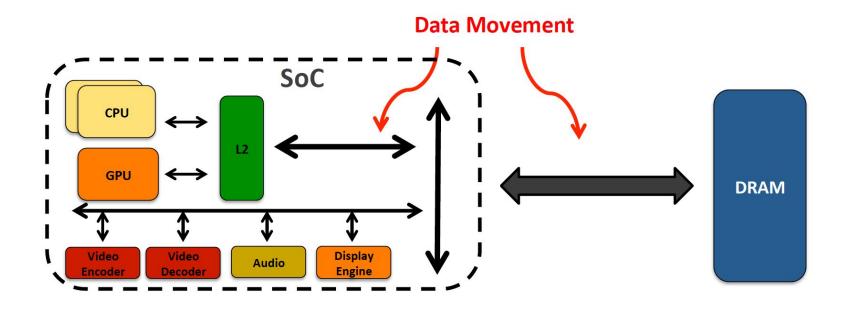

- Data movement is a major system energy bottleneck

- Comprises 41% of mobile system energy during web browsing [2]

[1]: Reducing data Movement Energy via Online Data Clustering and Encoding (MICRO'16)

[2]: Quantifying the energy cost of data movement for emerging smart phone workloads on mobile platforms (IISWC'14)

## Energy Waste in Mobile Devices

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the 23rd International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Williamsburg, VA, USA, March 2018.

# 62.7% of the total system energy is spent on data movement

## Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup> Saugata Ghose<sup>1</sup> Youngsok Kim<sup>2</sup> Rachata Ausavarungnirun<sup>1</sup> Eric Shiu<sup>3</sup> Rahul Thakur<sup>3</sup> Daehyun Kim<sup>4,3</sup> Aki Kuusela<sup>3</sup> Allan Knies<sup>3</sup> Parthasarathy Ranganathan<sup>3</sup> Onur Mutlu<sup>5,1</sup>

#### We Do Not Want to Move Data!

A memory access consumes ~100-1000X the energy of a complex addition

## We Need A Paradigm Shift To ...

Enable computation with minimal data movement

Compute where it makes sense (where data resides)

Make computing architectures more data-centric

# Goal: Processing Inside Memory

- Many questions ... How do we design the:

- compute-capable memory & controllers?

- processor chip and in-memory units?

- software and hardware interfaces?

- system software, compilers, languages?

- algorithms and theoretical foundations?

Algorithm

Program/Languag

System Software

SW/HW Interface

Micro-architecture

Logic

**Devices**

Electrons

## PIM Review and Open Problems

## A Modern Primer on Processing in Memory

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b,c</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>d</sup>

SAFARI Research Group

<sup>a</sup>ETH Zürich

<sup>b</sup>Carnegie Mellon University

<sup>c</sup>University of Illinois at Urbana-Champaign

<sup>d</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "A Modern Primer on Processing in Memory"

Invited Book Chapter in <u>Emerging Computing: From Devices to Systems - Looking</u> <u>Beyond Moore and Von Neumann</u>, Springer, to be published in 2021.

#### A Modern Primer on Processing in Memory

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b,c</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>d</sup>

SAFARI Research Group

<sup>a</sup>ETH Zürich

<sup>b</sup>Carnegie Mellon University

<sup>c</sup>University of Illinois at Urbana-Champaign

<sup>d</sup>King Mongkut's University of Technology North Bangkok

#### Abstract

Modern computing systems are overwhelmingly designed to move data to computation. This design choice goes directly against at least three key trends in computing that cause performance, scalability and energy bottlenecks: (1) data access is a key bottleneck as many important applications are increasingly data-intensive, and memory bandwidth and energy do not scale well, (2) energy consumption is a key limiter in almost all computing platforms, especially server and mobile systems, (3) data movement, especially off-chip to on-chip, is very expensive in terms of bandwidth, energy and latency, much more so than computation. These trends are especially severely-felt in the data-intensive server and energy-constrained mobile systems of today.

At the same time, conventional memory technology is facing many technology scaling challenges in terms of reliability, energy, and performance. As a result, memory system architects are open to organizing memory in different ways and making it more intelligent, at the expense of higher cost. The emergence of 3D-stacked memory plus logic, the adoption of error correcting codes inside the latest DRAM chips, proliferation of different main memory standards and chips, specialized for different purposes (e.g., graphics, low-power, high bandwidth, low latency), and the necessity of designing new solutions to serious reliability and security issues, such as the RowHammer phenomenon, are an evidence of this trend.

This chapter discusses recent research that aims to practically enable computation close to data, an approach we call processing-in-memory (PIM). PIM places computation mechanisms in or near where the data is stored (i.e., inside the memory chips, in the logic layer of 3D-stacked memory, or in the memory controllers), so that data movement between the computation units and memory is reduced or eliminated. While the general idea of PIM is not new, we discuss motivating trends in applications as well as memory circuits/technology that greatly exacerbate the need for enabling it in modern computing systems. We examine at least two promising new approaches to designing PIM systems to accelerate important data-intensive applications: (1) processing using memory by exploiting analog operational properties of DRAM chips to perform massively-parallel operations in memory, with low-cost changes, (2) processing near memory by exploiting 3D-stacked memory technology design to provide high memory bandwidth and low memory latency to in-memory logic. In both approaches, we describe and tackle relevant cross-layer research, design, and adoption challenges in devices, architecture, systems, and programming models. Our focus is on the development of in-memory processing designs that can be adopted in real computing platforms at low cost. We conclude by discussing work on solving key challenges to the practical adoption of PIM.

Keywords: memory systems, data movement, main memory, processing-in-memory, near-data processing, computation-in-memory, processing using memory, processing near memory, 3D-stacked memory, non-volatile memory, energy efficiency, high-performance computing, computer architecture, computing paradigm, emerging technologies, memory scaling, technology scaling, dependable systems, robust systems, hardware security, system security, latency, low-latency computing

| Con | tom |

|-----|-----|

| COH | Len |

| 1 | Introduction                                |     |  |  |  |  |

|---|---------------------------------------------|-----|--|--|--|--|

| 2 | <b>Major Trends Affecting Main Memory</b>   | 4   |  |  |  |  |

| 3 | The Need for Intelligent Memory Controllers |     |  |  |  |  |

|   | to Enhance Memory Scaling                   | 6   |  |  |  |  |

| 4 | Perils of Processor-Centric Design          | 9   |  |  |  |  |

| 5 | Processing-in-Memory (PIM): Technology      |     |  |  |  |  |

|   | Enablers and Two Approaches                 | 12  |  |  |  |  |

|   | 5.1 New Technology Enablers: 3D-Stacked     |     |  |  |  |  |

|   | Memory and Non-Volatile Memory              | 12  |  |  |  |  |

| _ | 5.2 Two Approaches: Processing Using        |     |  |  |  |  |

|   | Memory (PUM) vs. Processing Near            |     |  |  |  |  |

|   | Memory (PNM)                                | 13  |  |  |  |  |

| 6 | <b>Processing Using Memory (PUM)</b>        | 14  |  |  |  |  |

| - | 6.1 RowClone                                | 14  |  |  |  |  |

|   | 6.2 Ambit                                   | 15  |  |  |  |  |

|   | 6.2 Ambit                                   | 17  |  |  |  |  |

|   | 6.4 In-DRAM Security Primitives             | 17  |  |  |  |  |

|   | 0.4 III-Dicard Security Himmires            | 17  |  |  |  |  |

| 7 | Processing Near Memory (PNM)                | 18  |  |  |  |  |

|   | 7.1 Tesseract: Coarse-Grained Application-  | - 1 |  |  |  |  |

|   | Level PNM Acceleration of Graph Pro-        |     |  |  |  |  |

|   | cessing                                     | 19  |  |  |  |  |

|   | 7.2 Function-Level PNM Acceleration of      |     |  |  |  |  |

|   | Mobile Consumer Workloads                   | 20  |  |  |  |  |

|   | 7.3 Programmer-Transparent Function-        |     |  |  |  |  |

|   | Level PNM Acceleration of GPU               |     |  |  |  |  |

|   | Applications                                | 21  |  |  |  |  |

|   | 7.4 Instruction-Level PNM Acceleration      |     |  |  |  |  |

|   | with PIM-Enabled Instructions (PEI)         | 21  |  |  |  |  |

|   | 7.5 Function-Level PNM Acceleration of      |     |  |  |  |  |

|   | Genome Analysis Workloads                   | 22  |  |  |  |  |

|   | 7.6 Application-Level PNM Acceleration of   | 22  |  |  |  |  |

|   | Time Series Analysis                        | 23  |  |  |  |  |

| 8 | Enabling the Adoption of PIM                | 24  |  |  |  |  |

|   | 8.1 Programming Models and Code Genera-     |     |  |  |  |  |

|   | tion for PIM                                | 24  |  |  |  |  |

|   | 8.2 PIM Runtime: Scheduling and Data        |     |  |  |  |  |

|   | Mapping                                     | 25  |  |  |  |  |

|   | 8.3 Memory Coherence                        | 27  |  |  |  |  |

|   | 8.4 Virtual Memory Support                  | 27  |  |  |  |  |

|   | 8.5 Data Structures for PIM                 | 28  |  |  |  |  |

|   | 8.6 Benchmarks and Simulation Infrastruc-   |     |  |  |  |  |

|   | tures                                       | 29  |  |  |  |  |

|   | 8.7 Real PIM Hardware Systems and Proto-    | -   |  |  |  |  |

|   | types                                       | 30  |  |  |  |  |

| _ | 8.8 Security Considerations                 | 30  |  |  |  |  |

|   |                                             |     |  |  |  |  |

| 9 | Conclusion and Future Outlook               | 31  |  |  |  |  |

#### 1. Introduction

Main memory, built using the Dynamic Random Access Memory (DRAM) technology, is a major component in nearly all computing systems, including servers, cloud platforms, mobile/embedded devices, and sensor systems. Across all of these systems, the data working set sizes of modern applications are rapidly growing, while the need for fast analysis of such data is increasing. Thus, main memory is becoming an increasingly significant bottleneck across a wide variety of computing systems and applications [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16]. Alleviating the main memory bottleneck requires the memory capacity, energy, cost, and performance to all scale in an efficient manner across technology generations. Unfortunately, it has become increasingly difficult in recent years, especially the past decade, to scale all of these dimensions [1, 2, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 40, 41, 42, 43, 44, 45, 46, 47, 48, 49], and thus the main memory bottleneck has been worsening.

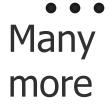

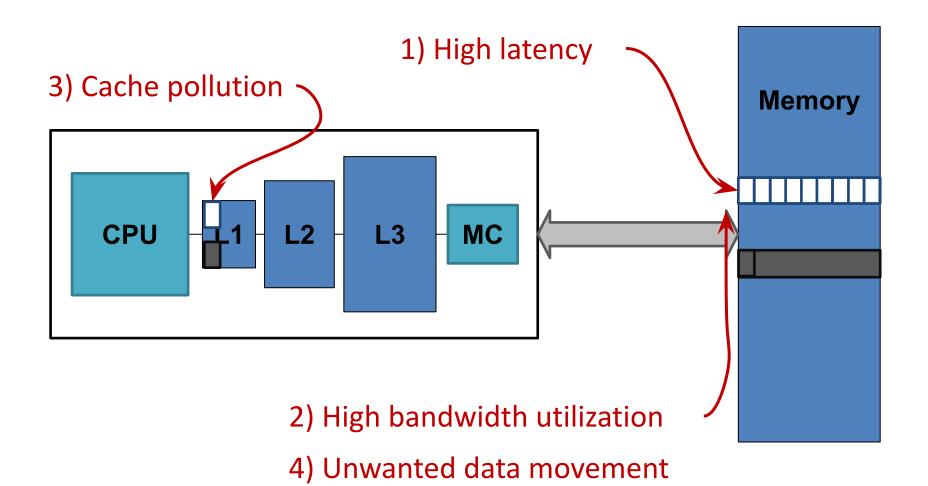

A major reason for the main memory bottleneck is the high energy and latency cost associated with data movement. In modern computers, to perform any operation on data that resides in main memory, the processor must retrieve the data from main memory. This requires the memory controller to issue commands to a DRAM module across a relatively slow and power-hungry off-chip bus (known as the memory channel). The DRAM module sends the requested data across the memory channel, after which the data is placed in the caches and registers. The CPU can perform computation on the data once the data is in its registers. Data movement from the DRAM to the CPU incurs long latency and consumes a significant amount of energy [7, 50, 51, 52, 53, 54]. These costs are often exacerbated by the fact that much of the data brought into the caches is not reused by the CPU [52, 53, 55, 56], providing little benefit in return for the high latency and energy cost.

The cost of data movement is a fundamental issue with the processor-centric nature of contemporary computer systems. The CPU is considered to be the master in the system, and computation is performed only in the processor (and accelerators). In contrast, data storage and communication units, including the main memory, are treated as unintelligent workers that are incapable of computation. As a result of this processor-centric design paradigm, data moves a lot in the system between the computation units and communication/ storage units so that computation can be done on it. With the increasingly data-centric nature of contemporary and emerging appli-

# Processing Data Where It Makes Sense

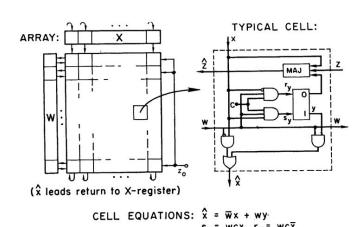

## Processing in/near Memory: An Old Idea

Kautz, "Cellular Logic-in-Memory Arrays", IEEE TC 1969.

IEEE TRANSACTIONS ON COMPUTERS, VOL. C-18, NO. 8, AUGUST 1969

## Cellular Logic-in-Memory Arrays

WILLIAM H. KAUTZ, MEMBER, IEEE

Abstract—As a direct consequence of large-scale integration, many advantages in the design, fabrication, testing, and use of digital circuitry can be achieved if the circuits can be arranged in a two-dimensional iterative, or cellular, array of identical elementary networks, or cells. When a small amount of storage is included in each cell, the same array may be regarded either as a logically enhanced memory array, or as a logic array whose elementary gates and connections can be "programmed" to realize a desired logical behavior.

In this paper the specific engineering features of such cellular logic-in-memory (CLIM) arrays are discussed, and one such special-purpose array, a cellular sorting array, is described in detail to illustrate how these features may be achieved in a particular design. It is shown how the cellular sorting array can be employed as a single-address, multiword memory that keeps in order all words stored within it. It can also be used as a content-addressed memory, a pushdown memory, a buffer memory, and (with a lower logical efficiency) a programmable array for the realization of arbitrary switching functions. A second version of a sorting array, operating on a different sorting principle, is also described.

Index Terms—Cellular logic, large-scale integration, logic arrays logic in memory, push-down memory, sorting, switching functions.

Fig. 1. Cellular sorting array I.

$\hat{z} = M(x, \overline{y}, z) = x\overline{y} + z(x + \overline{y})$

## Processing in/near Memory: An Old Idea

Stone, "A Logic-in-Memory Computer," IEEE TC 1970.

### A Logic-in-Memory Computer

HAROLD S. STONE

Abstract—If, as presently projected, the cost of microelectronic arrays in the future will tend to reflect the number of pins on the array rather than the number of gates, the logic-in-memory array is an extremely attractive computer component. Such an array is essentially a microelectronic memory with some combinational logic associated with each storage element.

## UPMEM Processing-in-DRAM Engine (2019)

- Processing in DRAM Engine

- Includes standard DIMM modules, with a large number of DPU processors combined with DRAM chips.

- Replaces standard DIMMs

- DDR4 R-DIMM modules

- 8GB+128 DPUs (16 PIM chips)

- Standard 2x-nm DRAM process

- Large amounts of compute & memory bandwidth

## 2,560-DPU Processing-in-Memory System

databases, data analytics, graph processing, neural networks, bioinformatics, image processing), which we identify as memory-bound. We evaluate the performance and scaling characteristics of PrIM benchmarks on the UPMEM PIM architecture, and compare their performance and energy consumption to their state-of-the-art CPU and GPU counterparts. Our extensive evaluation conducted on two real UPMEM-based PIM.

systems with 640 and 2,556 DPUs provides new insights about suitability of different workloads to the PIM

system, programming recommendations for software designers, and suggestions and hints for hardware and

architecture designers of future PIM systems.

## Experimental Analysis of the UPMEM PIM Engine

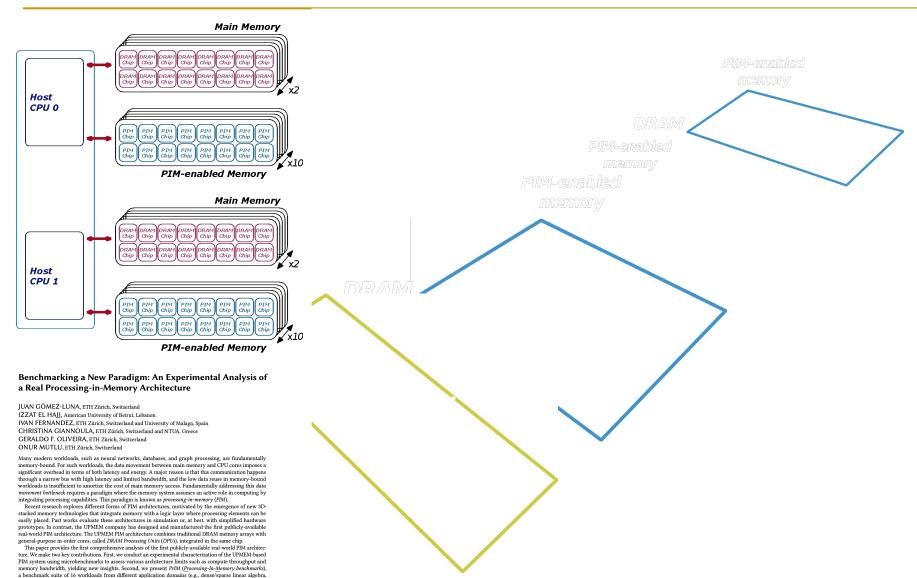

## Benchmarking a New Paradigm: An Experimental Analysis of a Real Processing-in-Memory Architecture

JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland IZZAT EL HAJJ, American University of Beirut, Lebanon IVAN FERNANDEZ, ETH Zürich, Switzerland and University of Malaga, Spain CHRISTINA GIANNOULA, ETH Zürich, Switzerland and NTUA, Greece GERALDO F. OLIVEIRA, ETH Zürich, Switzerland ONUR MUTLU, ETH Zürich, Switzerland

Many modern workloads, such as neural networks, databases, and graph processing, are fundamentally memory-bound. For such workloads, the data movement between main memory and CPU cores imposes a significant overhead in terms of both latency and energy. A major reason is that this communication happens through a narrow bus with high latency and limited bandwidth, and the low data reuse in memory-bound workloads is insufficient to amortize the cost of main memory access. Fundamentally addressing this *data movement bottleneck* requires a paradigm where the memory system assumes an active role in computing by integrating processing capabilities. This paradigm is known as *processing-in-memory (PIM)*.

Recent research explores different forms of PIM architectures, motivated by the emergence of new 3D-stacked memory technologies that integrate memory with a logic layer where processing elements can be easily placed. Past works evaluate these architectures in simulation or, at best, with simplified hardware prototypes. In contrast, the UPMEM company has designed and manufactured the first publicly-available real-world PIM architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called *DRAM Processing Units* (*DPUs*), integrated in the same chip.

This paper provides the first comprehensive analysis of the first publicly-available real-world PIM architecture. We make two key contributions. First, we conduct an experimental characterization of the UPMEM-based PIM system using microbenchmarks to assess various architecture limits such as compute throughput and memory bandwidth, yielding new insights. Second, we present *PrIM* (*Processing-In-Memory benchmarks*), a benchmark suite of 16 workloads from different application domains (e.g., dense/sparse linear algebra, databases, data analytics, graph processing, neural networks, bioinformatics, image processing), which we identify as memory-bound. We evaluate the performance and scaling characteristics of PrIM benchmarks on the UPMEM PIM architecture, and compare their performance and energy consumption to their state-of-the-art CPU and GPU counterparts. Our extensive evaluation conducted on two real UPMEM-based PIM systems with 640 and 2,556 DPUs provides new insights about suitability of different workloads to the PIM system, programming recommendations for software designers, and suggestions and hints for hardware and architecture designers of future PIM systems.

https://arxiv.org/pdf/2105.03814.pdf

## Samsung Function-in-Memory DRAM (2021)

Samsung Newsroom

CORPORATE

**PRODUCTS**

PRESS RESOURCES

VIEWS

**ABOUT US**

Q

# Samsung Develops Industry's First High Bandwidth Memory with Al Processing Power

Korea on February 17, 2021

Audio

Share 5

The new architecture will deliver over twice the system performance and reduce energy consumption by more than 70%

Samsung Electronics, the world leader in advanced memory technology, today announced that it has developed the industry's first High Bandwidth Memory (HBM) integrated with artificial intelligence (AI) processing power — the HBM-PIM The new processing-in-memory (PIM) architecture brings powerful AI computing capabilities inside high-performance memory, to accelerate large-scale processing in data centers, high performance computing (HPC) systems and AI-enabled mobile applications.

Kwangil Park, senior vice president of Memory Product Planning at Samsung Electronics stated, "Our groundbreaking HBM-PIM is the industry's first programmable PIM solution tailored for diverse Al-driven workloads such as HPC, training and inference. We plan to build upon this breakthrough by further collaborating with Al solution providers for even more advanced PIM-powered applications."

## Samsung Function-in-Memory DRAM (2021)

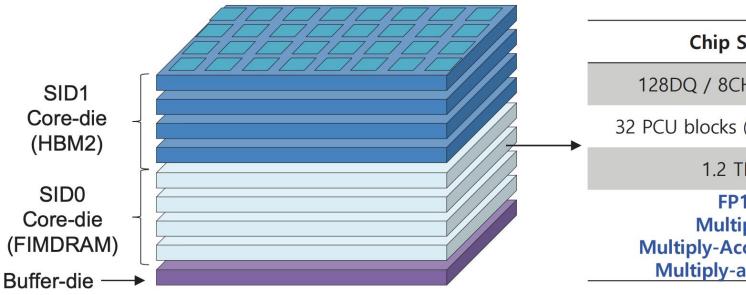

#### FIMDRAM based on HBM2

[3D Chip Structure of HBM with FIMDRAM]

#### **Chip Specification**

128DQ / 8CH / 16 banks / BL4

32 PCU blocks (1 FIM block/2 banks)

1.2 TFLOPS (4H)

FP16 ADD /

Multiply (MUL) /

Multiply-Accumulate (MAC) /

Multiply-and- Add (MAD)

#### ISSCC 2021 / SESSION 25 / DRAM / 25.4

25.4 A 20nm 6GB Function-In-Memory DRAM, Based on HBM2 with a 1.2TFLOPS Programmable Computing Unit Using Bank-Level Parallelism. for Machine Learning Applications

Young-Cheon Kwon', Suk Han Lee', Jaehoon Lee', Sang-Hyuk Kwon', Je Min Ryu', Jong-Pii Son', Seongil O', Hak-Soo Yu', Haesuk Lee', Soo Young Kim', Youngmin Cho', Jin Guk Kim', Jongyoon Choi', Hyun-Sung Shin', Jin Kim', BengSeng Phuah', HyoungMin Kim', Myeong Jun Song', Ahn Choi', Daeho Kim', SooYoung Kim', Eun-Bong Kim', David Wang', Shinhaeng Kang', Yuhwan Ro³, Seungwoo Seo³, JoonHo Song³, Jaeyoun Youn', Kyomin Sohn', Nam Sung Kim'

<sup>1</sup>Samsung Electronics, Hwaseong, Korea <sup>2</sup>Samsung Electronics, San Jose, CA <sup>3</sup>Samsung Electronics, Suwon, Korea

## Samsung Function-in-Memory DRAM (2021)

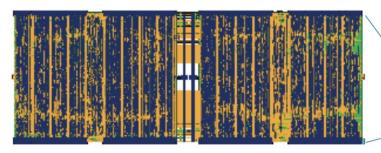

## **Chip Implementation**

- Mixed design methodology to implement FIMDRAM

- Full-custom + Digital RTL

[Digital RTL design for PCU block]

#### ISSCC 2021 / SESSION 25 / DRAM / 25.4

25.4 A 20nm 6GB Function-In-Memory DRAM, Based on HBM2 with a 1.2TFLOPS Programmable Computing Unit Using Bank-Level Parallelism, for Machine Learning Applications

Young-Cheon Kwon', Suk Han Let', Jaehoon Lee', Sang-Hvuk Kwon', Je Min Ryu', Jong-Pil Son', Seongil O', Hak-Soo Yu', Haesuk Lee', Soo Young Kim', Youngmin Cho', Jin Guk Kim', Jongyoon Choi', Hyun-Sung Shin', Jin Kim', BengSeng Phuah', HyoungMin Kim', Hyeeng Juan Song', Ahn Choi', Jeacho Kim', Soo'Oung Kim', Eun-Bong Kim', David Wang', Shinhaeng Kang', Yuhwan Ro', Seungwoo Seo', JoonHo Song', Jaeyoun Youn', Kyomin Sohn', Man Sung Kim'

| Cell array<br>for bank0                                               | Cell array<br>for bank4                                               | Cell array<br>for bank0                                                                       | Cell array<br>for bank4                                               | Pseudo       | Pseudo    |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|-----------|

| PCU block<br>for bank0 & 1                                            | PCU block<br>for bank4 & 5                                            | PCU block<br>for bank0 & 1                                                                    | PCU block<br>for bank4 & 5                                            | channel-0    | channel-1 |

| Cell array<br>for bank1<br>Cell array<br>for bank2                    | Cell array<br>for bank5<br>Cell array<br>for bank6                    | Cell array<br>for bank1<br>Cell array<br>for bank2                                            | Cell array<br>for bank5<br>Cell array<br>for bank6                    |              |           |

| PCU block<br>for bank2 & 3                                            | PCU block<br>for bank6 & 7                                            | PCU block<br>for bank2 & 3                                                                    | PCU block<br>for bank6 & 7                                            |              |           |

| Cell array<br>for bank3                                               | Cell array<br>for bank7                                               | Cell array<br>for bank3                                                                       | Cell array<br>for bank7                                               |              |           |

|                                                                       | 在非效制物。                                                                | TSV &                                                                                         | Peri C                                                                | ontrol Block |           |

|                                                                       |                                                                       |                                                                                               |                                                                       |              |           |

| Cell array<br>for bank11<br>PCU block                                 | Cell array<br>for bank15<br>PCU block                                 | Cell array<br>for bank11<br>PCU block                                                         | Cell array<br>for bank15<br>PCU block                                 |              |           |

| for bank11 PCU block                                                  | for bank15                                                            | for bank11 PCU block                                                                          | for bank15<br>PCU block                                               |              |           |

| for bank11 PCU block for bank10 & 1  Cell array for bank10 Cell array | for bank15 PCU block for bank14 & 15 Cell array for bank14 Cell array | for bank11  PCU block for bank10 & 11  Cell array for bank10  Cell array for bank9  PCU block | for bank15 PCU block for bank14 & 15 Cell array for bank14 Cell array | Pseudo       | Pseudo    |

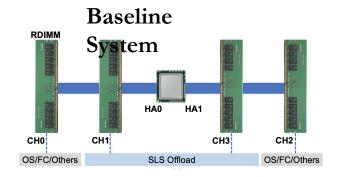

## Samsung AxDIMM (2021)

- DDR5-PIM

- DLRM recommendation system

## FPGA-based Processing Near Memory

Gagandeep Singh, Mohammed Alser, Damla Senol Cali, Dionysios

Diamantopoulos, Juan Gómez-Luna, Henk Corporaal, and Onur Mutlu,

"FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications"

<u>IEEE Micro</u> (**IEEE MICRO**), to appear, 2021.

# FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications

Gagandeep Singh<sup>⋄</sup> Mohammed Alser<sup>⋄</sup> Damla Senol Cali<sup>⋈</sup>

Dionysios Diamantopoulos<sup>▽</sup> Juan Gómez-Luna<sup>⋄</sup>

Henk Corporaal<sup>⋆</sup> Onur Mutlu<sup>⋄⋈</sup>

<sup>⋄</sup>ETH Zürich <sup>⋈</sup> Carnegie Mellon University \*Eindhoven University of Technology <sup>▽</sup>IBM Research Europe

## Why In-Memory Computation Today?

- Push from Technology

- DRAM Scaling at jeopardy

- □ Controllers close to DRAM

- ☐ Industry open to new memory architectures

- Pull from Systems and Applications

- Data access is a major system and application bottleneck

- Systems are energy limited

- Data movement much more energy-hungry than computation

## Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Processing using Memory

- Processing near Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

## Two PIM Approaches

## 5.2. Two Approaches: Processing Using Memory (PUM) vs. Processing Near Memory (PNM)

Many recent works take advantage of the memory technology innovations that we discuss in Section 5.1 to enable and implement PIM. We find that these works generally take one of two approaches, which are categorized in Table 1: (1) processing using memory or (2) processing near memory. We briefly describe each approach here. Sections 6 and 7 will provide example approaches and more detail for both.

Table 1: Summary of enabling technologies for the two approaches to PIM used by recent works. Adapted from [309].

| Approach                | <b>Enabling Technologies</b>      |  |

|-------------------------|-----------------------------------|--|

|                         | SRAM                              |  |

|                         | DRAM                              |  |

| Processing Using Memory | Phase-change memory (PCM)         |  |

|                         | Magnetic RAM (MRAM)               |  |

|                         | Resistive RAM (RRAM)/memristors   |  |

|                         | Logic layers in 3D-stacked memory |  |

| Processing Near Memory  | Silicon interposers               |  |

| -                       | Logic in memory controllers       |  |

**Processing using memory (PUM)** exploits the existing memory architecture and the operational principles of the memory circuitry to enable operations within main memory with minimal changes. PUM makes use

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun,

### "A Modern Primer on Processing in Memory"

Invited Book Chapter in <u>Emerging Computing:</u>

<u>From Devices to Systems - Looking Beyond</u>

<u>Moore and Von Neumann</u>, Springer, to be published in 2021.

[<u>Tutorial Video on "Memory-Centric Computing</u> <u>Systems"</u> (1 hour 51 minutes)]

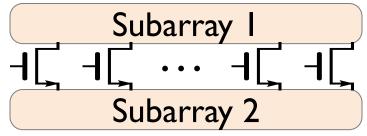

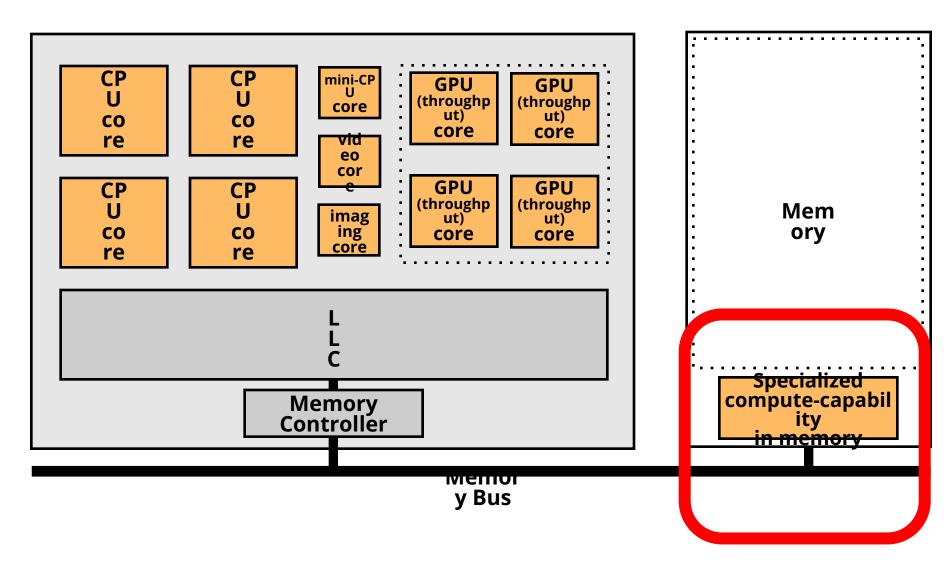

# Processing in Memory: Two Approaches

- 1. Processing using Memory

- 2. Processing near Memory

## Approach 1: Processing Using Memory

- Take advantage of operational principles of memory to perform bulk data movement and computation in memory

- Can exploit internal connectivity to move data

- Can exploit analog computation capability

- Examples: RowClone, In-DRAM AND/OR, Gather/Scatter DRAM

- RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data (Seshadri et al., MICRO 2013)

- Fast Bulk Bitwise AND and OR in DRAM (Seshadri et al., IEEE CAL 2015)

- Gather-Scatter DRAM: In-DRAM Address Translation to Improve the Spatial Locality of Non-unit Strided Accesses (Seshadri et al., MICRO 2015)

- "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity

DRAM Technology" (Seshadri et al., MICRO 2017)

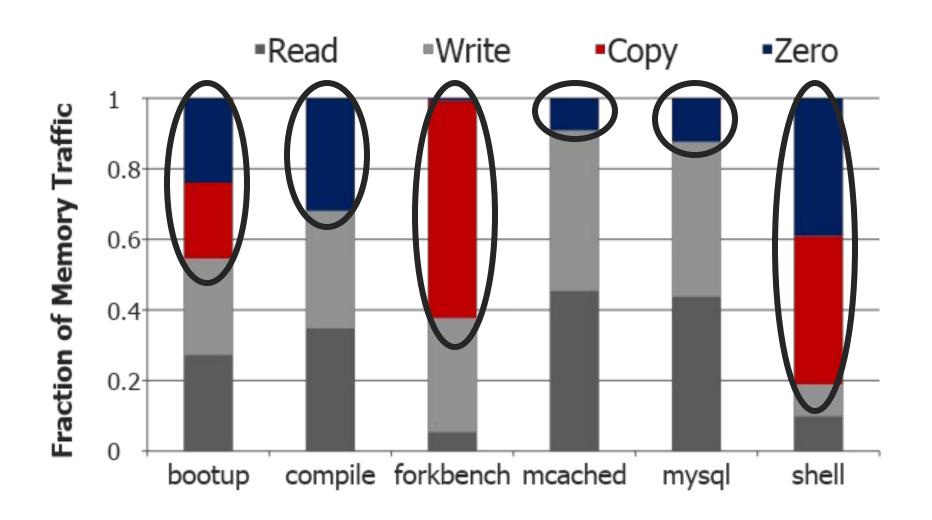

## Starting Simple: Data Copy and Initialization

Bulk Data Copy src ----→ dst

**Bulk Data Initialization**

# Bulk Data Copy and Initialization

# The Impact of Architectural Trends on Operating System Performance

Mendel Rosenblum, Edouard Bugnion, Stephen Alan Herrod,

# Hardware Support for Bulk Data Movement in Server Platforms

Li Zhao<sup>†</sup>, Ravi Iyer<sup>‡</sup> Srihari Makineni<sup>‡</sup>, Laxmi Bhuyan<sup>†</sup> and Don Newell<sup>‡</sup>

Department of Computer Science and Engineering, University of California, Riverside, CA 92521

Email: {zhao, bhuyan}@cs.ucr.edu

Communications Technology Lab Intel-Communications Technology Lab Intel-Communications

#### Tr

#### Architecture Support for Improving Bulk Memory Copying and Initialization Performance

Xiaowei Jiang, Yan Solihin

Dept. of Electrical and Computer Engineering

North Carolina State University

Raleigh, USA

Li Zhao, Ravishankar Iyer Intel Labs Intel Corporation Hillsboro, USA

## Starting Simple: Data Copy and Initialization

memmove & memcpy: 5% cycles in Google's datacenter [Kanev+ ISCA'I

VM Cloning Deduplicati

Zero initialization (e.g., security)

Page Migration

Checkpointi ng

## Today's Systems: Bulk Data Copy

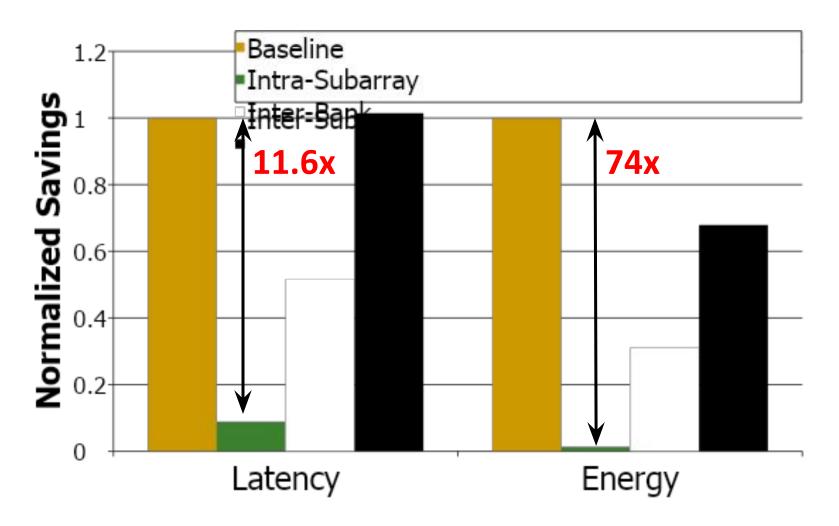

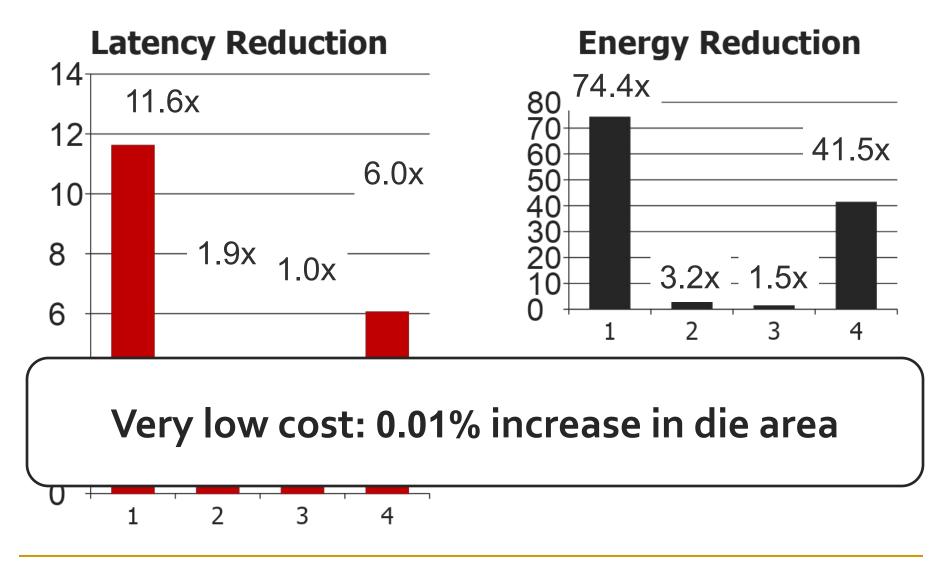

1046ns, 3.6uJ (for 4KB page copy via DMA)

## Future Systems: In-Memory Copy

- 1046ns, 3.6uJ

- □ 90ns, 0.04uJ

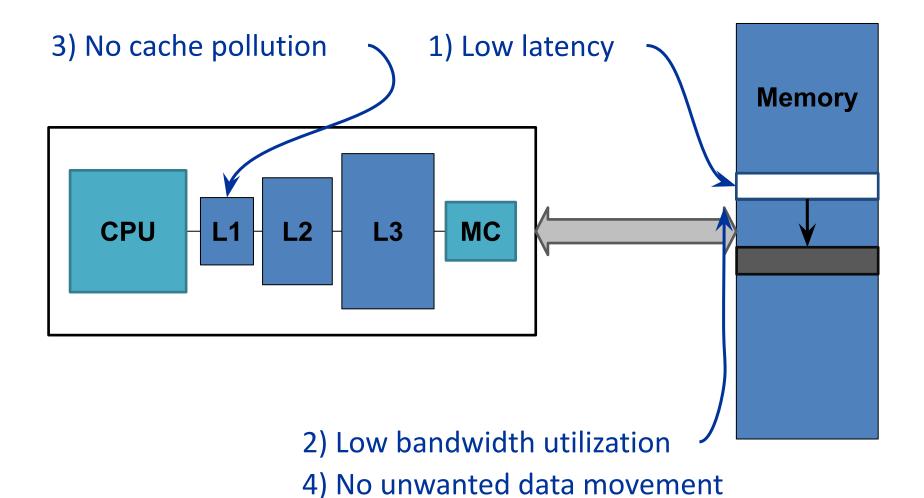

#### RowClone: In-DRAM Row Copy

11.6X latency reduction, 74X energy reduction

**DUS**

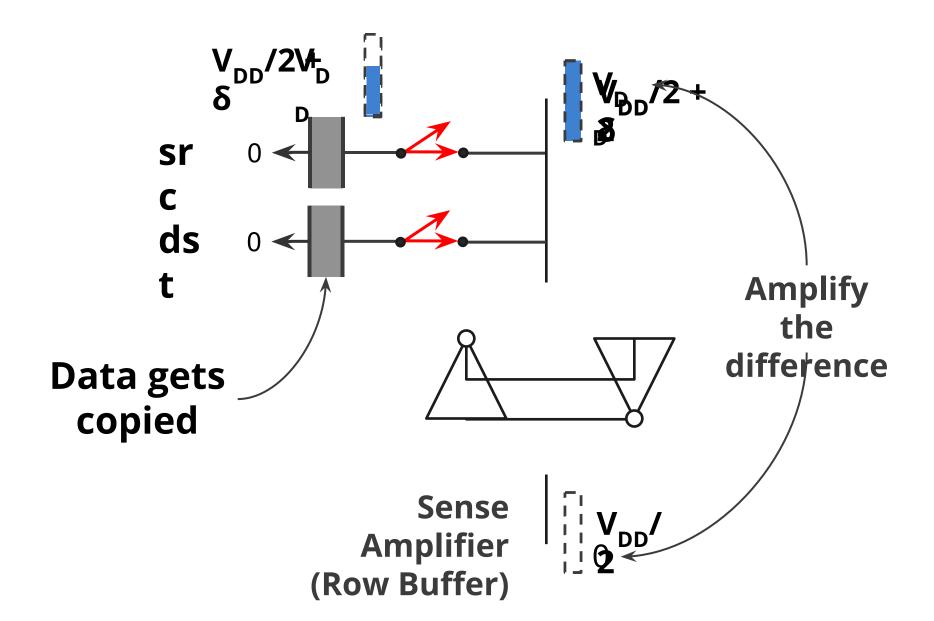

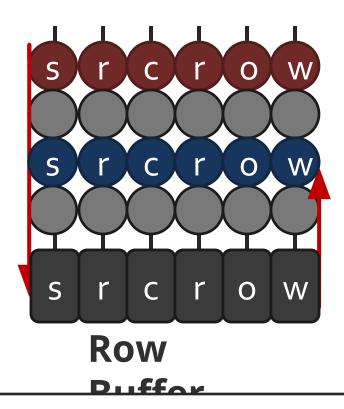

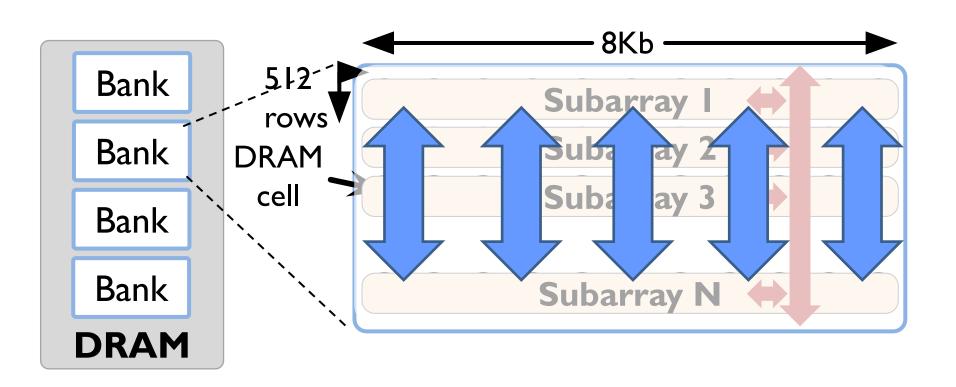

## RowClone: Intra-Subarray

## RowClone: Intra-Subarray (II)

- 1. Activate src row (copy data from src to row buffer)

- 2. **Activate** dst row (disconnect src from row buffer, connect dst copy data from row buffer to dst)

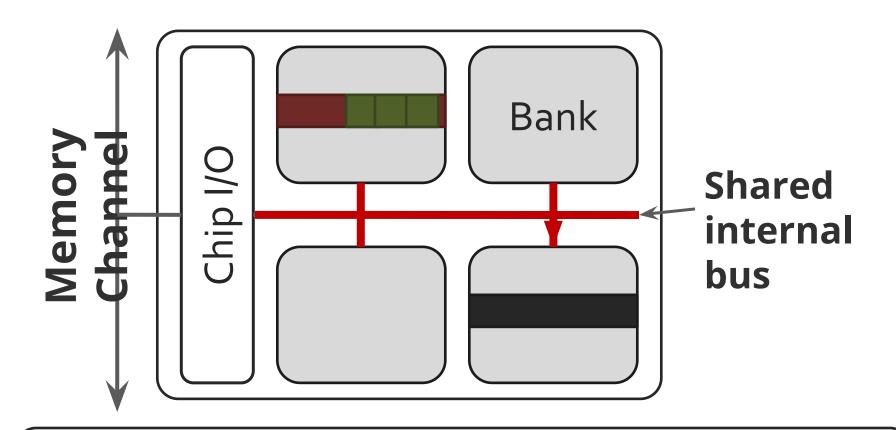

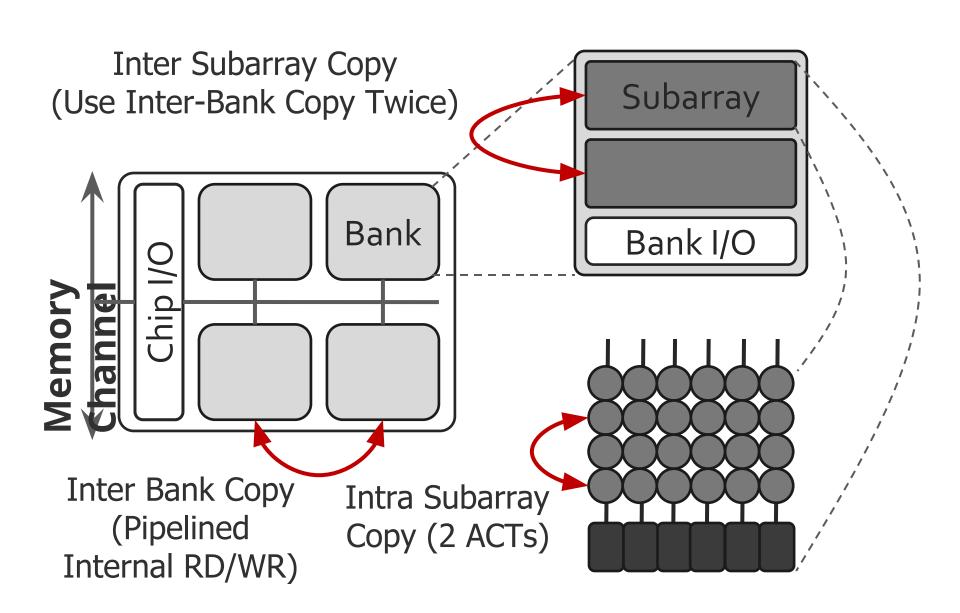

#### RowClone: Inter-Bank

Overlap the latency of the read and the write 1.9X latency reduction, 3.2X energy reduction

#### Generalized RowClone

#### 0.01% area cost

### RowClone: Latency and Energy Savings

Seshadri et al., "RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data," MICRO 2013.

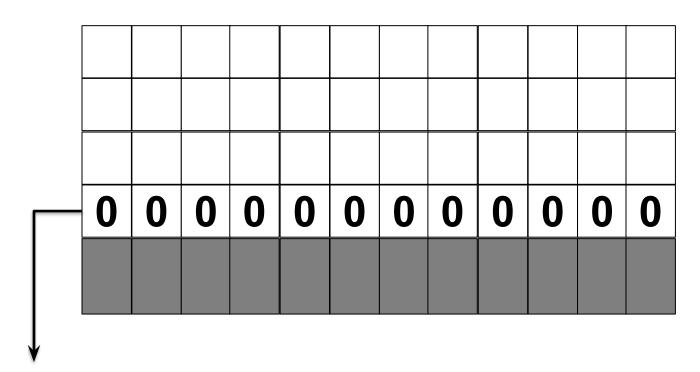

#### RowClone: Fast Row Initialization

Fix a row at Zero (0.5% loss in capacity)

#### RowClone: Bulk Initialization

- Initialization with arbitrary data

- Initialize one row

- Copy the data to other rows

- Zero initialization (most common)

- Reserve a row in each subarray (always zero)

- Copy data from reserved row (FPM mode)

- 6.0X lower latency, 41.5X lower DRAM energy

- □ 0.2% loss in capacity

#### RowClone: Latency & Energy Benefits

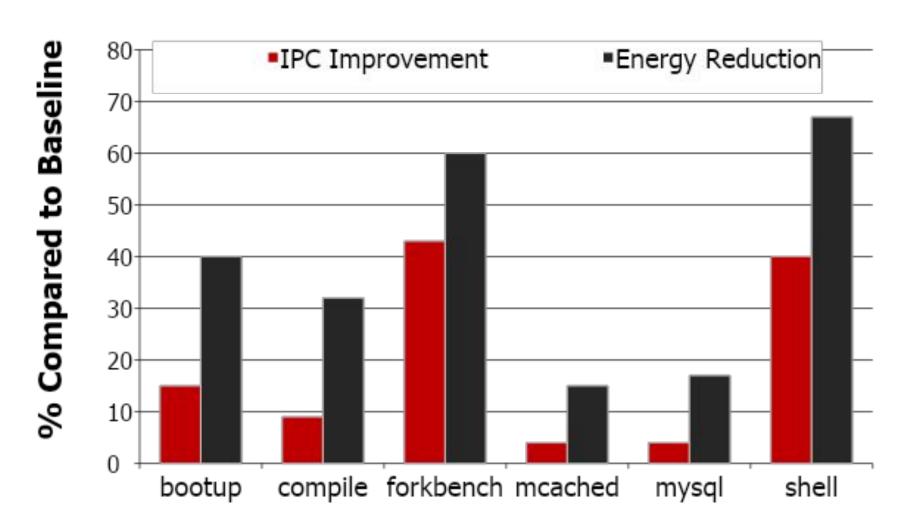

### Copy and Initialization in Workloads

### RowClone: Application Performance

## End-to-End System Design

**Application**

**Operating System**

ISA

Microarchitecture

DRAM (RowClone)

How to communicate occurrences of bulk copy/initialization across layers?

How to ensure cache coherence?

How to maximize latency and energy savings?

How to handle data reuse?

#### More on RowClone

Vivek Seshadri, Yoongu Kim, Chris Fallin, Donghyuk Lee, Rachata Ausavarungnirun, Gennady Pekhimenko, Yixin Luo, Onur Mutlu, Michael A. Kozuch, Phillip B. Gibbons, and Todd C. Mowry,

"RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization"

Proceedings of the <u>46th International Symposium on Microarchitecture</u> (**MICRO**), Davis, CA, December 2013. [<u>Slides (pptx) (pdf)</u>] [<u>Lightning Session Slides (pptx) (pdf)</u>] [<u>Poster (pptx) (pdf)</u>]

## RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization

Vivek Seshadri Yoongu Kim Chris Fallin\* Donghyuk Lee vseshadr@cs.cmu.edu yoongukim@cmu.edu cfallin@c1f.net donghyuk1@cmu.edu

Rachata Ausavarungnirun Gennady Pekhimenko Yixin Luo gpekhime@cs.cmu.edu yixinluo@andrew.cmu.edu

Onur Mutlu Phillip B. Gibbons† Michael A. Kozuch† Todd C. Mowry onur@cmu.edu phillip.b.gibbons@intel.com michael.a.kozuch@intel.com tcm@cs.cmu.edu

Carnegie Mellon University †Intel Pittsburgh

#### Lecture on RowClone & Processing using DRAM

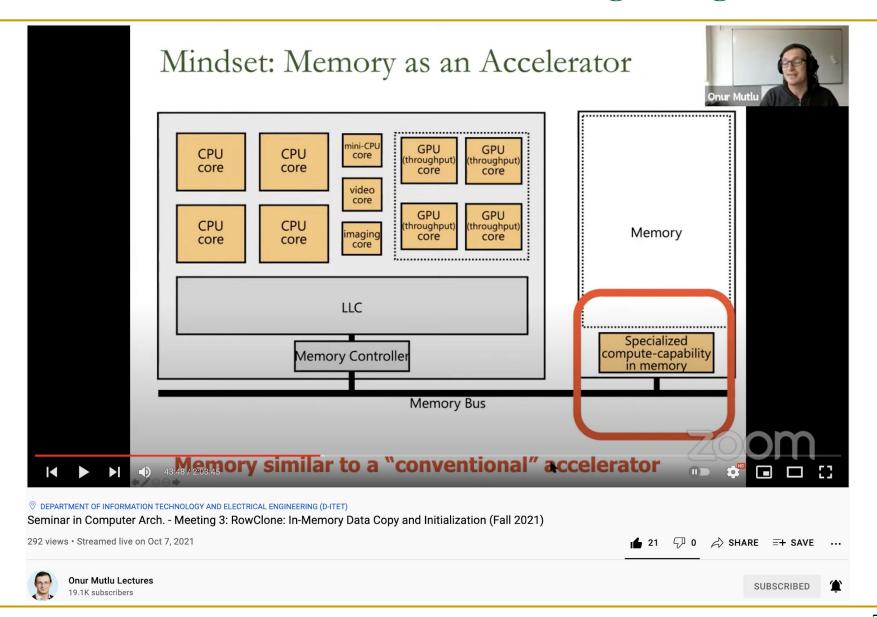

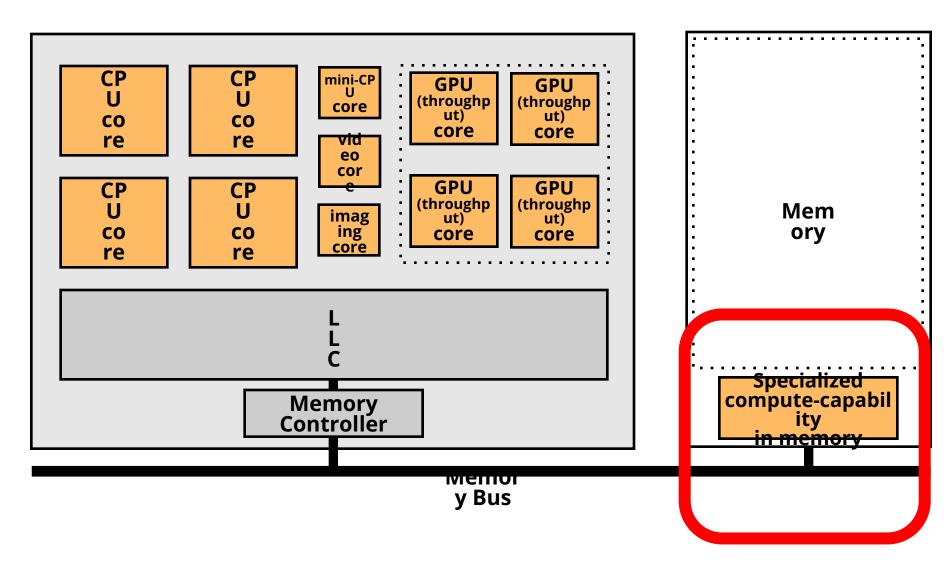

## Mindset: Memory as an Accelerator

Memory similar to a "conventional" accelerator

# RowClone Strengths

#### Strengths of the Paper

- Simple, novel mechanism to solve an important problem

- Effective and low hardware overhead

- Intuitive idea!

- Greatly improves performance and efficiency (assuming data is mapped nicely)

- Seems like a clear win for data initialization (without mapping requirements)

- Makes software designer's life easier

- If copies are 10x-100x cheaper, how to design software?

- Paper tackles many low-level and system-level issues

- Well-written, insightful paper

## RowClone Weaknesses

#### Weaknesses

- Requires data to be mapped in the same subarray to deliver the largest benefits

- Helps less if data movement is not within a subarray

- Does not help if data movement is across DRAM channels

- Inter-subarray copy is very inefficient

- Causes many changes in the system stack

- End-to-end design spans applications to circuits

- Software-hardware cooperative solution might not always be easy to adopt

- Cache coherence and data reuse cause real overheads

- Evaluation is done solely in simulation

- Evaluation does not consider multi-chip systems

- Are these the best workloads to evaluate?

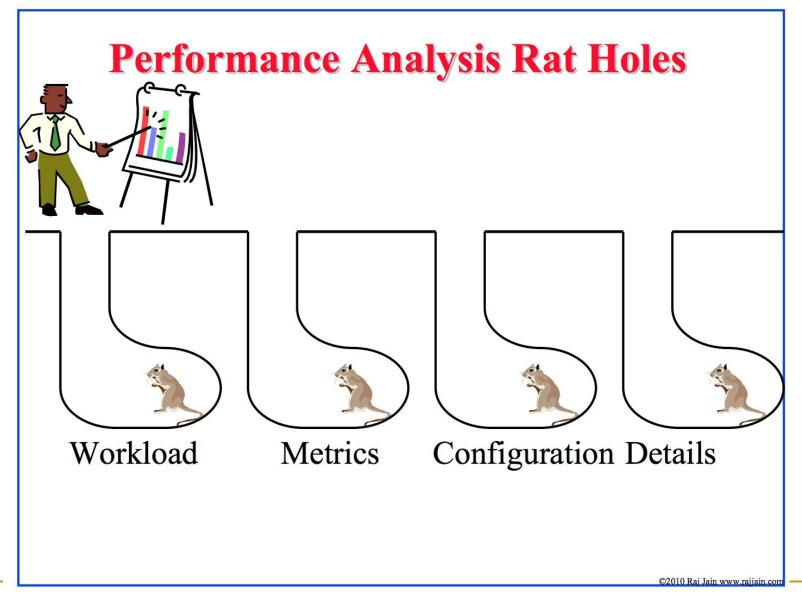

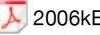

#### Recall: Try to Avoid Rat Holes

## Improvements on RowClone

#### RowClone Extensions and Follow-Up Work

- Can we do faster inter-subarray copy?

- Yes, see LISA [Chang et al., HPCA 2016]

- Can we enable data movement at smaller granularities within a bank?

- Yes, see FIGARO [Wang et al., MICRO 2020]

- Can we do better inter-bank copy?

- Yes, see Network-on-Memory [CAL 2020]

- Can similar ideas and DRAM properties be used to perform computation on data?

- Yes, see Ambit [Seshadri et al., CAL 2015, MICRO 2017]

## LISA: Increasing Connectivity in DRAM

Kevin K. Chang, Prashant J. Nair, Saugata Ghose, Donghyuk Lee, Moinuddin K. Qureshi, and Onur Mutlu, "Low-Cost Inter-Linked Subarrays (LISA): Enabling Fast

**Inter-Subarray Data Movement in DRAM**"

Proceedings of the <u>22nd International Symposium on</u>

<u>High-Performance Computer Architecture</u> (**HPCA**), Barcelona, Spain,

March 2016.

[Slides (pptx) (pdf)]

[Source Code]

#### Low-Cost Inter-Linked Subarrays (LISA): Enabling Fast Inter-Subarray Data Movement in DRAM

Kevin K. Chang<sup>†</sup>, Prashant J. Nair\*, Donghyuk Lee<sup>†</sup>, Saugata Ghose<sup>†</sup>, Moinuddin K. Qureshi\*, and Onur Mutlu<sup>†</sup>

†Carnegie Mellon University \*Georgia Institute of Technology

#### **Moving Data Inside DRAM?**

Goal: Provide a new substrate to enable wide connectivity between subarrays

#### **Key Idea and Applications**

- Low-cost Inter-linked subarrays (LISA)

- Fast bulk data movement between subarrays

- Wide datapath via isolation transistors: 0.8% DRAM chip area

LISA is a versatile substrate → new applications

Fast bulk data copy: Copy latency  $1.363 \text{ms} \rightarrow 0.148 \text{ms}$  (9.2x)

→ 66% speedup, -55% DRAM energy

In-DRAM caching: Hot data access latency 48.7ns→21.5ns (2.2x)

→ 5% speedup

Fast precharge: Precharge latency 13.1ns→5.0ns (2.6x)

→ 8% speedup

#### More on LISA

Kevin K. Chang, Prashant J. Nair, Saugata Ghose, Donghyuk Lee, Moinuddin K. Qureshi, and Onur Mutlu, "Low-Cost Inter-Linked Subarrays (LISA): Enabling Fast Inter-Subarray Data Movement in DRAM" Proceedings of the <u>22nd International Symposium on</u> <u>High-Performance Computer Architecture</u> (HPCA), Barcelona, Spain, March 2016.

[Slides (pptx) (pdf)] [Source Code]

#### Low-Cost Inter-Linked Subarrays (LISA): Enabling Fast Inter-Subarray Data Movement in DRAM

Kevin K. Chang<sup>†</sup>, Prashant J. Nair\*, Donghyuk Lee<sup>†</sup>, Saugata Ghose<sup>†</sup>, Moinuddin K. Qureshi\*, and Onur Mutlu<sup>†</sup>

†Carnegie Mellon University \*Georgia Institute of Technology

### FIGARO: Fine-Grained In-DRAM Copy

Yaohua Wang, Lois Orosa, Xiangjun Peng, Yang Guo, Saugata Ghose, Minesh Patel, Jeremie S. Kim, Juan Gómez Luna, Mohammad Sadrosadati, Nika Mansouri Ghiasi, and Onur Mutlu, "FIGARO: Improving System Performance via Fine-Grained In-DRAM Data Relocation and Caching"

Proceedings of the <u>53rd International Symposium on Microarchitecture</u> (MICRO), Virtual, October 2020.

## FIGARO: Improving System Performance via Fine-Grained In-DRAM Data Relocation and Caching

Yaohua Wang\* Lois Orosa<sup>†</sup> Xiangjun Peng<sup>⊙</sup>\* Yang Guo\* Saugata Ghose<sup>◇‡</sup> Minesh Patel<sup>†</sup> Jeremie S. Kim<sup>†</sup> Juan Gómez Luna<sup>†</sup> Mohammad Sadrosadati<sup>§</sup> Nika Mansouri Ghiasi<sup>†</sup> Onur Mutlu<sup>†‡</sup>

\*National University of Defense Technology  $^{\dagger}$ ETH Zürich  $^{\odot}$ Chinese University of Hong Kong  $^{\diamond}$ University of Illinois at Urbana–Champaign  $^{\ddagger}$ Carnegie Mellon University  $^{\S}$ Institute of Research in Fundamental Sciences

#### Network-On-Memory: Fast Inter-Bank Copy

Seyyed Hossein SeyyedAghaei Rezaei, Mehdi Modarressi, Rachata Ausavarungnirun, Mohammad Sadrosadati, Onur Mutlu, and Masoud Daneshtalab,

"NoM: Network-on-Memory for Inter-Bank Data Transfer in Highly-Banked Memories"

<u>IEEE Computer Architecture Letters</u> (CAL), to appear in 2020.

#### NoM: Network-on-Memory for Inter-bank Data Transfer in Highly-banked Memories

Seyyed Hossein SeyyedAghaei Rezaei<sup>1</sup>

Mohammad Sadrosadati<sup>3</sup>

Mehdi Modarressi<sup>1,3</sup> Rachata Ausavarungnirun<sup>2</sup> Onur Mutlu<sup>4</sup> Masoud Daneshtalab<sup>5</sup>

<sup>1</sup>University of Tehran

<sup>2</sup>King Mongkut's University of Technology North Bangkok <sup>3</sup>Institute for Research in Fundamental Sciences <sup>4</sup>ETH Zürich <sup>5</sup>Mälardalens University

## Mindset: Memory as an Accelerator

Memory similar to a "conventional" accelerator

#### In-DRAM Bulk Bitwise AND/OR

Vivek Seshadri, Kevin Hsieh, Amirali Boroumand, Donghyuk Lee, Michael A. Kozuch, Onur Mutlu, Phillip B. Gibbons, and Todd C. Mowry,

"Fast Bulk Bitwise AND and OR in DRAM"

IEEE Computer Architecture Letters (CAL), April 2015.

#### Fast Bulk Bitwise AND and OR in DRAM

Vivek Seshadri\*, Kevin Hsieh\*, Amirali Boroumand\*, Donghyuk Lee\*, Michael A. Kozuch<sup>†</sup>, Onur Mutlu\*, Phillip B. Gibbons<sup>†</sup>, Todd C. Mowry\*

\*Carnegie Mellon University †Intel Pittsburgh

### Ambit: Bulk-Bitwise in-DRAM Computation

Vivek Seshadri, Donghyuk Lee, Thomas Mullins, Hasan Hassan, Amirali Boroumand, Jeremie Kim, Michael A. Kozuch, Onur Mutlu, Phillip B. Gibbons, and Todd C. Mowry,

"Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology"

Proceedings of the 50th International Symposium on

Microarchitecture (MICRO), Boston, MA, USA, October 2017.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Poster (pptx) (pdf)]

Ambit: In-Memory Accelerator for Bulk Bitwise Operations

Using Commodity DRAM Technology

Vivek Seshadri $^{1,5}$  Donghyuk Lee $^{2,5}$  Thomas Mullins $^{3,5}$  Hasan Hassan $^4$  Amirali Boroumand $^5$  Jeremie Kim $^{4,5}$  Michael A. Kozuch $^3$  Onur Mutlu $^{4,5}$  Phillip B. Gibbons $^5$  Todd C. Mowry $^5$

$^1$ Microsoft Research India  $^2$ NVIDIA Research  $^3$ Intel  $^4$ ETH Zürich  $^5$ Carnegie Mellon University

#### In-DRAM Bulk Bitwise Execution Paradigm

Vivek Seshadri and Onur Mutlu, "In-DRAM Bulk Bitwise Execution Engine"

Invited Book Chapter in Advances in Computers, to appear in 2020.

[Preliminary arXiv version]

#### In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

#### SIMDRAM Framework for in-DRAM Computing

Nastaran Hajinazar, Geraldo F. Oliveira, Sven Gregorio, Joao Dinis Ferreira, Nika Mansouri Ghiasi, Minesh Patel, Mohammed Alser, Saugata Ghose, Juan Gomez-Luna, and Onur Mutlu, "SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Computing in DRAM" Proceedings of the 26th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Virtual, March-April 2021.

[2-page Extended Abstract]

Short Talk Slides (pptx) (pdf)

[Talk Slides (pptx) (pdf)]

[Short Talk Video (5 mins)]

[Full Talk Video (27 mins)]

## SIMDRAM: A Framework for Bit-Serial SIMD Processing using DRAM

\*Nastaran Hajinazar<sup>1,2</sup> Nika Mansouri Ghiasi<sup>1</sup> \*Geraldo F. Oliveira<sup>1</sup>

Minesh Patel<sup>1</sup>

Juan Gómez-Luna<sup>1</sup>

Sven Gregorio<sup>1</sup> Mohammed Alser<sup>1</sup> Onur Mutlu<sup>1</sup>

João Dinis Ferreira<sup>1</sup> Saugata Ghose<sup>3</sup>

<sup>1</sup>ETH Zürich

<sup>2</sup>Simon Fraser University

<sup>3</sup>University of Illinois at Urbana–Champaign

# Extensions and Follow-Up Work (II)

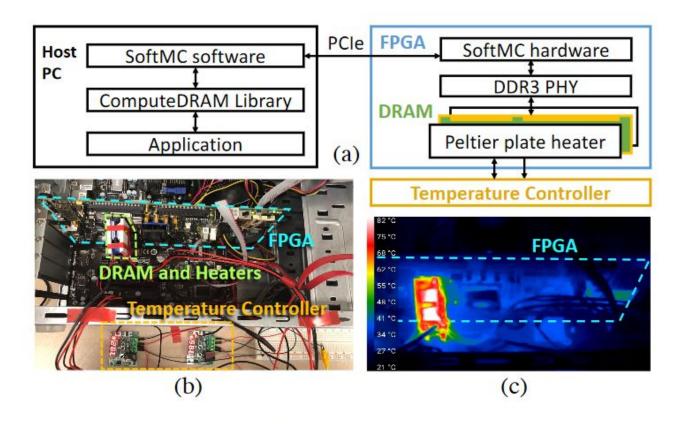

- Can this idea be evaluated on a real system? How?

- Yes, see the ComputeDRAM paper [MICRO 2019]

- Can similar ideas be used in other types of memories? Phase Change Memory? RRAM? STT-MRAM?

- Yes, see the Pinatubo paper [DAC 2016]

- Can charge sharing properties be used for other functions?

- Yes, see the D-RaNGe [HPCA 2019], DL-PUF [HPCA 2018],

QUAC-TRNG [ISCA 2021] works on random numbers & PUFs

- Can we have more efficient solutions to

- Cache coherence (minimize overhead)

- Data reuse after copy and initialization

#### RowClone Demonstration in Real DRAM Chips

# ComputeDRAM: In-Memory Compute Using Off-the-Shelf DRAMs

Fei Gao feig@princeton.edu Department of Electrical Engineering Princeton University Georgios Tziantzioulis georgios.tziantzioulis@princeton.edu Department of Electrical Engineering Princeton University David Wentzlaff wentzlaf@princeton.edu Department of Electrical Engineering Princeton University

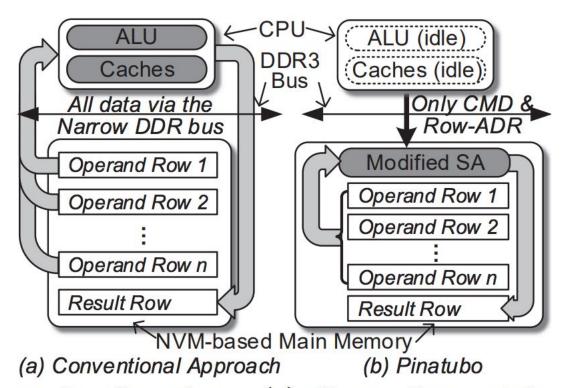

## Pinatubo: PCM RowClone and Bitwise Ops

# Pinatubo: A Processing-in-Memory Architecture for Bulk Bitwise Operations in Emerging Non-volatile Memories

Shuangchen Li<sup>1</sup>\*, Cong Xu<sup>2</sup>, Qiaosha Zou<sup>1,5</sup>, Jishen Zhao<sup>3</sup>, Yu Lu<sup>4</sup>, and Yuan Xie<sup>1</sup>

University of California, Santa Barbara<sup>1</sup>, Hewlett Packard Labs<sup>2</sup> University of California, Santa Cruz<sup>3</sup>, Qualcomm Inc.<sup>4</sup>, Huawei Technologies Inc.<sup>5</sup> {shuangchenli, yuanxie}ece.ucsb.edu<sup>1</sup>

# Takeaways

# Key Takeaways

- A novel method to accelerate data copy and initialization

- Simple and effective

- Hardware/software cooperative

- Good potential for work building on it to extend it

- To different granularities

- To make things more efficient and effective

- Many works have already built on the paper (see LISA, FIGARO, NoM, Ambit, ComputeDRAM, and other works in Google Scholar)

- Easy to read and understand paper

# RowClone: Memory as an

Memory similar to a "conventional" accelerator

# Mindset: Processing using DRAM

- DRAM has great capability to perform bulk data movement and computation internally with small changes

- Can exploit internal connectivity to move data

- Can exploit analog computation capability

- **...**

- Examples: RowClone, In-DRAM AND/OR, Gather/Scatter DRAM

- RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data (Seshadri et al., MICRO 2013)

- <u>Fast Bulk Bitwise AND and OR in DRAM</u> (Seshadri et al., IEEE CAL 2015)

- Gather-Scatter DRAM: In-DRAM Address Translation to Improve the Spatial Locality of Non-unit Strided Accesses (Seshadri et al., MICRO 2015)

- "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity

DRAM Technology" (Seshadri et al., MICRO 2017)

# In-Memory Bulk Bitwise Operations

# In-Memory Bulk Bitwise Operations

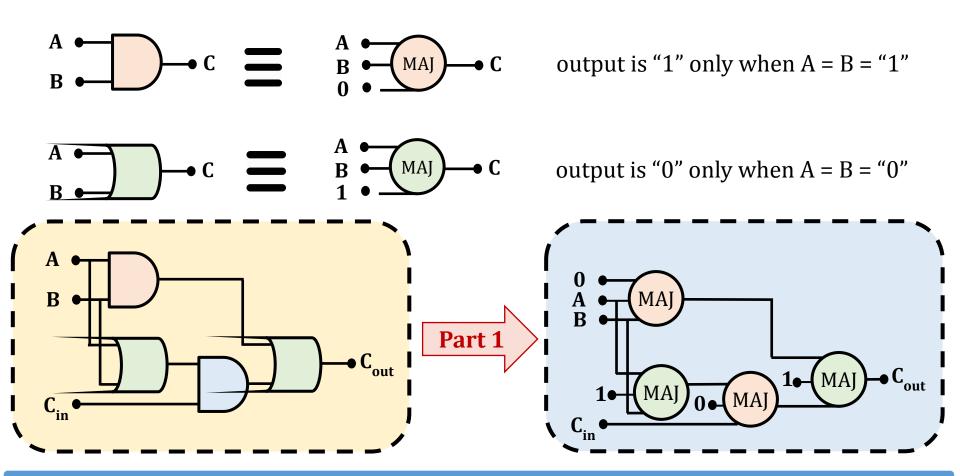

- We can support in-DRAM COPY, ZERO, AND, OR, NOT, MAJ

- At low cost

- Using inherent analog computation capability of DRAM

- Idea: activating multiple rows performs computation

- 30-60X performance and energy improvement

- Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology," MICRO 2017.

- New memory technologies enable even more opportunities

- Memristors, resistive RAM, phase change mem, STT-MRAM, ...

- Can operate on data with minimal movement

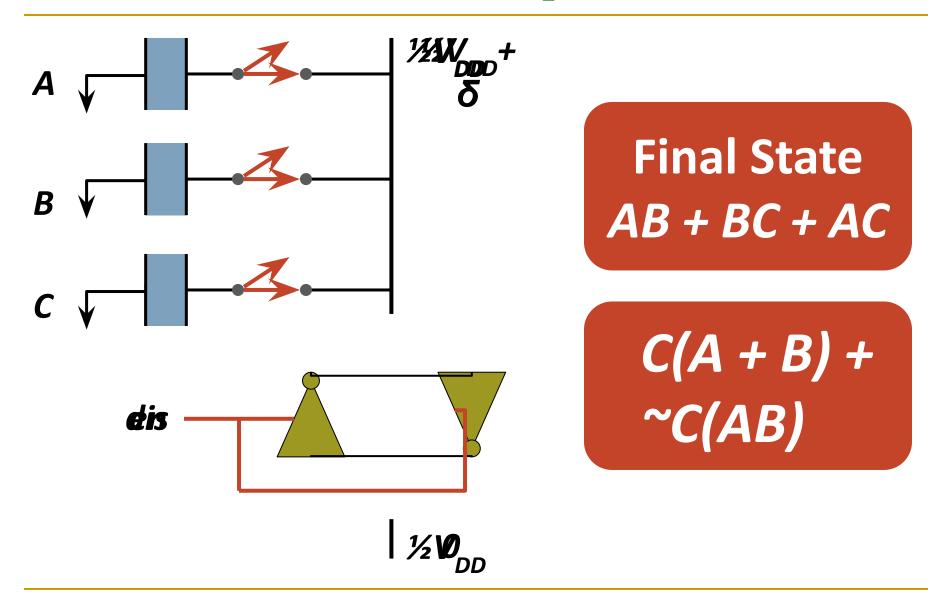

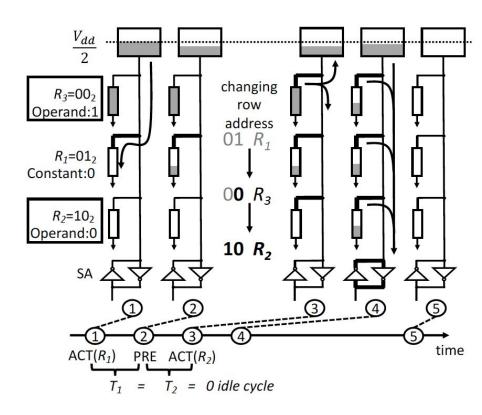

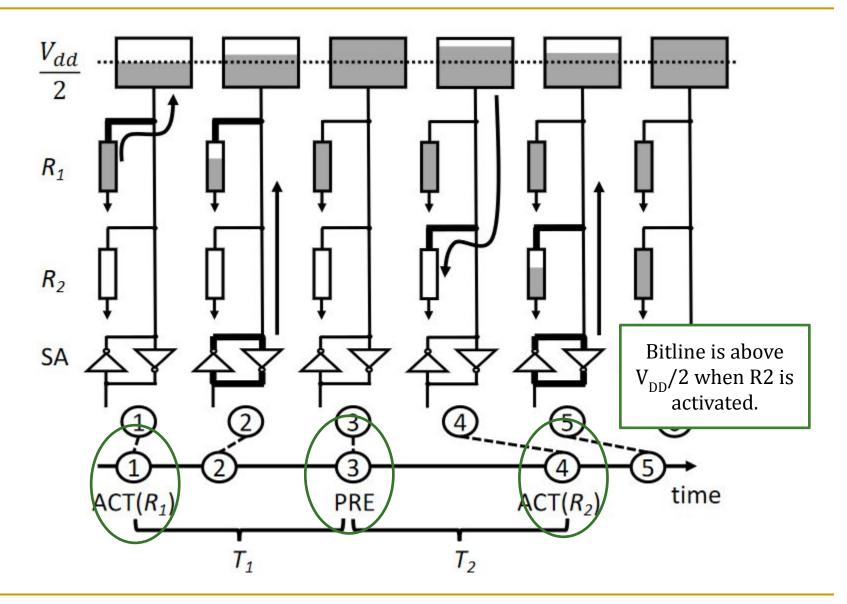

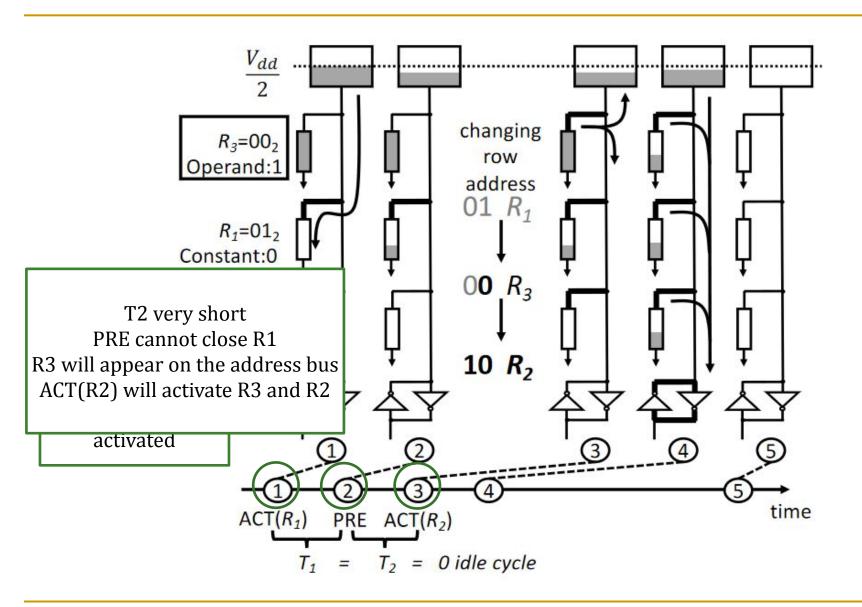

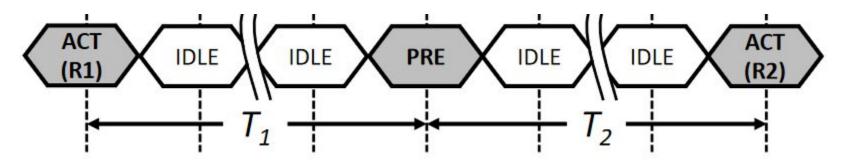

# In-DRAM AND/OR: Triple Row Activation

#### In-DRAM Bulk Bitwise AND/OR Operation

- BULKAND A, B □ C

- Semantics: Perform a bitwise AND of two rows A and B and store the result in row C

- R0 reserved zero row, R1 reserved one row

- D1, D2, D3 Designated rows for triple activation

- 1. RowClone A into D1

- 2. RowClone B into D2

- 3. RowClone R0 into D3

- 4. ACTIVATE D1,D2,D3

- 5. RowClone Result into C

#### More on In-DRAM Bulk AND/OR

Vivek Seshadri, Kevin Hsieh, Amirali Boroumand, Donghyuk Lee, Michael A. Kozuch, Onur Mutlu, Phillip B. Gibbons, and Todd C. Mowry,

"Fast Bulk Bitwise AND and OR in DRAM"

IEEE Computer Architecture Letters (CAL), April 2015.

#### Fast Bulk Bitwise AND and OR in DRAM

Vivek Seshadri\*, Kevin Hsieh\*, Amirali Boroumand\*, Donghyuk Lee\*, Michael A. Kozuch<sup>†</sup>, Onur Mutlu\*, Phillip B. Gibbons<sup>†</sup>, Todd C. Mowry\*

\*Carnegie Mellon University †Intel Pittsburgh

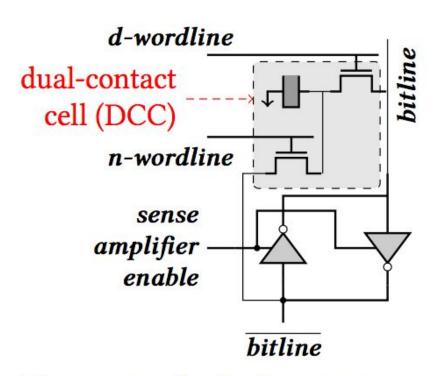

#### In-DRAM NOT: Dual Contact Cell

Figure 5: A dual-contact cell connected to both ends of a sense amplifier

Idea:

Feed the

negated value

in the sense amplifier

into a special row

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

# In-DRAM NOT Operation

Figure 5: Bitwise NOT using a dual contact capacitor

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

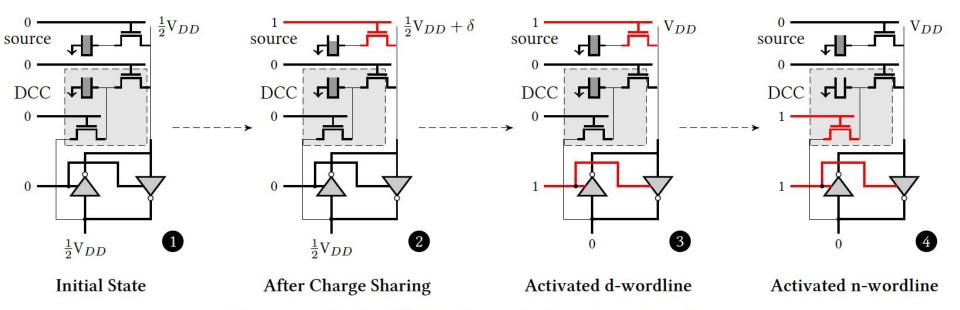

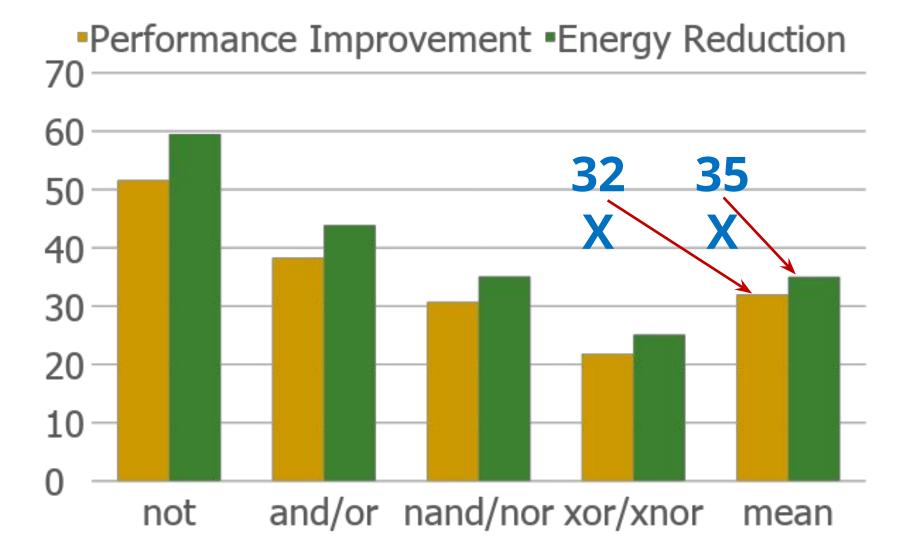

# Performance: In-DRAM Bitwise Operations

Figure 9: Throughput of bitwise operations on various systems.

# Energy of In-DRAM Bitwise Operations

|                | Design         | not   | and/or | nand/nor | xor/xnor |

|----------------|----------------|-------|--------|----------|----------|

| DRAM &         | DDR3           | 93.7  | 137.9  | 137.9    | 137.9    |

| Channel Energy | <b>Ambit</b>   | 1.6   | 3.2    | 4.0      | 5.5      |

| (nJ/KB)        | $(\downarrow)$ | 59.5X | 43.9X  | 35.1X    | 25.1X    |

Table 3: Energy of bitwise operations.  $(\downarrow)$  indicates energy reduction of Ambit over the traditional DDR3-based design.

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

# Ambit vs. DDR3: Performance and **Energy**

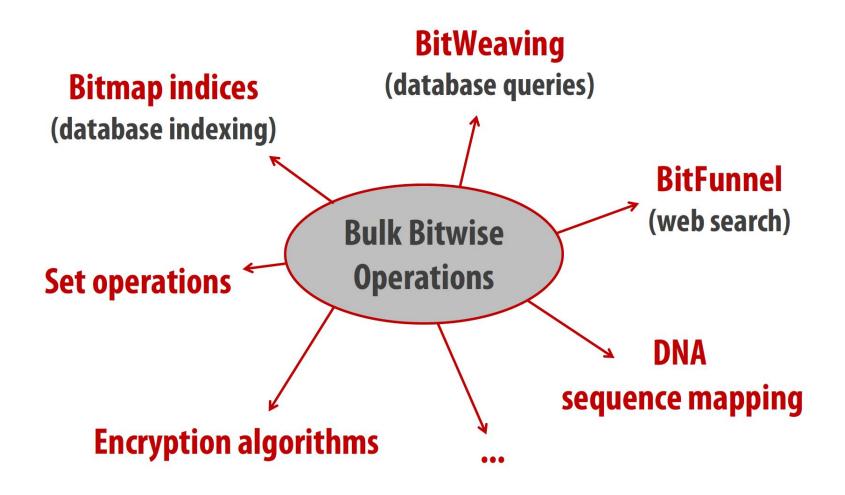

# Bulk Bitwise Operations in Workloads

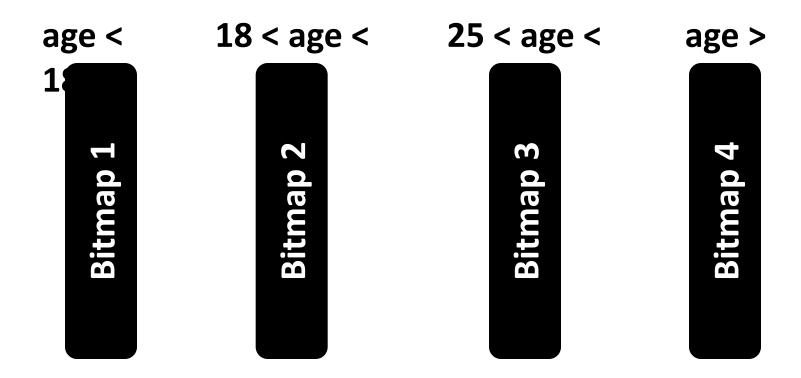

# Example Data Structure: Bitmap Index

- Alternative to B-tree and its variants

- Efficient for performing range queries and joins

- Many bitwise operations to perform a query

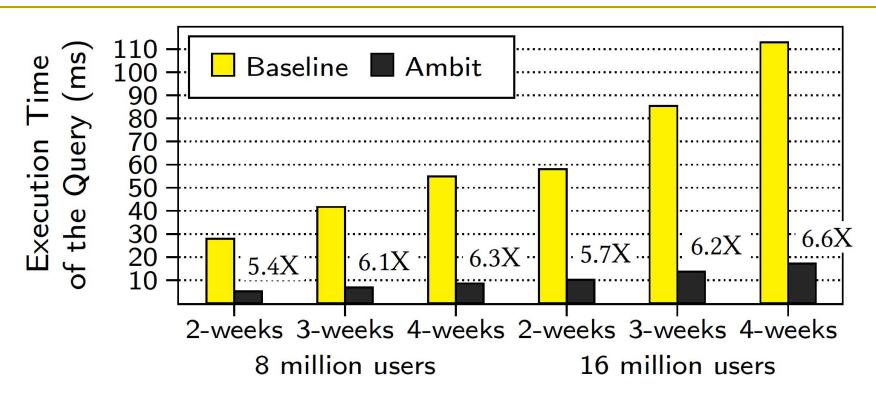

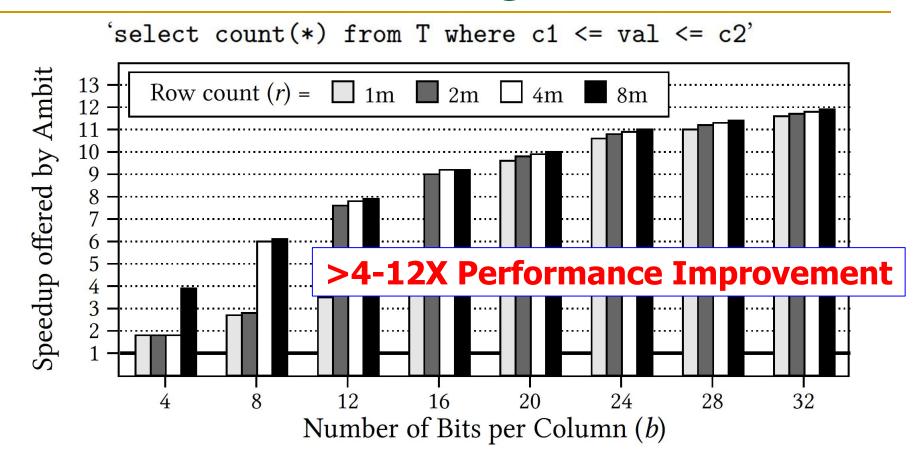

# Performance: Bitmap Index on Ambit

Figure 10: Bitmap index performance. The value above each bar indicates the reduction in execution time due to Ambit.

>5.4-6.6X Performance Improvement

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO

SAFARI

# Performance: BitWeaving on Ambit

Figure 11: Speedup offered by Ambit over baseline CPU with SIMD for BitWeaving

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

#### More on In-DRAM Bulk AND/OR

Vivek Seshadri, Kevin Hsieh, Amirali Boroumand, Donghyuk Lee, Michael A. Kozuch, Onur Mutlu, Phillip B. Gibbons, and Todd C. Mowry,

"Fast Bulk Bitwise AND and OR in DRAM"

IEEE Computer Architecture Letters (CAL), April 2015.

#### Fast Bulk Bitwise AND and OR in DRAM

Vivek Seshadri\*, Kevin Hsieh\*, Amirali Boroumand\*, Donghyuk Lee\*, Michael A. Kozuch<sup>†</sup>, Onur Mutlu\*, Phillip B. Gibbons<sup>†</sup>, Todd C. Mowry\*

\*Carnegie Mellon University †Intel Pittsburgh

# More on In-DRAM Bitwise Operations

Vivek Seshadri et al., "<u>Ambit: In-Memory Accelerator</u> for Bulk Bitwise Operations Using Commodity DRAM <u>Technology</u>," MICRO 2017.

Ambit: In-Memory Accelerator for Bulk Bitwise Operations

Using Commodity DRAM Technology

```

Vivek Seshadri^{1,5} Donghyuk Lee^{2,5} Thomas Mullins^{3,5} Hasan Hassan^4 Amirali Boroumand^5 Jeremie Kim^{4,5} Michael A. Kozuch^3 Onur Mutlu^{4,5} Phillip B. Gibbons^5 Todd C. Mowry^5

```

$^1$ Microsoft Research India  $^2$ NVIDIA Research  $^3$ Intel  $^4$ ETH Zürich  $^5$ Carnegie Mellon University

#### More on In-DRAM Bulk Bitwise Execution

Vivek Seshadri and Onur Mutlu, "In-DRAM Bulk Bitwise Execution Engine"

Invited Book Chapter in Advances in Computers, to appear in 2020.

[Preliminary arXiv version]

#### In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

#### SIMDRAM Framework

Nastaran Hajinazar, Geraldo F. Oliveira, Sven Gregorio, Joao Dinis Ferreira, Nika Mansouri Ghiasi, Minesh Patel, Mohammed Alser, Saugata Ghose, Juan Gomez-Luna, and Onur Mutlu, "SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Computing in DRAM" Proceedings of the 26th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Virtual, March-April 2021.

2-page Extended Abstract

Short Talk Slides (pptx) (pdf)

[Talk Slides (pptx) (pdf)]

[Short Talk Video (5 mins)]

[Full Talk Video (27 mins)]

# SIMDRAM: A Framework for Bit-Serial SIMD Processing using DRAM

\*Nastaran Hajinazar<sup>1,2</sup> Nika Mansouri Ghiasi<sup>1</sup> \*Geraldo F. Oliveira<sup>1</sup> Minesh Patel<sup>1</sup> Juan Gómez-Luna<sup>1</sup> Sven Gregorio<sup>1</sup> Mohammed Alser<sup>1</sup> Onur Mutlu<sup>1</sup>

João Dinis Ferreira<sup>1</sup> Saugata Ghose<sup>3</sup>

<sup>1</sup>ETH Zürich

<sup>2</sup>Simon Fraser University

<sup>3</sup>University of Illinois at Urbana-Champaign

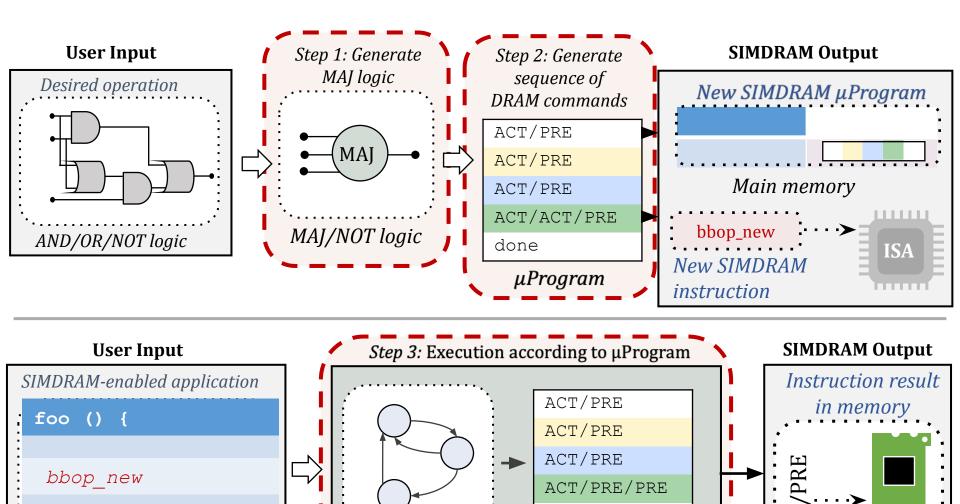

# SIMDRAM Key Idea

- **SIMDRAM**: An end-to-end processing-using-DRAM framework that provides the programming interface, the ISA, and the hardware support for:

- Efficiently computing complex operations in DRAM

- Providing the ability to implement **arbitrary** operations as required

- Using an **in-DRAM massively-parallel SIMD substrate** that requires **minimal** changes to DRAM architecture

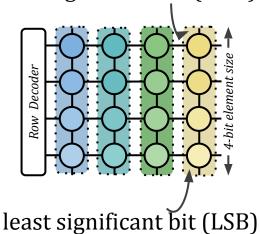

#### SIMDRAM: PuM Substrate

• SIMDRAM framework is built around a DRAM substrate that enables two techniques:

#### (1) Vertical data layout

most significant bit (MSB)

# Pros compared to the conventional horizontal layout:

- Implicit shift operation

- Massive parallelism

#### SAFARI

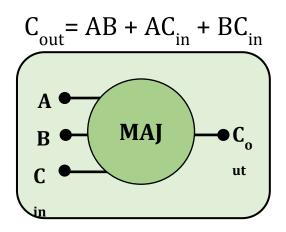

#### (2) Majority-based computation

# Pros compared to AND/OR/NOT-based computation:

- Higher performance

- Higher throughput

- Lower energy consumption

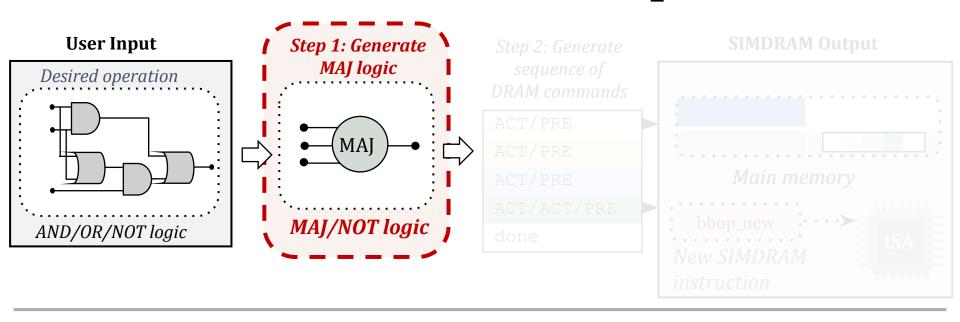

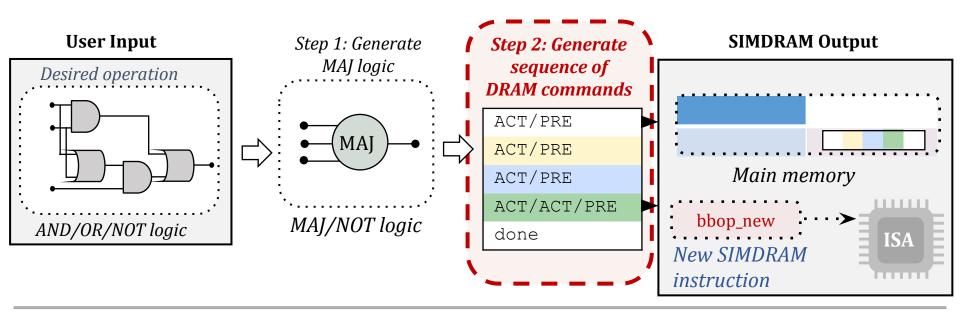

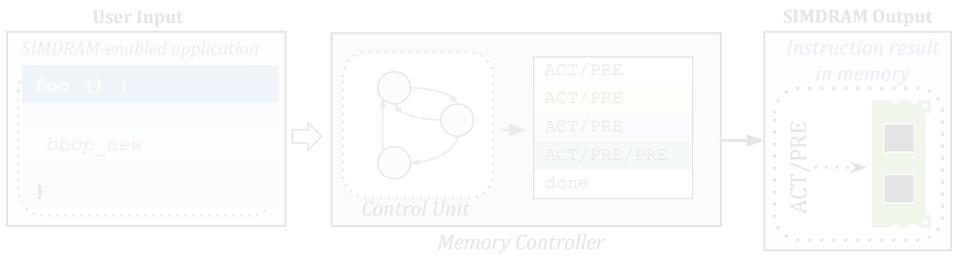

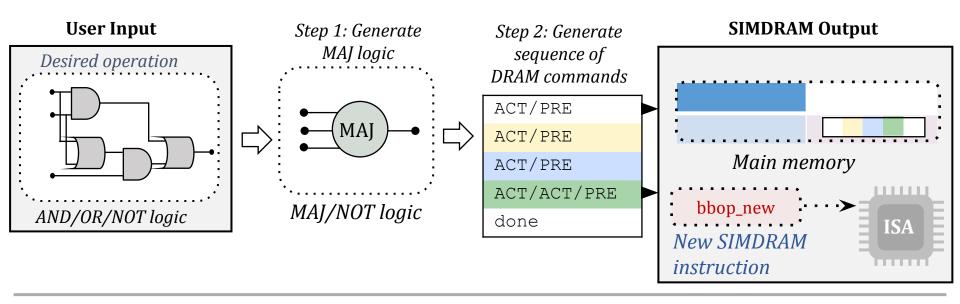

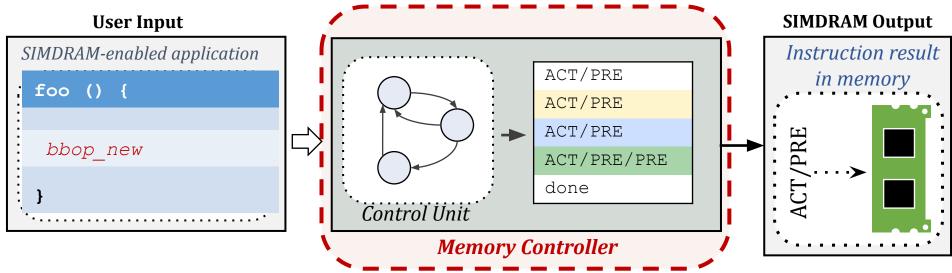

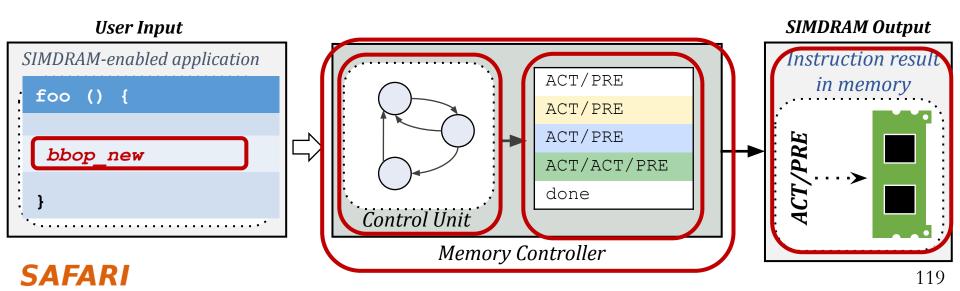

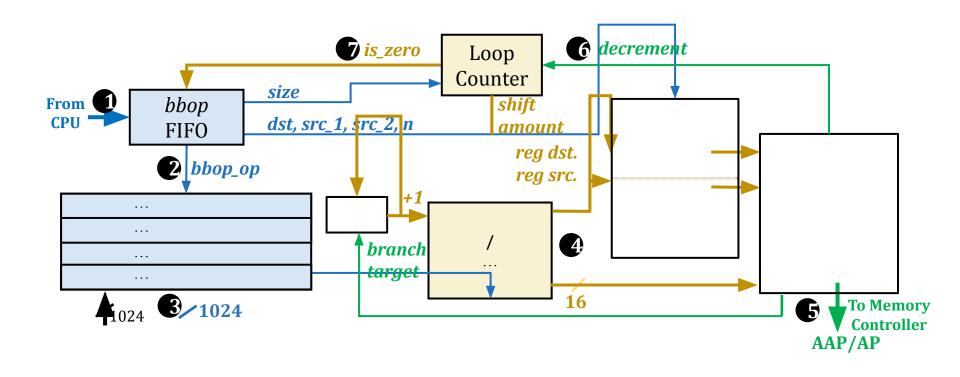

#### SIMDRAM Framework: Overview

Control Unit

ACT/PRE/PRE

μProgram

done

Memory Controller

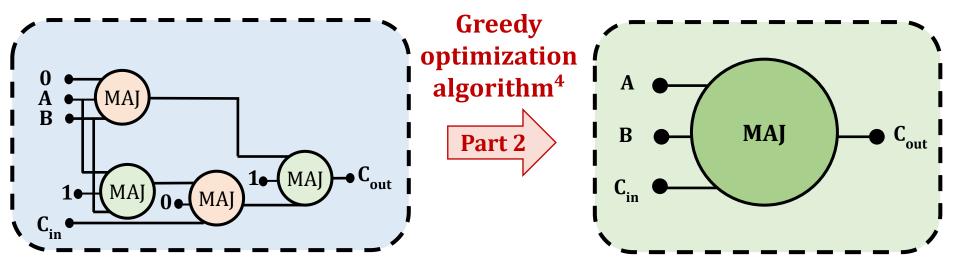

# SIMDRAM Framework: Step 1

#### Step 1: Naïve MAJ/NOT Implementation

Naïvely converting AND/OR/NOT-implementation to MAJ/NOT-implementation leads to an unoptimized circuit

## Step 1: Efficient MAJ/NOT Implementation

Step 1 generates an optimized MAJ/NOT-implementation of the desired operation

<sup>&</sup>lt;sup>4</sup> L. Amarù et al, "Majority-Inverter Graph: A Novel Data-Structure and Algorithms for Efficient Logic Optimization", DAC, 2014.

# SIMDRAM Framework: Step 2

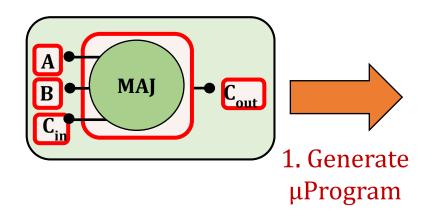

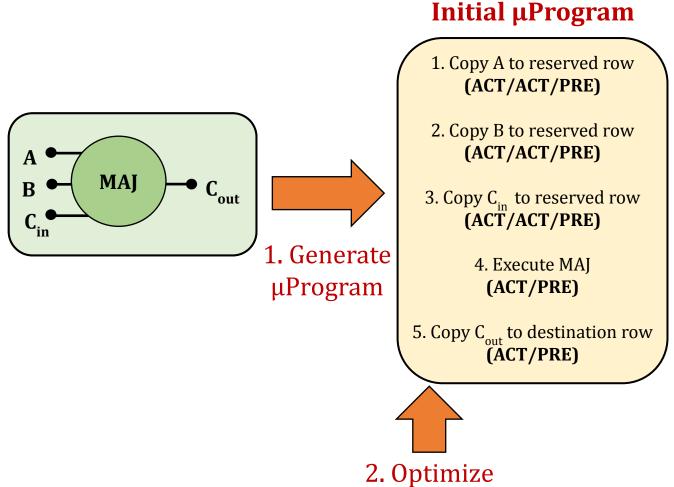

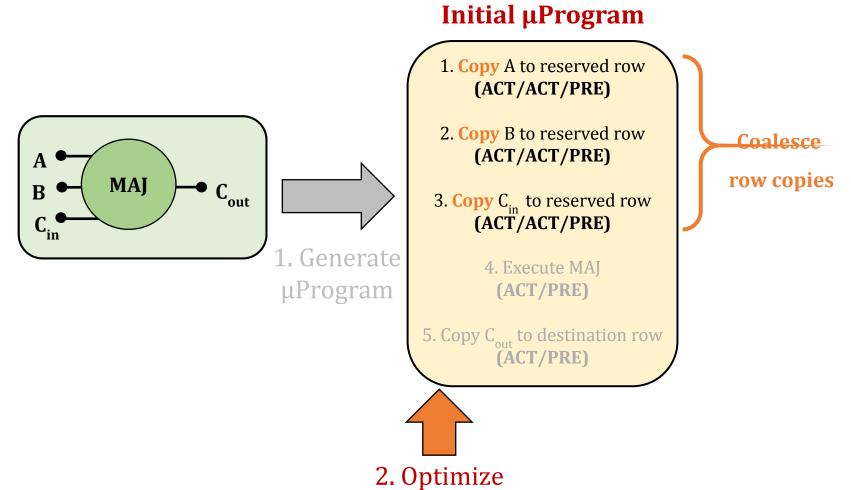

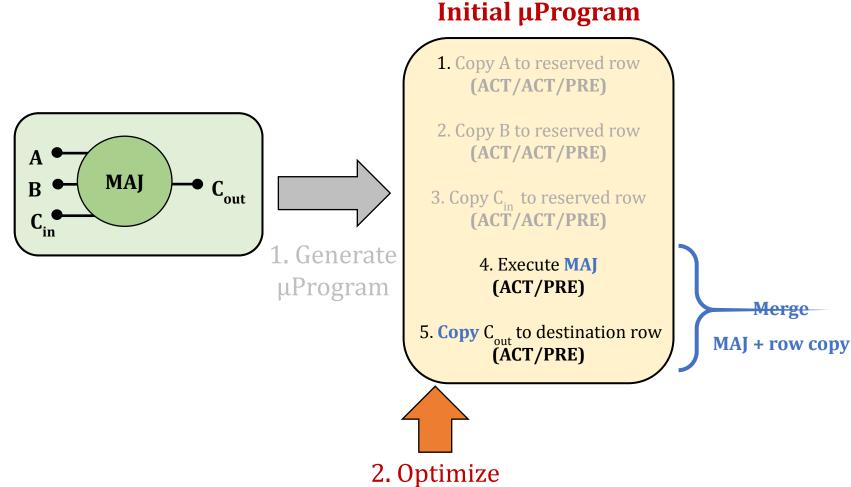

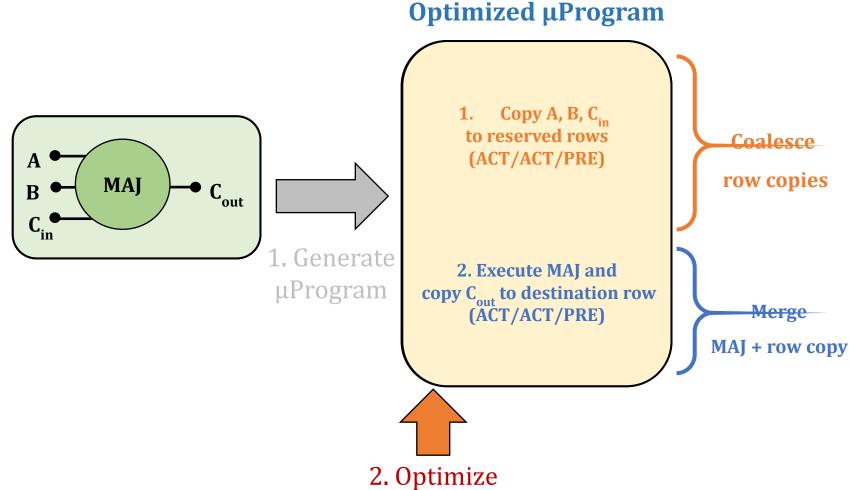

# Step 2: µProgram Generation

• **µProgram:** A series of microarchitectural operations (e.g., ACT/PRE) that SIMDRAM uses to execute SIMDRAM operation in DRAM

• Goal of Step 2: To generate the µProgram that executes the desired SIMDRAM operation in DRAM

Task 1: Allocate DRAM rows to the operands

Task 2: Generate μProgram

# Step 2: µProgram Generation

• **µProgram:** A series of microarchitectural operations (e.g., ACT/PRE) that SIMDRAM uses to execute SIMDRAM operation in DRAM

• Goal of Step 2: To generate the µProgram that executes the desired SIMDRAM operation in DRAM

Task 1: Allocate DRAM rows to the operands

Task 2: Generate μProgram

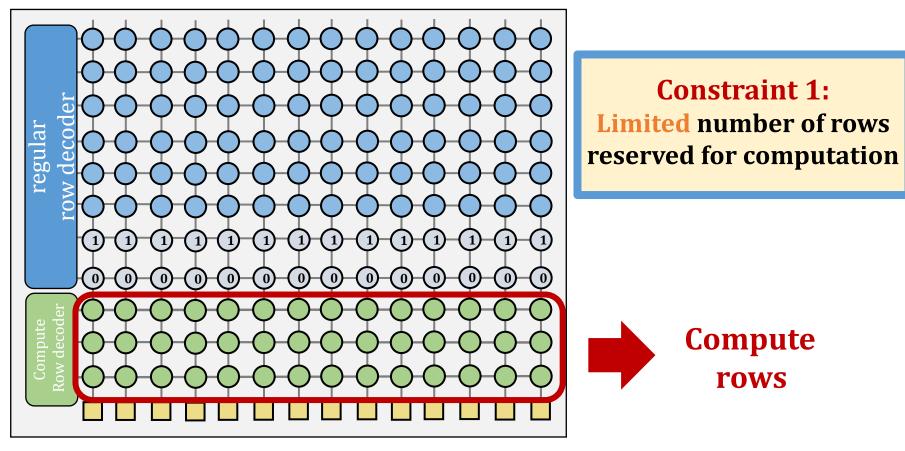

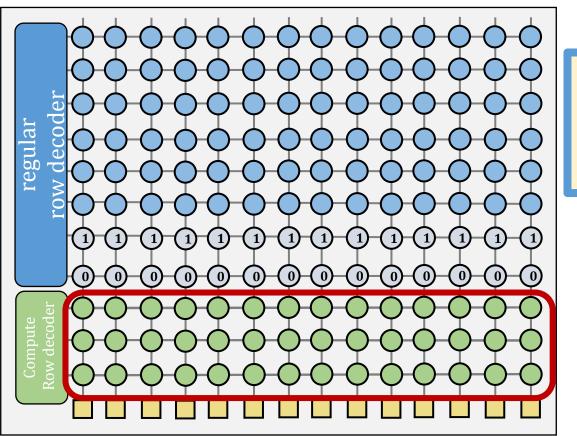

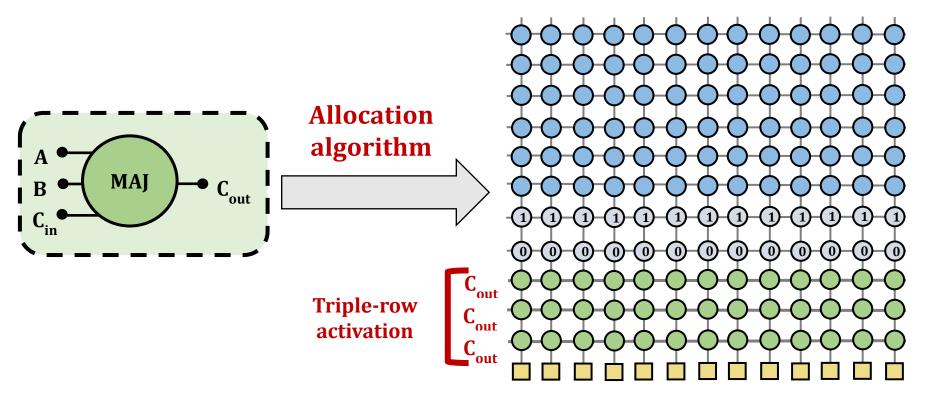

#### Task 1: Allocating DRAM Rows to Operands

Allocation algorithm considers two constraints specific to processing-using-DRAM

subarray organization

#### Task 1: Allocating DRAM Rows to Operands

Allocation algorithm considers two constraints specific to processing-using-DRAM

**Constraint 2:**

**Destructive** behavior of triple-row activation

Overwritten with MAJ output

subarray organization

### Task 1: Allocating DRAM Rows to Operands

- Allocation algorithm:

- Assigns as many inputs as the number of free compute rows

- All three input rows contain the MAJ output and can be reused

### Step 2: µProgram Generation

• **µProgram:** A series of microarchitectural operations (e.g., ACT/PRE) that SIMDRAM uses to execute SIMDRAM operation in DRAM

• Goal of Step 2: To generate the µProgram that executes the desired SIMDRAM operation in DRAM

Task 1: Allocate DRAM rows to the operands

Task 2: Generate μProgram

### Task 2: Generate an initial µProgram

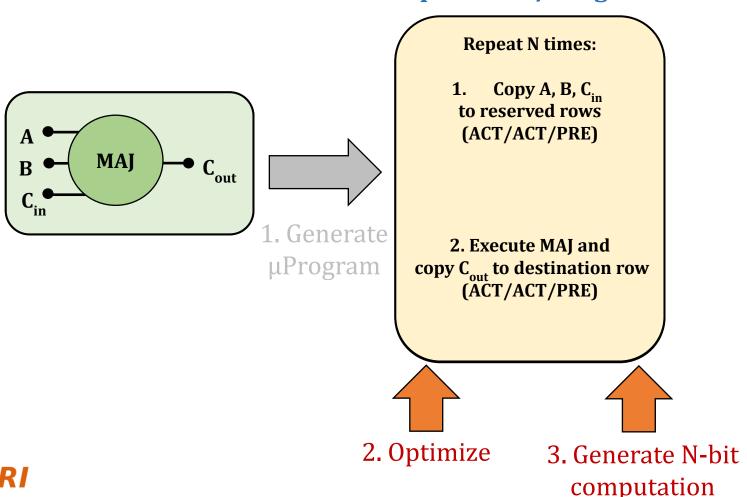

### Task 2: Generate N-bit Computation

• Final µProgram is optimized and computes the desired operation for operands of N-bit size in a bit-serial fashion

Optimized µProgram

### Task 2: Generate μProgram

Final μProgram is optimized and computes the desired operation for operands of N-bit size in a bit-serial fashion

# SIMDRAM Framework: Step 3

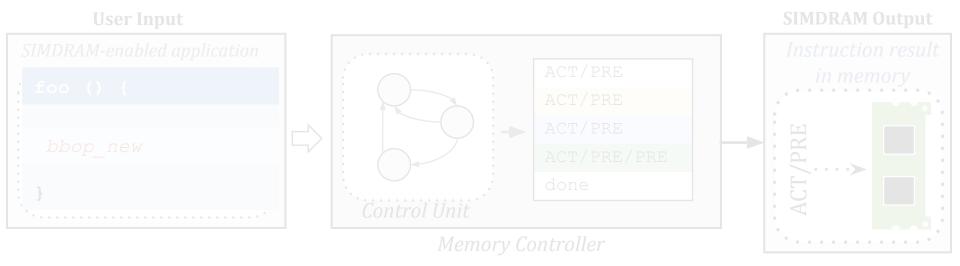

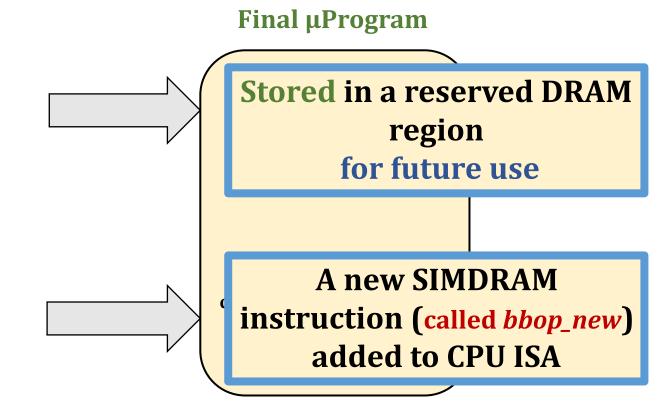

### Step 3: µProgram Execution

- **SIMDRAM control unit:** handles the execution of the µProgram at runtime

- Upon receiving a bbop instruction, the control unit:

- 1. Loads the μProgram corresponding to SIMDRAM operation

- 2. Issues the sequence of DRAM commands (ACT/PRE) stored in the μProgram to SIMDRAM subarrays to perform the in-DRAM operation

### More in the Paper

Detailed reference implementation and microarchitecture of the SIMDRAM control unit

# **System Integration**

**Efficiently transposing data**

**Programming interface**

Handling page faults, address translation, coherence, and interrupts

Handling limited subarray size

**Security implications**

**Limitations of our framework**

# **Transposing Data**

SIMDRAM operates on vertically-laid-out data

Other system components expect data to be laid out horizontally

**Challenging** to share data between SIMDRAM and CPU

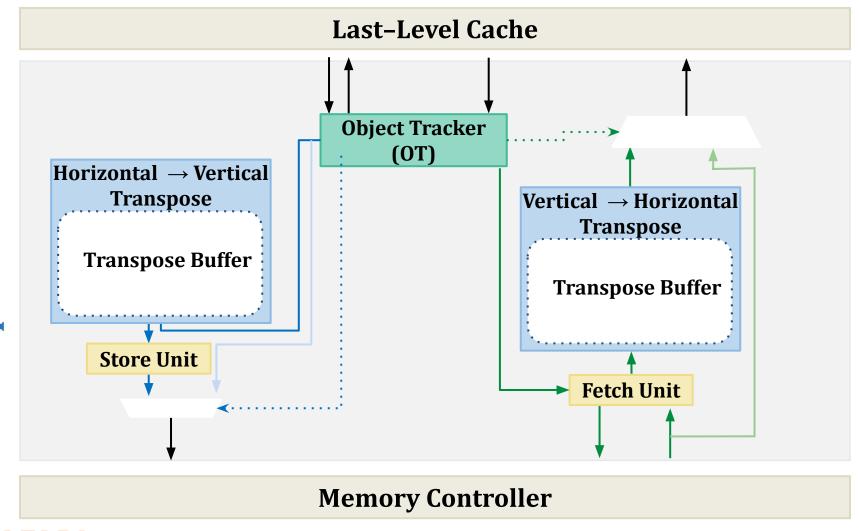

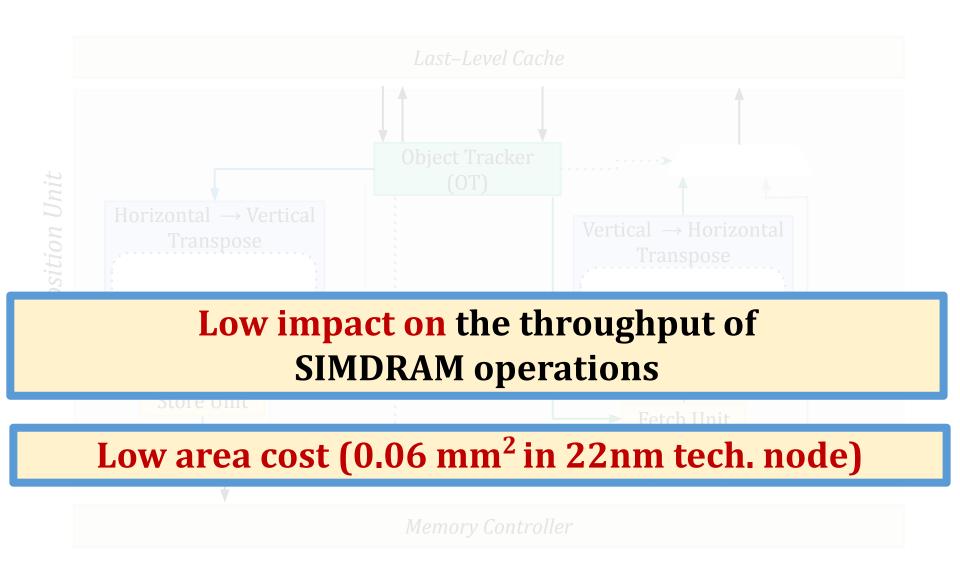

# **Fransposition Unit**

# **Transposition Unit**

Transforms the data layout from horizontal to vertical, and vice versa

# **Efficiently Transposing Data**

# More in the Paper

### SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Computing in DRAM

\*Nastaran Hajinazar<sup>1,2</sup> Nika Mansouri Ghiasi<sup>1</sup> \*Geraldo F. Oliveira<sup>1</sup> Minesh Patel<sup>1</sup> Juan Gómez-Luna<sup>1</sup> Sven Gregorio<sup>1</sup> Mohammed Alser<sup>1</sup> Onur Mutlu<sup>1</sup> João Dinis Ferreira<sup>1</sup> Saugata Ghose<sup>3</sup>

<sup>1</sup>ETH Zürich

<sup>2</sup>Simon Fraser University

<sup>3</sup>University of Illinois at Urbana–Champaign

### coherence, and interrupts

### Handling limited subarray size

**Security implications**

Limitations of our framework

### Methodology: Experimental Setup

• Simulator: gem5

### Baselines:

- A multi-core CPU (Intel Skylake)

- A high-end GPU (NVidia Titan V)

- Ambit: a state-of-the-art in-memory computing mechanism

- Evaluated SIMDRAM configurations (all using a DDR4\_2400\_x64 device):

- 1-bank: SIMDRAM exploits 65'536 SIMD lanes (an 8 kB row buffer)

- 4-banks: SIMDRAM exploits 262'144 SIMD lanes

- 16-banks: SIMDRAM exploits 1'048'576 SIMD lanes

### Methodology: Workloads

### **Evaluated:**

- 16 complex in-DRAM operations:

- Absolute Predication

- Addition/Subtraction ReLU

- BitCount AND-/OR-/XOR-Reduction

- Equality/ Greater/Greater Equal Division/Multiplication

- 7 real-world applications

- BitWeaving (databases) LeNET (neural networks)

- TPH-H (databases) VGG-13/VGG-16 (neural networks)

- kNN (machine learning) Brightness (graphics)

### **Throughput Analysis**

Average normalized throughput across all 16 SIMDRAM operations

SIMDRAM significantly outperforms all state-of-the-art baselines for a wide range of operations

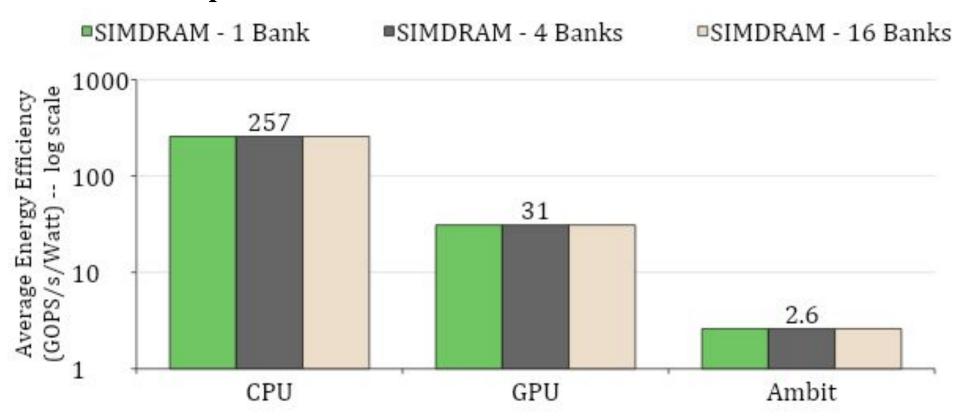

### **Energy Analysis**

Average normalized energy efficiency across all 16 SIMDRAM operations

SIMDRAM is more energy-efficient than all state-of-the-art baselines for a wide range of operations

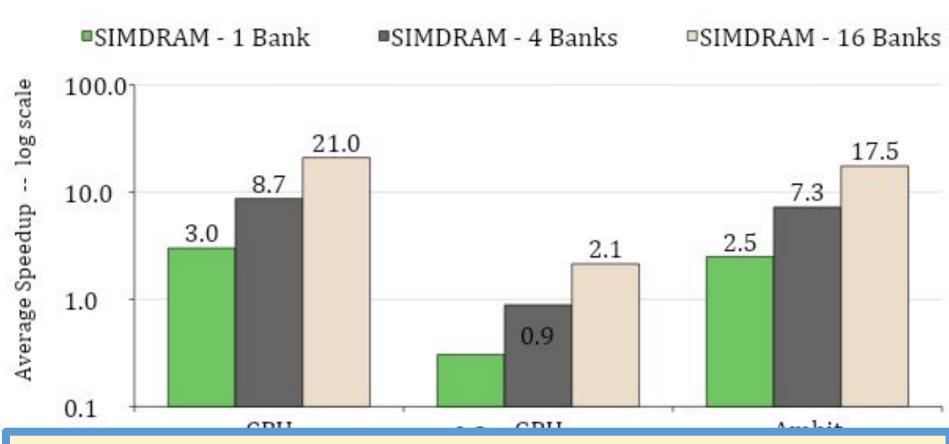

### **Real-World Applications**

Average speedup across 7 real-world applications

SIMDRAM effectively and efficiently accelerates many commonly-used real-world applications

# **SIMDRAM Key Results**

### Evaluated on:

- 16 complex in-DRAM operations

- 7 commonly-used real-world applications

### **SIMDRAM** provides:

- 88× and 5.8× the throughput of a CPU and a high-end GPU, respectively, over 16 operations

- 257× and 31× the energy efficiency of a CPU and a high-end GPU, respectively, over 16 operations

- 21× and 2.1× the performance of a CPU an a high-end GPU, over seven real-world applications

### **SIMDRAM Conclusion**

### • SIMDRAM:

- Enables efficient computation of a flexible set and wide range of operations in a PuM massively parallel SIMD substrate

- Provides the hardware, programming, and ISA support, to:

- Address key system integration challenges

- Allow programmers to define and employ new operations without hardware changes

### **SIMDRAM** is a promising PuM framework

- Can ease the adoption of processing-using-DRAM architectures

- Improves the performance and efficiency of processing-using-memory architectures

# SIMDRAM: A Framework for Bit-Serial SIMD Processing using DRAM

Nastaran Hajinazar\* Geraldo F. Oliveira\*

Sven Gregorio

Joao Ferreira Nika Mansouri Ghiasi

Minesh Patel

Mohammed Alser

Saugata Ghose

Juan Gómez–Luna

Onur Mutlu

### In-DRAM Physical Unclonable Functions

Jeremie S. Kim, Minesh Patel, Hasan Hassan, and Onur Mutlu,

"The DRAM Latency PUF: Quickly Evaluating Physical Unclonable

Functions by Exploiting the Latency-Reliability Tradeoff in Modern DRAM Devices"

Proceedings of the <u>24th International Symposium on High-Performance Computer</u> <u>Architecture</u> (**HPCA**), Vienna, Austria, February 2018.

[Lightning Talk Video]

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

[Full Talk Lecture Video (28 minutes)]

### The DRAM Latency PUF:

Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern Commodity DRAM Devices

Jeremie S. Kim<sup>†§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

### In-DRAM True Random Number Generation

Jeremie S. Kim, Minesh Patel, Hasan Hassan, Lois Orosa, and Onur Mutlu,

"D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput"

Proceedings of the <u>25th International Symposium on High-Performance Computer</u> <u>Architecture</u> (**HPCA**), Washington, DC, USA, February 2019.

[Slides (pptx) (pdf)]

[Full Talk Video (21 minutes)]

[Full Talk Lecture Video (27 minutes)]

Top Picks Honorable Mention by IEEE Micro.

### D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

Jeremie S. Kim<sup>‡§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§‡</sup> <sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

SAFARI 135

### In-DRAM True Random Number Generation

Ataberk Olgun, Minesh Patel, A. Giray Yaglikci, Haocong Luo, Jeremie S. Kim, F. Nisa Bostanci, Nandita Vijaykumar, Oguz Ergin, and Onur Mutlu,

"QUAC-TRNG: High-Throughput True Random Number Generation Using Quadruple Row Activation in Commodity DRAM Chips"

Proceedings of the <u>48th International Symposium on Computer Architecture</u> (**ISCA**), Virtual, June 2021.

[Slides (pptx) (pdf)]

Short Talk Slides (pptx) (pdf)

[Talk Video (25 minutes)]

[SAFARI Live Seminar Video (1 hr 26 mins)]

# QUAC-TRNG: High-Throughput True Random Number Generation Using Quadruple Row Activation in Commodity DRAM Chips

Ataberk Olgun<sup>§†</sup> Minesh Patel<sup>§</sup> A. Giray Yağlıkçı<sup>§</sup> Haocong Luo<sup>§</sup> Jeremie S. Kim<sup>§</sup> F. Nisa Bostancı<sup>§†</sup> Nandita Vijaykumar<sup>§⊙</sup> Oğuz Ergin<sup>†</sup> Onur Mutlu<sup>§</sup>

§ETH Zürich  $^{\dagger}$  TOBB University of Economics and Technology  $^{\odot}$  University of Toronto

SAFARI 136

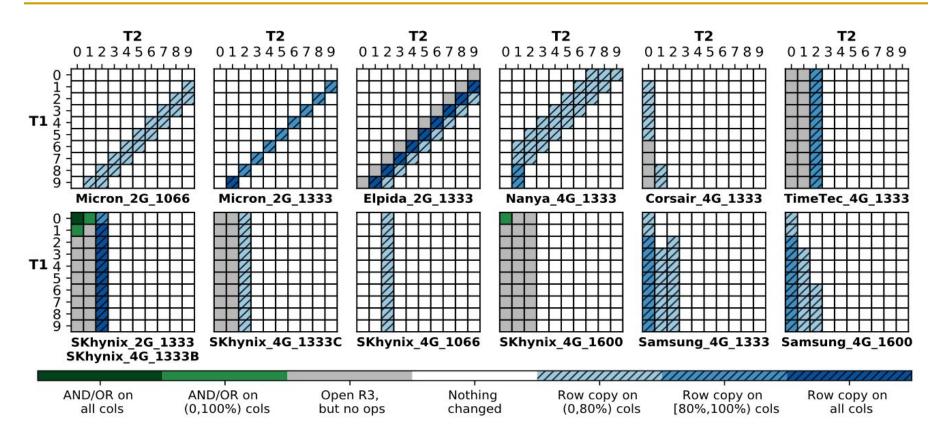

### RowClone & Bitwise Ops in Real DRAM Chips

# ComputeDRAM: In-Memory Compute Using Off-the-Shelf DRAMs

Fei Gao feig@princeton.edu Department of Electrical Engineering Princeton University Georgios Tziantzioulis georgios.tziantzioulis@princeton.edu Department of Electrical Engineering Princeton University David Wentzlaff wentzlaf@princeton.edu Department of Electrical Engineering Princeton University

### Pinatubo: RowClone and Bitwise Ops in PCM

# Pinatubo: A Processing-in-Memory Architecture for Bulk Bitwise Operations in Emerging Non-volatile Memories

Shuangchen Li<sup>1</sup>\*, Cong Xu<sup>2</sup>, Qiaosha Zou<sup>1,5</sup>, Jishen Zhao<sup>3</sup>, Yu Lu<sup>4</sup>, and Yuan Xie<sup>1</sup>

University of California, Santa Barbara<sup>1</sup>, Hewlett Packard Labs<sup>2</sup> University of California, Santa Cruz<sup>3</sup>, Qualcomm Inc.<sup>4</sup>, Huawei Technologies Inc.<sup>5</sup> {shuangchenli, yuanxie}ece.ucsb.edu<sup>1</sup>

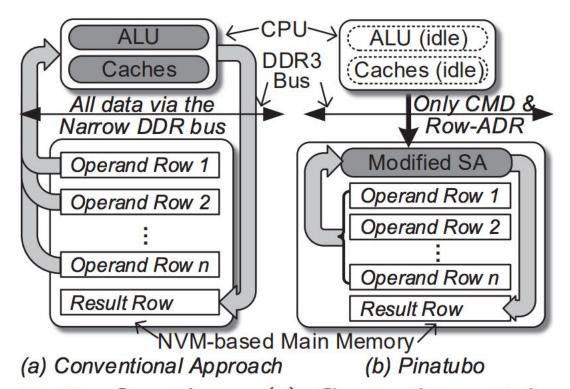

### Pinatubo: RowClone and Bitwise Ops in PCM

Figure 2: Overview: (a) Computing-centric approach, moving tons of data to CPU and write back. (b) The proposed Pinatubo architecture, performs *n*-row bitwise operations inside NVM in one step.

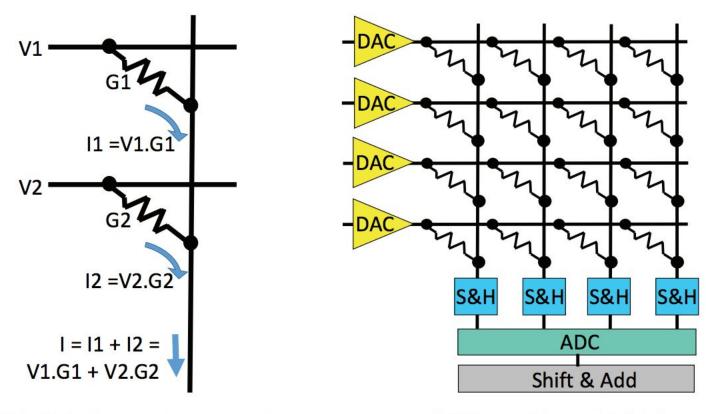

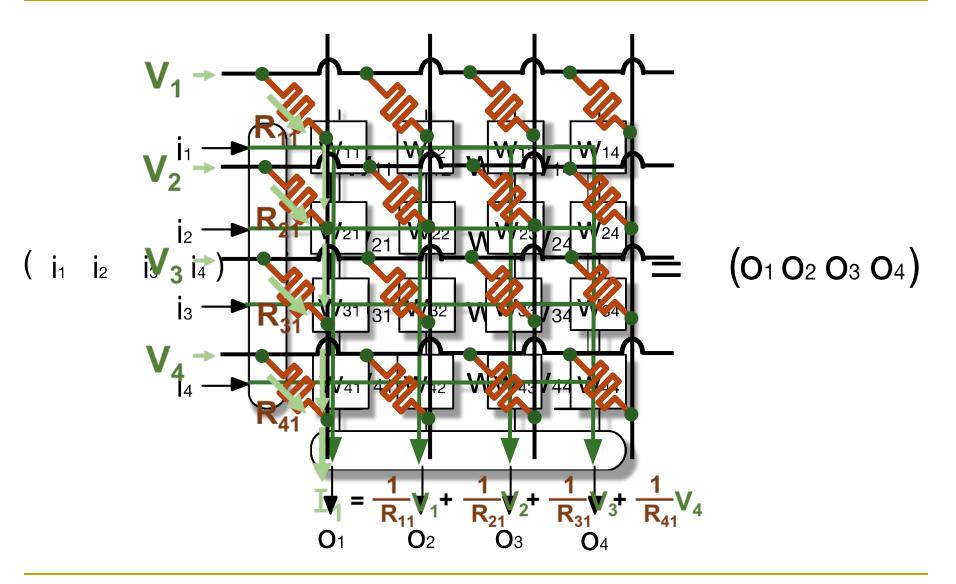

### In-Memory Crossbar Array Operations

- Some emerging NVM technologies have crossbar array structure

- Memristors, resistive RAM, phase change mem, STT-MRAM, ...

- Crossbar arrays can be used to perform dot product operations using "analog computation capability"

- Can operate on multiple pieces of data using Kirchoff's laws

- Bitline current is a sum of products of wordline  $V \times (1 / \text{cell R})$

- Computation is in analog domain inside the crossbar array

- Need peripheral circuitry for D□A and A□D conversion of inputs and outputs

### Aside: In-Memory Crossbar Computation

(a) Multiply-Accumulate operation

(b) Vector-Matrix Multiplier

Fig. 1. (a) Using a bitline to perform an analog sum of products operation. (b) A memristor crossbar used as a vector-matrix multiplier.

### Aside: In-Memory Crossbar Computation

# Readings on Processing using NVM

- Shafiee+, "ISAAC: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars", ISCA 2016.

- Chi+, "PRIME: A Novel Processing-in-memory Architecture for Neural Network Computation in ReRAM-based Main Memory", ISCA 2016.

- Prezioso+, "Training and Operation of an Integrated Neuromorphic Network based on Metal-Oxide Memristors", Nature 2015

- Ambrogio+, "Equivalent-accuracy accelerated neural-network training using analogue memory", Nature 2018.

### Challenge: Intelligent Memory Device

# Does memory have to be dumb?

# Challenge and Opportunity for Future

# Computing Architectures with Minimal Data Movement

# Historical Perspective & A Detour on the Review Process

# Ambit and RowClone Sound Great! No?

# Some History: RowClone

# RowClone: Historical Perspective

- This work is likely the first example of "minimally changing DRAM chips" to perform data movement and computation

- Surprising that it was done as late as 2013!

- It led to a body of work on in-DRAM (and in-NVM) computation with "hopefully small" changes

- Work building on RowClone still continues

- Initially, it was dismissed by some reviewers

- Rejected from ISCA 2013 conference

# One Review (ISCA 2013 Submission)

### PAPER STRENGTHS

The paper includes a well written background on DRAM organization/operation. The proposed technique is simple and elegant; it nicely exploits key circuit-level characteristics of DRAM designs and minimizes the changes necessary to commodity DRAM chips.

### PAPER WEAKNESSES

I am concerned on the applicability of the technique and found the

evaluation to be uncompelling in terms of motivating the work as well as

quantifying the potential benefit. Details on how to efficiently manage

the coherence between the cache hierarchy and DRAM to enable the proposed

technique are glossed over, but in my opinion are critical to the

narrative.

# Another Review and Rebuttal

### **DETAILED COMMENTS**

The paper proposes a simple and not new idea, block copy in a DRAM, and the creates a complete

Reviewer B mentions that our idea is "not new". An explicit

reference by the reviewer would be helpful here. While the

reviewer may be referring to one of the patents that we cite in

our paper (citations 2, 6, 25, 26, 27 in the paper), these patents

are at a superficial level and do \*not\* provide a concrete mechanism. In contrast, we propose three concrete mechanisms and

provide details on the most important architectural and microarchitectural modifications required at the DRAM chip, the

memory controller, and the CPU to enable a system that supports

the mechanisms. We also analyze their latency, hardware overhead,

power, and performance in detail. We are not aware of any prior

work that achieves this.

# ISCA 2013 Submission

### ISCA40

### **Paper #295**

onur@cmu.edu Profile | Help | Sign out

#268 Papers #353

(All) Search

### #295 RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data

### NOTIFICATION

If selected, you will receive email when updated comments are available for this paper.

+ OTHER CONFLICTS

### Rejected

1014kB

Thursday 22 Nov 2012 12:11:45am EST

0fd459a9adc6194cda028a394d2e4d929f662f32

You are an **author** of this paper.

### - ABSTRACT

Many programs initialize or copy large amounts of memory data.

Initialization and copying are

### + AUTHORS

- V. Seshadri, Y. Kim, D. Lee,

- C. Fallin, R. Ausavarungnirun,

- G. Pekhimenko, Y. Luo, O. Mutlu,

| Review | #295A |

|--------|-------|

| Review | #295B |

| Review | #295C |

| OveMer | Nov | WriQua | RevConAnd |

|--------|-----|--------|-----------|

| 3      | 4   | 5      | 3         |

| 4      | 3   | 4      | 3         |

| 3      | 4   | 4      | 3         |

# Yet Later... in ISCA 2015...

### Profiling a warehouse-scale computer

Svilen Kanev<sup>†</sup> Harvard University

Parthasarathy Ranganathan Google

Juan Pablo Darago† Universidad de Buenos Aires

Tipp Moseley Google

Gu-Yeon Wei Harvard University

Kim Hazelwood<sup>†</sup> Yahoo Labs

> **David Brooks** Harvard University

nents of "datacenter tax".

we see common building blocks once we aggregate sampled profile data across many applications running in a datacenter. In this section, we quantify the performance impact of the datacenter tax, and argue that its components are prime candidates for hardware acceleration in future datacenter SoCs.

**Data movement** In fact, RPCs are by far not the only code portions that do data movement. We also tracked all calls to the Figure 4: 22-27% of WSC cycles are spent in different cc memcpy() and memmove() library functions to estimate the amount of time spent on explicit data movement (i.e., exposed through a simple API). This is a conservative estimate because it does not track inlined or explicit copies. Just the variants of these two library functions represent 4-5% of datacenter cycles.

> Recent work in performing data movement in DRAM [45] could optimize away this piece of tax.

# MICRO 2013 Submission

# #206 RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization

ATION ceive

e for

**Accepted**

**1947kB** Friday 31 May 2013 1:48:46pm PDT | fd8423acdd9a222280302355899340083e5a40b1

You are an **author** of this paper.

### + ABSTRACT

Bulk data copy and initialization operations are frequently triggered by several system level operations in modern systems. Despite the fact that these operations do not require <a href="more">[more]</a>

### + Authors

- V. Seshadri, Y. Kim, C. Fallin,

- D. Lee, R. Ausavarungnirun,

- G. Pekhimenko, Y. Luo, O. Mutlu,

- P. Gibbons, M. Kozuch, T. Mowry [details]

### + Topics

|              | OveMe | r Nov | WriQua | RevExp |

|--------------|-------|-------|--------|--------|

| Review #206A | 5     | 4     | 4      | 4      |

| Review #206B | 4     | 2     | 4      | 4      |

| Review #206C | 3     | 4     | 4      | 4      |

| Review #206D | 3     | 3     | 4      | 3      |

| Review #206E | 4     | 3     | 5      | 3      |

# More History: Ambit

# **Ambit**

- First work on performing bulk bitwise operations in DRAM

- By exploiting analog computation capability of bitlines

- Extends and completes our IEEE CAL 2015 paper

- Disruptive -- spans algorithms to circuits/devices

- Requires hardware/software cooperation for adoption

- Led to a large amount of work in similar approaches in DRAM and NVM

- The work continues to build

- Initially, it was dismissed by many reviewers

- Rejected from 4 conferences!

# ISCA 2016: Rejected

### **Buddy RAM: Fast and Efficient Bulk Bitwise** Operations Using DRAM

Rejected

2006kB 23 Nov 2015 11:30:23pm EST ·

7f7234da178e644380275ce12a4f539ef45c4418

You are an **author** of this paper.

▶ Abstract

Many data structures (e.g., database bitmap indices) rely on fast bitwise operations on large bit vectors to achieve high performance. Unfortunately, the throughput of such bulk [more]

Authors

V. Seshadri, D. Lee, T. Mullins,

A. Boroumand, J. Kim,

M. Kozuch, O. Mutlu.

P. Gibbons, T. Mowry [details]

► Topics and Options

### RelISC OveMerPos RevConAnd Nov WriQua

| Review #171A | 3 | 4 | 4 | 2 | 3 |

|--------------|---|---|---|---|---|

| Review #171B | 2 | 4 | 3 | 3 | 4 |

| Review #171C | 3 | 4 | 4 | 2 | 3 |

| Review #171D | 3 | 5 | 2 | 2 | 3 |

| Review #171E | 2 | 3 | 2 | 3 | 3 |

# MICRO 2016: Rejected

Submission (1662kB) 10 Apr 2016 9:32:31pm EDT · e518c6a8916109492574858db80a6184fe61ca0c **▶** Abstract **▼**Authors Vivek Seshadri (CMU) Certain widely-used data structures <vseshadr@cs.cmu.ed (e.g., bitmap indices) rely on Donghyuk Lee (NVIDIA Re <donahyuk1@cmu.edu Thomas Mullins (Intel) [more] <thomas.p.mullins@int Amirali Boroumand (CMU) Jeremie Kim (CMU) Michael A. Kozuch (Intel) <michael.a.kozuch@in Onur Mutlu (CMU/ETH) <omutlu@gmail.com> Phillip B. Gibbons (CMU) <gibbons@cs.cmu.edu Todd C. Mowry (CMU) <tc **▶** Topics

Rejected · You are an author of this paper.

|              | PosRebOve | OveMer | RevExp | Nov | WriQua |

|--------------|-----------|--------|--------|-----|--------|

| Review #249A | 2         | 2      | 4      | 3   | 3      |

| Review #249B | 4         | 4      | 3      | 3   | 5      |

| Review #249C | 2         | 3      | 4      | 2   | 3      |

| Review #249D | 5         | 5      | 2      | 3   | 3      |

| Review #249E | 5         | 5      | 2      | 2   | 3      |

| Review #249F | 3         | 3      | 3      | 3   | 4      |

# HPCA 2017: Rejected

1)~significantly improves the performance of queries in applications that use bitmap indices for fast analytics, and 2)~makes bit vectors more attractive than red-black trees to represent sets. We believe Buddy can trigger programmers to redesign applications to use bitwise operations with the goal of achieving high performance and efficiency.

| Rejected | ٠ | You are an | author | of this | paper. |

|----------|---|------------|--------|---------|--------|

|          |   | 0          | D      | MALIO   | F N #  |