# Computer Architecture

Lecture 1: Introduction and Basics

Prof. Onur Mutlu

ETH Zürich

Fall 2022

29 September 2022

# Brief Self Introduction

### Onur Mutlu

- Full Professor @ ETH Zurich ITET (INFK), since September 2015

- □ Strecker Professor @ Carnegie Mellon University ECE/CS, 2009-2016, 2016-...

- PhD from UT-Austin, worked at Google, VMware, Microsoft Research, Intel, AMD

- https://people.inf.ethz.ch/omutlu/

- omutlu@gmail.com (Best way to reach me)

- https://people.inf.ethz.ch/omutlu/projects.htm

### Research and Teaching in:

- Computer architecture, computer systems, hardware security, bioinformatics

- Memory and storage systems

- Hardware security, safety, predictability

- Fault tolerance

- Hardware/software cooperation

- Architectures for bioinformatics, health, medicine

- **...**

# Current Research Mission

### Computer architecture, HW/SW, systems, bioinformatics, security

# **Build fundamentally better architectures**

# Four Key Current Directions

Fundamentally Secure/Reliable/Safe Architectures

- Fundamentally Energy-Efficient Architectures

- Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency and Predictable Architectures

Architectures for AI/ML, Genomics, Medicine, Health

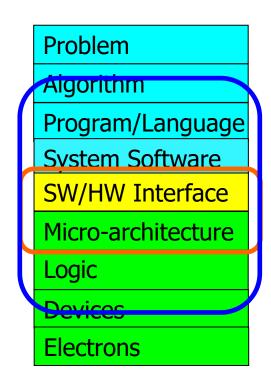

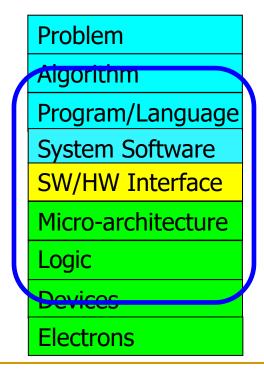

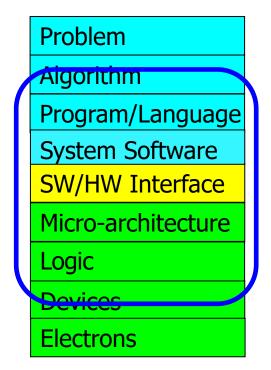

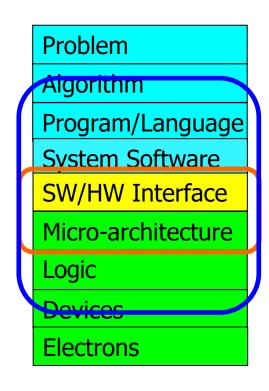

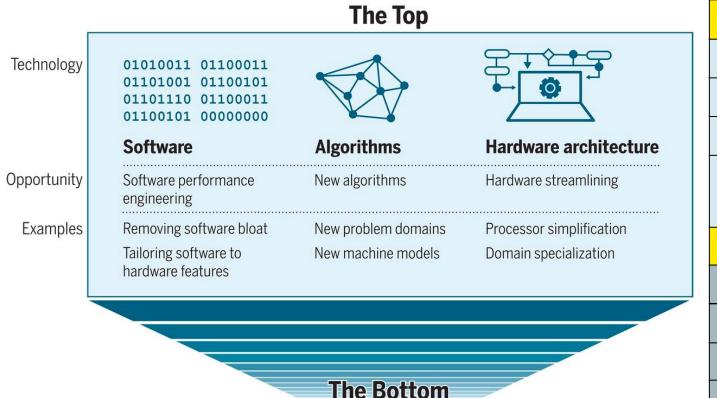

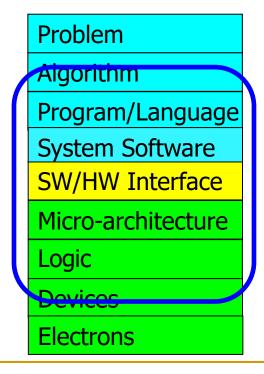

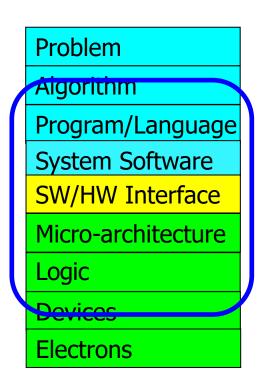

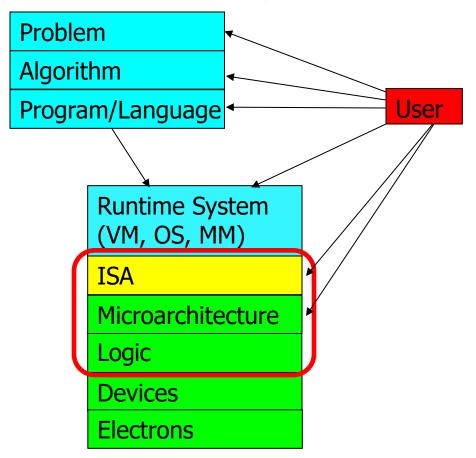

# The Transformation Hierarchy

Computer Architecture (expanded view)

Computer Architecture (narrow view)

# Computing System

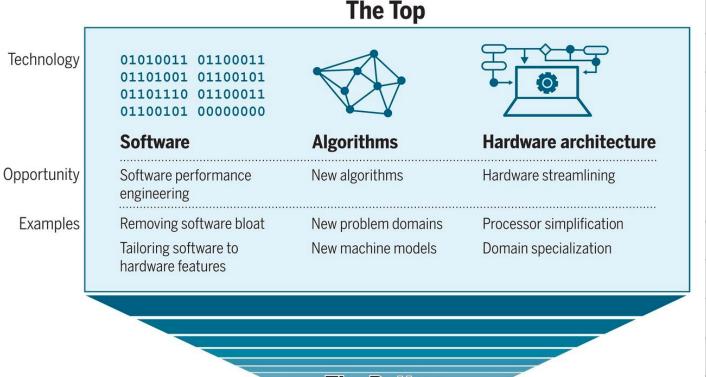

Leiserson+, "There's plenty of room at the Top: What will drive computer performance after Moore's law?", Science, 2020

Data **Problem** Algorithm Program/Language **Runtime System** (VM, OS, MM) ISA (Architecture) Microarchitecture Logic **Devices**

Electrons

The Bottom

for example, semiconductor technology

Richard Feynman, "There's Plenty of Room at the Bottom: An Invitation to Enter a New Field of Physics", a lecture given at Caltech, 1959.

# Software & Hardware Optimizations

```

Multiplying Two 4096-by-4096 Matrices

for i in xrange(4096):

for j in xrange(4096):

for k in xrange(4096):

C[i][j] += A[i][k] * B[k][j]

[7 8

9 10

11 12]

[7 8

9 10

11 12]

```

| Implementation              | Running time (s) | Absolute speedup |

|-----------------------------|------------------|------------------|

| Python                      | 25,552.48        | 1x               |

| Java                        | 2,372.68         | 11x              |

| C                           | 542.67           | 47x              |

| Parallel loops              | 69.80            | 366x             |

| Parallel divide and conquer | 3.80             | 6,727x           |

| plus vectorization          | 1.10             | 23,224x          |

| plus AVX intrinsics         | 0.41             | 62,806x          |

Leiserson+, "There's plenty of room at the Top: What will drive computer performance after Moore's law?", Science, 2020

# Axiom

To achieve the highest energy efficiency and performance:

# we must take the expanded view

of computer architecture

Co-design across the hierarchy:

Algorithms to devices

Specialize as much as possible within the design goals

# Current Research Mission & Major Topics

# **Build fundamentally better architectures**

Broad research spanning apps, systems, logic with architecture at the center

- Data-centric arch. for low energy & high perf.

- Proc. in Mem/DRAM, NVM, unified mem/storage

- Low-latency & predictable architectures

- Low-latency, low-energy yet low-cost memory

- QoS-aware and predictable memory systems

- Fundamentally secure/reliable/safe arch.

- Tolerating all bit flips; patchable HW; secure mem

- Architectures for ML/AI/Genomics/Graph/Med

- Algorithm/arch./logic co-design; full heterogeneity

- Data-driven and data-aware architectures

- ML/AI-driven architectural controllers and design

- Expressive memory and expressive systems

# SAFARI Research Group

# Think BIG, Aim HIGH!

https://safari.ethz.ch

# Onur Mutlu's SAFARI Research Group

Computer architecture, HW/SW, systems, bioinformatics, security, memory

https://safari.ethz.ch/safari-newsletter-april-2020/

Think BIG, Aim HIGH!

SAFARI

https://safari.ethz.ch

# SAFARI Newsletter December 2021 Edition

https://safari.ethz.ch/safari-newsletter-december-2021/

Think Big, Aim High

View in your browser December 2021

# SAFARI PhD and Post-Doc Alumni

### https://safari.ethz.ch/safari-alumni/

- Minesh Patel (ETH Zurich)

- Damla Senol Cali (Bionano Genomics)

- Nastaran Hajinazar (ETH Zurich)

- Gagandeep Singh (ETH Zurich)

- Amirali Boroumand (Stanford Univ)

- Jeremie Kim (ETH Zurich)

- Nandita Vijaykumar (Univ. of Toronto, Assistant Professor)

- Kevin Hsieh (Microsoft Research, Senior Researcher)

- Justin Meza (Facebook)

- Mohammed Alser (ETH Zurich)

- Yixin Luo (Google)

- Kevin Chang (Facebook)

- Rachata Ausavarungnirun (KMUNTB, Assistant Professor)

- Gennady Pekhimenko (Univ. of Toronto, Assistant Professor)

- Vivek Seshadri (Microsoft Research)

- Donghyuk Lee (NVIDIA Research, Senior Researcher)

- Yoongu Kim (Google)

- Lavanya Subramanian (Intel Labs → Facebook)

- Samira Khan (Univ. of Virginia, Assistant Professor)

- Saugata Ghose (Univ. of Illinois, Assistant Professor)

- Jawad Haj-Yahya (Huawei Research Zurich, Principal Researcher)

- Lois Orosa (Galicia Supercomputing Center)

- Jisung Park (POSTECH, Assistant Professor)

# SAFARI Research Group: Introduction and Research

Onur Mutlu,

"SAFARI Research Group: Introduction & Research"

Talk at ETH Future Computing Laboratory Welcome

Workshop (EFCL), Virtual, 6 July 2021.

[Slides (pptx) (pdf)]

# A Talk on Impactful Research & Teaching

# Principle: Teaching and Research

Teaching drives Research Research drives Teaching HOME

VIDEOS

**PLAYLISTS**

COMMUNITY

CHANNELS

ABOUT

Popular uploads

▶ PLAY ALL

Includes standard DIMM modu number of DPU processors co TTT TT 2:24:11 ML accelerator: 260 mm², 6 billion transist 600 GFLOPS GPU, 12 ARM 2.2 GHz CPUs.

Design of Digital Circuits Lecture 1: Introduction and Basics

Design of Digital Circuits -

Lecture 1: Introduction and...

**Digital Design & Computer** Architecture: Lecture 1:...

49K views • 1 year ago

Computer Architecture -Lecture 1: Introduction and...

36K views • 3 years ago

Computer Architecture -Lecture 1: Introduction and...

31K views • 1 year ago 30K views • 8 months ago

Computer Architecture -Lecture 1: Introduction and...

22K views • 2 years ago

Computer Architecture -Lecture 2: Fundamentals....

17K views • 3 years ago

### First Course in Computer Architecture & Digital Design 2021-2013

Architecture - ETH Zurich -...

Livestream - Digital Design and Digital Design & Computer Computer Architecture - ETH...

Onur Mutlu Lectures VIEW FULL PLAYLIST Architecture - ETH Zürich...

Onur Mutlu Lectures VIEW FULL PLAYLIST

Design of Digital Circuits - ETH Zürich - Spring 2019

Onur Mutlu Lectures VIEW FULL PLAYLIST Design of Digital Circuits - ETH Zürich - Spring 2018

Onur Mutlu Lectures

VIEW FULL PLAYLIST

Onur Mutlu Lectures VIEW FULL PLAYLIST

Spring 2015 -- Computer Architecture Lectures --...

Carnegie Mellon Computer Architec... VIEW FULL PLAYLIST

### Advanced Computer Architecture Courses 2020-2012

Computer Architecture - ETH Zürich - Fall 2020

Onur Mutlu Lectures VIEW FULL PLAYLIST

Computer Architecture - ETH Zürich - Fall 2019

Onur Mutlu Lectures VIEW FULL PLAYLIST

Computer Architecture - ETH Zürich - Fall 2018

Onur Mutlu Lectures VIEW FULL PLAYLIST Computer Architecture - ETH Zürich - Fall 2017

Onur Mutlu Lectures VIEW FULL PLAYLIST Fall 2015 - 740 Computer Architecture

Carnegie Mellon Computer Architec... VIEW FULL PLAYLIST

Architecture - Carnegie Mellon Carnegie Mellon Computer Architec... VIEW FULL PLAYLIST

Fall 2013 - 740 Computer

### Special Courses on Memory Systems

Memory Technology Lectures

Onur Mutlu Lectures VIEW FULL PLAYLIST

Champéry Winter School 2020 - Perugia NiPS Summer School Memory Systems and Memory... 2019

Onur Mutlu Lectures VIEW FULL PLAYLIST

Onur Mutlu Lectures VIEW FULL PLAYLIST

Systems

Onur Mutlu Lectures VIEW FULL PLAYLIST Systems and Memory-Centric... Onur Mutlu Lectures

VIEW FULL PLAYLIST

ACACES 2018 Lectures --Memory Systems and Memory...

Onur Mutlu Lectures VIEW FULL PLAYLIST

# Online Courses & Lectures

# First Computer Architecture & Digital Design Course

- Digital Design and Computer Architecture

- Spring 2022 Livestream Edition:

<a href="https://www.youtube.com/watch?v=cpXdE3HwvK0&list=PL5Q2soXY2Zi97Ya5DEUpMpO2bbAoaG7c6">https://www.youtube.com/watch?v=cpXdE3HwvK0&list=PL5Q2soXY2Zi97Ya5DEUpMpO2bbAoaG7c6</a>

# Advanced Computer Architecture Course

- Computer Architecture

- Fall 2021 Edition:

https://www.youtube.com/watch?v=4yfkM\_5EFgo&list=P L5Q2soXY2Zi-Mnk1PxjEIG32HAGILkTOF

### Fall 2021 Edition:

https://safari.ethz.ch/architecture/fall2021/doku. php?id=schedule

### Fall 2020 Edition:

https://safari.ethz.ch/architecture/fall2020/doku. php?id=schedule

### Youtube Livestream (2021):

https://www.youtube.com/watch?v=4yfkM\_5EFg o&list=PL5Q2soXY2Zi-Mnk1PxjEIG32HAGILkTOF

### Youtube Livestream (2020):

https://www.youtube.com/watch?v=c3mPdZA-Fmc&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN

### Master's level course

- Taken by Bachelor's/Masters/PhD students

- Cutting-edge research topics + fundamentals in Computer Architecture

- 5 Simulator-based Lab Assignments

- Potential research exploration

- Many research readings

Computer Architecture - Fall 2021

Trace: · readings · start · schedule

Home

Announcements

### Materials

- Lectures/Schedule

- Lecture Buzzwords

- Readings

- HWs

- Labs

- Related Courses

### Resources

- Computer Architecture FS20:

Course Webpage

- Computer Architecture FS20

Lecture Videos

- Lecture Videos

Digitaltechnik SS21: Course

- Webpage

Digitaltechnik SS21: Lecture

- Videos Moodle

- Moodle

HotCRE

- Verilog Practice Website (HDLBits)

### Lecture Video Playlist on YouTube

Recorded Lecture Playlist

### Fall 2021 Lectures & Schedule

| Week | Date          | Livestream    | Lecture                                                    | Readings               | Lab          | HW          |

|------|---------------|---------------|------------------------------------------------------------|------------------------|--------------|-------------|

| W1   | 30.09<br>Thu. | You Tube Live | L1: Introduction and Basics                                | Required<br>Mentioned  | Lab 1<br>Out | HW 0<br>Out |

|      | 01.10<br>Fri. | You Tube Live | L2: Trends, Tradeoffs and Design Fundamentals  (PDF) (PPT) | Required<br>Mentioned  |              |             |

| W2   | 07.10<br>Thu. | You Tube Live | L3a: Memory Systems: Challenges and Opportunities          | Described<br>Suggested |              | HW 1<br>Out |

|      |               |               | L3b: Course Info & Logistics                               |                        |              |             |

|      |               |               | L3c: Memory Performance Attacks                            | Described<br>Suggested |              |             |

|      | 08.10<br>Fri. | You Live      | L4a: Memory Performance Attacks                            | Described<br>Suggested | Lab 2<br>Out |             |

|      |               |               | L4b: Data Retention and Memory Refresh (PDF) (PPT)         | Described<br>Suggested |              |             |

|      |               |               | L4c: RowHammer                                             | Described<br>Suggested |              |             |

https://www.youtube.com/onurmutlulectures

# DDCA (Spring 2022)

### **Spring 2022 Edition:**

https://safari.ethz.ch/digitaltechnik/spring2022/do ku.php?id=schedule

### **Spring 2021 Edition:**

https://safari.ethz.ch/digitaltechnik/spring2021/do ku.php?id=schedule

### Youtube Livestream (Spring 2022):

https://www.youtube.com/watch?v=cpXdE3HwvK 0&list=PL5Q2soXY2Zi97Ya5DEUpMpO2bbAoaG7c6

### Youtube Livestream (Spring 2021):

https://www.youtube.com/watch?v=LbC0EZY8yw 4&list=PL5Q2soXY2Zi\_uej3aY39YB5pfW4SJ7LIN

### Bachelor's course

- 2<sup>nd</sup> semester at ETH Zurich

- Rigorous introduction into "How Computers Work"

- Digital Design/Logic

- Computer Architecture

- 10 FPGA Lab Assignments

Trace: • schedule

Home

### Announcements

### Materials

- Lectures/Schedule

- Lecture Buzzwords

- Readings

- Optional HWs

- Optional HW

- Extra Assignments

- Exams

Technical Docs

### Resources

- S Computer Architecture (CMU)

- SS15: Lecture Videos

- Computer Architecture (CMU) SS15: Course Website

- Digitaltechnik SS18: Lecture Videos

- Digitaltechnik SS18: Course Website

- Digitaltechnik SS19: Lecture Videos

- Digitaltechnik SS19: Course Website

- Digitaltechnik SS20: Lecture Videos

- Digitaltechnik SS20: Course Website

- Moodle

### Lecture Video Playlist on YouTube

Livestream Lecture Playlist

Recent Changes Media Manager Siter

Recorded Lecture Playlist

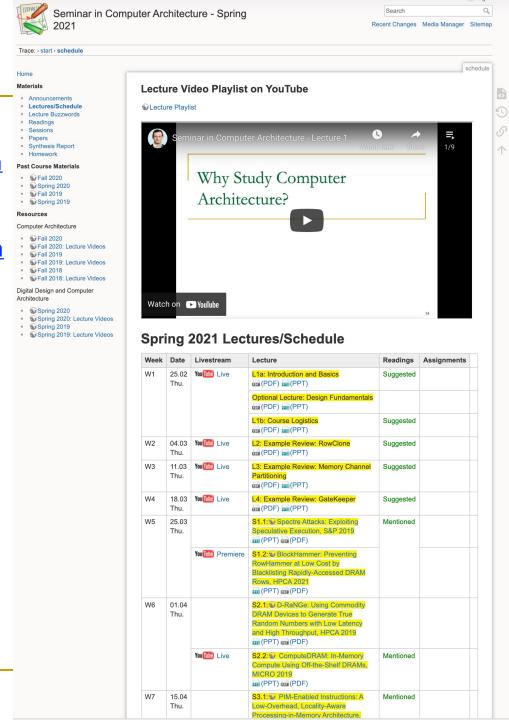

### Spring 2021 Lectures/Schedule

| Week       | Date          | Livestream    | Lecture                                             | Readings                           | Lab | HW |

|------------|---------------|---------------|-----------------------------------------------------|------------------------------------|-----|----|

| Thu<br>26. | 25.02<br>Thu. | YouTube Live  | L1: Introduction and Basics                         | Required<br>Suggested<br>Mentioned |     |    |

|            | 26.02<br>Fri. | You Tube Live | L2a: Tradeoffs, Metrics, Mindset                    | Required                           |     |    |

|            |               |               | L2b: Mysteries in Computer Architecture (PDF) (PPT) | Required<br>Mentioned              |     |    |

| W2         | 04.03<br>Thu. | You Tube Live | L3a: Mysteries in Computer Architecture II          | Required<br>Suggested              |     |    |

https://www.youtube.com/onurmutlulectures

# Seminar (Spring'21)

- https://safari.ethz.ch/architecture\_semin ar/spring2021/doku.php?id=schedule

- https://www.youtube.com/watch?v=t3m 93ZpLOyw&list=PL5Q2soXY2Zi awYdjm WVIUegsbY7TPGW4

- Critical analysis course

- Taken by Bachelor's/Masters/PhD students

- Cutting-edge research topics + fundamentals in Computer Architecture

- 20+ research papers, presentations, analyses

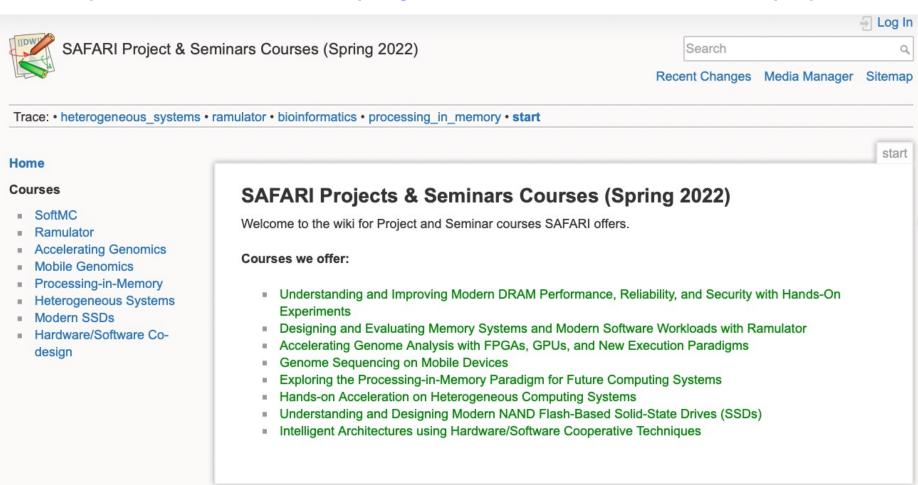

# PIM Course (Spring 2022)

### Spring 2022 Edition:

https://safari.ethz.ch/projects and semi nars/spring2022/doku.php?id=processing in memory

### Youtube Livestream:

https://www.youtube.com/watch?v=9e4 Chnwdovo&list=PL5Q2soXY2Zi-841fUYYUK9EsXKhQKRPyX

### Project course

- Taken by Bachelor's/Master's students

- Processing-in-Memory lectures

- Hands-on research exploration

- Many research readings

https://www.youtube.com/onurmutlulectures

### Spring 2022 Meetings/Schedule Week Date Livestream M

|     | Date          |                   |                                                                         | Materials                                      | , too igninone |

|-----|---------------|-------------------|-------------------------------------------------------------------------|------------------------------------------------|----------------|

| W1  | 10.03<br>Thu. | You Tobe Live     | M1: P&S PIM Course Presentation (PDF) (PPT)                             | Required Materials<br>Recommended<br>Materials | HW 0 Out       |

| W2  | 15.03<br>Tue. |                   | Hands-on Project Proposals                                              |                                                |                |

|     | 17.03<br>Thu. | You Premiere      | M2: Real-world PIM: UPMEM PIM (PDF) (PPT)                               |                                                |                |

| W3  | 24.03<br>Thu. | YouTube Live      | M3: Real-world PIM: Microbenchmarking of UPMEM PIM (SSE (PDF) (PPT)     |                                                |                |

| W4  | 31.03<br>Thu. | You Tobb Live     | M4: Real-world PIM: Samsung HBM-PIM (PDF) (PPT)                         |                                                |                |

| W5  | 07.04<br>Thu. | You Tube Live     | M5: How to Evaluate Data<br>Movement Bottlenecks<br>(PDF) (PPT)         |                                                |                |

| W6  | 14.04<br>Thu. | You Tube Live     | M6: Real-world PIM: SK Hynix AiM (PDF) (PPT)                            |                                                |                |

| W7  | 21.04<br>Thu. | You Premiere      | M7: Programming PIM Architectures (PDF) (PPT)                           |                                                |                |

| W8  | 28.04<br>Thu. | You Tube Premiere | M8: Benchmarking and Workload<br>Suitability on PIM<br>(PDF) (PPT)      |                                                |                |

| W9  | 05.05<br>Thu. | You Tube Premiere | M9: Real-world PIM: Samsung AXDIMM (PDF) (PPT)                          |                                                |                |

| W10 | 12.05<br>Thu. | You De Premiere   | M10: Real-world PIM: Alibaba HB-PNM  (PDF) (PPT)                        |                                                |                |

| W11 | 19.05<br>Thu. | You Tube Live     | M11: SpMV on a Real PIM Architecture  (PDF) (PPT)                       |                                                |                |

| W12 | 26.05<br>Thu. | You Tube Live     | M12: End-to-End Framework for<br>Processing-using-Memory<br>(PDF) (PPT) |                                                |                |

| W13 | 02.06<br>Thu. | YouTube Live      | M13: Bit-Serial SIMD Processing using DRAM  (PDF) (PPT)                 |                                                |                |

| W14 | 09.06<br>Thu. | You Tube Live     | M14: Analyzing and Mitigating ML<br>Inference Bottlenecks               |                                                |                |

| W15 | 15.06<br>Thu. | You Tube Live     | M15: In-Memory HTAP Databases with HW/SW Co-design (PDF) are (PPT)      |                                                |                |

| W16 | 23.06<br>Thu. | You Tube Live     | M16: In-Storage Processing for Genome Analysis (PDF) (PPT)              |                                                |                |

| W17 | 18.07<br>Mon. | You Tube Premiere | M17: How to Enable the Adoption of PIM?                                 |                                                |                |

| W18 | 09.08<br>Tue. | You Tube Premiere | SS1: ISVLSI 2022 Special Session on PIM (PDF & PPT)                     |                                                |                |

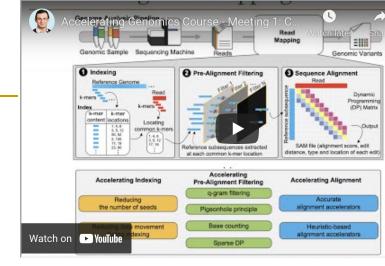

# Genomics (Spring 2022)

### Spring 2022 Edition:

https://safari.ethz.ch/projects and semi nars/spring2022/doku.php?id=bioinforma tics

### Youtube Livestream:

https://www.youtube.com/watch?v=DEL

5A Y3TI&list=PL5Q2soXY2Zi8NrPDgOR

1yRU Cxxjw-u18

### Project course

- Taken by Bachelor's/Master's students

- Genomics lectures

- Hands-on research exploration

- Many research readings

https://www.youtube.com/onurmutlulectures

### Spring 2022 Meetings/Schedule

|          | Week | Date          | Livestream        | Meeting                                                                           | Learning<br>Materials                             |

|----------|------|---------------|-------------------|-----------------------------------------------------------------------------------|---------------------------------------------------|

|          | W1   | 11.3<br>Fri.  | You Tube Live     | M1: P&S Accelerating Genomics Course Introduction & Project Proposals (PDF) (PPT) | Required<br>Materials<br>Recommended<br>Materials |

|          | W2   | 18.3<br>Fri.  | You Tube Live     | M2: Introduction to Sequencing (PDF) (PPT)                                        |                                                   |

|          | W3   | 25.3<br>Fri.  | You Tube Premiere | M3: Read Mapping  (PDF) (PPT)                                                     |                                                   |

|          | W4   | 01.04<br>Fri. | You Tube Premiere | M4: GateKeeper  (PDF) (PPT)                                                       |                                                   |

|          | W5   | 08.04<br>Fri. | You Tube Premiere | M5: MAGNET & Shouji (PDF) (PPT)                                                   |                                                   |

|          | W6   | 15.4<br>Fri.  | You Tube Premiere | M6: SneakySnake (PDF) (PPT)                                                       |                                                   |

|          | W7   | 29.4<br>Fri.  | You Tube Premiere | M7: GenStore (PDF) (PPT)                                                          |                                                   |

|          | W8   | 06.05<br>Fri. | You Tube Premiere | M8: GRIM-Filter  (PDF) (PPT)                                                      |                                                   |

|          | W9   | 13.05<br>Fri. | You Tube Premiere | M9: Genome Assembly (PDF) (PPT)                                                   |                                                   |

| <u>S</u> | W10  | 20.05<br>Fri. | You Tube Live     | M10: Genomic Data Sharing Under Differential Privacy (PDF) (PPT)                  |                                                   |

|          | W11  | 10.06<br>Fri. | You Tube Premiere | M11: Accelerating Genome Sequence Analysis (PDF) (PPT)                            |                                                   |

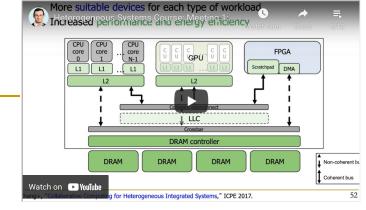

# Hetero. Systems (Spring'22)

### Spring 2022 Edition:

https://safari.ethz.ch/projects and semi nars/spring2022/doku.php?id=heterogen eous systems

### Youtube Livestream:

https://www.youtube.com/watch?v=oFO 5fTrgFIY&list=PL5Q2soXY2Zi9XrgXR38IM FTimY6h7Gzm

### Project course

- Taken by Bachelor's/Master's students

- GPU and Parallelism lectures

- Hands-on research exploration

- Many research readings

https://www.youtube.com/onurmutlulectures

### Spring 2022 Meetings/Schedule

| Week | Date          | Livestream        | Meeting                                                              | Learning<br>Materials                          | Assignments |

|------|---------------|-------------------|----------------------------------------------------------------------|------------------------------------------------|-------------|

| W1   | 15.03<br>Tue. | You Tube Premiere | M1: P&S Course Presentation (PDF) (PPT)                              | Required Materials<br>Recommended<br>Materials | HW 0 Out    |

| W2   | 22.03<br>Tue. | You Tube Premiere | M2: SIMD Processing and GPUs (PDF) (PPT)                             |                                                |             |

| W3   | 29.03<br>Tue. | You Tube Premiere | M3: GPU Software Hierarchy (PDF) (PPT)                               |                                                |             |

| W4   | 05.04<br>Tue. | You Tube Premiere | M4: GPU Memory Hierarchy (PDF) (PPT)                                 |                                                |             |

| W5   | 12.04<br>Tue. | You Tube Premiere | M5: GPU Performance Considerations (PDF) (PPT)                       |                                                |             |

| W6   | 19.04<br>Tue. | You Tube Premiere | M6: Parallel Patterns: Reduction (PDF) (PPT)                         |                                                |             |

| W7   | 26.04<br>Tue. | You Tube Premiere | M7: Parallel Patterns: Histogram (PDF) (PPT)                         |                                                |             |

| W8   | 03.05<br>Tue. | You Tube Premiere | M8: Parallel Patterns: Convolution (PDF) (PPT)                       |                                                |             |

| W9   | 10.05<br>Tue. | You Tube Premiere | M9: Parallel Patterns: Prefix Sum (Scan) (Com (PDF) (PPT)            |                                                |             |

| W10  | 17.05<br>Tue. | You Tube Premiere | M10: Parallel Patterns: Sparse Matrices (PDF) (PPT)                  |                                                |             |

| W11  | 24.05<br>Tue. | You Tube Premiere | M11: Parallel Patterns: Graph<br>Search<br>(PDF) (PPT)               |                                                |             |

| W12  | 01.06<br>Wed. | You Tube Premiere | M12: Parallel Patterns: Merge<br>Sort<br>(PDF) (PPT)                 |                                                |             |

| W13  | 07.06<br>Tue. | You Tube Premiere | M13: Dynamic Parallelism (PDF) (PPT)                                 |                                                |             |

| W14  | 15.06<br>Wed. | You Tube Premiere | M14: Collaborative Computing (PDF) (PPT)                             |                                                |             |

| W15  | 24.06<br>Fri. | You Tube Premiere | M15: GPU Acceleration of Genome Sequence Alignment (PDF) (PDF) (PPT) |                                                |             |

| W16  | 14.07<br>Thu. | You Tube Premiere | M16: Accelerating Agent-based Simulations                            |                                                |             |

# HW/SW Co-Design (Spring 2022)

### Spring 2022 Edition:

https://safari.ethz.ch/projects and semi nars/spring2022/doku.php?id=hw sw co design

### Youtube Livestream:

https://youtube.com/playlist?list=PL5Q2s oXY2Zi8nH7un3ghD2nutKWWDk-NK

### Project course

- Taken by Bachelor's/Master's students

- HW/SW co-design lectures

- Hands-on research exploration

- Many research readings

https://www.youtube.com/onurmutlulectures

SAFARI

### 2022 Meetings/Schedule (Tentative)

| Week | Date  | Livestream    | Meeting                               | Materials | Assignments |

|------|-------|---------------|---------------------------------------|-----------|-------------|

| W0   | 16.03 | You Tube Live | Intro to HW/SW Co-Design (PPTX) (PDF) | Required  | HW 0 Out    |

| W1   | 23.03 |               | Project selection                     | Required  |             |

| W2   | 30.03 | You Tube Live | Virtual Memory (I)  (PPTX) (PDF)      |           |             |

| W3   | 13.04 | You Tube Live | Virtual Memory (II)  (PPTX) (PDF)     |           |             |

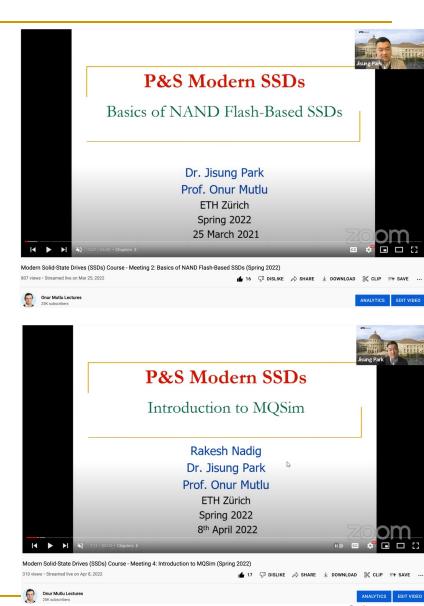

# SSD Course (Spring 2022)

### Spring 2022 Edition:

https://safari.ethz.ch/projects and semi nars/spring2022/doku.php?id=modern s sds

### Youtube Livestream:

https://www.youtube.com/watch?v= q4r m71DsY4&list=PL5Q2soXY2Zi8vabcse1kL 22DEcgMl2RAq

### Project course

- Taken by Bachelor's/Master's students

- SSD Basics and Advanced Topics

- Hands-on research exploration

- Many research readings

https://www.youtube.com/onurmutlulectures

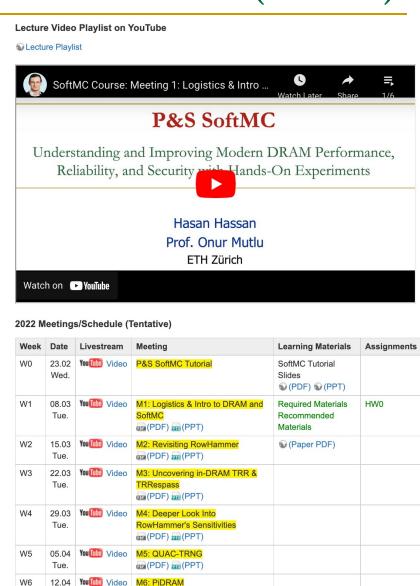

# Projects & Seminars: SoftMC FPGA-Based Exploration of DRAM and RowHammer (Fall 2022)

### Fall 2022 Edition:

https://safari.ethz.ch/projects and seminars/fall2022/doku.php?id=softmc

### Spring 2022 Edition:

https://safari.ethz.ch/projects\_and\_seminars/spring2022/doku.php?id=softmc

### Youtube Livestream (Spring 2022):

https://www.youtube.com/watch?v=r5QxuoJWttg &list=PL5Q2soXY2Zi 1trfCckr6PTN8WR72icUO

### Bachelor's course

- Elective at ETH Zurich

- Introduction to DRAM organization & operation

- Tutorial on using FPGA-based infrastructure

- Verilog & C++

- Potential research exploration

(PDF) (PPT)

Shttps://www.youtube.com/onurmutlulectures

# Projects & Seminars: Ramulator

### Exploration of Emerging Memory Systems (Fall 2022)

### Fall 2022 Edition:

https://safari.ethz.ch/projects and seminars/fall2 022/doku.php?id=ramulator

### Spring 2022 Edition:

https://safari.ethz.ch/projects and seminars/spring2022/doku.php?id=ramulator

### Youtube Livestream (Spring 2022):

https://www.youtube.com/watch?v=aMllXRQd3s&list=PL5Q2soXY2Zi\_TlmLGw\_Z8hBo292 5ZApqV

### Bachelor's course

- Elective at ETH Zurich

- Introduction to memory system simulation

- Tutorial on using Ramulator

- □ C++

- Potential research exploration

### 2022 Meetings/Schedule (Tentative)

| Week | Date          | Livestream     | Meeting                                                                        | Learning<br>Materials | Assignments |

|------|---------------|----------------|--------------------------------------------------------------------------------|-----------------------|-------------|

| W1   | 09.03<br>Wed. | YouTube Video  | M1: Logistics & Intro to Simulating Memory Systems Using Ramulator (PDF) (PPT) |                       | HW0         |

| W2   | 16.03<br>Fri. | You Tube Video | M2: Tutorial on Using Ramulator (PDF) (PPT)                                    |                       |             |

| W3   | 25.02<br>Fri. | You Tube Video | M3: BlockHammer  (PDF) (PPT)                                                   |                       |             |

| W4   | 01.04<br>Fri. | You Tube Video | M4: CLR-DRAM  (PDF) (PPT)                                                      |                       |             |

| W5   | 08.04<br>Fri. | You Tube Video | M5: SIMDRAM  (PDF) (PPT)                                                       |                       |             |

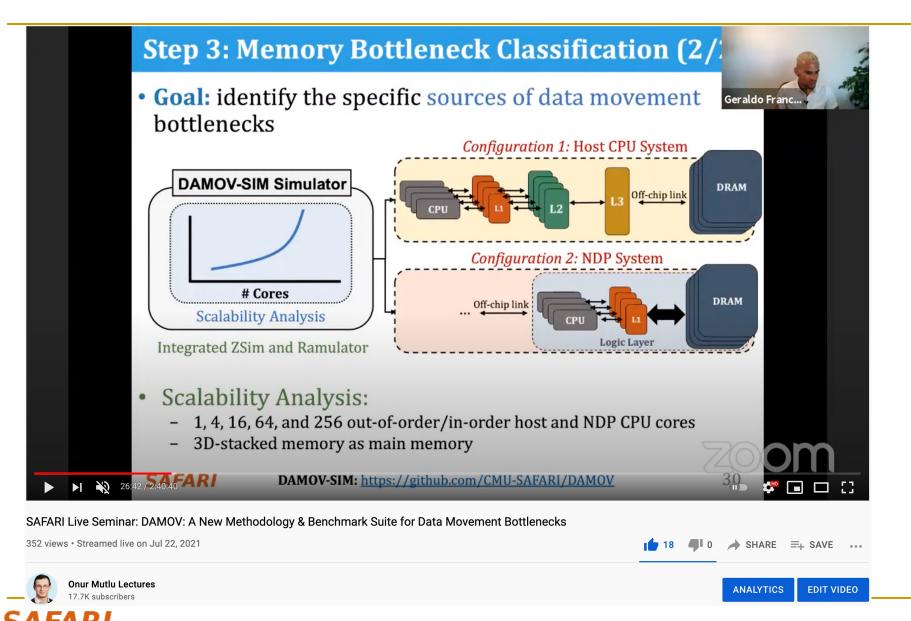

| W6   | 29.04<br>Fri. | You Tube Video | M6: DAMOV (PDF) aaa (PPT)                                                      |                       |             |

| W7   | 06.05<br>Fri. | You Tube Video | M7: Syncron  (PDF) (PPT)                                                       |                       |             |

Shttps://www.youtube.com/onurmutlulectures

# Hands-On Projects & Seminars Courses

https://safari.ethz.ch/projects\_and\_seminars/doku.php

# Focus on Insight Encourage New Ideas

Principle: Learning and Scholarship

# Focus on learning and scholarship

# SAFARI Live Seminars (I)

# SAFARI Live Seminars (II)

SAFARI Live Seminar: Nastaran Hajinazar 27 Oct 2021 Posted on October 1, 2021 by ewent

SAFARI Live Seminar: Damla Senol Cali 07 Nov 2021 Posted on October 18, 2021 by ewent

SAFARI Live Seminar: Gennady Pekhimenko 08 Nov 2021 osted on November 1, 2021 by ewent

SAFARI Live Seminar: Serghei Mangul 11 Nov 2021

SAFARI Live Seminar: Rahul Bera 20 Dec 2021

Join us for our joint SAFARI Live Seminar & EFCL Seminar with Fabrice Devaux, UPMEM Wednesday, February 2 2022 at 11:00 am Zurich time (CET)

SAFARI Live Seminar: Fabrice Devaux, 2 Feb 2022

sted on January 15, 2022 by ewent

Posted on January 19, 2022 by ewent

SAFARI Live Seminar: Lois Orosa, 10 Feb 2022 Join us for our next SAFARI Live Seminar with Lois Orosa. Thursday, February 10 at 5:00 pm Zurich time (CET)

Posted on January 16, 2022 by ewent

Join us for our SAFARI Live Seminar with Sean Lie, Cerebras Systems Monday. February 28 2022 at 6:00 pm Zurich time (CET)

# SAFARI Live Seminars (Upcoming Talks)

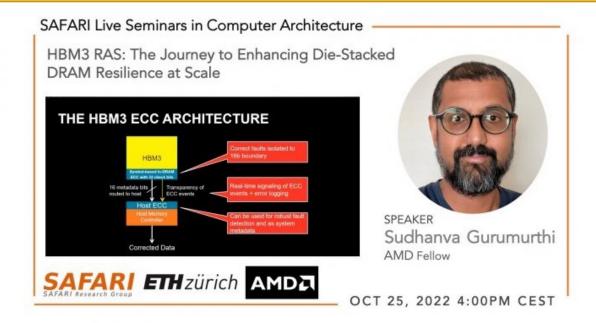

SAFARI Live Seminar: Sudhanva Gurumurthi, Oct 25 2022

Posted on September 6, 2022 by ewent

We're excited to have Sudhanva Gurumurthi with us for our upcoming SAFARI Live Seminar!

Date: Tuesday, October 25 at 4:00 pm Zurich time (CEST)

Speaker: Sudhanva Gurumurthi, AMD Fellow

Link: Livestream on YouTube Link

Title: HBM3 RAS: The Journey to Enhancing Die-Stacked DRAM Resilience at Scale

# SAFARI Live Seminars (Upcoming Talks)

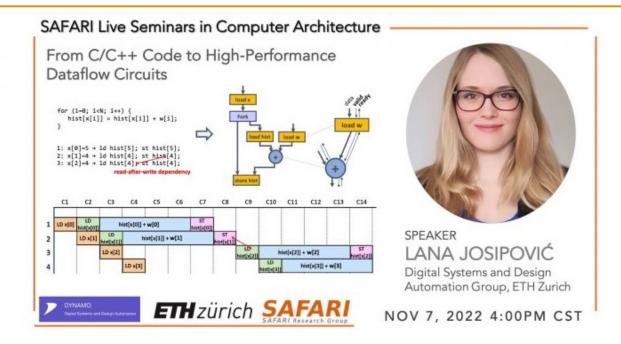

SAFARI Live Seminar: Lana Josipović, Nov 7 2022

Posted on September 9, 2022 by ewent

Join us for our upcoming SAFARI Live Seminar

Date: Monday, November 7 at 4:00 pm Zurich time (CET)

Speaker: Lana Josipovic, DYNAMO Research Group, ETH Zurich

Link: Livestream on YouTube Link

Title: From C/C++ Code to High-Performance Dataflow Circuits

# SAFARI Live Seminars (Upcoming Talks)

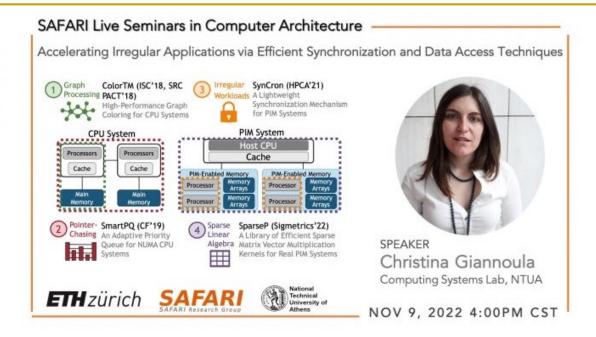

### SAFARI Live Seminar, Christina Giannoula, Nov 9 2022

Posted on September 15, 2022 by ewent

Join us for our upcoming SAFARI Live Seminar

Date: Wednesday, November 9 at 4:00 pm Zurich time (CET)

Speaker: Christina Giannoula, School of Electrical and Computer Engineering, NTUA

Link: Livestream on YouTube Link

Title: Accelerating Irregular Applications via Efficient Synchronization and Data Access

**Techniques**

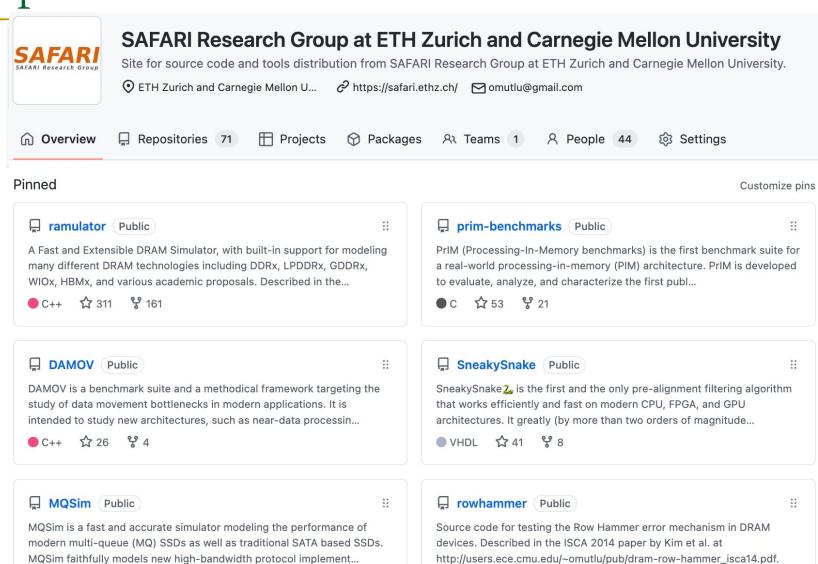

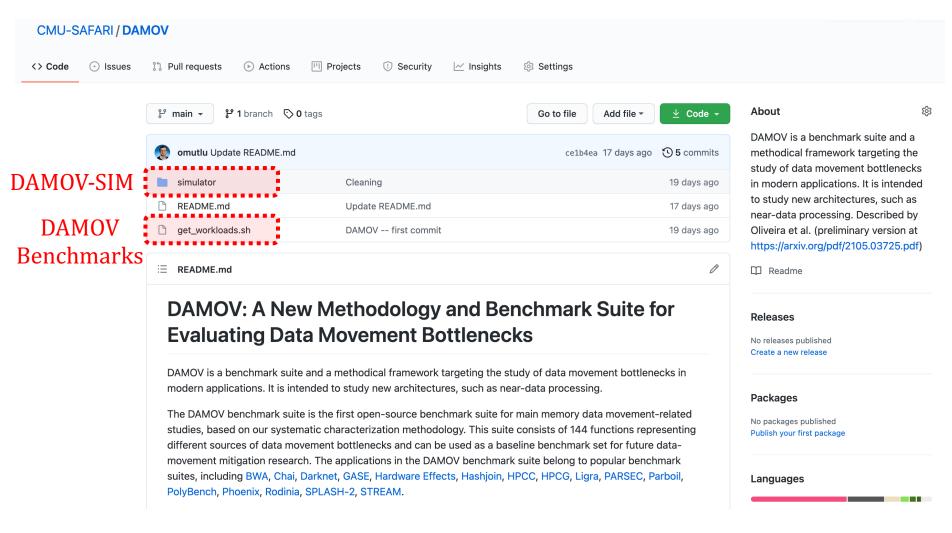

#### Open-Source Artifacts

https://github.com/CMU-SAFARI

#### Open Source Tools: SAFARI GitHub

☆ 146

<del>۷</del> 41

**189**

#### Some Open Source Tools (I)

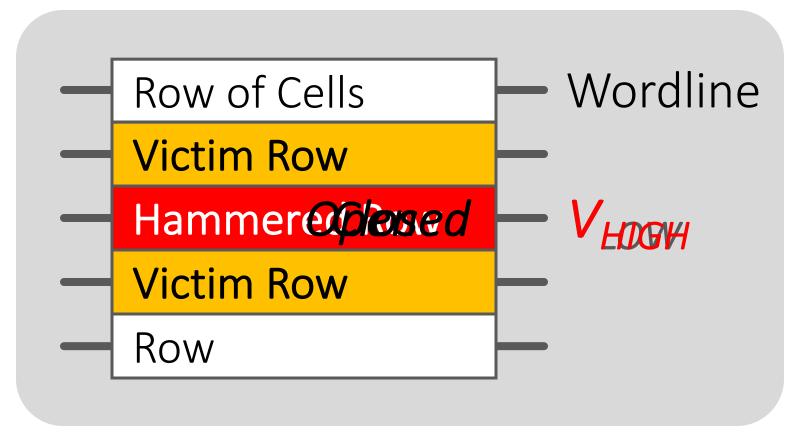

- Rowhammer Program to Induce RowHammer Errors

- https://github.com/CMU-SAFARI/rowhammer

- Ramulator Fast and Extensible DRAM Simulator

- https://github.com/CMU-SAFARI/ramulator

- MemSim Simple Memory Simulator

- https://github.com/CMU-SAFARI/memsim

- NOCulator Flexible Network-on-Chip Simulator

- https://github.com/CMU-SAFARI/NOCulator

- SoftMC FPGA-Based DRAM Testing Infrastructure

- https://github.com/CMU-SAFARI/SoftMC

- Other open-source software from my group

- https://github.com/CMU-SAFARI/

#### Some Open Source Tools (II)

- MQSim A Fast Modern SSD Simulator

- https://github.com/CMU-SAFARI/MQSim

- Mosaic GPU Simulator Supporting Concurrent Applications

- https://github.com/CMU-SAFARI/Mosaic

- IMPICA Processing in 3D-Stacked Memory Simulator

- https://github.com/CMU-SAFARI/IMPICA

- SMLA Detailed 3D-Stacked Memory Simulator

- https://github.com/CMU-SAFARI/SMLA

- HWASim Simulator for Heterogeneous CPU-HWA Systems

- https://github.com/CMU-SAFARI/HWASim

- Other open-source software from my group

- https://github.com/CMU-SAFARI/

#### More Open Source Tools (III)

#### **COVIDHunter** Pythia COVIDHunter \*\*: An accurate and flexible COVID-19 outbreak simulation model that A Customizable Hardware Prefetching Framework Using Online Reinforcement Learning. forecasts the strength of future mitigation measures and the numbers of cases, machine-learning reinforcement-learning prefetcher cache-replacement hospitalizations, and deaths for a given day, while considering the potential effect of branch-predictor champsim-simulator champsim-tracer environmental conditions. Described by Alser et al. (preliminary version at https://arxiv.org/abs/2... ● C++ ♀1 ☆0 ⊙0 ┆ 0 Updated yesterday simulation epidemiology covid-19 covid-19-data covid-19-tracker reproduction-number covidhunter BurstLink ● Swift គ្នMIT ម្1 ភ្ជ 5 ⊙ 0 ព្រ 0 Updated on Jun 27 ಳ0 ದು0 ⊙0 ಭಾ0 Updated 21 days ago prim-benchmarks MIG-7-PHY-DDR3-Controller PrIM (Processing-In-Memory benchmarks) is the first benchmark suite for a real-world A DDR3 Controller that uses the Xilinx MIG-7 PHY to interface with DDR3 devices. processing-in-memory (PIM) architecture. PrIM is developed to evaluate, analyze, and Verilog ♀1 ☆1 ⊙0 ☎0 Updated on Aug 22 characterize the first publicly-available real-world PIM architecture, the UPMEM PIM architecture. Described by Gómez-Luna et al. (preliminary version at Pythia-HDL https://arxiv.org/abs/2... Implementation of Pythia: A Customizable Hardware Prefetching Framework Using Online ●C ΦMIT ೪8 ☆18 ⊙0 11 0 Updated on Jun 16 Reinforcement Learning in Chisel HDL. machine-learning scala reinforcement-learning chisel chisel3 firrtl hdl **SNP-Selective-Hiding** An optimization-based mechanism of M to selectively hide the minimum number of ● Scala គ្នMIT មុ0 ☆0 ⊙0 រៀ0 Updated on Jul 31 overlapping SNPs among the family members 🚵 who participated in the genomic studies (i.e. GWAS). Our goal is to distort the dependencies among the family members in the HARP (Private) original database for achieving better privacy without significantly degrading the data មុ0 ☆0 ⊙0 រុះ្ 0 Updated on Jul 31 gwas genomics data-privacy differential-privacy genomic-data-analysis **EINSim** laplace-distribution genomic-privacy DRAM error-correction code (ECC) simulator incorporating statistical error properties ● MATLAB មុ0 ☆0 ⊙0 រា្ល 0 Updated on Jun 16 and DRAM design characteristics for inferring pre-correction error characteristics using only the post-correction errors. Described in the 2019 DSN paper by Patel et al.: SneakySnake https://people.inf.ethz.ch/omutlu/pub/understanding-and-modeling-in-DRAM-SneakySnake 2 is the first and the only pre-alignment filtering algorithm that works ECC\_dsn19.pdf. efficiently and fast on modern CPU, FPGA, and GPU architectures. It greatly (by more simulator reliability statistical-inference dram error-correcting-codes than two orders of magnitude) expedites sequence alignment calculation for both short map-estimation error-correction and long reads. Described in the Bioinformatics (2020) by Alser et al. https://arxiv.org/abs... ● C++ 毎 MIT ♥0 ☆5 ⊙0 st 0 Updated on Jul 29 fpga gpu smith-waterman needleman-wunsch sequence-alignment DAMOV long-reads minimap2 DAMOV is a benchmark suite and a methodical framework targeting the study of data ● VHDL ΦGPL-3.0 ゅ6 ☆35 ⊙0 11 1 Updated on May 12 movement bottlenecks in modern applications. It is intended to study new architectures, such as near-data processing. Described by Oliveira et al. (preliminary version at https://arxiv.org/pdf/2105.03725.pdf) A Fast and Extensible DRAM Simulator, with built-in support for modeling many different ● C++ ♀1 ☆12 ⊙1 ३ 0 Updated on Jul 13 DRAM technologies including DDRx, LPDDRx, GDDRx, WIOx, HBMx, and various academic proposals. Described in the IEEE CAL 2015 paper by Kim et al. at MetaSys http://users.ece.cmu.edu/~omutlu/pub/ramulator\_dram\_simulator-ieee-cal15.pdf Metasys is the first open-source FPGA-based infrastructure with a prototype in a RISC-V core, to enable the rapid implementation and evaluation of a wide range of cross-layer software/hardware cooperative techniques techniques in real hardware. Described in our GenASM pre-print: https://arxiv.org/abs/2105.08123 Source code for the software implementations of the GenASM algorithms proposed in our ម្1 ☆0 ⊙0 រា្0 Updated on Jul 9 MICRO 2020 paper: Senol Cali et. al., "GenASM: A High-Performance, Low-Power Approximate String Matching Acceleration Framework for Genome Sequence Analysis" at **NATSA** https://people.inf.ethz.ch/omutlu/pub/GenASM-approximate-string-matching-framework-NATSA is the first near-data-processing accelerator for time series analysis based on the for-genome-analys... Matrix Profile (SCRIMP) algorithm. NATSA exploits modern 3D-stacked High Bandwidth approximate-string-matching read-mapping hw-sw-co-design Memory (HBM) to enable efficient and fast matrix profile computation near memory. read-alignment bitap-algorithm pre-alignment-filtering Described in ICCD 2020 by Fernandez et al. https://people.inf.ethz.ch/omutlu/pub/NATSA\_time-... genome-sequence-analysis accelerator hbm time-series-analysis matrix-profile near-data-processing ● C ஷ GPL-3.0 ೪3 ☆ 20 ⊙ 0 ൂ 0 Updated on Mar 22 C++ ♀1 ☆4 ⊙0 ₥0 Updated on Jun 28 AirLift is a tool that updates mapped reads from one reference genome to another. Unlike

#### Papers, Talks, Videos, Artifacts

All are openly available at

https://people.inf.ethz.ch/omutlu/projects.htm

http://scholar.google.com/citations?user=7XyGUGkAAAAJ&hl=en

https://www.youtube.com/onurmutlulectures

https://github.com/CMU-SAFARI/

## Create an environment that values free exploration, openness, collaboration, hard work, creativity

#### My Suggestions to You

Suggestion to Researchers: Principle: Passion

# Follow Your Passion (Do not get derailed by naysayers)

Principle: Build Infrastructure

## Build Infrastructure to Enable Your Passion

Principle: Work Hard

### Work Hard to Enable Your Passion

Suggestion to Researchers: Principle: Resilience

#### Be Resilient

Principle: Learning and Scholarship

## Focus on learning and scholarship

Principle: Learning and Scholarship

## The quality of your work defines your impact

Principle: Good Mindset, Goals & Focus

# You can make a good impact on the world

#### Research & Teaching: Some Overview Talks

#### https://www.youtube.com/onurmutlulectures

- Future Computing Architectures

- https://www.youtube.com/watch?v=kqiZISOcGFM&list=PL5Q2soXY2Zi8D 5MGV6EnXEJHnV2YFBJI&index=1

- Enabling In-Memory Computation

- https://www.youtube.com/watch?v=njX 14584Jw&list=PL5Q2soXY2Zi8D 5MGV6EnXEJHnV2YFBJl&index=16

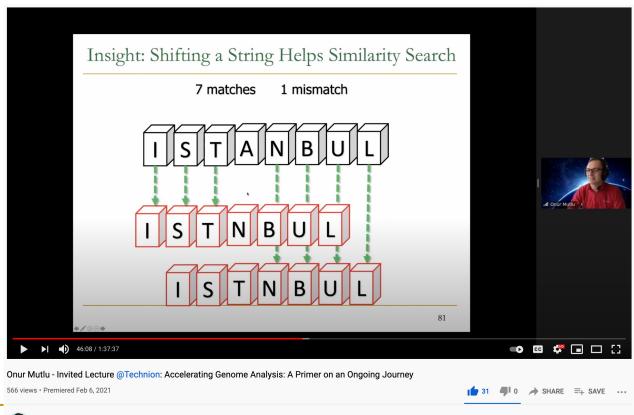

- Accelerating Genome Analysis

- https://www.youtube.com/watch?v=r7sn41lH-4A&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=41

- Rethinking Memory System Design

- https://www.youtube.com/watch?v=F7xZLNMIY1E&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=3

- Intelligent Architectures for Intelligent Machines

- https://www.youtube.com/watch?v=c6\_LgzuNdkw&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=25

- The Story of RowHammer

- https://www.youtube.com/watch?v=sgd7PHQQ1AI&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=39

#### An Interview on Research and Education

- Computing Research and Education (@ ISCA 2019)

- https://www.youtube.com/watch?v=8ffSEKZhmvo&list=PL5Q2 soXY2Zi\_4oP9LdL3cc8G6NIjD2Ydz

- Maurice Wilkes Award Speech (10 minutes)

- https://www.youtube.com/watch?v=tcQ3zZ3JpuA&list=PL5Q2 soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=15

#### More Thoughts and Suggestions

Onur Mutlu,

#### "Some Reflections (on DRAM)"

Award Speech for <u>ACM SIGARCH Maurice Wilkes Award</u>, at the **ISCA** Awards Ceremony, Phoenix, AZ, USA, 25 June 2019.

[Slides (pptx) (pdf)]

[Video of Award Acceptance Speech (Youtube; 10 minutes) (Youku; 13 minutes)]

[Video of Interview after Award Acceptance (Youtube; 1 hour 6 minutes) (Youku;

1 hour 6 minutes)

[News Article on "ACM SIGARCH Maurice Wilkes Award goes to Prof. Onur Mutlu"]

Onur Mutlu,

#### "How to Build an Impactful Research Group"

57th Design Automation Conference Early Career Workshop (DAC), Virtual, 19 July 2020.

[Slides (pptx) (pdf)]

#### More Thoughts and Suggestions (II)

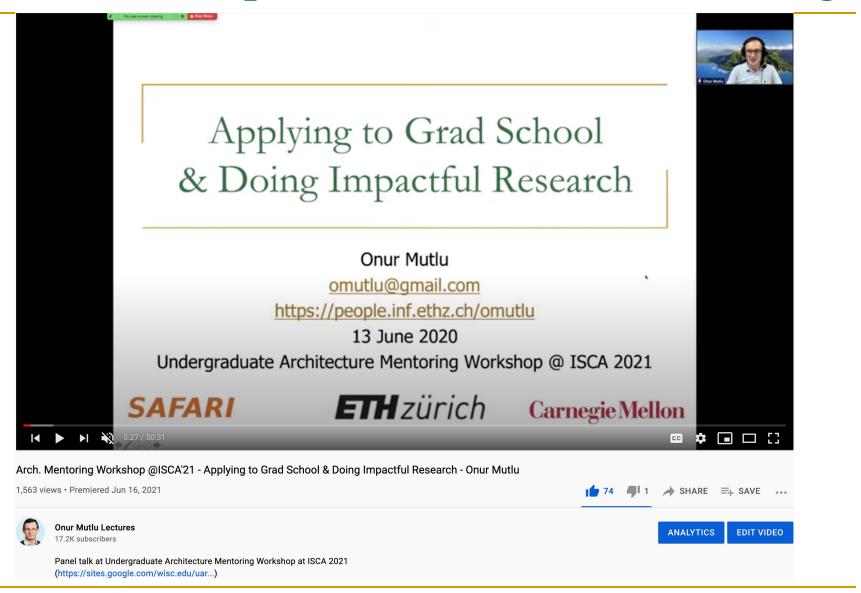

Onur Mutlu,

"Computer Architecture: Why Is It So Important and Exciting Today?"

Invited Lecture at *Izmir Institute of Technology (IYTE)*, Virtual, 16 October 2020.

[Slides (pptx) (pdf)]

[Talk Video (2 hours 12 minutes)]

Onur Mutlu,

"Applying to Graduate School & Doing Impactful Research"

Invited Panel Talk at <u>the 3rd Undergraduate Mentoring Workshop</u>, held with <u>the</u> <u>48th International Symposium on Computer Architecture</u> (**ISCA**), Virtual, 18 June 2021.

[Slides (pptx) (pdf)]

[Talk Video (50 minutes)]

#### A Talk on Impactful Research & Teaching

#### Required Reading

## Richard Hamming "You and Your Research"

Transcription of the

Bell Communications Research Colloquium Seminar

7 March 1986

https://safari.ethz.ch/architecture/fall2021/lib/exe/fetch.php?media=youandyourresearch.pdf

#### How to Approach This Course

### "Formative Experience"

#### How to Approach This Course

## "High investment, high return"

## "Recorded lectures allowed me to go over the lectures when necessary"

#### How to Approach This Course

# "YouTube allows me to watch the lectures on my TV"

### "The lecturer is very responsive to questions and remarks from students"

"Perhaps even better than in-person classes as questions can be asked asynchronously"

#### How to Approach This Course

## "Easy to understand course format with homework, labs, and lectures"

"Paper reviews + assignments + labs, a really great plan to learn in a comprehensive way"

## "the course was fantastic and I would do it again at any time"

## Learning experience Long-term tradeoff analysis Critical thinking & decision making

#### How to Approach This Course

Concepts & Ideas **Fundamentals** Cutting-edge Hands-on learning

Your mindset will determine what you get out of the course

#### Required Reading on Mindset & More

## Richard Hamming "You and Your Research"

Transcription of the

Bell Communications Research Colloquium Seminar

7 March 1986

https://safari.ethz.ch/architecture/fall2021/lib/exe/fetch.php?media=youandyourresearch.pdf

#### Required Reading on Mindset & More

If you really want to be a first-class scientist you need to know yourself, your weaknesses, your strengths, and your bad faults, like my egotism. How can you convert a fault to an asset? How can you convert a situation where you haven't got enough manpower to move into a direction when that's exactly what you need to do? I say again that I have seen, as I studied the history, the successful scientist changed the viewpoint and what was a defect became an asset.

In summary, I claim that some of the reasons why so many people who have greatness within their grasp don't succeed are: they don't work on important problems, they don't become emotionally involved, they don't try and change what is difficult to some other situation which is easily done but is still important, and they keep giving themselves alibis why they don't. They keep saying that it is a matter of luck. I've told you how easy it is; furthermore I've told you how to reform. Therefore, go forth and become great scientists!

# Why Study Computer Architecture?

### Computer Architecture

- is the science and art of designing computing platforms (hardware, interface, system SW, and programming model)

- to achieve a set of design goals

- E.g., highest performance on earth on workloads X, Y, Z

- E.g., longest battery life at a form factor that fits in your pocket with cost < \$\$\$ CHF</li>

- E.g., best average performance across all known workloads at the best performance/cost ratio

- **...**

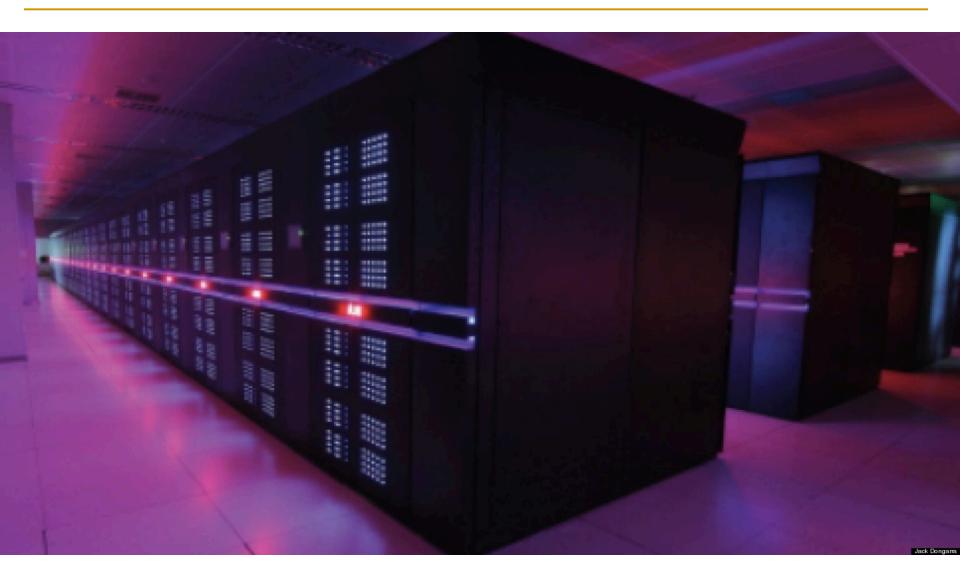

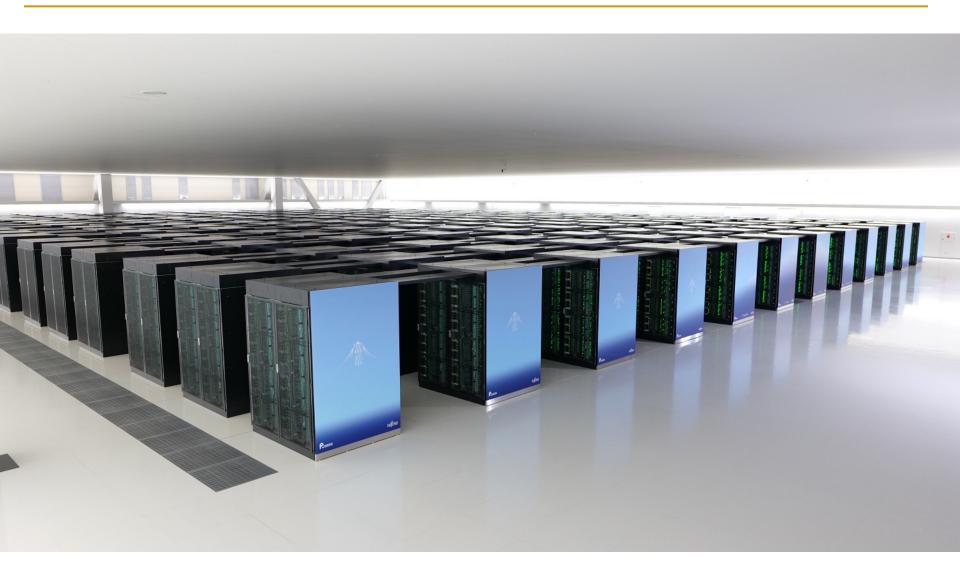

- □ Designing a supercomputer is different from designing a smartphone → But, many fundamental principles are similar

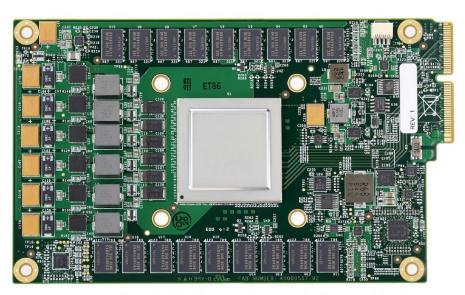

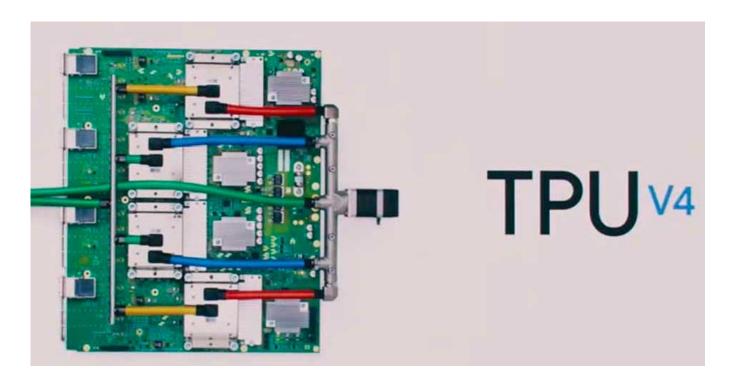

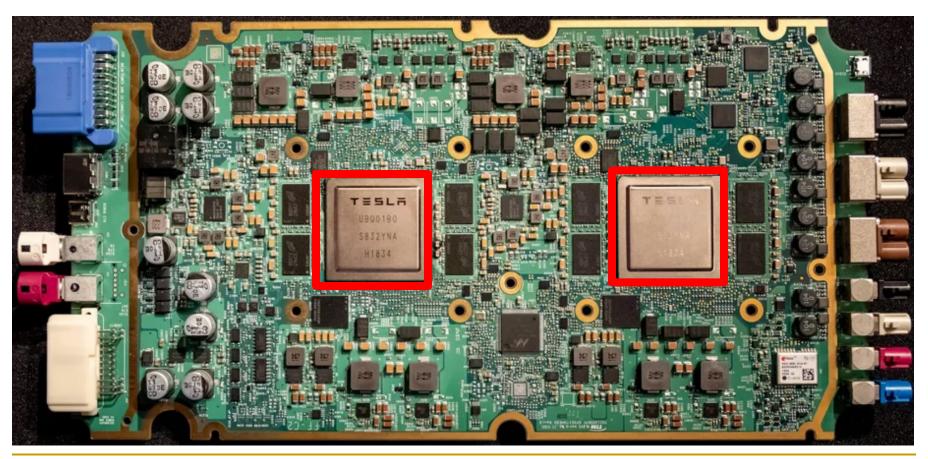

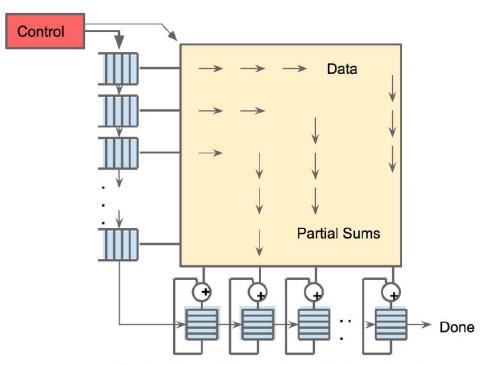

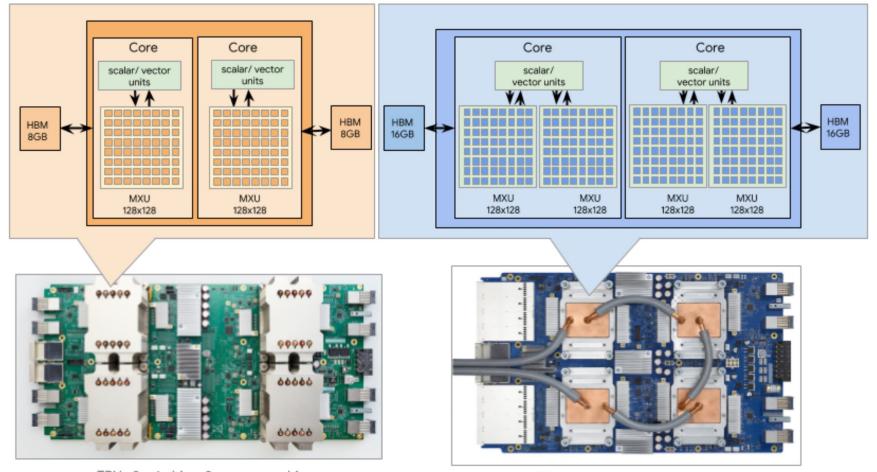

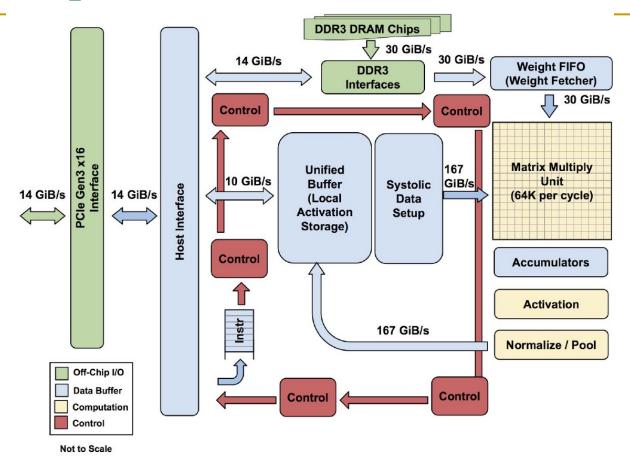

**Figure 3.** TPU Printed Circuit Board. It can be inserted in the slot for an SATA disk in a server, but the card uses PCIe Gen3 x16.

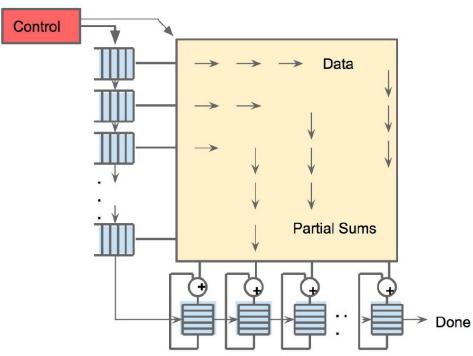

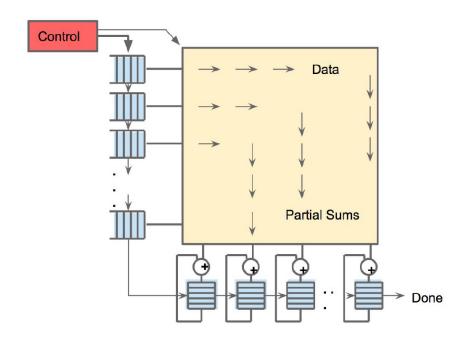

**Figure 4.** Systolic data flow of the Matrix Multiply Unit. Software has the illusion that each 256B input is read at once, and they instantly update one location of each of 256 accumulator RAMs.

Jouppi et al., "In-Datacenter Performance Analysis of a Tensor Processing Unit", ISCA 2017.

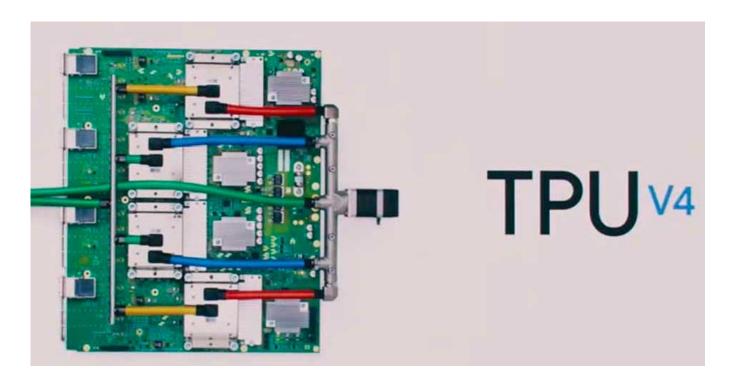

#### New ML applications (vs. TPU3):

- Computer vision

- Natural Language Processing (NLP)

- Recommender system

- Reinforcement learning that plays Go

250 TFLOPS per chip in 2021 vs 90 TFLOPS in TPU3

1 ExaFLOPS per board

https://spectrum.ieee.org/tech-talk/computing/hardware/heres-how-googles-tpu-v4-ai-chip-stacked-up-in-training-tests

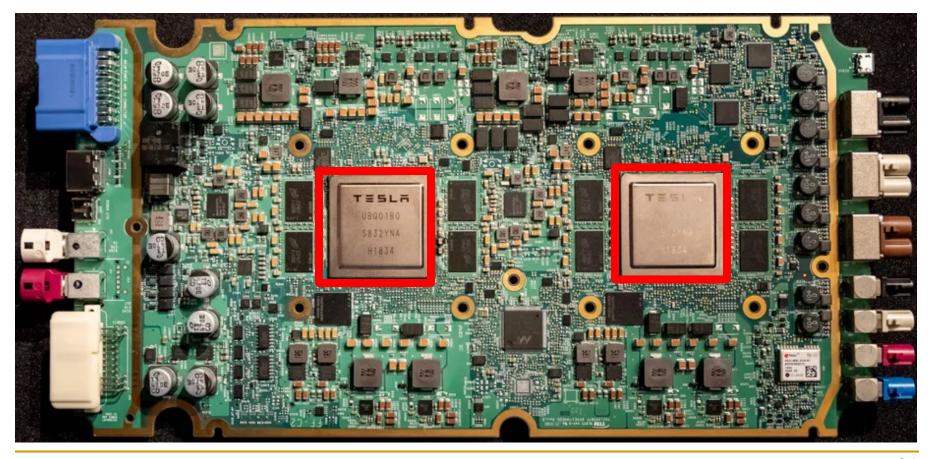

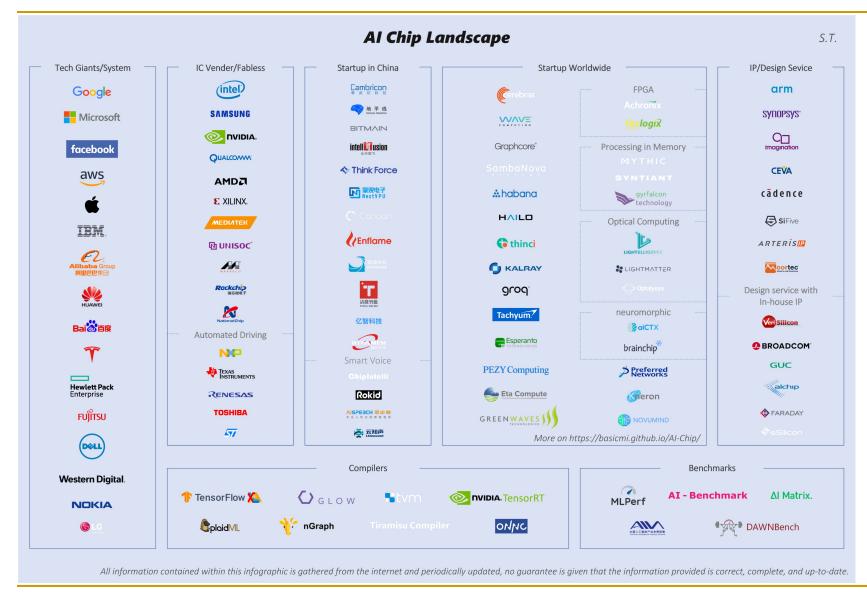

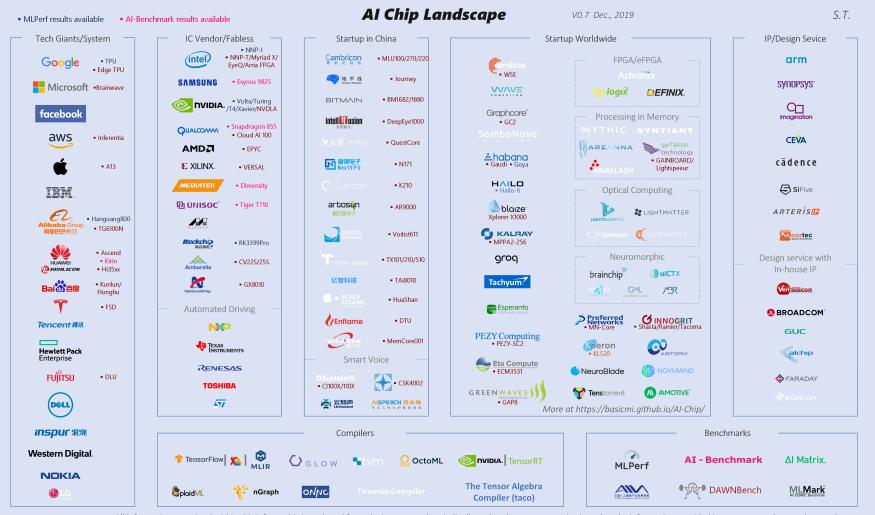

- ML accelerator: 260 mm<sup>2</sup>, 6 billion transistors,

600 GFLOPS GPU, 12 ARM 2.2 GHz CPUs.

- Two redundant chips for better safety.

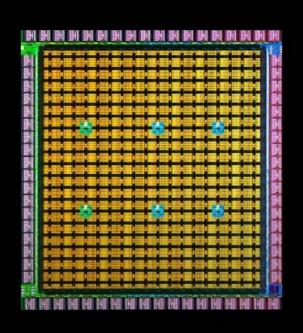

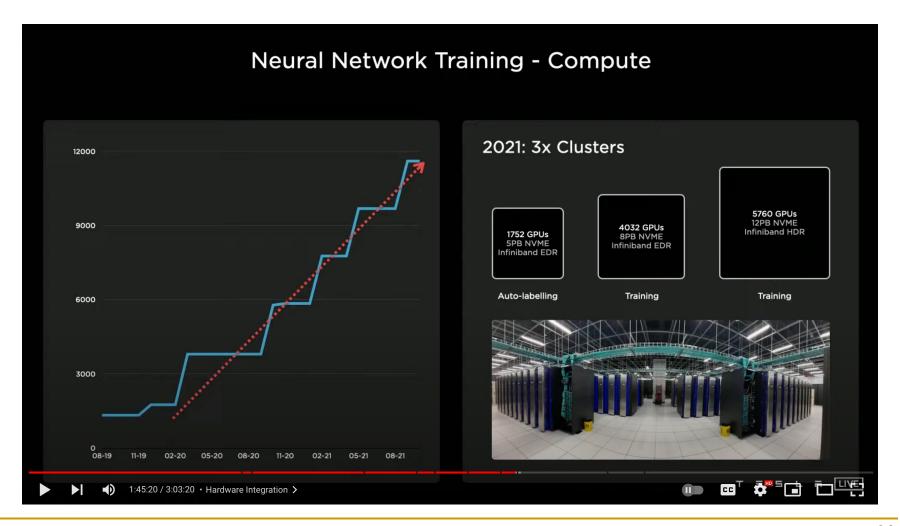

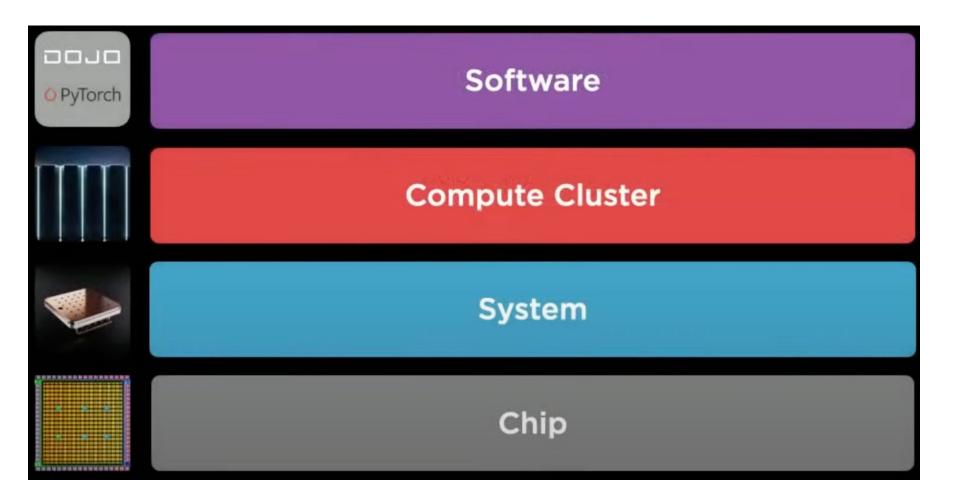

Tesla Dojo Chip & System

TESLA

Tesla Dojo Chip & System

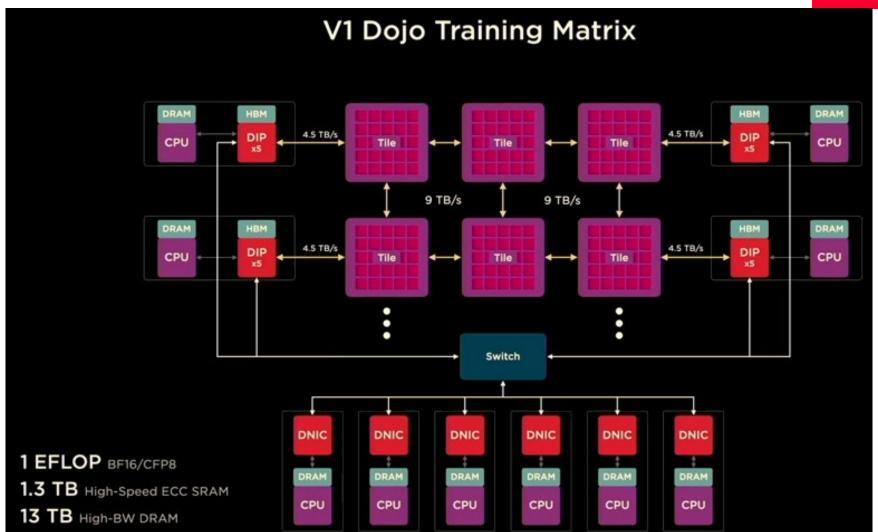

#### **V1 Dojo Interface Processor**

#### **32GB High-Bandwidth Memory**

- 800 GB/s Total Memory Bandwidth

#### 900 GB/s TTP Interface

- Tesla Transport Protocol (TTP) Full custom protocol

- Provides full DRAM bandwidth to Training Tile

#### 50 GB/s TTP over Ethernet (TTPoE)

- Enables extending communication over standard Ethernet

- Native hardware support

#### 32 GB/s Gen4 PCIe Interface

TESLA

Tesla Dojo Chip & System

#### D1 Chip

362 TFLOPs BF16/CFP8

22.6 TFLOPs FP32

10TBps/dir. on-Chip Bandwidth

4TBps/edge. off-Chip Bandwidth

**400W TDP**

645mm<sup>2</sup> 7nm Technology

**50 Billion** Transistors

11+ Miles Of Wires

TESLA

Tesla Dojo Chip & System

TESLA

Tesla Dojo Chip & System

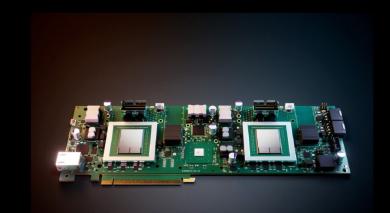

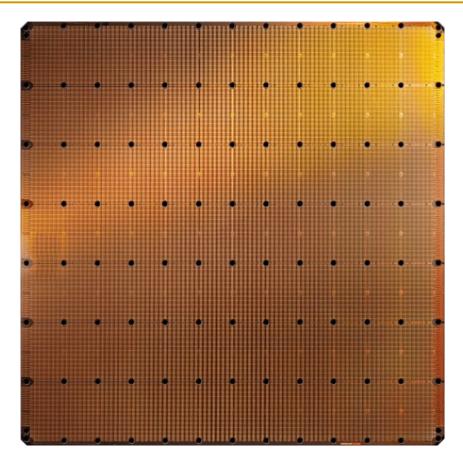

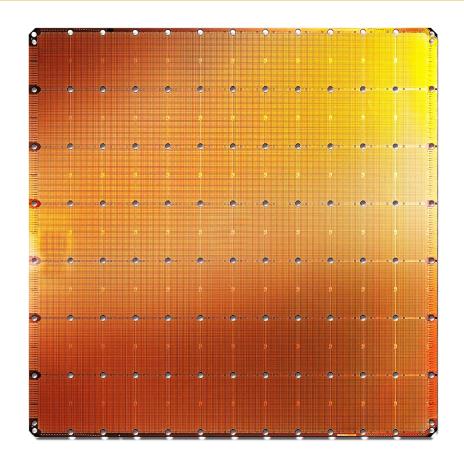

The largest ML accelerator chip (2021)

850,000 cores

#### **Cerebras WSE-2**

2.6 Trillion transistors 46,225 mm<sup>2</sup>

#### **Largest GPU**

54.2 Billion transistors 826 mm<sup>2</sup>

**NVIDIA** Ampere GA100

https://www.anandtech.com/show/14758/hot-chips-31-live-blogs-cerebras-wafer-scale-deep-learning

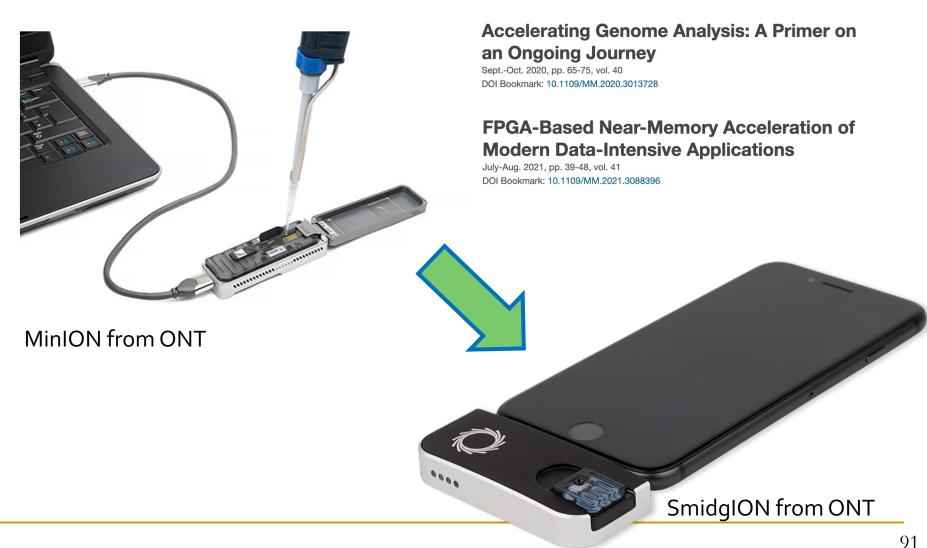

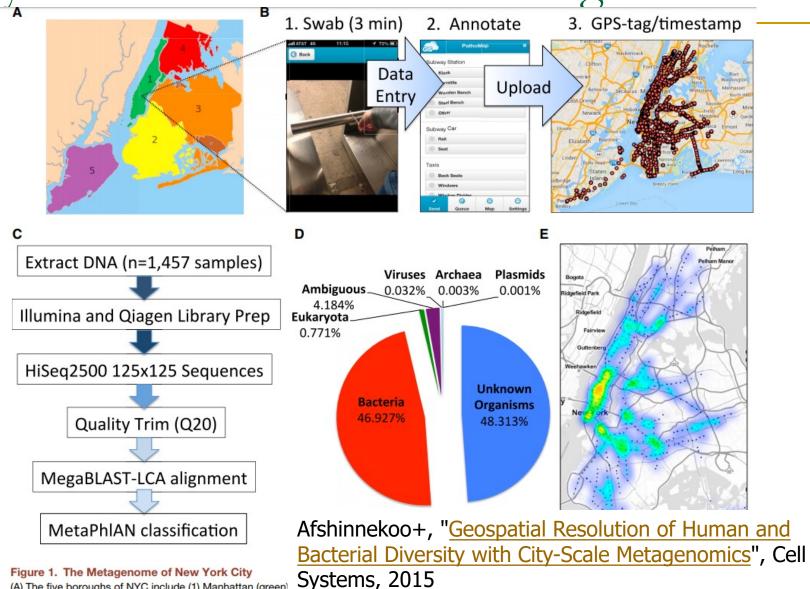

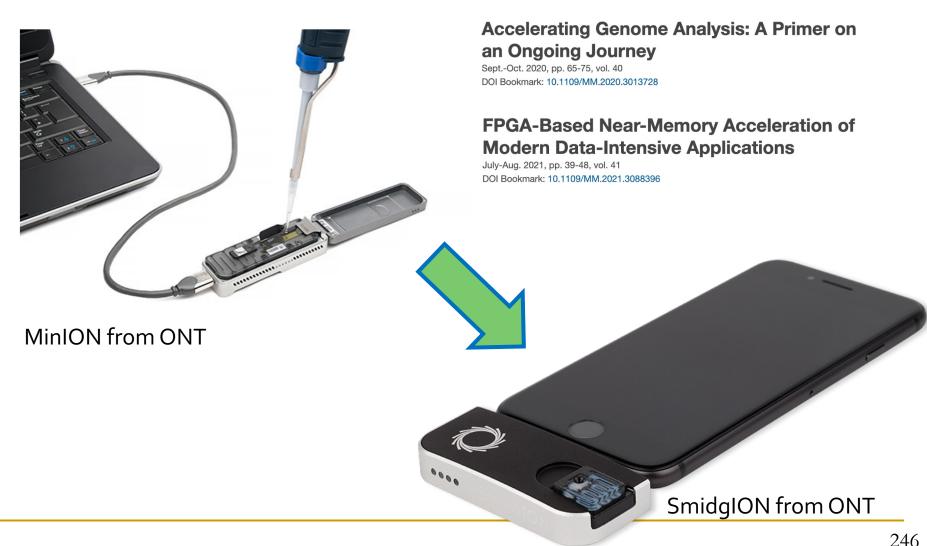

Mohammed Alser, Zülal Bingöl, Damla Senol Cali, Jeremie Kim, Saugata Ghose, Can Alkan, Onur Mutlu "Accelerating Genome Analysis: A Primer on an Ongoing Journey" IEEE Micro, August 2020.

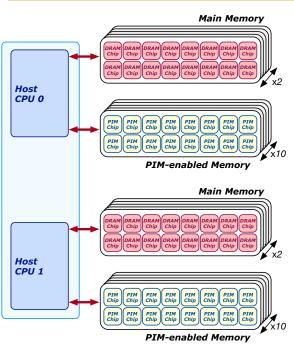

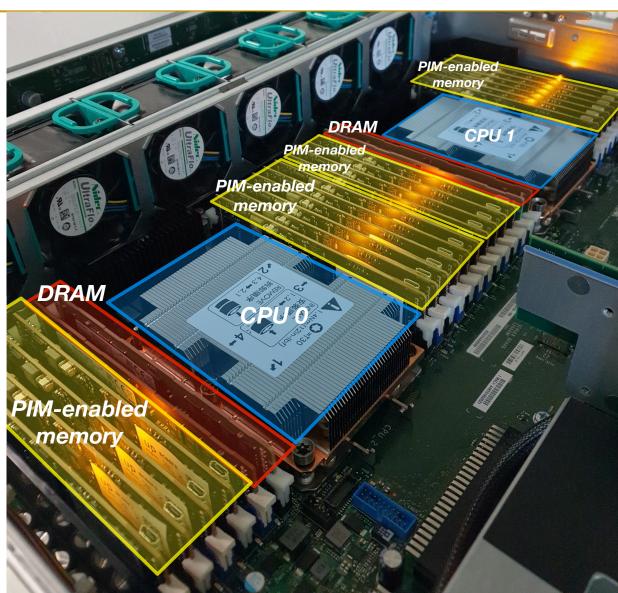

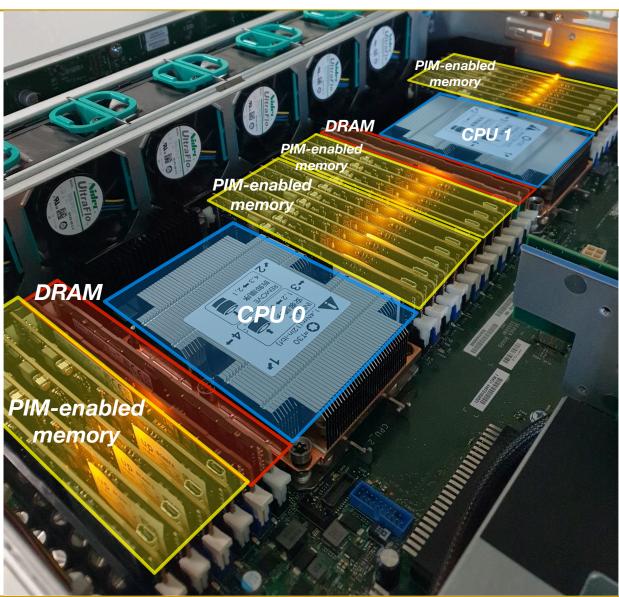

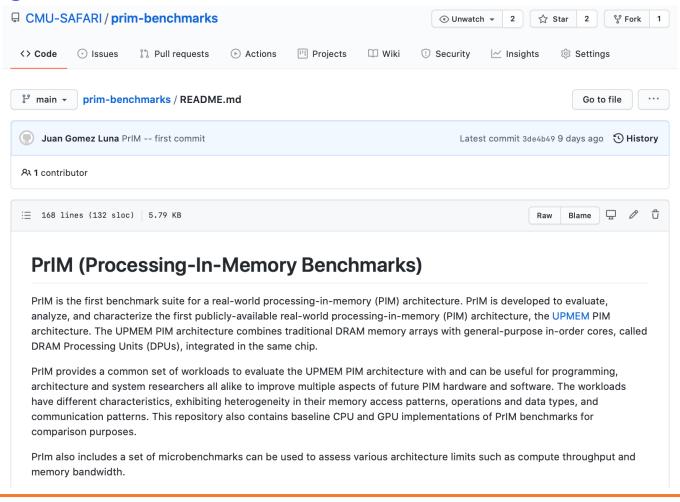

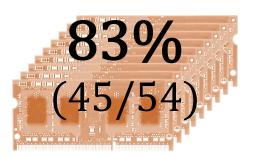

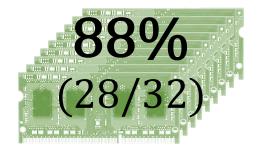

#### Benchmarking a New Paradigm: An Experimental Analysis of a Real Processing-in-Memory Architecture

JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland

IZZAT EL HAJJ, American University of Beirut, Lebanon

IVAN FERNANDEZ, ETH Zürich, Switzerland and University of Malaga, Spain

CHRISTINA GIANNOULA, ETH Zürich, Switzerland and NTUA, Greece

GERALDO F. OLIVEIRA, ETH Zürich, Switzerland

ONUR MUTLU, ETH Zürich, Switzerland

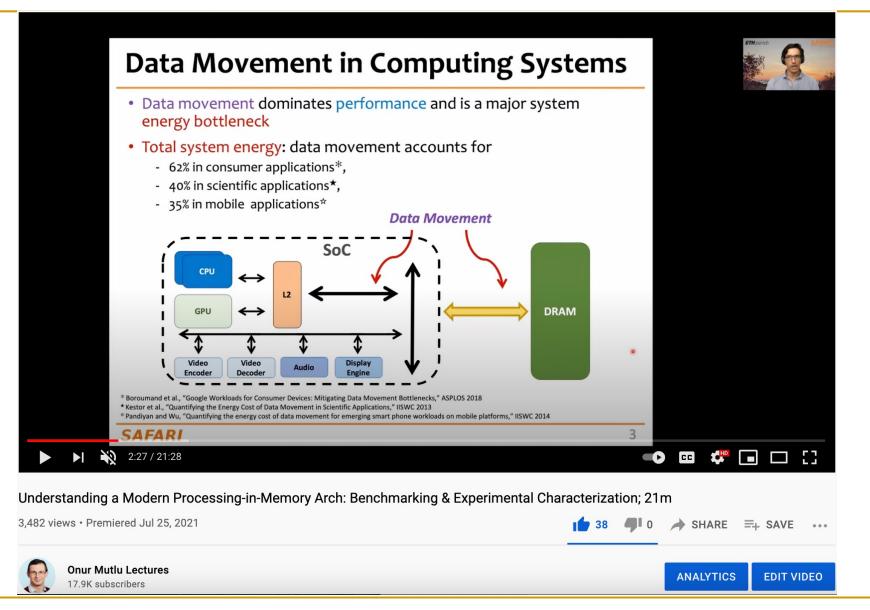

Many modern workloads, such as neural networks, databases, and graph processing, are fundamentally memory-bound. For such workloads, the data movement between main memory and CPU core imposes a significant overhead in terms of both latency and neary. A major reason is that this communication happens through a narrow bus with high latency and limited bandwidth, and the low data reuse in memory-bound workloads is insufficient to amortize the cost of main memory access. Fundamentally addressing this ideal movement bottleneck requires a paradigm where the memory system assumes an active role in computing by integrating processing capabilities. This paradigm is known as processing—in-memory (EM).

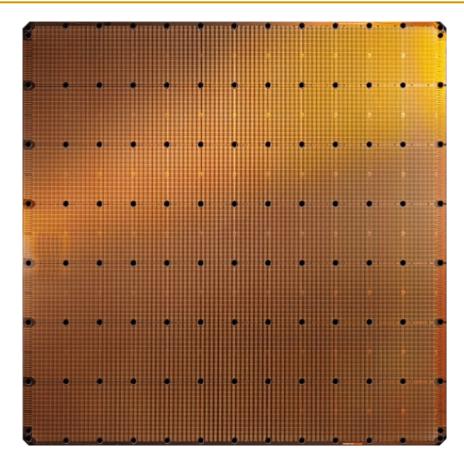

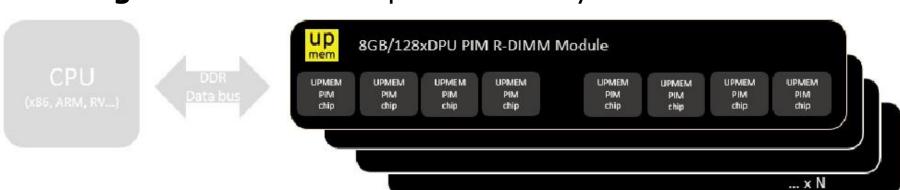

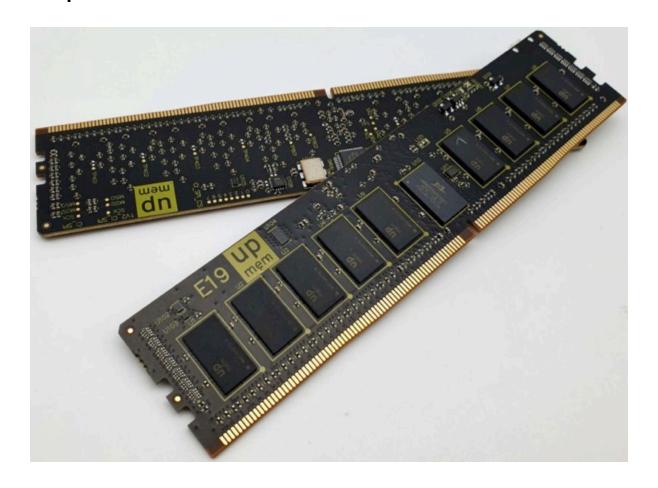

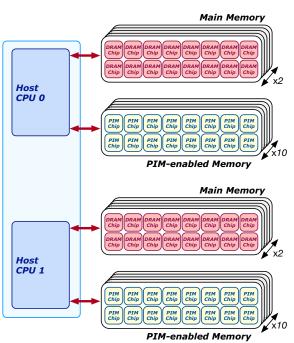

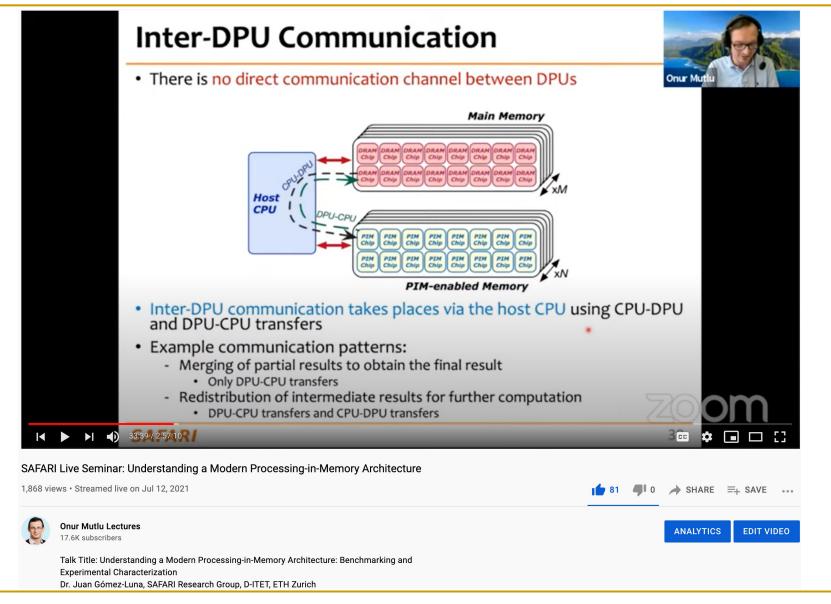

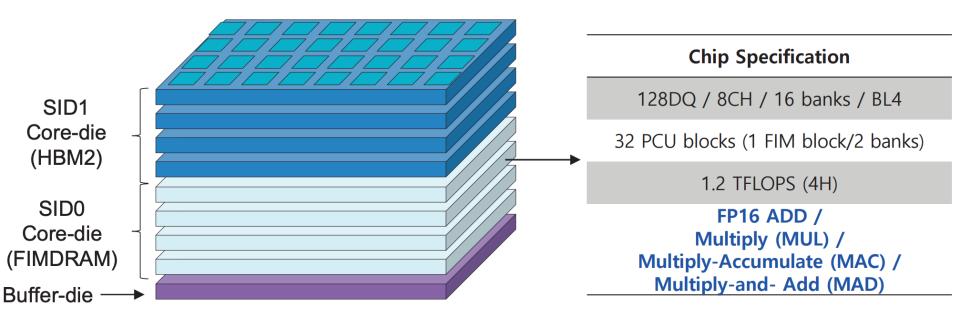

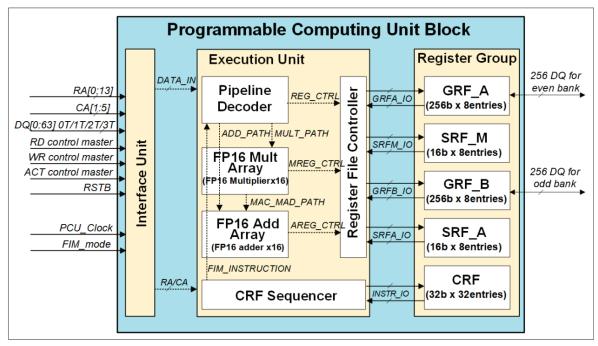

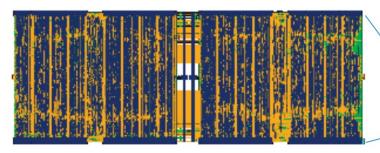

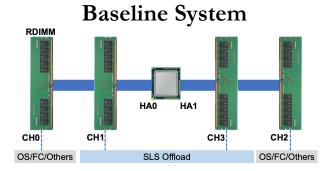

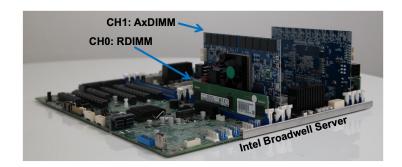

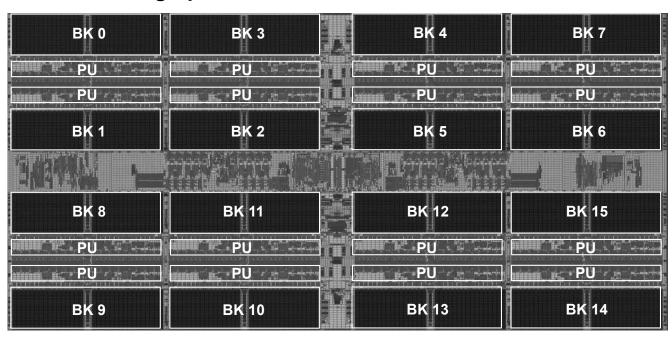

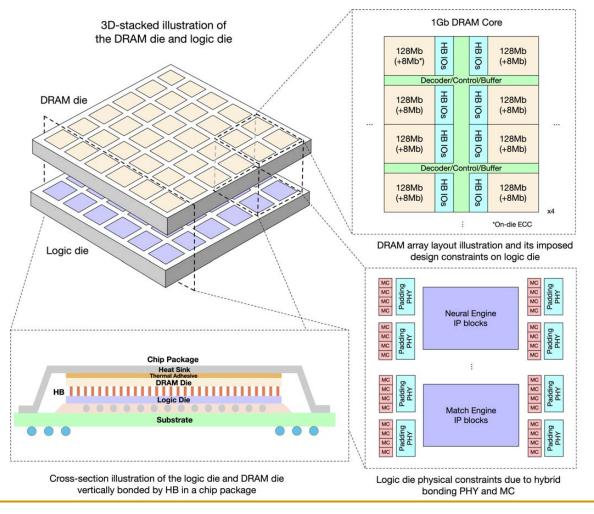

Recent research explores different forms of PIM architectures, motivated by the emergence of new 3Dstacked memory technologies that integrate memory with a logic layer where processing elements can be easily placed. Past works evaluate these architectures in simulation or, at best, with simplified hardware prototypes. In contrast, the UPMEM company has designed and manufactured the first publicly-available real-world PIM architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called DRAM Processing Units (DPUs), integrated in the same chip.

This paper provides the first comprehensive analysis of the first publicly-available real-world PIM architecture. We make two key contributions. First, we conduct an experimental characterization of the UPIMEM-based to PIM system using microbenchmarks to assess various architecture limits such as compute throughput and memory bandwidth, yielding new insights. Second, we present PPIM (Processing, in-Pigmory) benchmarks) as a benchmark suite of 16 workfoads from different application domains (e.g., dense/sparse linear algebra, databases, data naphytics, graph processing, which we identify as memory-bound. We evaluate the performance and scaling characteristics of PIM benchmarks on the UPIMEM PIM architecture, and compare their performance and energy consumption to their state-of-the-art CPU and CPU counterparts. Our extensive evaluation conducted on two real UPIMEM-based PIM systems with 640 and 2550 PDIS provides new insights about satiability of different workloads to the PIM systems with 640 was not software designers, and suggestions and hints for hardware and architecture designers of future PIM systems.

#### What is Computer Architecture?

The science and art of designing, selecting, and interconnecting hardware components and designing the hardware/software interface to create a computing system that meets functional, performance, energy consumption, cost, and other specific goals.

### The Transformation Hierarchy

Computer Architecture (expanded view)

Computer Architecture (narrow view)

## Computing System

Leiserson+, "There's plenty of room at the Top: What will drive computer performance after Moore's law?", Science, 2020

Richard Feynman, "There's Plenty of Room at the Bottom: An Invitation to Enter a New Field of Physics", a lecture given at Caltech, 1959.

for example, semiconductor technology

## Software & Hardware Optimizations

```

Multiplying Two 4096-by-4096 Matrices

for i in xrange(4096):

for j in xrange(4096):

for k in xrange(4096):

C[i][j] += A[i][k] * B[k][j]

7 8

9 10

11 12

```

| Implementation              | Running time (s) | Absolute speedup |

|-----------------------------|------------------|------------------|

| Python                      | 25,552.48        | 1x               |

| Java                        | 2,372.68         | 11x              |

| C                           | 542.67           | 47x              |

| Parallel loops              | 69.80            | 366x             |

| Parallel divide and conquer | 3.80             | 6,727x           |

| plus vectorization          | 1.10             | 23,224x          |

| plus AVX intrinsics         | 0.41             | 62,806x          |

Leiserson+, "There's plenty of room at the Top: What will drive computer performance after Moore's law?", Science, 2020

#### Why Study Computer Architecture?

- Enable better systems: make computers faster, cheaper, smaller, more reliable, ...

- By exploiting advances and changes in underlying technology/circuits

- Enable new applications

- Life-like 3D visualization 20 years ago? Virtual reality?

- Self-driving cars?

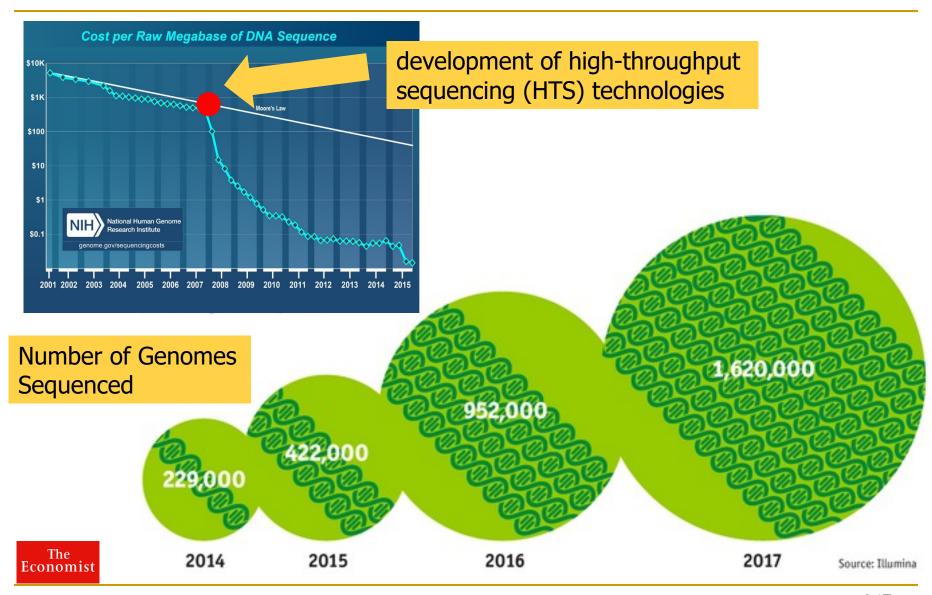

- Personalized genomics? Personalized medicine?

- Enable better solutions to problems

- Software innovation is built on trends and changes in computer architecture

- > 50% performance improvement per year has enabled this innovation

- Understand why computers work the way they do

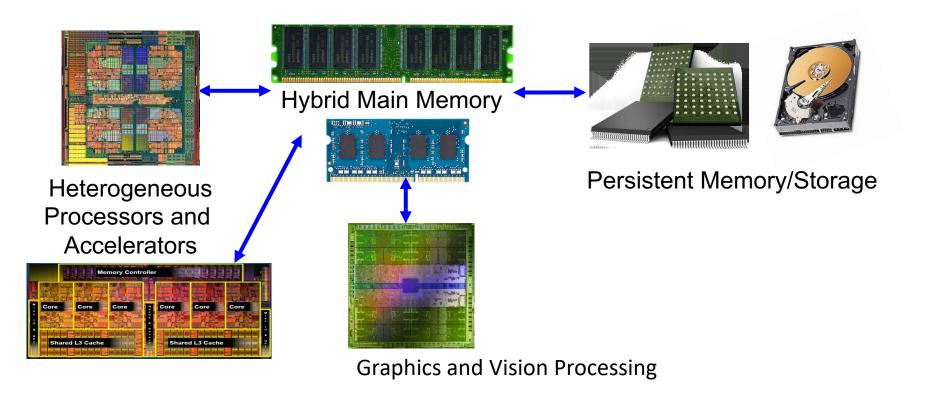

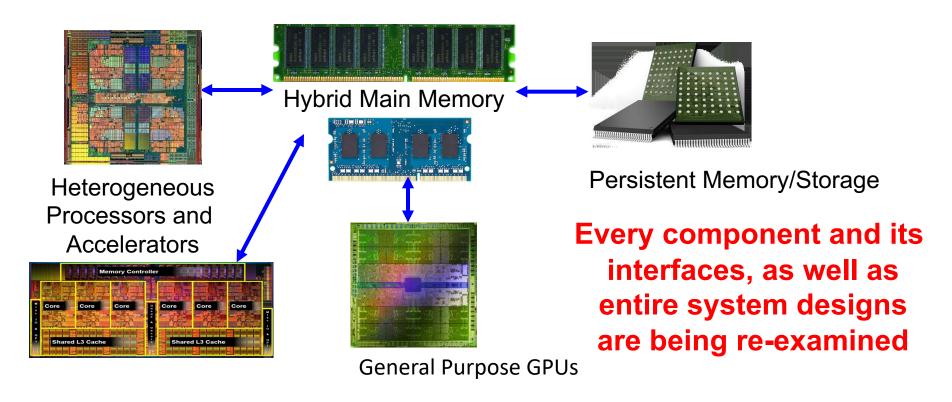

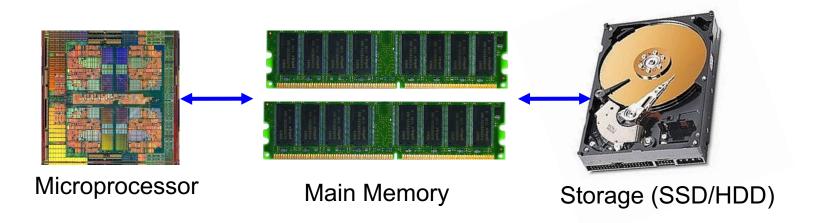

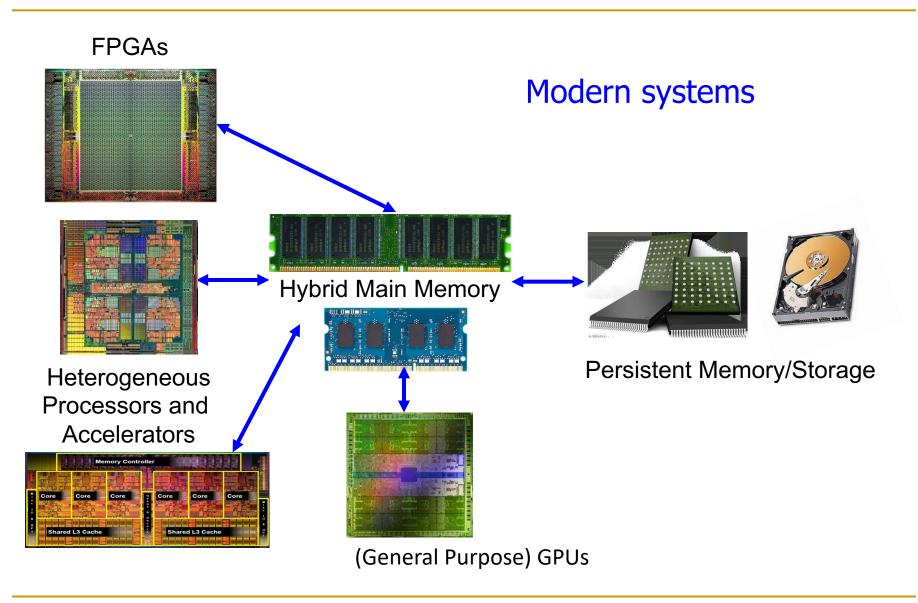

## Computer Architecture Today (I)

- Today is a very exciting time to study computer architecture

- Industry is in a large paradigm shift (to novel architectures)

- many different potential system designs possible

- Many difficult problems motivating and caused by the shift

- Huge hunger for data and new data-intensive applications

- Power/energy/thermal constraints

- Complexity of design

- Difficulties in technology scaling

- Memory bottleneck

- Reliability problems

- Programmability problems

- Security and privacy issues

- No clear, definitive answers to these problems

## Computer Architecture Today (II)

These problems affect all parts of the computing stack – if we do not change the way we design systems

Many new demands from the top (Look Up)

Fast changing demands and personalities of users (Look Up)

Many new issues at the bottom (Look Down)

No clear, definitive answers to these problems

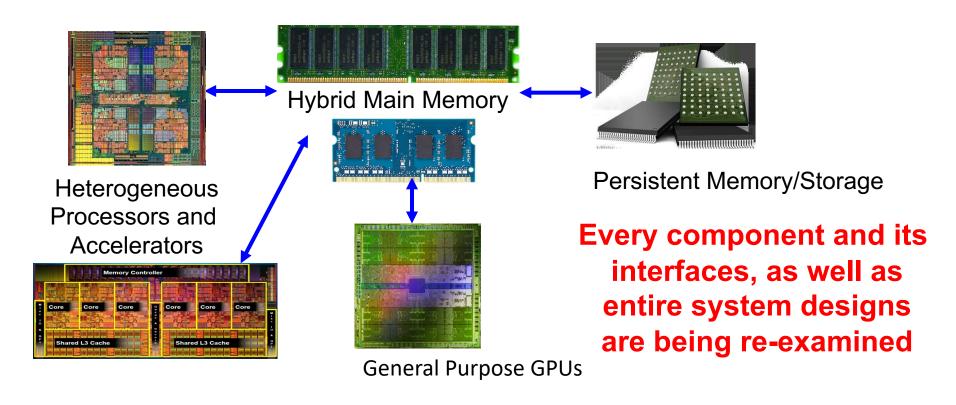

## Computer Architecture Today (III)

- Computing landscape is very different from 10-20 years ago

- Both UP (software and humanity trends) and DOWN (technologies and their issues), FORWARD and BACKWARD, and the resulting requirements and constraints

To achieve the highest energy efficiency and performance:

#### we must take the expanded view

of computer architecture

Co-design across the hierarchy:

Algorithms to devices

Specialize as much as possible within the design goals

#### Historical: Opportunities at the Bottom

#### There's Plenty of Room at the Bottom

From Wikipedia, the free encyclopedia

"There's Plenty of Room at the Bottom: An Invitation to Enter a New Field of Physics" was a lecture given by physicist Richard Feynman at the annual American Physical Society meeting at Caltech on December 29, 1959. [1] Feynman considered the possibility of direct manipulation of individual atoms as a more powerful form of synthetic chemistry than those used at the time. Although versions of the talk were reprinted in a few popular magazines, it went largely unnoticed and did not inspire the conceptual beginnings of the field. Beginning in the 1980s, nanotechnology advocates cited it to establish the scientific credibility of their work.

## Historical: Opportunities at the Bottom (II)

#### There's Plenty of Room at the Bottom

From Wikipedia, the free encyclopedia

Feynman considered some ramifications of a general ability to manipulate matter on an atomic scale. He was particularly interested in the possibilities of denser computer circuitry, and microscopes that could see things much smaller than is possible with scanning electron microscopes. These ideas were later realized by the use of the scanning tunneling microscope, the atomic force microscope and other examples of scanning probe microscopy and storage systems such as Millipede, created by researchers at IBM.

Feynman also suggested that it should be possible, in principle, to make nanoscale machines that "arrange the atoms the way we want", and do chemical synthesis by mechanical manipulation.

He also presented the possibility of "swallowing the doctor", an idea that he credited in the essay to his friend and graduate student Albert Hibbs. This concept involved building a tiny, swallowable surgical robot.

## Historical: Opportunities at the Top

#### **REVIEW**

## There's plenty of room at the Top: What will drive computer performance after Moore's law?

- (D) Charles E. Leiserson<sup>1</sup>, (D) Neil C. Thompson<sup>1,2,\*</sup>, (D) Joel S. Emer<sup>1,3</sup>, (D) Bradley C. Kuszmaul<sup>1,†</sup>, Butler W. Lampson<sup>1,4</sup>, (D)...

- + See all authors and affiliations

Science 05 Jun 2020: Vol. 368, Issue 6495, eaam9744 DOI: 10.1126/science.aam9744

Much of the improvement in computer performance comes from decades of miniaturization of computer components, a trend that was foreseen by the Nobel Prize-winning physicist Richard Feynman in his 1959 address, "There's Plenty of Room at the Bottom," to the American Physical Society. In 1975, Intel founder Gordon Moore predicted the regularity of this miniaturization trend, now called Moore's law, which, until recently, doubled the number of transistors on computer chips every 2 years.

Unfortunately, semiconductor miniaturization is running out of steam as a viable way to grow computer performance—there isn't much more room at the "Bottom." If growth in computing power stalls, practically all industries will face challenges to their productivity. Nevertheless, opportunities for growth in computing performance will still be available, especially at the "Top" of the computing-technology stack: software, algorithms, and hardware architecture.

### Axiom, Revisited

There is plenty of room both at the top and at the bottom

but much more so

when you

communicate well between and optimize across

the top and the bottom

## Hence the Expanded View

Computer Architecture (expanded view)

# Some Cross-Layer Design Examples (Foreshadowing)

#### EDEN: Data-Aware Efficient DNN Inference

Skanda Koppula, Lois Orosa, A. Giray Yaglikci, Roknoddin Azizi, Taha Shahroodi, Konstantinos Kanellopoulos, and Onur Mutlu,

<u>"EDEN: Enabling Energy-Efficient, High-Performance Deep Neural Network Inference Using Approximate DRAM"</u>

Proceedings of the <u>52nd International Symposium on Microarchitecture</u> (**MICRO**), Columbus, OH, USA, October 2019.

[Slides (pptx) (pdf)]

[<u>Lightning Talk Slides (pptx)</u> (pdf)]

[Poster (pptx) (pdf)]

[Lightning Talk Video (90 seconds)]

[Full Talk Lecture (38 minutes)]

#### EDEN: Enabling Energy-Efficient, High-Performance Deep Neural Network Inference Using Approximate DRAM

Skanda Koppula Lois Orosa A. Giray Yağlıkçı Roknoddin Azizi Taha Shahroodi Konstantinos Kanellopoulos Onur Mutlu ETH Zürich

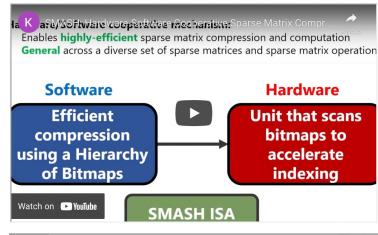

## SMASH: SW/HW Indexing Acceleration

Konstantinos Kanellopoulos, Nandita Vijaykumar, Christina Giannoula, Roknoddin Azizi, Skanda Koppula, Nika Mansouri Ghiasi, Taha Shahroodi, Juan Gomez-Luna, and Onur Mutlu,

"SMASH: Co-designing Software Compression and Hardware-<u>Accelerated Indexing for Efficient Sparse Matrix Operations</u>

Proceedings of the <u>52nd International Symposium on</u>

Microarchitecture (MICRO), Columbus, OH, USA, October 2019.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Poster (pptx) (pdf)]

[Lightning Talk Video (90 seconds)]

[Full Talk Lecture (30 minutes)]

#### SMASH: Co-designing Software Compression and Hardware-Accelerated Indexing for Efficient Sparse Matrix Operations

Konstantinos Kanellopoulos<sup>1</sup> Nandita Vijaykumar<sup>2,1</sup> Christina Giannoula<sup>1,3</sup> Roknoddin Azizi<sup>1</sup> Skanda Koppula<sup>1</sup> Nika Mansouri Ghiasi<sup>1</sup> Taha Shahroodi<sup>1</sup> Juan Gomez Luna<sup>1</sup> Onur Mutlu<sup>1,2</sup>

#### GenASM: HW/SW Approximate String Matching Accelerator

Damla Senol Cali, Gurpreet S. Kalsi, Zulal Bingol, Can Firtina, Lavanya Subramanian, Jeremie S. Kim, Rachata Ausavarungnirun, Mohammed Alser, Juan Gomez-Luna, Amirali Boroumand, Anant Nori, Allison Scibisz, Sreenivas Subramoney, Can Alkan, Saugata Ghose, and Onur Mutlu, "GenASM: A High-Performance, Low-Power Approximate String Matching Acceleration Framework for Genome Sequence Analysis"

Proceedings of the 53rd International Symposium on Microarchitecture (MICRO), Virtual, October 2020.

[<u>Lighting Talk Video</u> (1.5 minutes)] [<u>Lightning Talk Slides (pptx) (pdf)</u>] [<u>Talk Video</u> (18 minutes)] [<u>Slides (pptx) (pdf)</u>]

#### GenASM: A High-Performance, Low-Power Approximate String Matching Acceleration Framework for Genome Sequence Analysis

Damla Senol Cali<sup>†™</sup> Gurpreet S. Kalsi<sup>™</sup> Zülal Bingöl<sup>▽</sup> Can Firtina<sup>⋄</sup> Lavanya Subramanian<sup>‡</sup> Jeremie S. Kim<sup>⋄†</sup> Rachata Ausavarungnirun<sup>⊙</sup> Mohammed Alser<sup>⋄</sup> Juan Gomez-Luna<sup>⋄</sup> Amirali Boroumand<sup>†</sup> Anant Nori<sup>™</sup> Allison Scibisz<sup>†</sup> Sreenivas Subramoney<sup>™</sup> Can Alkan<sup>▽</sup> Saugata Ghose<sup>\*†</sup> Onur Mutlu<sup>⋄†▽</sup>

† Carnegie Mellon University <sup>™</sup> Processor Architecture Research Lab, Intel Labs <sup>▽</sup> Bilkent University <sup>⋄</sup> ETH Zürich

‡ Facebook <sup>⊙</sup> King Mongkut's University of Technology North Bangkok <sup>\*</sup> University of Illinois at Urbana–Champaign

110

## SW/HW Climate Modeling Accelerator

Gagandeep Singh, Dionysios Diamantopoulos, Christoph Hagleitner, Juan Gómez-Luna, Sander Stuijk, Onur Mutlu, and Henk Corporaal, "NERO: A Near High-Bandwidth Memory Stencil Accelerator for Weather Prediction Modeling"

Proceedings of the <u>30th International Conference on Field-Programmable Logic</u> <u>and Applications</u> (**FPL**), Gothenburg, Sweden, September 2020.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Talk Video (23 minutes)]

Nominated for the Stamatis Vassiliadis Memorial Award.

## NERO: A Near High-Bandwidth Memory Stencil Accelerator for Weather Prediction Modeling

Gagandeep Singh $^{a,b,c}$  Dionysios Diamantopoulos $^c$  Christoph Hagleitner $^c$  Juan Gómez-Luna $^b$  Sander Stuijk $^a$  Onur Mutlu $^b$  Henk Corporaal $^a$  Eindhoven University of Technology  $^b$ ETH Zürich  $^c$ IBM Research Europe, Zurich

### HW/SW Time Series Analysis Accelerator

Ivan Fernandez, Ricardo Quislant, Christina Giannoula, Mohammed Alser, Juan Gómez-Luna, Eladio Gutiérrez, Oscar Plata, and Onur Mutlu, "NATSA: A Near-Data Processing Accelerator for Time Series Analysis" Proceedings of the 38th IEEE International Conference on Computer Design (ICCD), Virtual, October 2020.

[Slides (pptx) (pdf)]

[Talk Video (10 minutes)]

Source Code

## NATSA: A Near-Data Processing Accelerator for Time Series Analysis

Ivan Fernandez $^\S$  Ricardo Quislant $^\S$  Christina Giannoula $^\dagger$  Mohammed Alser $^\ddagger$  Juan Gómez-Luna $^\ddagger$  Eladio Gutiérrez $^\S$  Oscar Plata $^\S$  Onur Mutlu $^\ddagger$   $^\S$ University of Malaga  $^\dagger$ National Technical University of Athens  $^\ddagger$ ETH Zürich

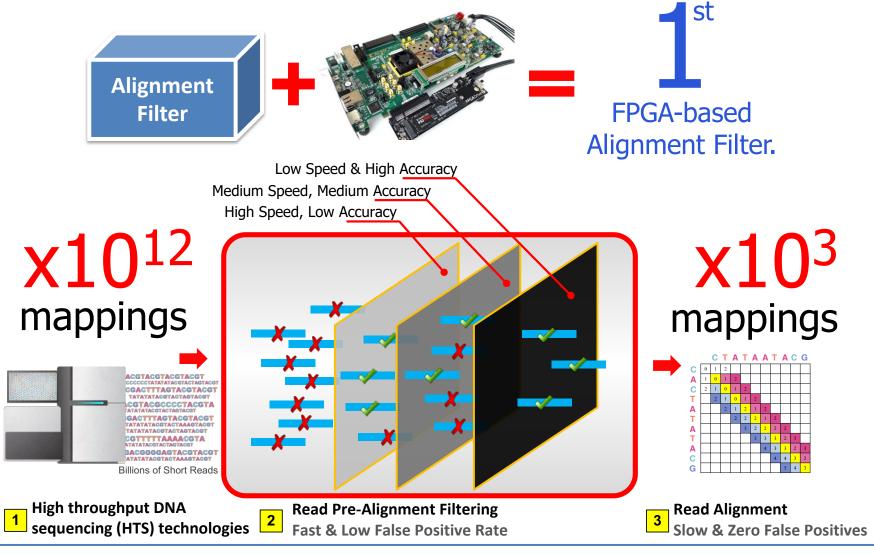

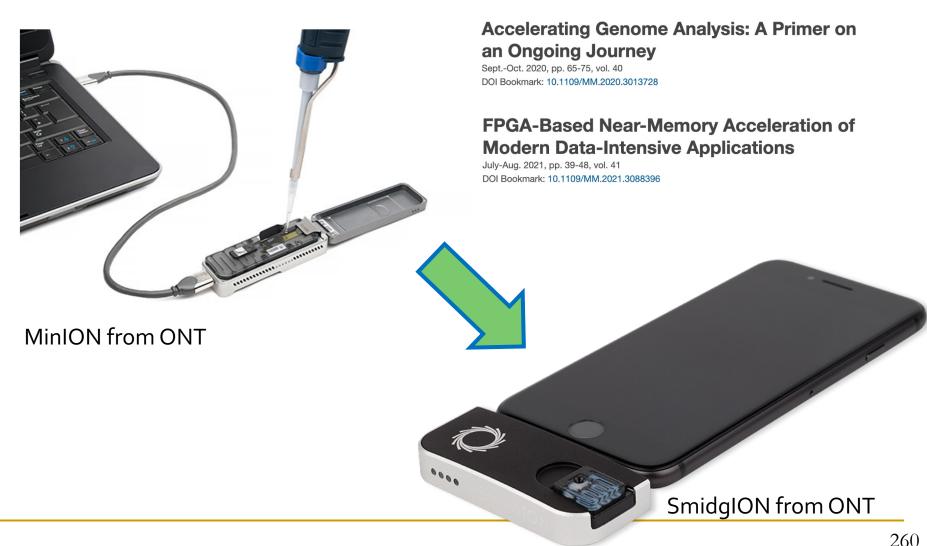

## FPGA-based Processing Near Memory

Gagandeep Singh, Mohammed Alser, Damla Senol Cali, Dionysios

Diamantopoulos, Juan Gómez-Luna, Henk Corporaal, and Onur Mutlu,

"FPGA-based Near-Memory Acceleration of Modern Data-Intensive

Applications"

IEEE Micro (IEEE MICRO), 2021.

## FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications

Gagandeep Singh<sup>⋄</sup> Mohammed Alser<sup>⋄</sup> Damla Senol Cali<sup>⋈</sup>

Dionysios Diamantopoulos<sup>▽</sup> Juan Gómez-Luna<sup>⋄</sup>

Henk Corporaal<sup>⋆</sup> Onur Mutlu<sup>⋄⋈</sup>

<sup>⋄</sup>ETH Zürich <sup>⋈</sup> Carnegie Mellon University \*Eindhoven University of Technology <sup>▽</sup>IBM Research Europe

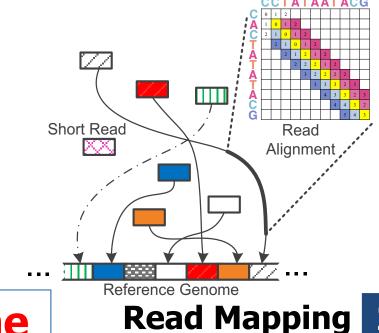

#### Accelerating Genome Analysis

Mohammed Alser, Zulal Bingol, Damla Senol Cali, Jeremie Kim, Saugata Ghose, Can Alkan, and Onur Mutlu,

"Accelerating Genome Analysis: A Primer on an Ongoing Journey"

IEEE Micro (IEEE MICRO), Vol. 40, No. 5, pages 65-75, September/October 2020.

[Slides (pptx)(pdf)]

[Talk Video (1 hour 2 minutes)]

## Accelerating Genome Analysis: A Primer on an Ongoing Journey

#### **Mohammed Alser**

ETH Zürich

#### Zülal Bingöl

Bilkent University

#### Damla Senol Cali

Carnegie Mellon University

#### Jeremie Kim

ETH Zurich and Carnegie Mellon University

#### Saugata Ghose

University of Illinois at Urbana–Champaign and Carnegie Mellon University

#### Can Alkan

Bilkent University

#### **Onur Mutlu**

ETH Zurich, Carnegie Mellon University, and Bilkent University

## Graph Processing Accelerator w/ PIM

Junwhan Ahn, Sungpack Hong, Sungjoo Yoo, Onur Mutlu, and Kiyoung Choi,

"A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing"

Proceedings of the <u>42nd International Symposium on</u> <u>Computer Architecture</u> (**ISCA**), Portland, OR, June 2015. [Slides (pdf)] [Lightning Session Slides (pdf)]

#### A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing

Junwhan Ahn Sungpack Hong<sup>§</sup> Sungjoo Yoo Onur Mutlu<sup>†</sup> Kiyoung Choi junwhan@snu.ac.kr, sungpack.hong@oracle.com, sungjoo.yoo@gmail.com, onur@cmu.edu, kchoi@snu.ac.kr Seoul National University <sup>§</sup>Oracle Labs <sup>†</sup>Carnegie Mellon University

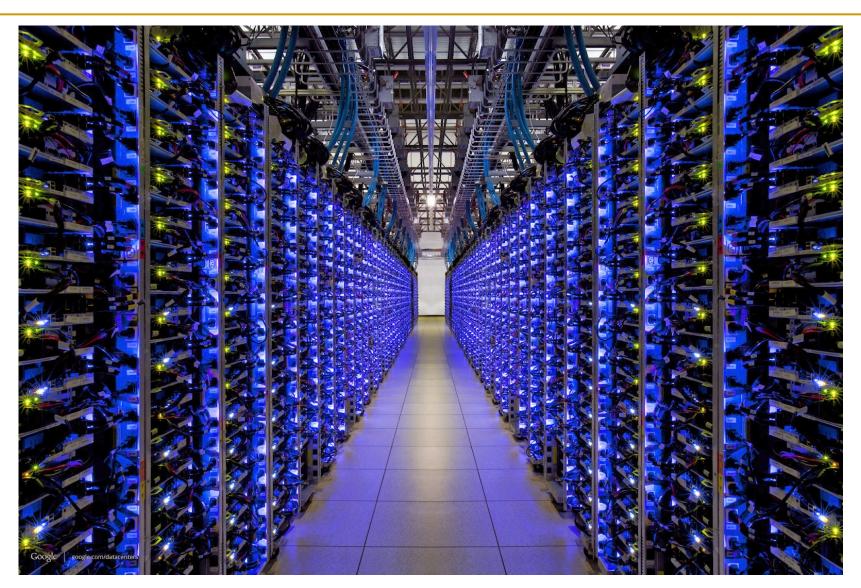

#### Processing in Memory for Mobile Workloads

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks"

Proceedings of the <u>23rd International Conference on Architectural</u> <u>Support for Programming Languages and Operating</u> <u>Systems</u> (**ASPLOS**), Williamsburg, VA, USA, March 2018.

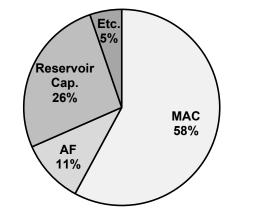

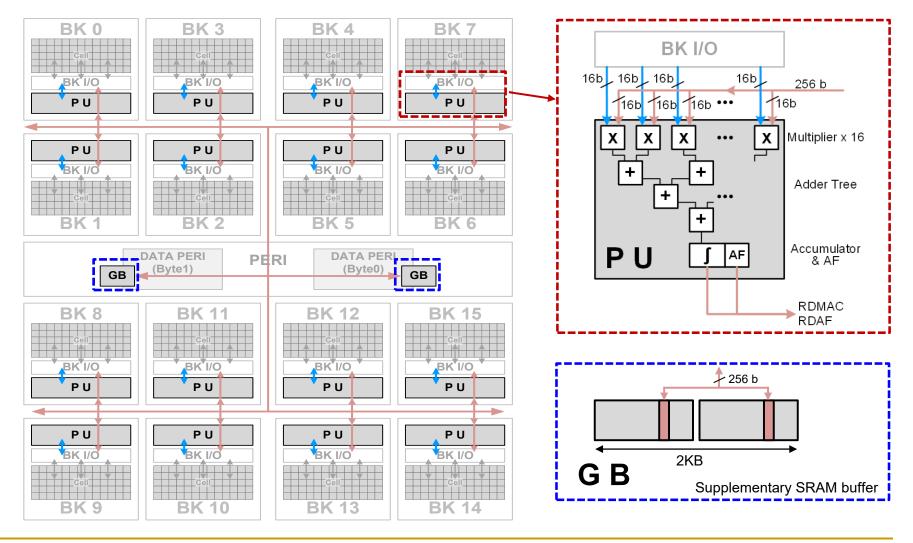

#### Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup> Saugata Ghose<sup>1</sup> Youngsok Kim<sup>2</sup> Rachata Ausavarungnirun<sup>1</sup> Eric Shiu<sup>3</sup> Rahul Thakur<sup>3</sup> Daehyun Kim<sup>4,3</sup> Aki Kuusela<sup>3</sup> Allan Knies<sup>3</sup> Parthasarathy Ranganathan<sup>3</sup> Onur Mutlu<sup>5,1</sup>

#### Accelerating Linked Data Structures

Kevin Hsieh, Samira Khan, Nandita Vijaykumar, Kevin K. Chang, Amirali Boroumand, Saugata Ghose, and Onur Mutlu, "Accelerating Pointer Chasing in 3D-Stacked Memory: Challenges, Mechanisms, Evaluation" Proceedings of the 34th IEEE International Conference on Computer Design (ICCD), Phoenix, AZ, USA, October 2016.

## Accelerating Pointer Chasing in 3D-Stacked Memory: Challenges, Mechanisms, Evaluation

Kevin Hsieh<sup>†</sup> Samira Khan<sup>‡</sup> Nandita Vijaykumar<sup>†</sup> Kevin K. Chang<sup>†</sup> Amirali Boroumand<sup>†</sup> Saugata Ghose<sup>†</sup> Onur Mutlu<sup>§†</sup> <sup>†</sup> Carnegie Mellon University <sup>‡</sup> University of Virginia <sup>§</sup> ETH Zürich

## Expressive (Memory) Interfaces

Nandita Vijaykumar, Abhilasha Jain, Diptesh Majumdar, Kevin Hsieh, Gennady Pekhimenko, Eiman Ebrahimi, Nastaran Hajinazar, Phillip B. Gibbons and Onur Mutlu, <u>"A Case for Richer Cross-layer Abstractions: Bridging the Semantic Gapwith Expressive Memory"</u>

Proceedings of the <u>45th International Symposium on Computer Architecture</u> (**ISCA**), Los Angeles, CA, USA, June 2018.

[Slides (pptx) (pdf)] [Lightning Talk Slides (pptx) (pdf)] [Lightning Talk Video]

#### A Case for Richer Cross-layer Abstractions: Bridging the Semantic Gap with Expressive Memory

Nandita Vijaykumar<sup>†§</sup> Abhilasha Jain<sup>†</sup> Diptesh Majumdar<sup>†</sup> Kevin Hsieh<sup>†</sup> Gennady Pekhimenko<sup>‡</sup> Eiman Ebrahimi<sup>ℵ</sup> Nastaran Hajinazar<sup>‡</sup> Phillip B. Gibbons<sup>†</sup> Onur Mutlu<sup>§†</sup>

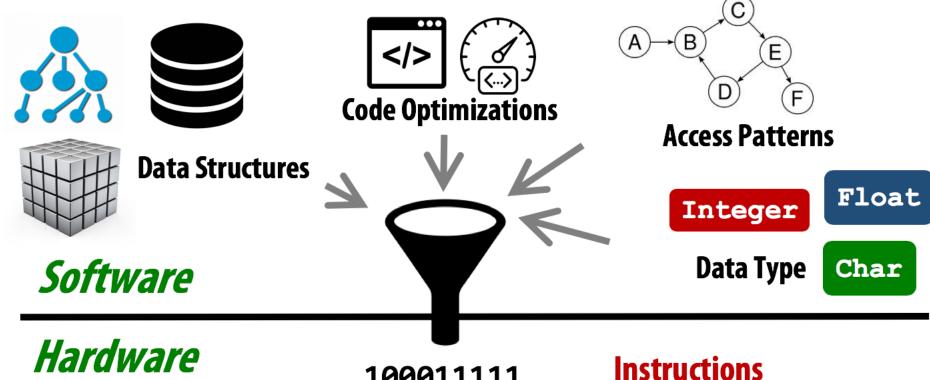

#### One Problem: Limited SW/HW Communication

#### Higher-level information is not visible to HW

100011111... Instructions 101010011... Memory Addresses

## A Solution: More Expressive Interfaces

**Performance**

**Software**

ISA Virtual Memory Higher-level Program Semantics

Expressive Memory "XMem"

**Hardware**

## X-MeM Aids Many Optimizations

| Memory optimization                                       | Example semantics provided by XMem (described in §3.3)                                                                           | Example Benefits of XMem                                                                                                                                                                                                                                                                                                                                                                  |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Cache<br>management                                       | (i) Distinguishing between data structures or pools of similar data; (ii) Working set size; (iii) Data reuse                     | Enables: (i) applying different caching policies to different data structures or pools of data; (ii) avoiding cache thrashing by <i>knowing</i> the active working set size; (iii) bypassing/prioritizing data that has no/high reuse. (§5)                                                                                                                                               |  |

| Page placement<br>in DRAM<br>e.g., [23, 24]               | (i) Distinguishing between data structures; (ii) Access pattern; (iii) Access intensity                                          | Enables page placement at the <i>data structure</i> granularity to (i) isolate data structures that hav high row buffer locality and (ii) spread out concurrently-accessed irregular data structure across banks and channels to improve parallelism. (§6)                                                                                                                                |  |

| Cache/memory<br>compression<br>e.g., [25–32]              | (i) Data type: integer, float, char;<br>(ii) Data properties: sparse, pointer,<br>data index                                     | Enables using a <i>different compression algorithm</i> for each data structure based on data type and data properties, e.g., sparse data encodings, FP-specific compression, delta-based compression for pointers [27].                                                                                                                                                                   |  |

| Data<br>prefetching<br>e.g., [33–36]                      | (i) Access pattern: strided, irregular, irregular but repeated (e.g., graphs), access stride; (ii) Data type: index, pointer     | Enables (i) highly accurate software-driven prefetching while leveraging the benefits of hardware prefetching (e.g., by being memory bandwidth-aware, avoiding cache thrashing); (ii) using different prefetcher types for different data structures: e.g., stride [33], tile-based [20], pattern-based [34–37], data-based for indices/pointers [38,39], etc.                            |  |

| DRAM cache<br>management<br>e.g., [40–46]                 | (i) Access intensity; (ii) Data reuse; (iii) Working set size                                                                    | (i) Helps avoid cache thrashing by knowing working set size [44]; (ii) Better DRAM cache management via reuse behavior and access intensity information.                                                                                                                                                                                                                                  |  |

| Approximation in memory e.g., [47–53]                     | (i) Distinguishing between pools of similar data; (ii) Data properties: tolerance towards approximation                          | Enables (i) each memory component to track how approximable data is (at a fine granularity to inform approximation techniques; (ii) data placement in heterogeneous reliability memories [54].                                                                                                                                                                                            |  |

| Data placement:<br>NUMA systems<br>e.g., [55, 56]         | (i) Data partitioning across threads (i.e., relating data to threads that access it); (ii) Read-Write properties                 | Reduces the need for profiling or data migration (i) to co-locate data with threads that access it and (ii) to identify Read-Only data, thereby enabling techniques such as replication.                                                                                                                                                                                                  |  |

| Data placement:<br>hybrid<br>memories<br>e.g., [16,57,58] | (i) Read-Write properties<br>(Read-Only/Read-Write); (ii) Access<br>intensity; (iii) Data structure size;<br>(iv) Access pattern | Avoids the need for profiling/migration of data in hybrid memories to (i) effectively manage the asymmetric read-write properties in NVM (e.g., placing Read-Only data in the NVM) [16, 57]; (ii) make tradeoffs between data structure "hotness" and size to allocate fast/high bandwidth memory [14]; and (iii) leverage row-buffer locality in placement based on access pattern [45]. |  |

| Managing<br>NUCA systems<br>e.g., [15, 59]                | (i) Distinguishing pools of similar data;<br>(ii) Access intensity; (iii) Read-Write or<br>Private-Shared properties             | (i) Enables using different cache policies for different data pools (similar to [15]); (ii) Reduces the need for reactive mechanisms that detect sharing and read-write characteristics to inform cache policies.                                                                                                                                                                         |  |

## Expressive (Memory) Interfaces for GPUs

Nandita Vijaykumar, Eiman Ebrahimi, Kevin Hsieh, Phillip B. Gibbons and Onur Mutlu,

"The Locality Descriptor: A Holistic Cross-Layer Abstraction to Express

Data Locality in GPUs"

Proceedings of the <u>45th International Symposium on Computer Architecture</u> (**ISCA**), Los Angeles, CA, USA, June 2018.

[Slides (pptx) (pdf)] [Lightning Talk Slides (pptx) (pdf)] [Lightning Talk Video]

#### The Locality Descriptor:

#### A Holistic Cross-Layer Abstraction to Express Data Locality in GPUs

```

Nandita Vijaykumar<sup>†§</sup> Eiman Ebrahimi<sup>‡</sup> Kevin Hsieh<sup>†</sup> Phillip B. Gibbons<sup>†</sup> Onur Mutlu<sup>§†</sup>

```

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>NVIDIA <sup>§</sup>ETH Zürich

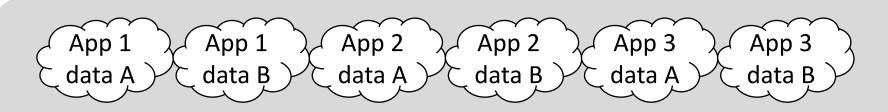

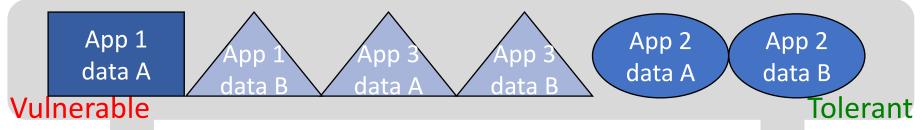

#### Heterogeneous-Reliability Memory

Yixin Luo, Sriram Govindan, Bikash Sharma, Mark Santaniello, Justin Meza, Aman Kansal, Jie Liu, Badriddine Khessib, Kushagra Vaid, and Onur Mutlu, "Characterizing Application Memory Error Vulnerability to Optimize Data Center Cost via Heterogeneous-Reliability Memory"

Proceedings of the 44th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Atlanta, GA, June 2014. [Summary]

[Slides (pptx) (pdf)] [Coverage on ZDNet]