# **Computer Architecture** Lecture 8b: Memory Latency

Prof. Onur Mutlu ETH Zürich Fall 2022 21 October 2022

# Four Key Current Directions

Fundamentally Secure/Reliable/Safe Architectures

Fundamentally Energy-Efficient Architectures

Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency and Predictable Architectures

Architectures for AI/ML, Genomics, Medicine, Health, ...

SAFARI Source: Jane Ades, NHGRI

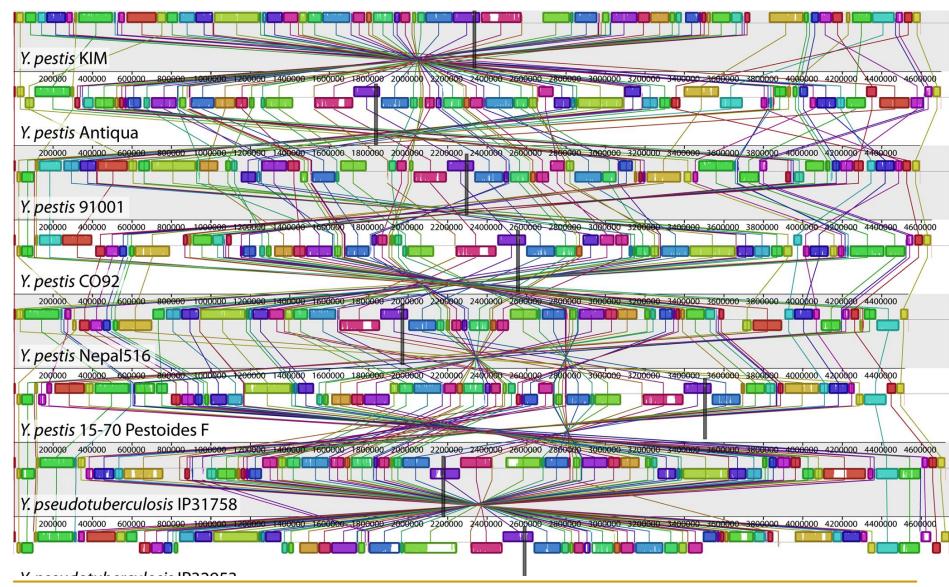

Source: By Aaron E. Darling, István Miklós, Mark A. Ragan - Figure 1 from Darling AE, Miklós I, Ragan MA (2008). "Dynamics of Genome Rearrangement in Bacterial Populations". PLOS Genetics. DOI:10.1371/journal.pgen.1000128., CC BY 2.5, https://commons.wikimedia.org/w/index.php?curid=30550950

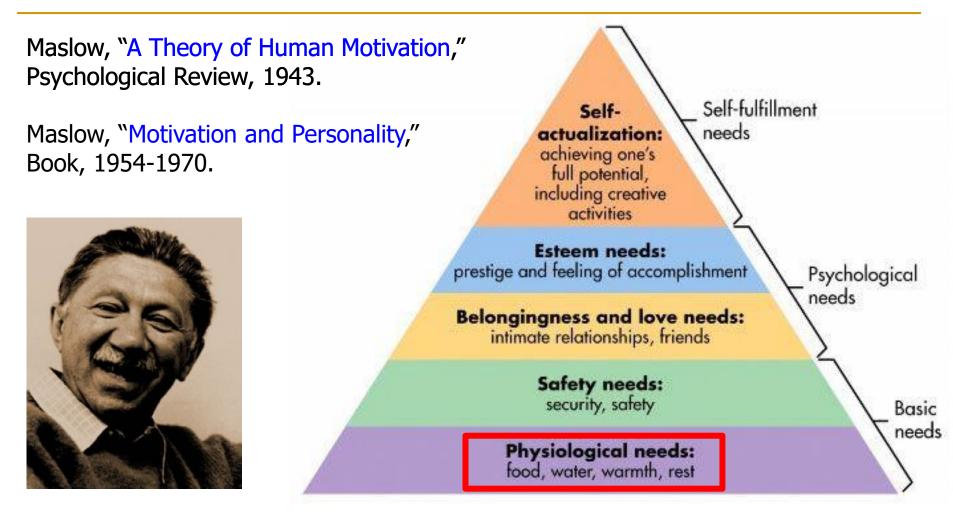

# Maslow's (Human) Hierarchy of Needs

### We need to start with energy...

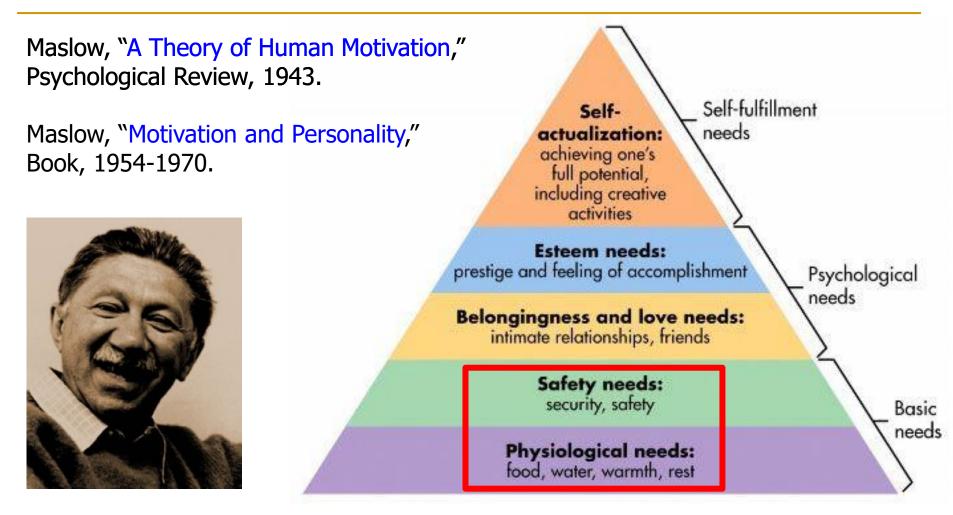

# Maslow's (Human) Hierarchy of Needs

### And then reliability and security...

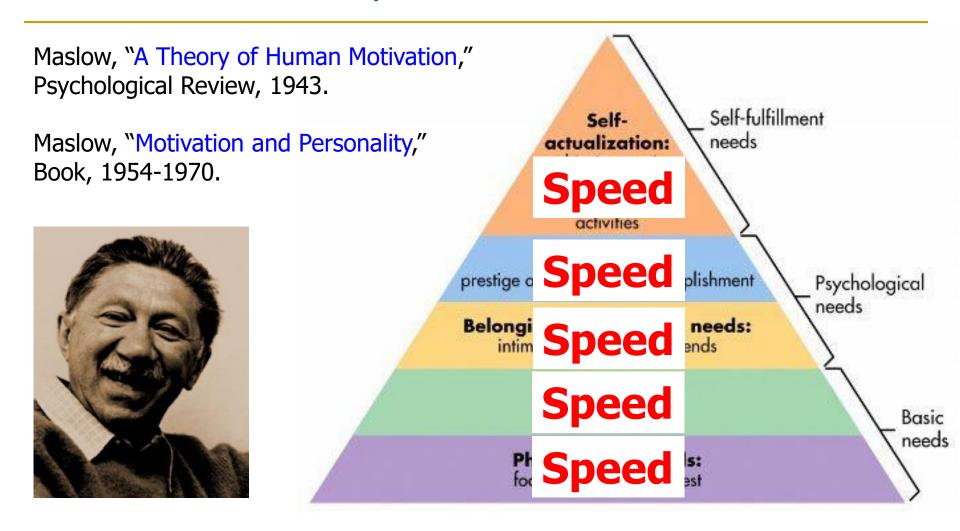

### Maslow's Hierarchy of Needs, Another Take

### SAFARI

Source: https://www.simplypsychology.org/maslow.html Source: By User:Factoryjoe - Mazlow's Hierarchy of Needs.svg, CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=7964065 Challenge and Opportunity for Future

# Fundamentally Low-Latency Computing Architectures

# More Motivation for Low Latency

- Watch Satya's (CMU) keynote talk at SYSTOR 2020

- https://youtu.be/u-KygYmbqDc?t=1723

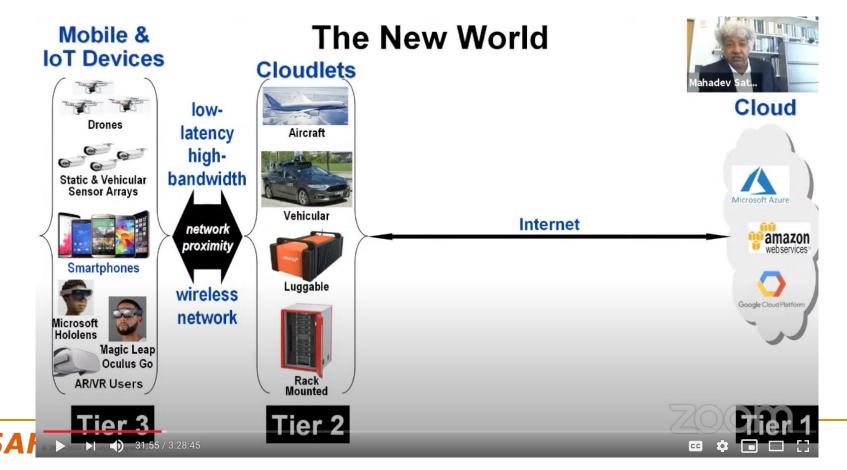

- Edge Computing: A New Disruptive Force

### More Motivation for Low Latency

- Watch Satya's (CMU) keynote talk at SYSTOR 2020

- https://youtu.be/u-KygYmbqDc?t=1723

- Edge Computing: A New Disruptive Force

### Value Proposition of Edge Computing

What is the edge doing for you?

1. Edge analytics in IoT

"Scalable real-time sensor analytics"

### 2. Highly responsive cloud-like services

"New applications and microservices"

- 3. Exposure firewall in the IoT "Crossing the IoT Chasm"

- 4. Mask disruption of cloud services "Disconnected operation for cloud services"

#### 5. Honor data export restrictions

"In country storage and processing" ▶Inty Dyna35:33 / 3:28:45 Bandwidth (peak and average)

Latency (mean and tail)

Privacy (control of sensor data)

Availability (UPS for cloud)

bring processing to the data

### More Motivation for Low Latency

- Watch Satya's (CMU) keynote talk at SYSTOR 2020

- <u>https://youtu.be/u-KygYmbqDc?t=1723</u>

- Edge Computing: A New Disruptive Force

### **Human Cognition is Amazing**

#### Fast, accurate and robust

▶ 44:49 / 3:28:45

face detection under hostile conditions < 700 ms (low lighting, distorted optics)

- face recognition 370 ms 620 ms

- is this sound from a human? 4 ms

- VR head tracking < 16 ms</li>

#### To be "superhuman" we need to beat these speeds

Leave time for additional software processing (e.g. database lookup) to add value to user

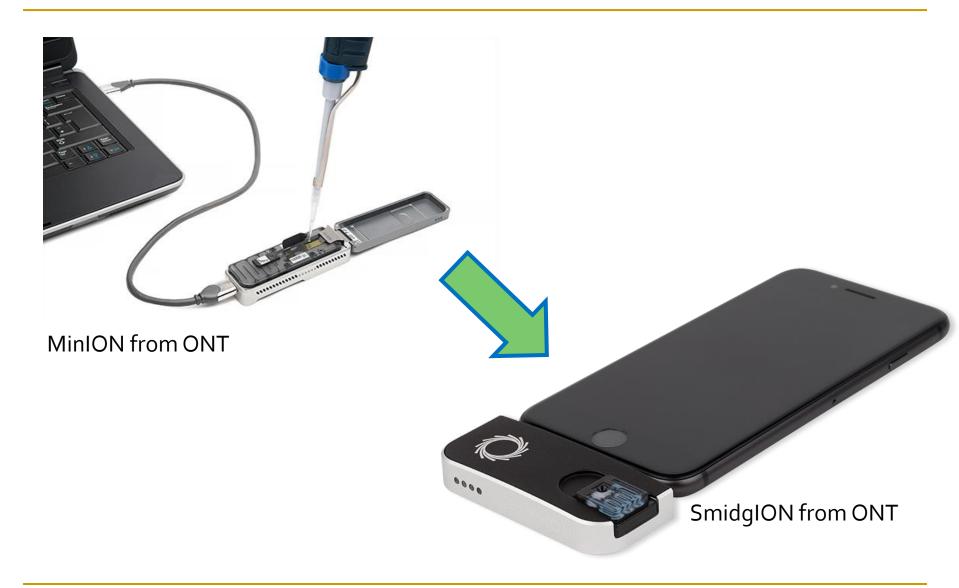

# Future of Genome Sequencing & Analysis

**SAFARI** Alser+, "Accelerating Genome Analysis: A Primer on an Ongoing Journey", IEEE Micro 2020.

# Recall Our Dream (from 2007)

- An embedded device that can perform comprehensive genome analysis in real time (within a minute)

- Still a long ways to go

- Energy efficiency

- Performance (latency)

- Security

Huge memory bottleneck

# Data-Centric (Memory-Centric) Architectures

# Data-Centric Architectures: Properties

### Process data where it resides (where it makes sense)

Processing in and near memory structures

### Low-latency & low-energy data access

- Low latency memory

- □ Low energy memory

### Low-cost data storage & processing

High capacity memory at low cost: hybrid memory, compression

### Intelligent data management

Intelligent controllers handling robustness, security, cost, scaling

# Low-Latency & Low-Energy Data Access

# Memory Latency: Fundamental Tradeoffs

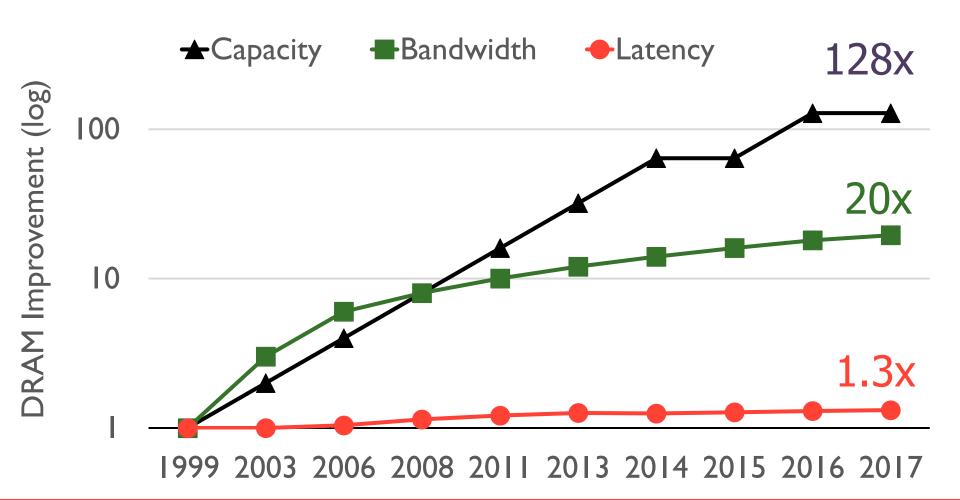

# Review: Memory Latency Lags Behind

Memory latency remains almost constant

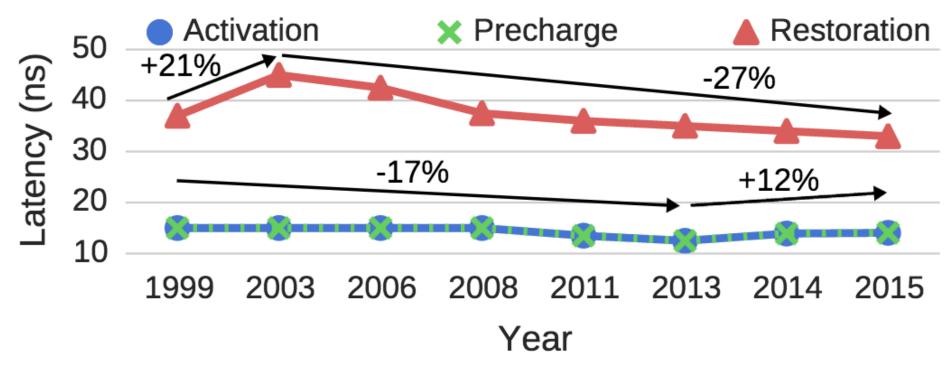

### A Closer Look ...

Figure 1: DRAM latency trends over time [20, 21, 23, 51].

Chang+, "<u>Understanding Latency Variation in Modern DRAM Chips: Experimental</u> Characterization, Analysis, and Optimization"," SIGMETRICS 2016.

# DRAM Latency Is Critical for Performance

### **In-memory Databases**

[Mao+, EuroSys'12; Clapp+ (**Intel**), IISWC'15]

### In-Memory Data Analytics

[Clapp+ (**Intel**), IISWC'15; Awan+, BDCloud'15]

**Graph/Tree Processing** [Xu+, IISWC'12; Umuroglu+, FPL'15]

**Datacenter Workloads** [Kanev+ (**Google**), ISCA'15]

# DRAM Latency Is Critical for Performance

### **In-memory Databases**

### **Graph/Tree Processing**

### Long memory latency → performance bottleneck

### In-Memory Data Analytics

[Clapp+ (**Intel**), IISWC'15; Awan+, BDCloud'15]

### **Datacenter Workloads**

[Kanev+ (Google), ISCA'I 5]

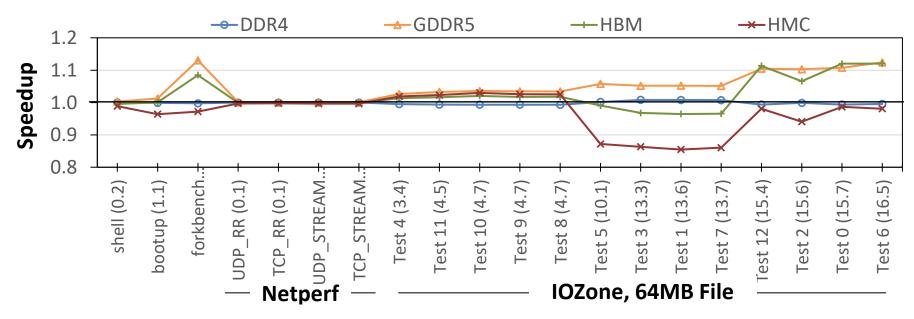

# New DRAM Types Increase Latency!

- Saugata Ghose, Tianshi Li, Nastaran Hajinazar, Damla Senol Cali, and Onur Mutlu, "Demystifying Workload–DRAM Interactions: An Experimental Study" Proceedings of the <u>ACM International Conference on Measurement and Modeling</u> of Computer Systems (SIGMETRICS), Phoenix, AZ, USA, June 2019. [Preliminary arXiv Version] [Abstract] [Slides (pptx) (pdf)] [MemBen Benchmark Suite] Source Code for GPGPUSim-Ramulator

- Source Code for Ramulator modeling Hybrid Memory Cube (HMC)

### **Demystifying Complex Workload–DRAM Interactions: An Experimental Study**

Saugata Ghose<sup>†</sup> Tianshi Li<sup>†</sup> Nastaran Hajinazar<sup>‡†</sup> Damla Senol Cali<sup>†</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>Simon Fraser University

<sup>§</sup>ETH Zürich

### Why Study Workload–DRAM Interactions?

- Manufacturers are developing many new types of DRAM

- DRAM limits performance, energy improvements: new types may overcome some limitations

- Memory systems now serve a very diverse set of applications: can no longer take a one-size-fits-all approach

### • So which DRAM type works best with which application?

- Difficult to understand intuitively due to the complexity of the interaction

- Can't be tested methodically on real systems: new type needs a new CPU

- We perform a wide-ranging experimental study to uncover the combined behavior of workloads and DRAM types

- 115 prevalent/emerging applications and multiprogrammed workloads

- 9 modern DRAM types: DDR3, DDR4, GDDR5, HBM, HMC, LPDDR3, LPDDR4, Wide I/O, Wide I/O 2

### Modern DRAM Types: Comparison to DDR3

| DRAM<br>Type                        | Banks<br>per<br>Rank        | Bank<br>Groups | 3D-<br>Stacked | Low-<br>Power                  | Bank groups     Bank Group     Bank Group     Bank Group     Bank Group |

|-------------------------------------|-----------------------------|----------------|----------------|--------------------------------|-------------------------------------------------------------------------|

| DDR3                                | 8                           |                |                |                                | Bank Bank Bank Bank                                                     |

| DDR4                                | 16                          | ✓              | increased      | latency                        | () ()                                                                   |

| GDDR5                               | 16                          | 🗸 🚺            | creased are    | ea/power                       | memory channel                                                          |

| HBM<br>High-<br>Bandwidth<br>Memory | 16                          |                | ✓              |                                | • 3D-stacked DRAM<br>high bandwidth with                                |

| HMC<br>Hybrid Memory<br>Cube        | 256 <b>higher latency</b> ✓ |                |                | Through-Silicon<br>Vias (TSVs) |                                                                         |

| Wide I/O                            | 4                           |                | $\checkmark$   | $\checkmark$                   |                                                                         |

| Wide I/O 2                          | 8                           |                | $\checkmark$   | $\checkmark$                   |                                                                         |

| LPDDR3                              | 8                           |                |                | $\checkmark$                   | dedicated Logic Layer                                                   |

| LPDDR4                              | 16                          |                |                | $\checkmark$                   |                                                                         |

### 4. Need for Lower Access Latency: Performance SAFARI

- New DRAM types often increase access latency in order to provide more banks, higher throughput

- Many applications can't make up for the increased latency

- Especially true of common OS routines (e.g., file I/O, process forking)

• A variety of desktop/scientific, server/cloud, GPGPU applications

Several applications don't benefit from more parallelism

- 1. DRAM latency remains a critical bottleneck for many applications

- 2. Bank parallelism is not fully utilized by a wide variety of our applications

- 3. Spatial locality continues to provide significant performance benefits if it is exploited by the memory subsystem

- 4. For some classes of applications, low-power memory can provide energy savings without sacrificing significant performance

### Conclusion

- Manufacturers are developing many new types of DRAM

- DRAM limits performance, energy improvements: new types may overcome some limitations

- Memory systems now serve a very diverse set of applications: can no longer take a one-size-fits-all approach

- Difficult to intuitively determine which DRAM–workload pair works best

- We perform a wide-ranging experimental study to uncover the combined behavior of workloads, DRAM types

- 115 prevalent/emerging applications and multiprogrammed workloads

- 9 modern DRAM types

- 12 key observations on DRAM–workload behavior

Open-source tools: <u>https://github.com/CMU-SAFARI/ramulator</u> Full paper: <u>https://arxiv.org/pdf/1902.07609</u>

# New DRAM Types Increase Latency!

- Saugata Ghose, Tianshi Li, Nastaran Hajinazar, Damla Senol Cali, and Onur Mutlu, "Demystifying Workload–DRAM Interactions: An Experimental Study" Proceedings of the <u>ACM International Conference on Measurement and Modeling</u> of Computer Systems (SIGMETRICS), Phoenix, AZ, USA, June 2019. [Preliminary arXiv Version] [Abstract] [Slides (pptx) (pdf)] [MemBen Benchmark Suite] Source Code for GPGPUSim-Ramulator

- Source Code for Ramulator modeling Hybrid Memory Cube (HMC)

### **Demystifying Complex Workload–DRAM Interactions: An Experimental Study**

Saugata Ghose<sup>†</sup> Tianshi Li<sup>†</sup> Nastaran Hajinazar<sup>‡†</sup> Damla Senol Cali<sup>†</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>Simon Fraser University

<sup>§</sup>ETH Zürich

# The Memory Latency Problem

- High memory latency is a significant limiter of system performance and energy-efficiency

- It is becoming increasingly so with higher memory contention in multi-core and heterogeneous architectures

- Exacerbating the bandwidth need

- Exacerbating the QoS problem

- It increases processor design complexity due to the mechanisms incorporated to tolerate memory latency

### Retrospective: Conventional Latency Tolerance Techniques

- Caching [initially by Wilkes, 1965]

- Widely used, simple, effective, but inefficient, passive

- Not all applications/phases exhibit temporal or spatial locality

- Prefetching [initially in IBM 360/91, 1967]

- Works well for regular memory access patterns

- Prefetching irregular access patterns is difficult, inaccurate, and hardwareintensive

- Multithreading [initially in CDC 6600, 1964]

- Works well if there are multiple threads

- Improving single thread performance using multithreading hardware is an ongoing research effort

- Out-of-order execution [initially by Tomasulo, 1967]

- Tolerates cache misses that cannot be prefetched

- Requires extensive hardware resources for tolerating long latencies

Retrospective: Conventional Latency Tolerance Techniques

- Caching [initially by Wilkes, 1965]

- Widely used, simple, effective, but inefficient, passive

- Not all applications/phases exhibit temporal or spatial locality

Prefetching [initially in IBM 360/91 1967]

# None of These Fundamentally Reduce Memory Latency

ongoing research effort

- Out-of-order execution [initially by Tomasulo, 1967]

- Tolerates cache misses that cannot be prefetched

- Requires extensive hardware resources for tolerating long latencies

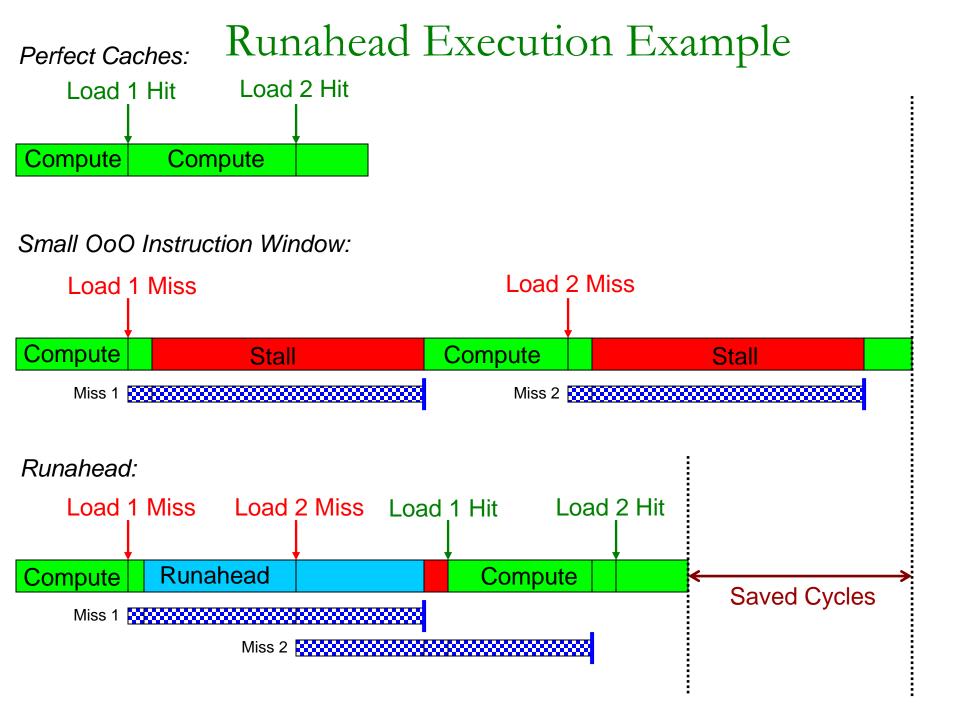

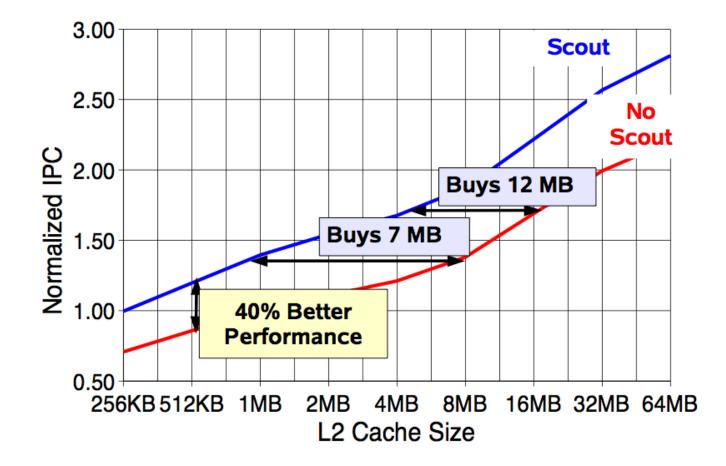

# Runahead Execution

#### Effect of Runahead in Sun ROCK

Shailender Chaudhry talk, Aug 2008.

#### More on Runahead Execution

Onur Mutlu, Jared Stark, Chris Wilkerson, and Yale N. Patt, <u>"Runahead Execution: An Alternative to Very Large Instruction</u> <u>Windows for Out-of-order Processors"</u> *Proceedings of the <u>9th International Symposium on High-Performance</u> <u>Computer Architecture</u> (HPCA), Anaheim, CA, February 2003. <u>Slides (pdf)</u> <u>One of the 15 computer architecture papers of 2003 selected as Top</u> <u>Picks by IEEE Micro.</u>*

#### **Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors**

Onur Mutlu § Jared Stark † Chris Wilkerson ‡ Yale N. Patt §

§ECE Department The University of Texas at Austin {onur,patt}@ece.utexas.edu †Microprocessor Research Intel Labs jared.w.stark@intel.com

Desktop Platforms Group Intel Corporation chris.wilkerson@intel.com

#### More on Runahead Execution (Short)

Onur Mutlu, Jared Stark, Chris Wilkerson, and Yale N. Patt, "Runahead Execution: An Effective Alternative to Large Instruction Windows"

*IEEE Micro, Special Issue: Micro's Top Picks from Microarchitecture Conferences* (*MICRO TOP PICKS*), Vol. 23, No. 6, pages 20-25, November/December 2003.

# RUNAHEAD EXECUTION: AN EFFECTIVE ALTERNATIVE TO LARGE INSTRUCTION WINDOWS

#### Runahead Readings

- Required

- Mutlu et al., "Runahead Execution", HPCA 2003, Top Picks 2003.

#### Recommended

- Mutlu et al., "Efficient Runahead Execution: Power-Efficient Memory Latency Tolerance," ISCA 2005, IEEE Micro Top Picks 2006.

- Mutlu et al., "Address-Value Delta (AVD) Prediction," MICRO 2005.

- Armstrong et al., "Wrong Path Events," MICRO 2004.

#### More on Runahead Execution (I)

**Onur Mutlu Lectures**

16.5K subscribers

EDIT VIDEO

ANALYTICS

#### More on Runahead Execution (II)

#### Runahead Execution in NVIDIA Denver

Reducing the effects of long cache-miss penalties has been a major focus of the microarchitecture, using techniques like prefetching and run-ahead. An aggressive hardware prefetcher implementation detects L2 cache requests and tracks up to 32 streams, each with complex stride patterns.

Run-ahead uses the idle time that a CPU spends waiting on a long latency operation to discover cache and DTLB misses further down the instruction stream and generates prefetch requests for these misses.<sup>1</sup> These prefetch requests warm up the data cache and DTLB well before the actual execution of the instructions that require the data. Runahead complements the hardware prefetcher because it's better at prefetching nonstrided streams, and it trains the hardware prefetcher faster than normal execution to yield a combined benefit of 13 percent on SPECint2000 and up to 60 percent on SPECfp2000.

Boggs+, "Denver: NVIDIA's First 64-Bit ARM Processor,"

Gwennap, "NVIDIA's First CPU is a Winner," MPR 2014.

The core includes a hardware prefetch unit that Boggs describes as "aggressive" in preloading the data cache but less aggressive in preloading the instruction cache. It also implements a "run-ahead" feature that continues to execute microcode speculatively after a data-cache miss; this execution can trigger additional cache misses that resolve in the shadow of the first miss. Once the data from the original miss returns, the results of this speculative execution are discarded and execution restarts with the bundle containing the original miss, but run-ahead can preload subsequent data into the cache, thus avoiding a string of time-wasting cache misses. These and other features help Denver outscore Cortex-A15 by more than 2.6x on a memory-read test even when both use the same SoC framework (Tegra K1).

50

▶ 💦 6:18 / 14:27

IEEE Micro 2015.

Onur Mutlu Lectures 16.5K subscribers

#### https://www.youtube.com/watch?v=KFCOecRQTIc

📼 🦑 🔳 🖂 🚼

EDIT VIDEO

→ SHARE =+ SAVE

ANALYTICS

Retrospective: Conventional Latency Tolerance Techniques

- Caching [initially by Wilkes, 1965]

- Widely used, simple, effective, but inefficient, passive

- Not all applications/phases exhibit temporal or spatial locality

Prefetching [initially in IBM 360/91 1967]

#### None of These Fundamentally Reduce Memory Latency

ongoing research effort

- Out-of-order execution [initially by Tomasulo, 1967]

- Tolerates cache misses that cannot be prefetched

- Requires extensive hardware resources for tolerating long latencies

#### Two Major Sources of Latency Inefficiency

- Modern DRAM is not designed for low latency

Main focus is cost-per-bit (capacity)

- Modern DRAM latency is determined by worst case conditions and worst case devices

- Much of memory latency is unnecessary

#### Our Goal: Reduce Memory Latency at the Source of the Problem

# Truly Reducing Memory Latency

What Causes the Long Memory Latency?

#### Why the Long Memory Latency?

- Reason 1: Design of DRAM Micro-architecture

Goal: Maximize capacity/area, not minimize latency

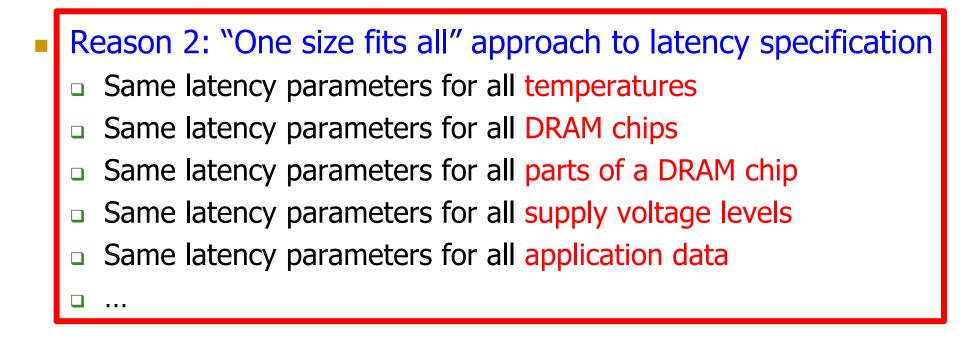

- Reason 2: "One size fits all" approach to latency specification

- Same latency parameters for all temperatures

- Same latency parameters for all DRAM chips

- Same latency parameters for all parts of a DRAM chip

- Same latency parameters for all supply voltage levels

- Same latency parameters for all application data

•••

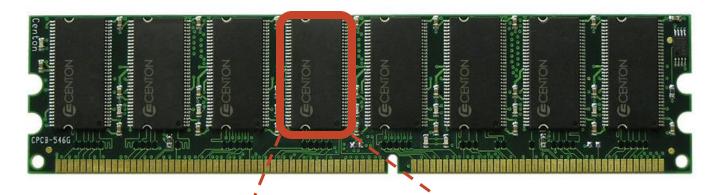

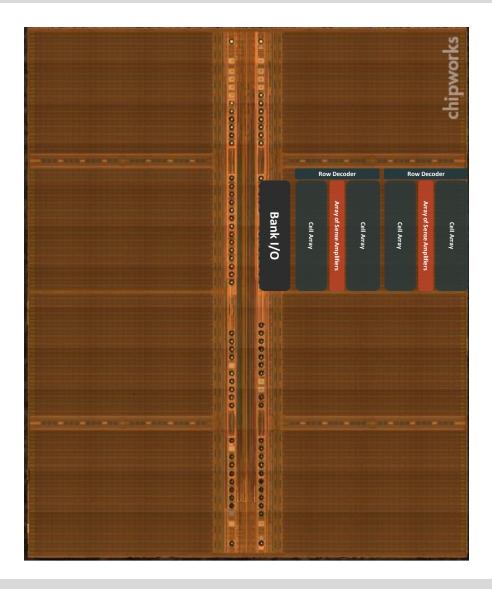

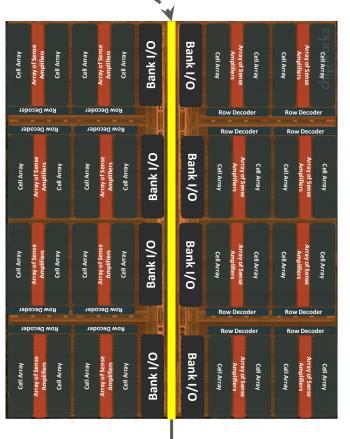

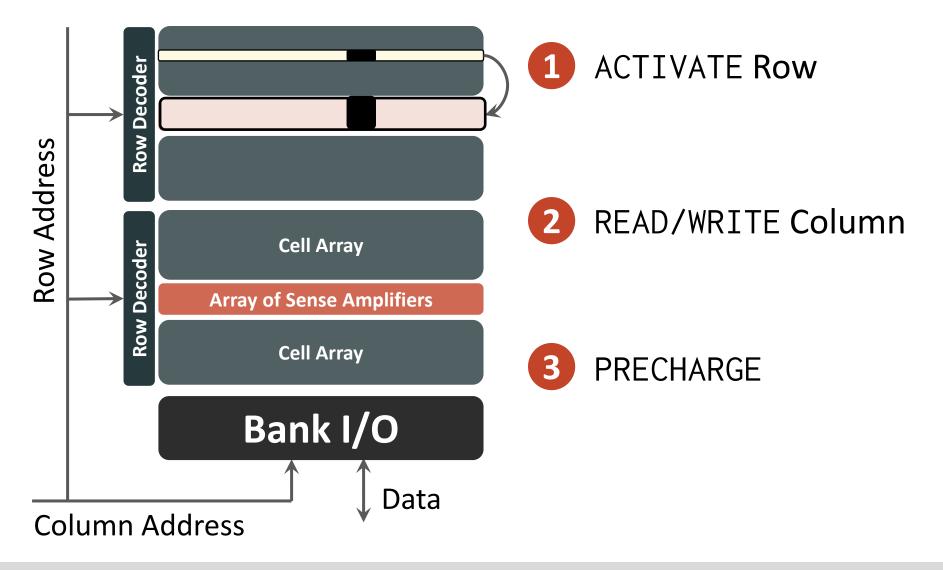

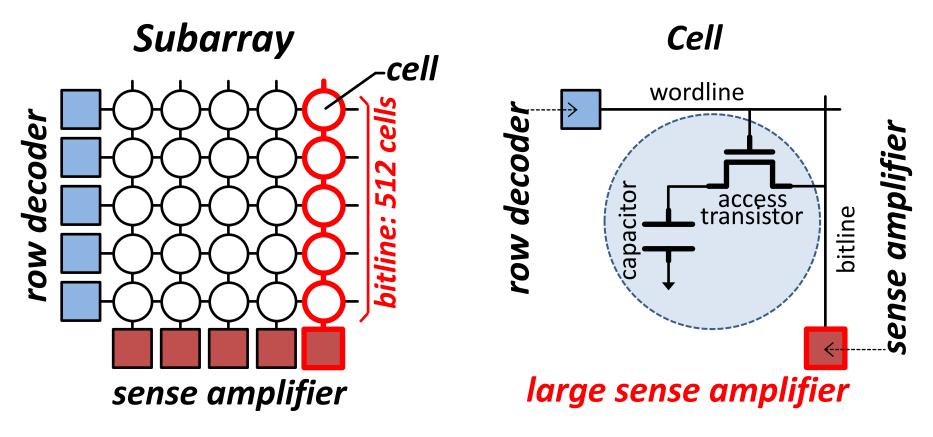

# Brief Review: Inside A DRAM Chip

#### **DRAM Module and Chip**

## Goals

- Cost

- Latency

- Bandwidth

- Parallelism

- Power

- Energy

- Reliability

## **DRAM Chip**

#### **Sense Amplifier**

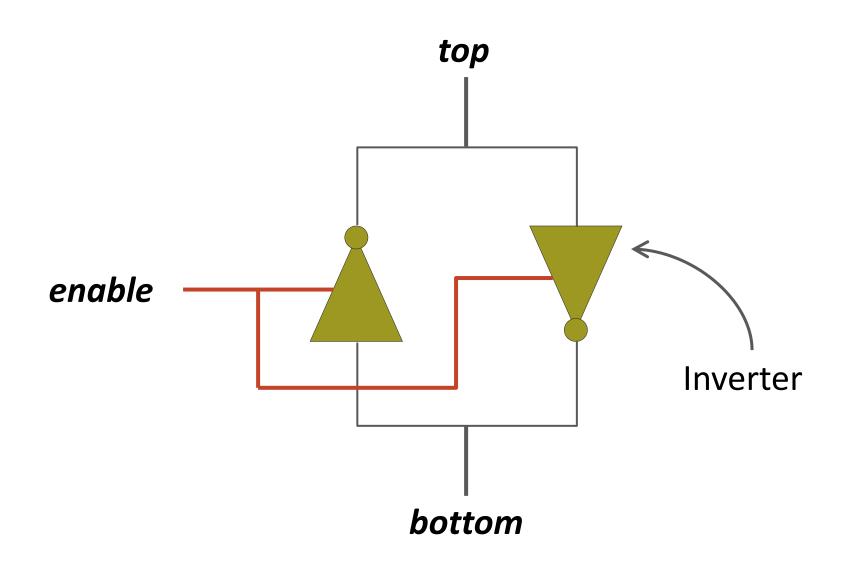

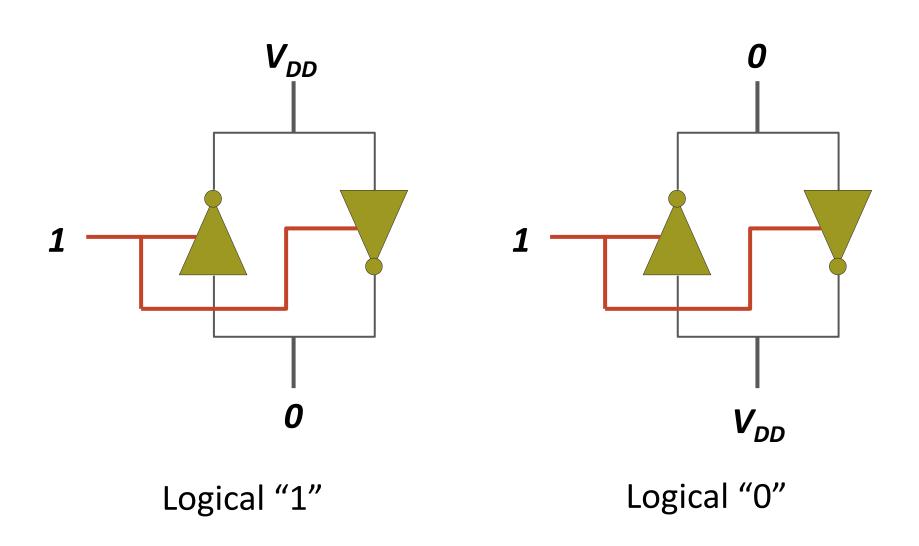

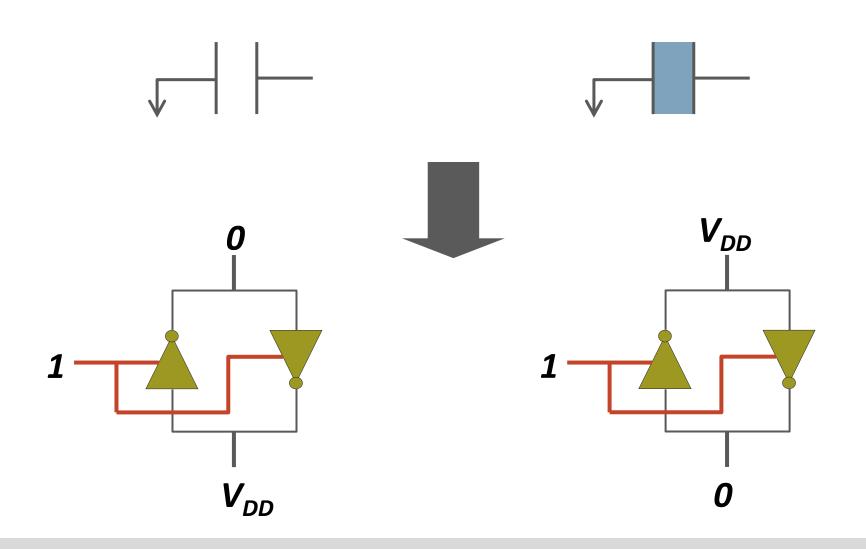

#### Sense Amplifier – Two Stable States

#### **Sense Amplifier Operation**

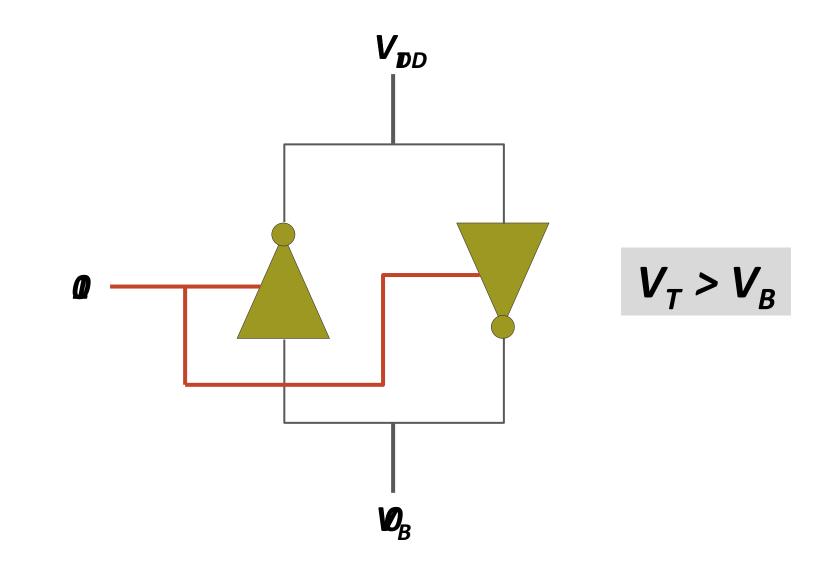

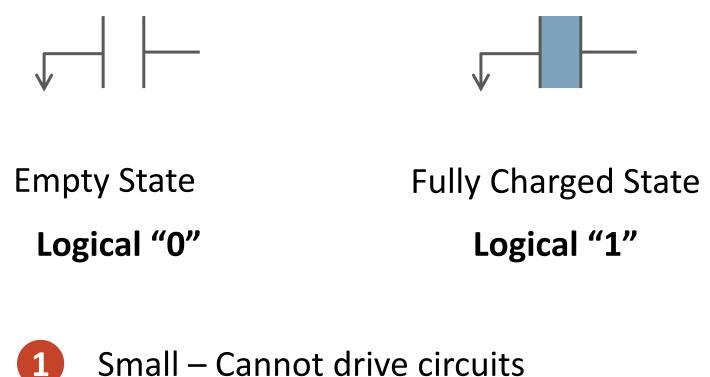

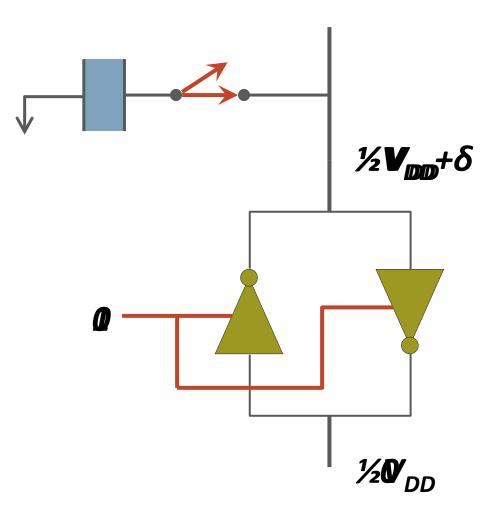

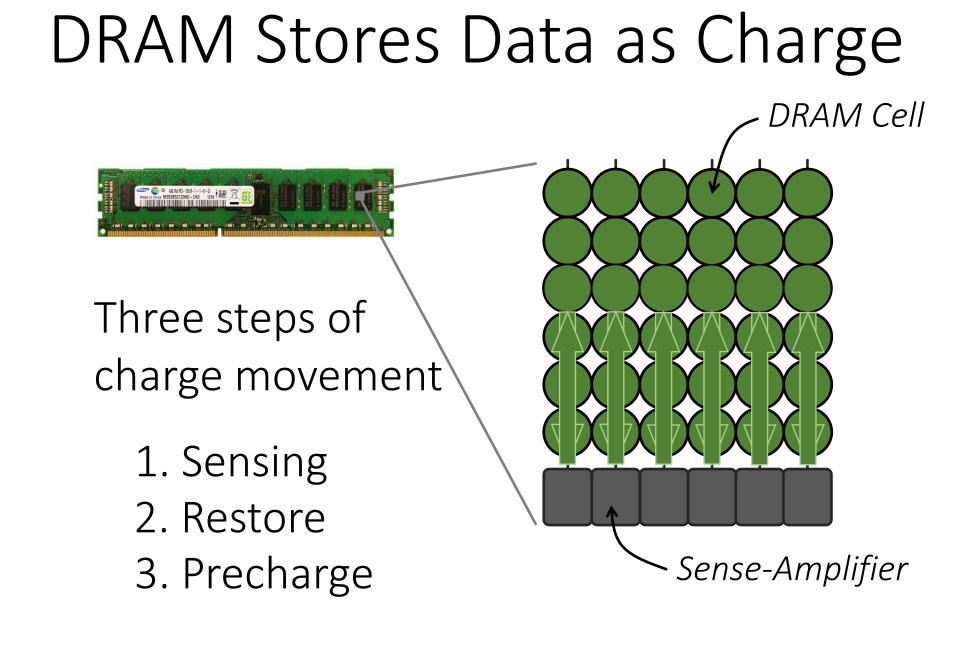

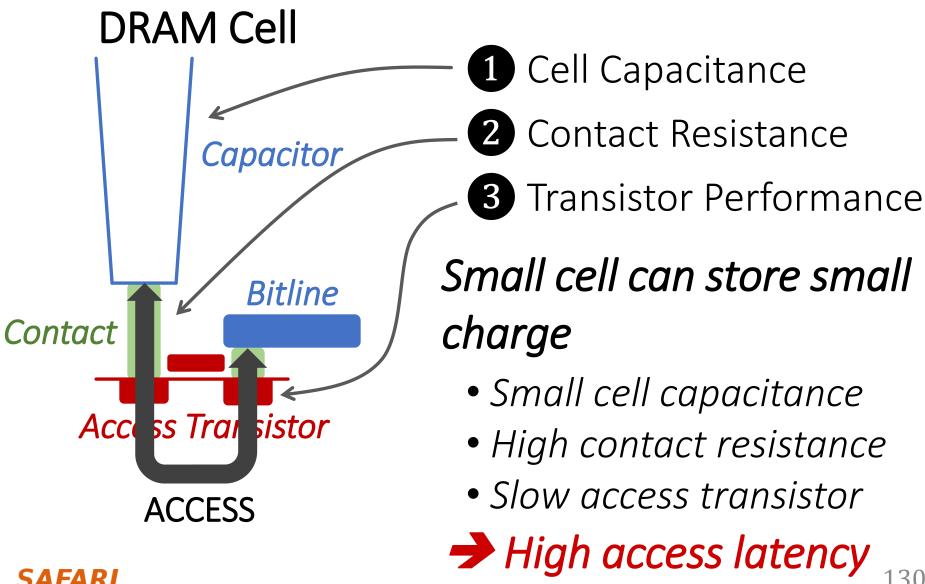

#### **DRAM Cell – Capacitor**

Small – Cannot drive circuits

Reading destroys the state

#### **Capacitor to Sense Amplifier**

#### **DRAM Cell Operation**

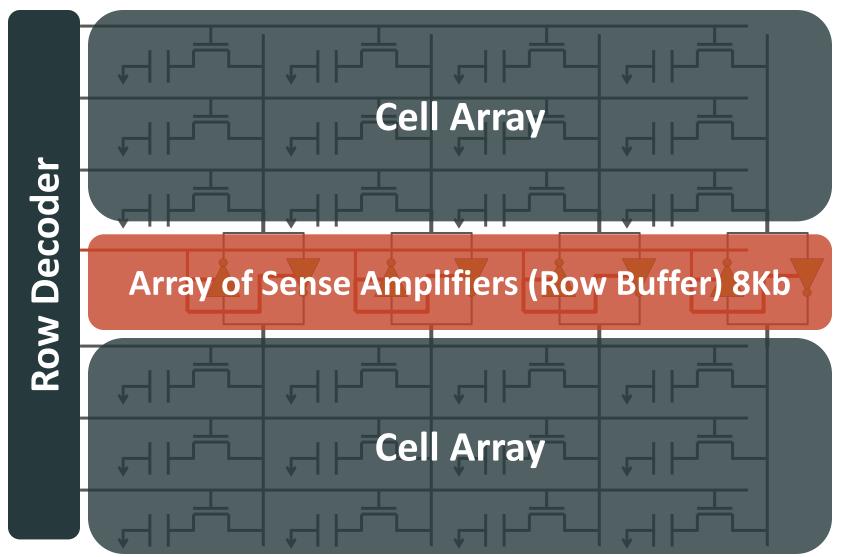

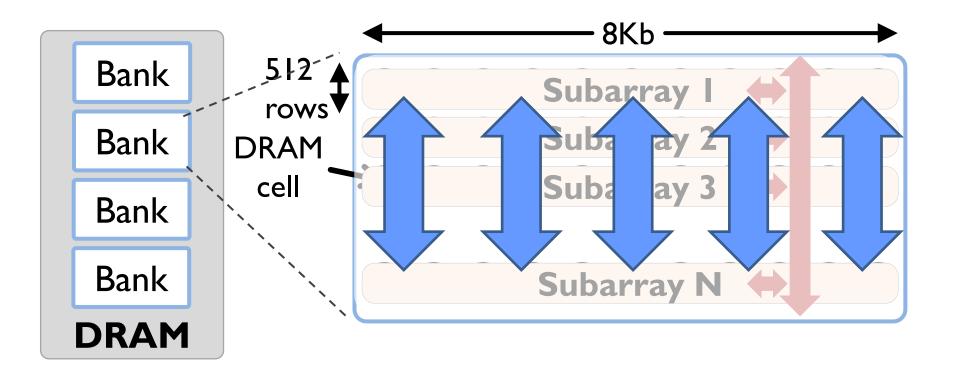

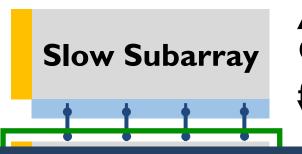

#### DRAM Subarray – Building Block for DRAM Chip

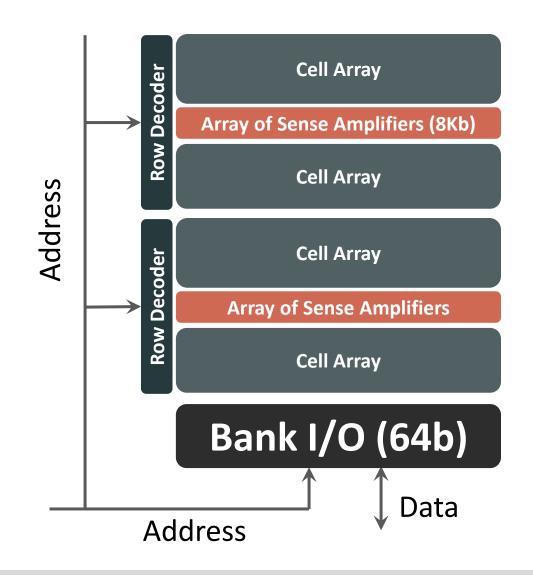

## **DRAM Bank**

## **DRAM Chip**

#### Shared internal bus

Memory channel - 8bits ←

### **DRAM Operation**

#### More on DRAM Operation: Section 2

Vivek Seshadri and Onur Mutlu,

"In-DRAM Bulk Bitwise Execution Engine" Invited Book Chapter in Advances in Computers, to appear in 2020.

[Preliminary arXiv version]

#### In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu ETH Zürich onur.mutlu@inf.ethz.ch

#### Why the Long Memory Latency?

- Reason 1: Design of DRAM Micro-architecture

Goal: Maximize capacity/area, not minimize latency

- Reason 2: "One size fits all" approach to latency specification

- Same latency parameters for all temperatures

- Same latency parameters for all DRAM chips

- Same latency parameters for all parts of a DRAM chip

- Same latency parameters for all supply voltage levels

- Same latency parameters for all application data

•••

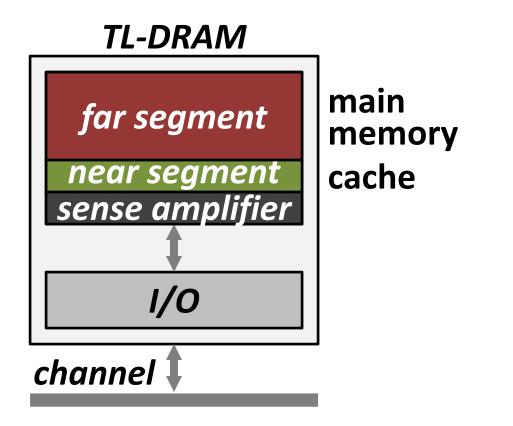

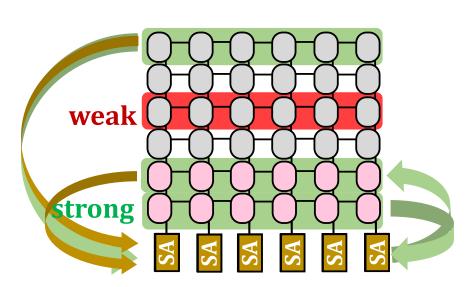

# Tiered Latency DRAM

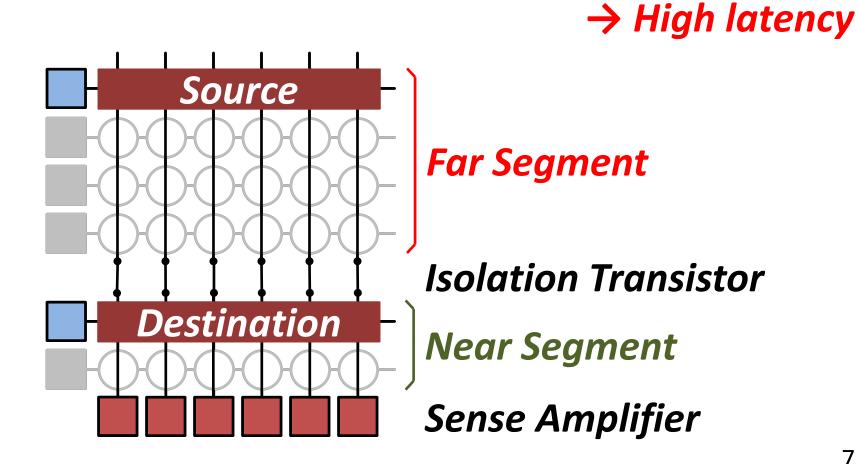

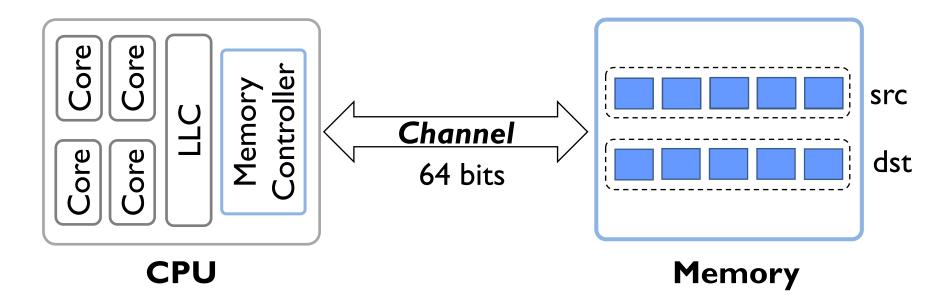

## What Causes the Long Latency? **DRAM** Chip subarray Subarray 0/ 1/0 channel **1** DRAM Latency - (Subarray Latency + II/O Latency Dominant

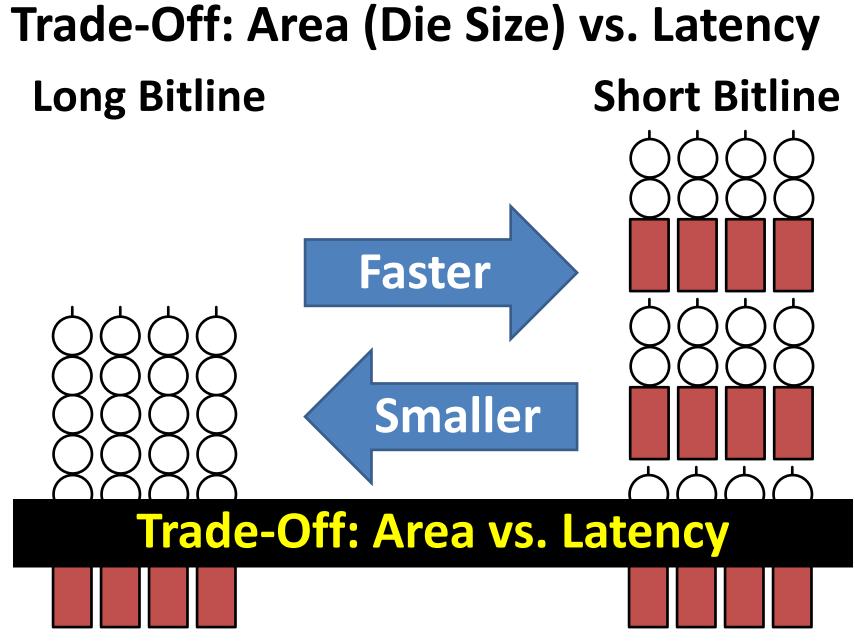

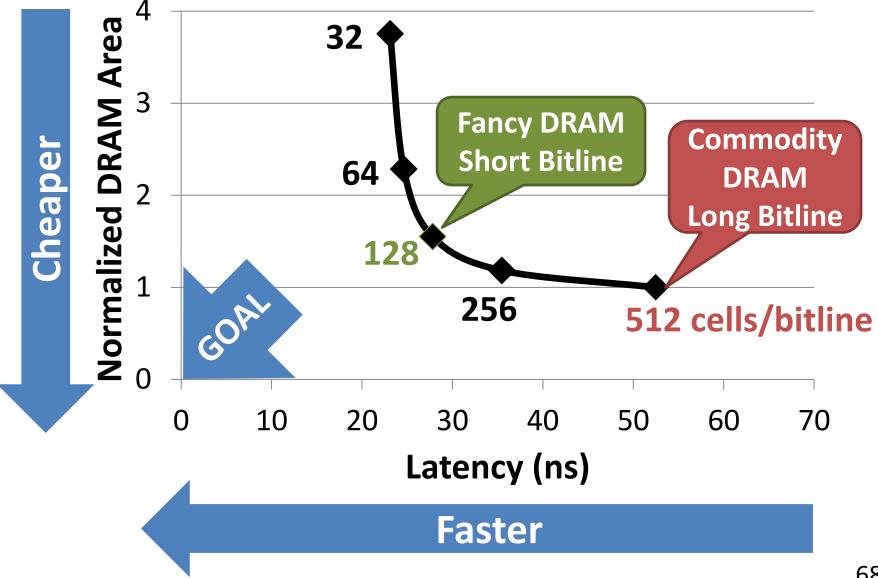

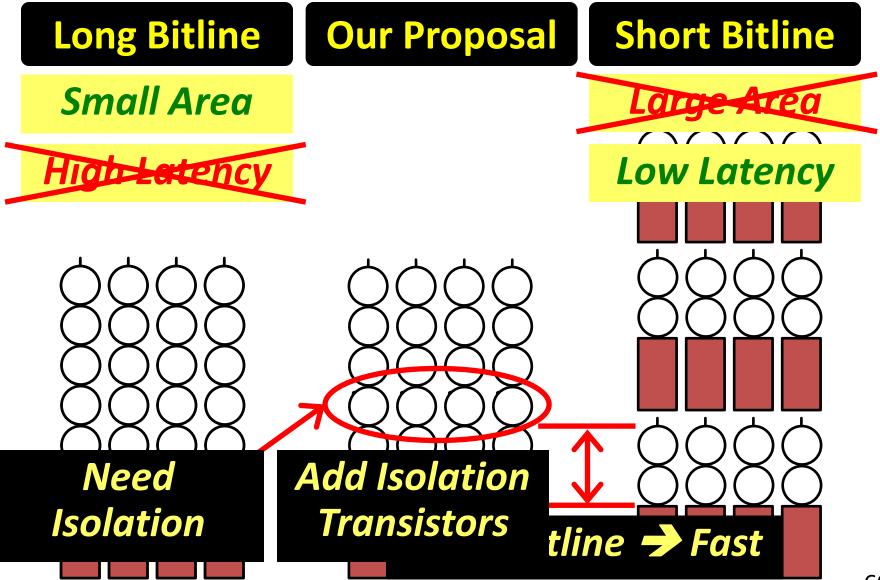

#### Why is the Subarray So Slow?

- Long bitline

- Amortizes sense amplifier cost  $\rightarrow$  Small area

- Large bitline capacitance → High latency & power

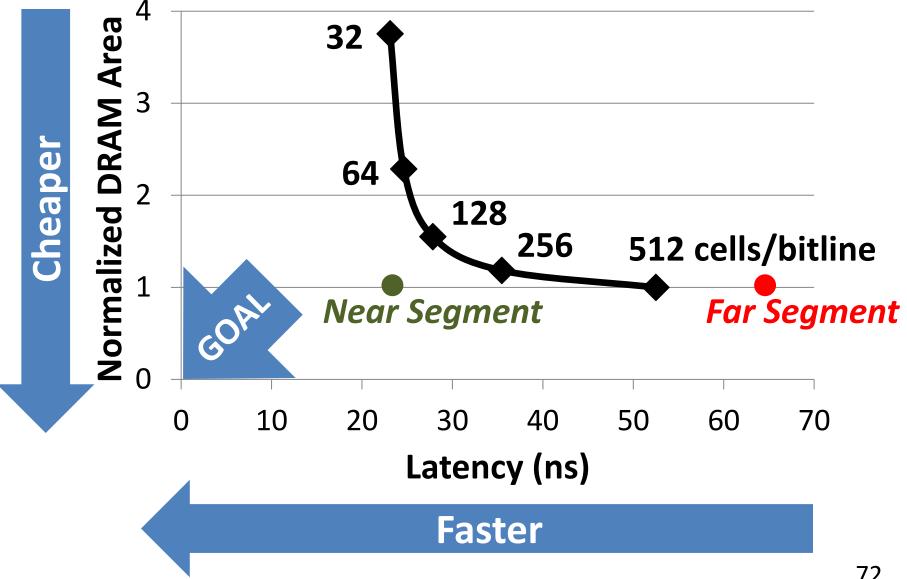

#### Trade-Off: Area (Die Size) vs. Latency

#### **Approximating the Best of Both Worlds**

#### **Approximating the Best of Both Worlds**

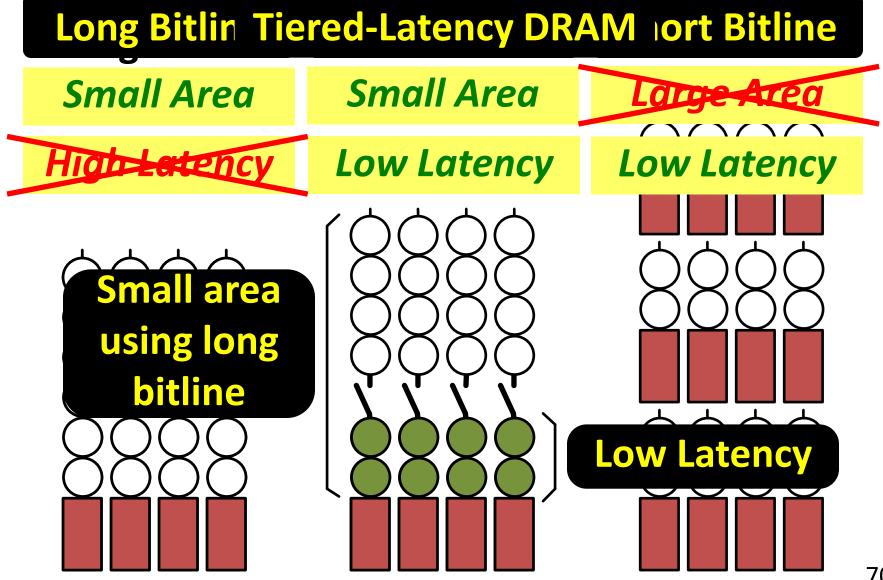

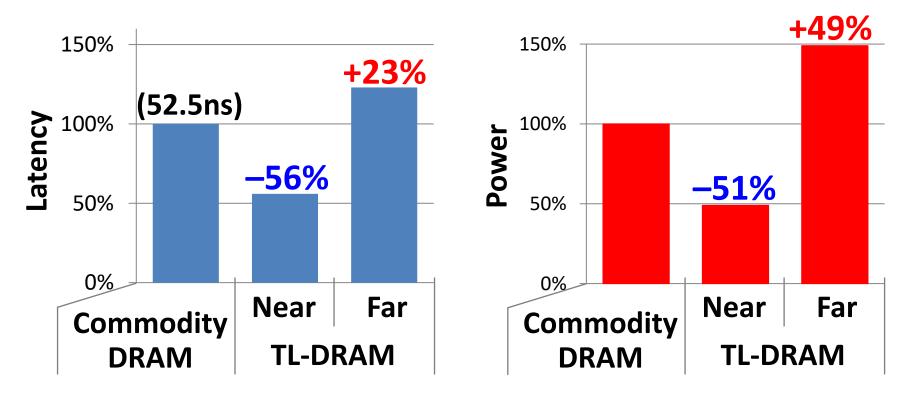

#### Commodity DRAM vs. TL-DRAM [HPCA 2013]

• DRAM Latency (tRC) • DRAM Power

#### DRAM Area Overhead

**~3%**: mainly due to the isolation transistors

#### Trade-Off: Area (Die-Area) vs. Latency

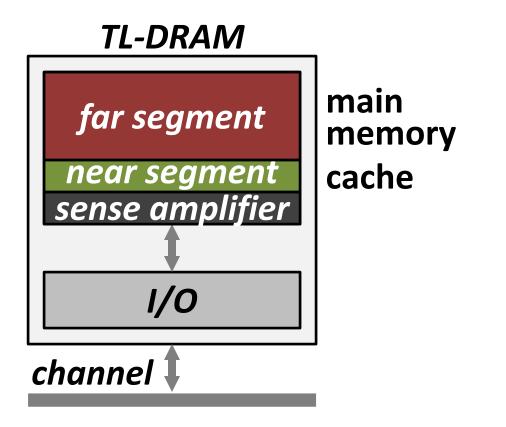

## Leveraging Tiered-Latency DRAM

- TL-DRAM is a *substrate* that can be leveraged by the hardware and/or software

- Many potential uses

Use near segment as hardware-managed *inclusive* cache to far segment

- 2. Use near segment as hardware-managed *exclusive* cache to far segment

- 3. Profile-based page mapping by operating system

- 4. Simply replace DRAM with TL-DRAM

### **Near Segment as Hardware-Managed Cache**

- Challenge 1: How to efficiently migrate a row between segments?

- **Challenge 2:** How to efficiently manage the cache?

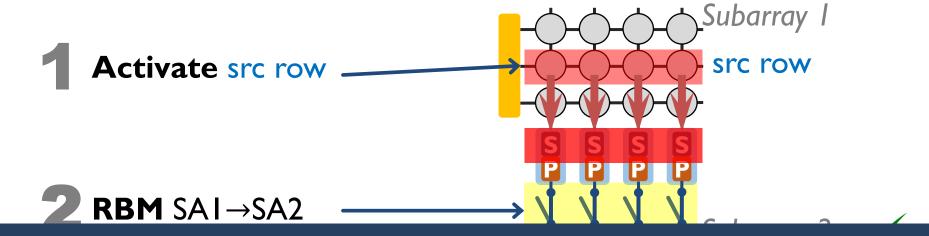

# **Inter-Segment Migration**

- **Goal:** Migrate source row into destination row

- Naïve way: Memory controller reads the source row byte by byte and writes to destination row byte by byte

# **Inter-Segment Migration**

### • Our way:

- Source and destination cells share bitlines

- Transfer data from source to destination across shared bitlines concurrently

Far Segment

### **Isolation Transistor**

Near Segment

Sense Amplifier

# **Inter-Segment Migration**

### • Our way:

- Source and destination cells share bitlines

- Transfer data from sor shared bitlines concu Step 1: Activate source row

- **Migration is overlapped with source row access**

- Additional ~4ns over row access latency

Step 2: Activate destination row to connect cell and bitline

Near Segment

Sense Amplifier

### **Near Segment as Hardware-Managed Cache**

- **Challenge 1:** How to efficiently migrate a row between segments?

- Challenge 2: How to efficiently manage the cache?

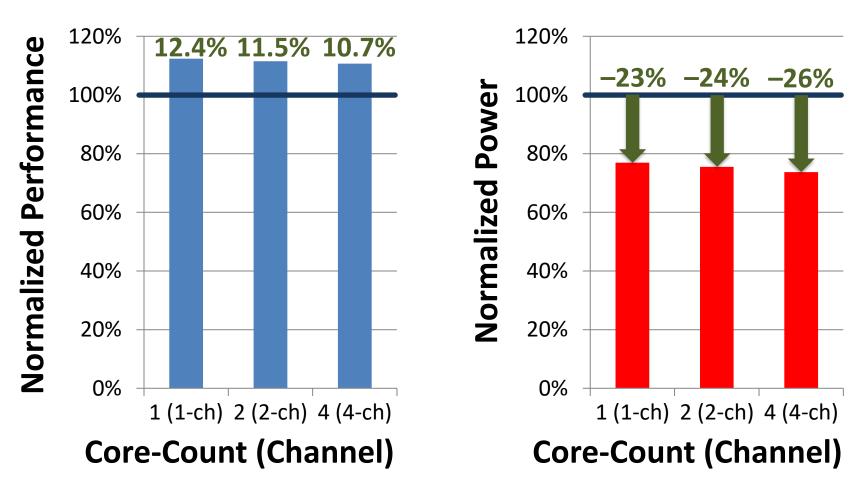

## **Performance & Power Consumption**

# Using near segment as a cache improves performance and reduces power consumption

Lee+, "Tiered-Latency DRAM: A Low Latency and Low Cost DRAM Architecture," HPCA 2013.

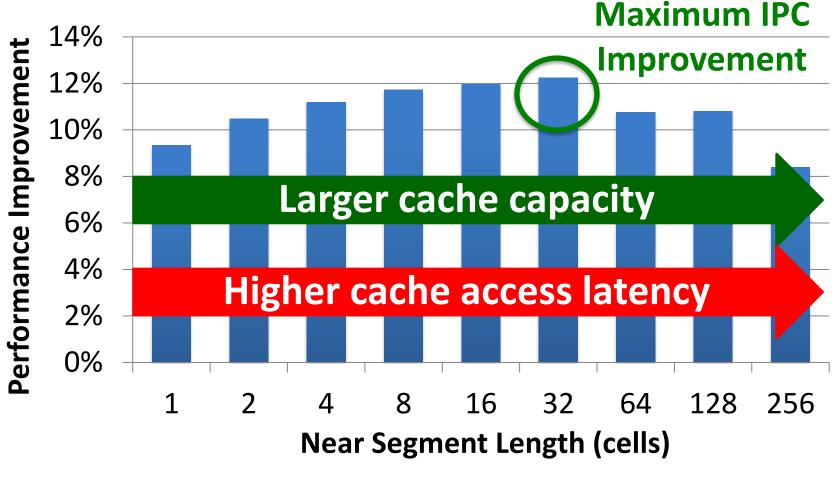

## Single-Core: Varying Near Segment Length

By adjusting the near segment length, we can trade off cache capacity for cache latency

### More on TL-DRAM

Donghyuk Lee, Yoongu Kim, Vivek Seshadri, Jamie Liu, Lavanya Subramanian, and Onur Mutlu,

"Tiered-Latency DRAM: A Low Latency and Low Cost DRAM Architecture"

Proceedings of the 19th International Symposium on High-Performance Computer Architecture (HPCA), Shenzhen, China,

February 2013. Slides (pptx)

#### Tiered-Latency DRAM: A Low Latency and Low Cost DRAM Architecture

Donghyuk Lee Yoongu Kim Vivek Seshadri Jamie Liu Lavanya Subramanian Onur Mutlu Carnegie Mellon University

#### SAFARI

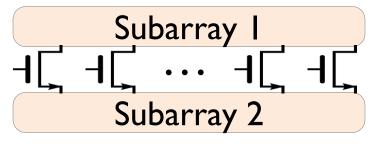

## LISA: Low-Cost Inter-Linked Subarrays [HPCA 2016]

### **Problem: Inefficient Bulk Data Movement**

Bulk data movement is a key operation in many applications – memmove & memcpy: 5% cycles in Google's datacenter [Kanev+ ISCA'15]

Long latency and high energy

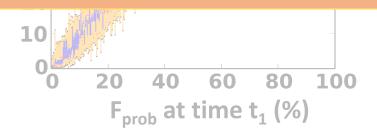

## Moving Data Inside DRAM?

# Goal: Provide a new substrate to enable wide connectivity between subarrays

# **Key Idea and Applications**

- Low-cost Inter-linked subarrays (LISA)

- Fast bulk data movement between subarrays

- Wide datapath via isolation transistors: 0.8% DRAM chip area

- LISA is a versatile substrate → new applications

Fast bulk data copy: Copy latency 1.363ms→0.148ms (9.2x)

→ 66% speedup, -55% DRAM energy

- In-DRAM caching: Hot data access latency 48.7ns→21.5ns (2.2x) → 5% speedup

Fast precharge: Precharge latency  $13.1ns \rightarrow 5.0ns$  (2.6x)

$\rightarrow$  8% speedup

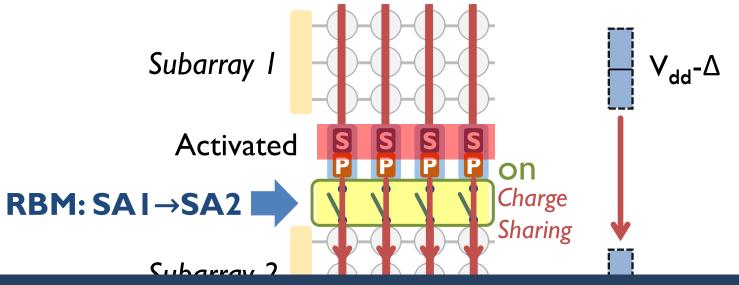

# New DRAM Command to Use LISA

**Row Buffer Movement (RBM)**: Move a row of data in an activated row buffer to a precharged one

#### **RBM transfers an entire row b/w subarrays**

# **RBM** Analysis

- The range of RBM depends on the DRAM design

- Multiple RBMs to move data across > 3 subarrays

- Validated with SPICE using worst-case cells

NCSU FreePDK 45nm library

- **4KB data in 8ns** (w/ 60% guardband)  $\rightarrow$  **500 GB/s, 26x** bandwidth of a DDR4-2400 channel

- 0.8% DRAM chip area overhead [O+ISCA'14]

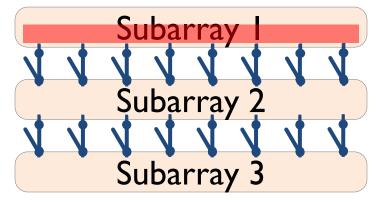

# 1. Rapid Inter-Subarray Copying (RISC)

- Goal: Efficiently copy a row across subarrays

- Key idea: Use RBM to form a new command sequence

### Reduces row-copy latency by 9.2x, DRAM energy by 48.1x

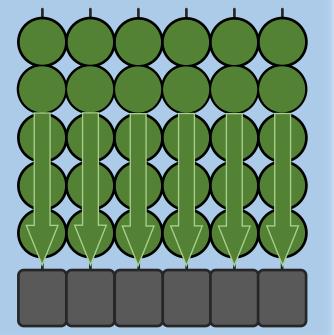

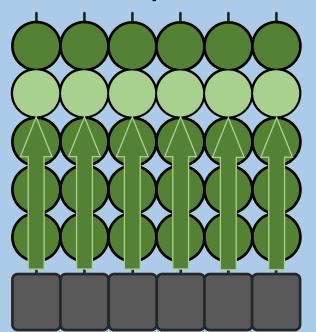

# 2.Variable Latency DRAM (VILLA)

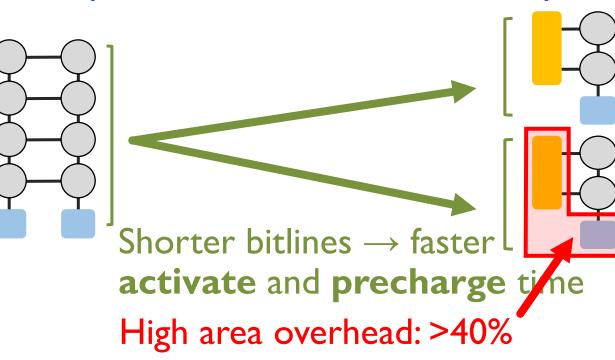

- Goal: Reduce DRAM latency with low area overhead

- Motivation: Trade-off between area and latency

Long Bitline

(DDRx)

Short Bitline

(RLDRAM)

# 2.Variable Latency DRAM (VILLA)

- Key idea: Reduce access latency of hot data via a heterogeneous DRAM design [Lee+ HPCA'13, Son+ ISCA'13]

- VILLA: Add fast subarrays as a cache in each bank

**Challenge**:VILLA cache requires

# Reduces hot data access latency by 2.2x at only 1.6% area overhead

# 3. Linked Precharge (LIP)

- **Problem**: The precharge time is limited by the strength of one precharge unit

- Linked Precharge (LIP): LISA precharges a subarray using multiple precharge units

# Reduces precharge latency by 2.6x (43% guardband)

### More on LISA

Kevin K. Chang, Prashant J. Nair, Saugata Ghose, Donghyuk Lee, Moinuddin K. Qureshi, and Onur Mutlu,

"Low-Cost Inter-Linked Subarrays (LISA): Enabling Fast Inter-Subarray Data Movement in DRAM"

Proceedings of the <u>22nd International Symposium on High-</u> Performance Computer Architecture (HPCA), Barcelona, Spain, March 2016.

[Slides (pptx) (pdf)]

[Source Code]

#### Low-Cost Inter-Linked Subarrays (LISA): Enabling Fast Inter-Subarray Data Movement in DRAM

Kevin K. Chang<sup>†</sup>, Prashant J. Nair<sup>\*</sup>, Donghyuk Lee<sup>†</sup>, Saugata Ghose<sup>†</sup>, Moinuddin K. Qureshi<sup>\*</sup>, and Onur Mutlu<sup>†</sup> <sup>†</sup>Carnegie Mellon University <sup>\*</sup>Georgia Institute of Technology

#### SAFARI

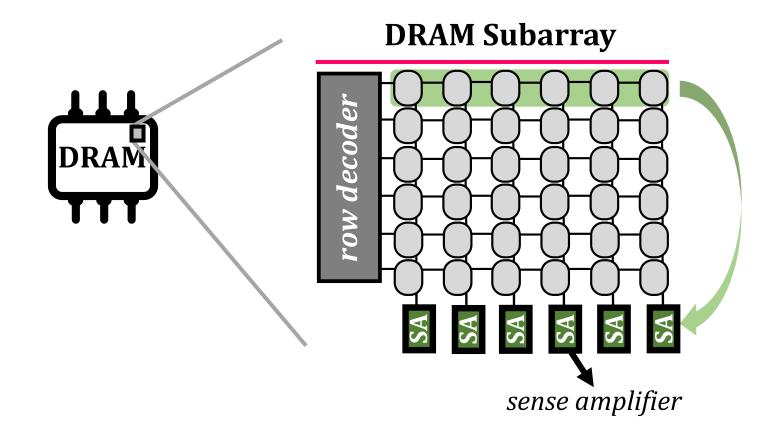

# CROW: The Copy Row Substrate [ISCA 2019]

# **Challenges of DRAM Scaling**

**3** exposure to vulnerabilities

DRAM

# **Conventional DRAM**

# Copy Row DRAM (CROW)

# **Use Cases of CROW**

# ➤ CROW-cache ✓ reduces access latency

### ≻CROW-ref

✓ reduces DRAM *refresh* overhead

➢A mechanism for protecting against *RowHammer*

# **Key Results**

### **CROW-cache + CROW-ref**

- •20% speedup

- •22% less DRAM energy

### **Hardware Overhead**

- •0.5% DRAM chip area

- •1.6% DRAM capacity

- •11.3 KiB memory controller storage

### More on CROW

Hasan Hassan, Minesh Patel, Jeremie S. Kim, A. Giray Yaglikci, Nandita Vijaykumar, Nika Mansourighiasi, Saugata Ghose, and Onur Mutlu,

"CROW: A Low-Cost Substrate for Improving DRAM Performance, Energy Efficiency, and Reliability"

Proceedings of the <u>46th International Symposium on Computer Architecture</u> (**ISCA**), Phoenix, AZ, USA, June 2019. [<u>Slides (pptx) (pdf</u>)] [<u>Lightning Talk Slides (pptx) (pdf</u>)] [<u>Poster (pptx) (pdf</u>)] [<u>Lightning Talk Video</u> (3 minutes)] [<u>Full Talk Video</u> (16 minutes)] [<u>Source Code for CROW</u> (Ramulator and Circuit Modeling)]

#### CROW: A Low-Cost Substrate for Improving DRAM Performance, Energy Efficiency, and Reliability

Hasan Hassan<sup>†</sup> Minesh Patel<sup>†</sup> Jeremie S. Kim<sup>†§</sup> A. Giray Yaglikci<sup>†</sup> Nandita Vijaykumar<sup>†§</sup> Nika Mansouri Ghiasi<sup>†</sup> Saugata Ghose<sup>§</sup> Onur Mutlu<sup>†§</sup>

<sup>†</sup>*ETH Zürich* <sup>§</sup>*Carnegie Mellon University*

#### SAFARI

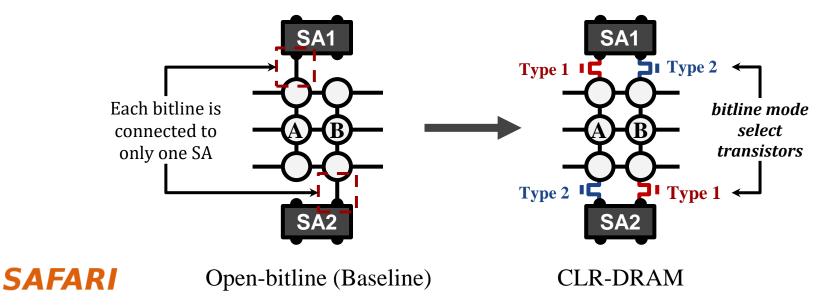

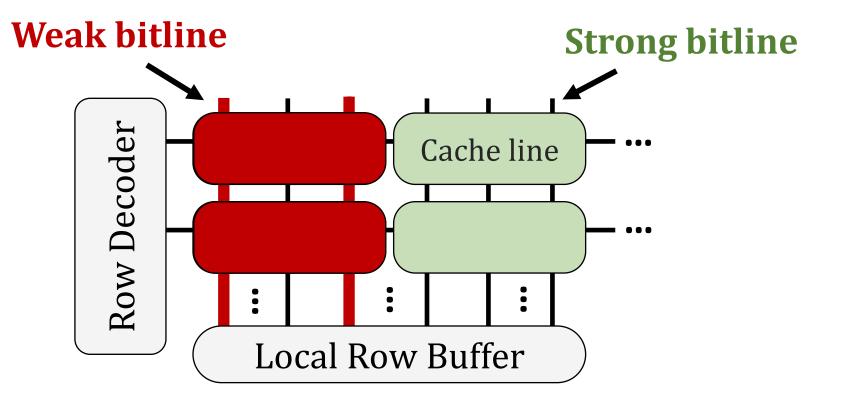

### CLR-DRAM: Capacity-Latency Reconfigurability

Haocong Luo, Taha Shahroodi, Hasan Hassan, Minesh Patel, A. Giray Yaglikci, Lois Orosa, Jisung Park, and Onur Mutlu,

"CLR-DRAM: A Low-Cost DRAM Architecture Enabling

Dynamic Capacity-Latency Trade-Off"

Proceedings of the <u>47th International Symposium on Computer</u>

<u>Architecture</u> (ISCA), Valencia, Spain, June 2020.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Talk Video (20 minutes)]

[Lightning Talk Video (3 minutes)]

#### CLR-DRAM: A Low-Cost DRAM Architecture Enabling Dynamic Capacity-Latency Trade-Off

Haocong Luo<sup>§†</sup> Taha Shahroodi<sup>§</sup> Hasan Hassan<sup>§</sup> Minesh Patel<sup>§</sup> A. Giray Yağlıkçı<sup>§</sup> Lois Orosa<sup>§</sup> Jisung Park<sup>§</sup> Onur Mutlu<sup>§</sup> <sup>§</sup>ETH Zürich <sup>†</sup>ShanghaiTech University

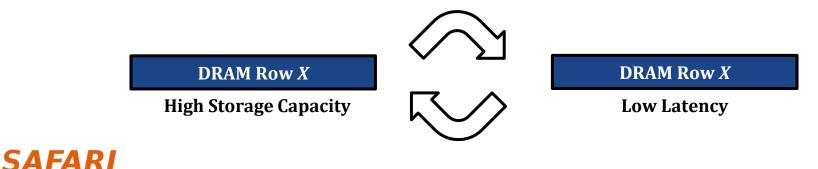

## CLR-DRAM: Capacity-Latency Reconfigurable DRAM [ISCA 2020]

### **CLR-DRAM:** A Low-Cost DRAM Architecture Enabling Dynamic Capacity-Latency Trade-off

Haocong Luo Taha Shahroodi Hasan Hassan Minesh Patel A. Giray Yaglıkçı Lois Orosa Jisung Park Onur Mutlu

#### **Motivation & Goal**

- Workloads and systems have varying main memory capacity and latency demands.

- Existing commodity DRAM makes static capacity-latency trade-off at design time.

- Systems miss opportunities to improve performance by adapting to changes in main memory capacity and latency demands.

- <u>Goal</u>: Design a low-cost DRAM architecture that can be dynamically configured to have high capacity or low latency at a fine granularity (i.e., at the granularity of a row).

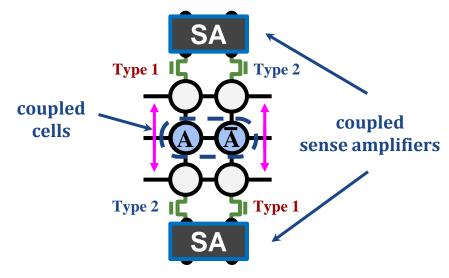

#### CLR-DRAM (Capacity-Latency-Reconfigurable DRAM)

- CLR-DRAM (Capacity-Latency-Reconfigurable DRAM):

- A low cost DRAM architecture that enables a single DRAM row to *dynamically* switch between **max-capacity mode** or **high-performance mode**.

#### • Key Idea:

*Dynamically* configure the connections between DRAM cells and sense amplifiers in the density-optimized open-bitline architecture.

104

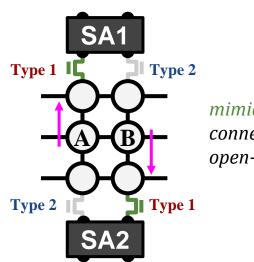

#### CLR-DRAM (Capacity-Latency-Reconfigurable DRAM)

• Max-capacity mode

*mimics the cell-to-SA connections as in the open-bitline architecture*

The same storage capacity as the conventional open-bitline architecture

#### SAFARI

Reduced latency and refresh overhead via coupled cell/SA operation

105

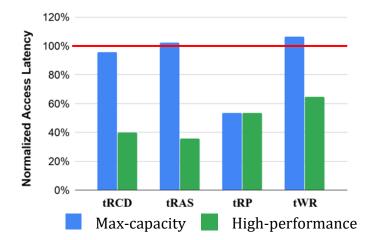

#### **Key Results**

#### <u>DRAM Latency Reduction</u>:

- Activation latency (tRCD) by 60.1%

- Restoration latency (tRAS) by 64.2%

- Precharge latency (**tRP**) by **46.4%**

- Write-recovery latency (tWR) by 35.2%

#### <u>System-level Benefits</u>:

- Performance improvement: **18.6%**

- DRAM energy reduction: **29.7%**

- DRAM refresh energy reduction: **66.1%**

We hope that CLR-DRAM can be exploited to develop more flexible systems that can adapt to the diverse and changing DRAM capacity and latency demands of workloads.

#### **SAFARI**

### More on CLR-DRAM

Haocong Luo, Taha Shahroodi, Hasan Hassan, Minesh Patel, A. Giray Yaglikci, Lois Orosa, Jisung Park, and Onur Mutlu,

"CLR-DRAM: A Low-Cost DRAM Architecture Enabling

Dynamic Capacity-Latency Trade-Off"

Proceedings of the <u>47th International Symposium on Computer</u>

Architecture (ISCA), Valencia, Spain, June 2020.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Lightning Talk Video (3 minutes)]

#### CLR-DRAM: A Low-Cost DRAM Architecture Enabling Dynamic Capacity-Latency Trade-Off

Haocong Luo<sup>§†</sup> Taha Shahroodi<sup>§</sup> Hasan Hassan<sup>§</sup> Minesh Patel<sup>§</sup> A. Giray Yağlıkçı<sup>§</sup> Lois Orosa<sup>§</sup> Jisung Park<sup>§</sup> Onur Mutlu<sup>§</sup> <sup>§</sup>ETH Zürich <sup>†</sup>ShanghaiTech University

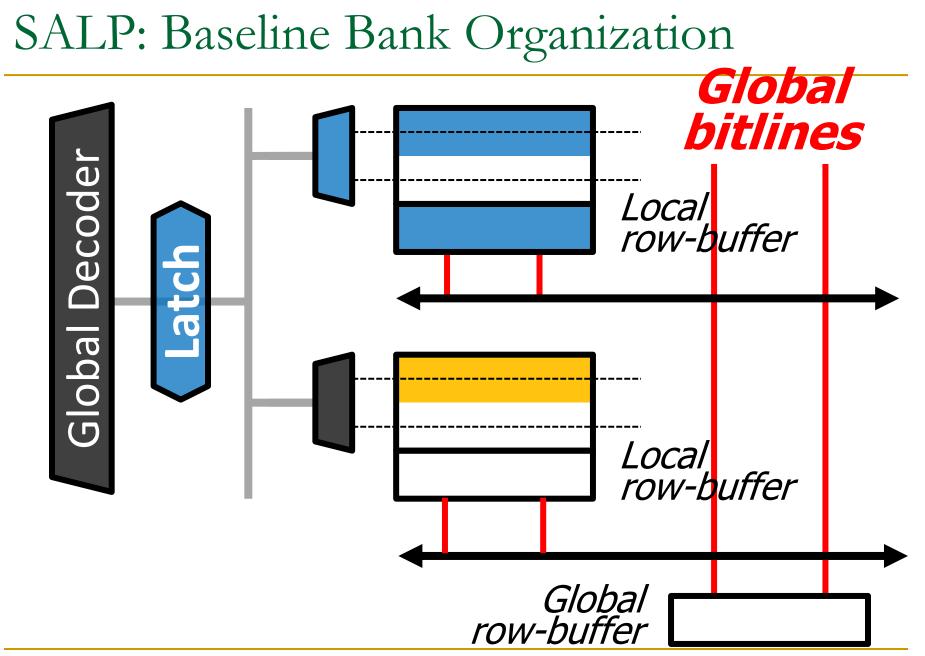

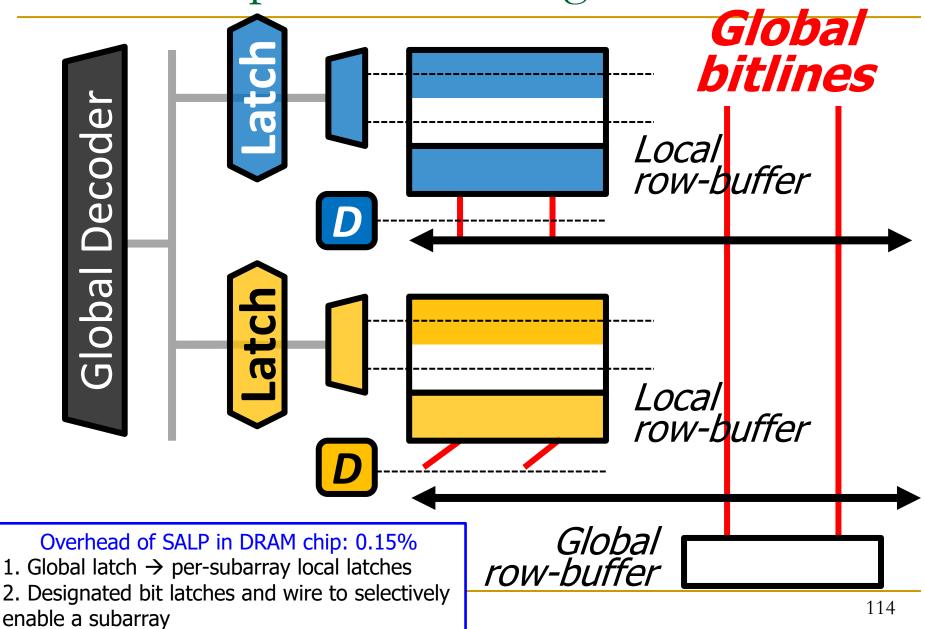

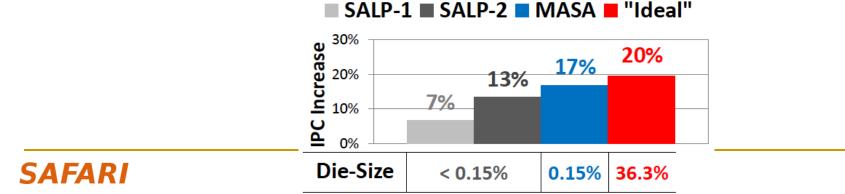

# SALP: Reducing DRAM Bank Conflict Impact

Kim, Seshadri, Lee, Liu, Mutlu <u>A Case for Exploiting Subarray-Level Parallelism</u> (SALP) in DRAM ISCA 2012.

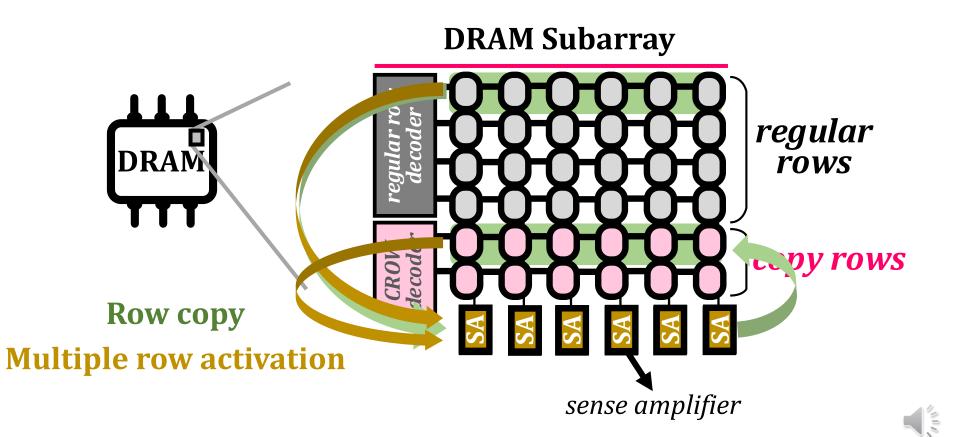

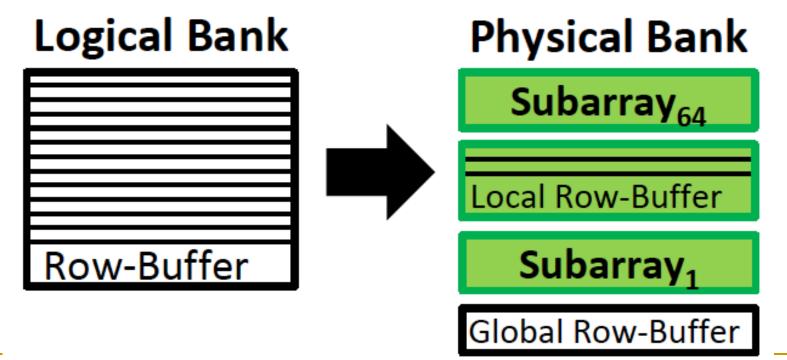

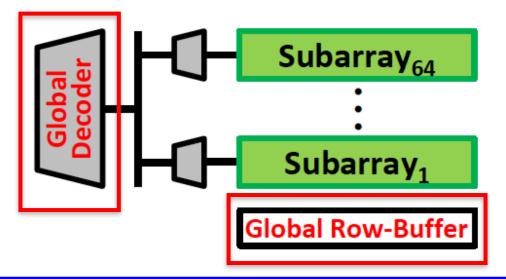

## SALP: Problem, Goal, Observations

- Problem: Bank conflicts are costly for performance and energy

- serialized requests, wasted energy (thrashing of row buffer, busy wait)

- Goal: Reduce bank conflicts without adding more banks (low cost)

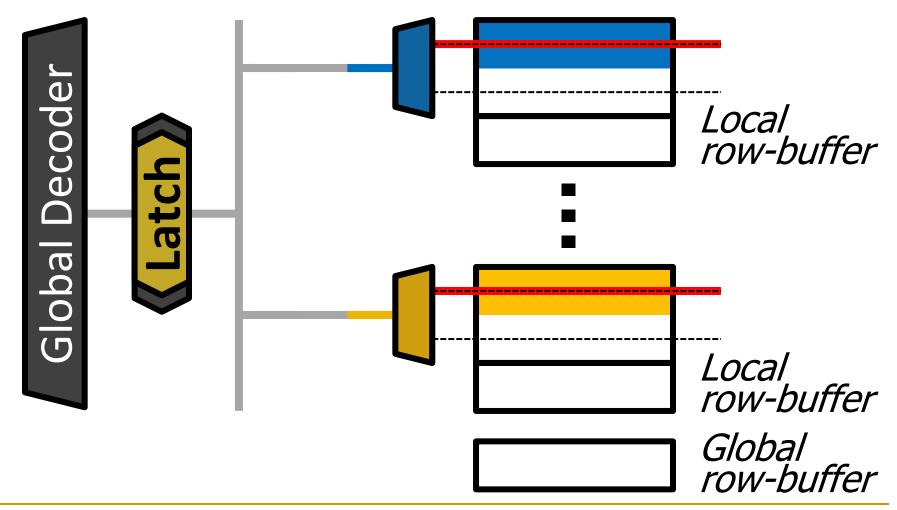

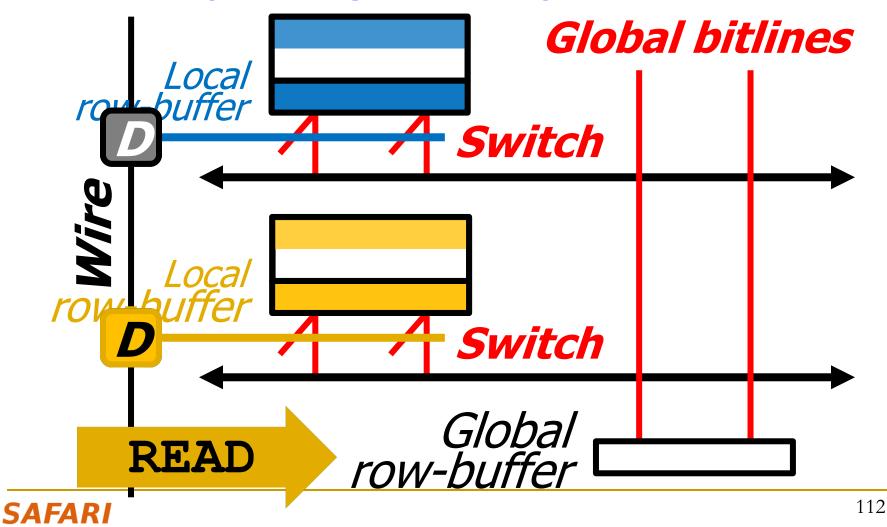

- Observation 1: A DRAM bank is divided into subarrays and each subarray has its own local row buffer

# SALP: Key Ideas

- Observation 2: Subarrays are mostly independent

- Except when sharing global structures to reduce cost

Key Idea of SALP: Minimally reduce sharing of global structures

Reduce the sharing of ...

Global decoder  $\rightarrow$  Enables almost parallel access to subarrays Global row buffer  $\rightarrow$  Utilizes multiple local row buffers

#### SAFARI

# SALP: Reduce Sharing of Global Decoder

Instead of a global latch, have *per-subarray latches*

### SALP: Reduce Sharing of Global Row-Buffer

Selectively connect local row-buffers to global rowbuffer using a *Designated* single-bit latch

#### SAFARI

## SALP: Proposed Bank Organization

## SALP: Results

- Wide variety of systems with different #channels, banks, ranks, subarrays

- Server, streaming, random-access, SPEC workloads

- Dynamic DRAM energy reduction: 19%

- DRAM row hit rate improvement: 13%

- System performance improvement: 17%

- Within 3% of ideal (all independent banks)

- DRAM die area overhead: 0.15%

- vs. 36% overhead of independent banks

115

Yoongu Kim, Vivek Seshadri, Donghyuk Lee, Jamie Liu, and Onur Mutlu,

"A Case for Exploiting Subarray-Level Parallelism (SALP) in DRAM"

Proceedings of the <u>39th International Symposium on</u> <u>Computer Architecture</u> (**ISCA**), Portland, OR, June 2012. <u>Slides (pptx)</u>

### A Case for Exploiting Subarray-Level Parallelism (SALP) in DRAM

Yoongu Kim

Vivek Seshadri Donghyuk Lee Jamie Liu Carnegie Mellon University

**Onur** Mutlu

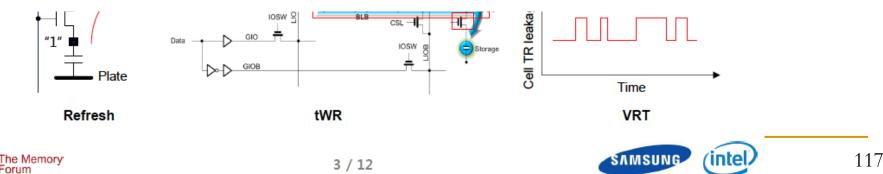

### **DRAM Process Scaling Challenges**

#### \* Refresh

Difficult to build high-aspect ratio cell capacitors decreasing cell capacitance

THE MEMORY FORUM 2014

# Co-Architecting Controllers and DRAM to Enhance DRAM Process Scaling

Uksong Kang, Hak-soo Yu, Churoo Park, \*Hongzhong Zheng, \*\*John Halbert, \*\*Kuljit Bains, SeongJin Jang, and Joo Sun Choi

Samsung Electronics, Hwasung, Korea / \*Samsung Electronics, San Jose / \*\*Intel

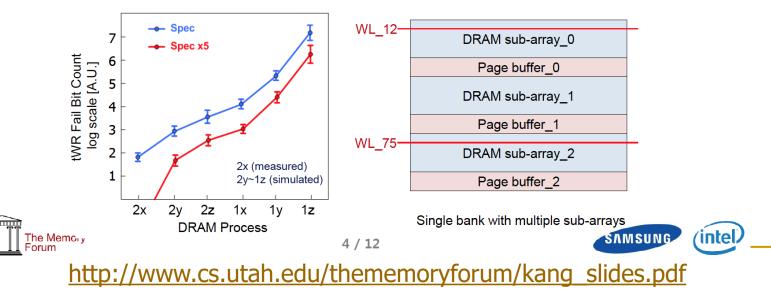

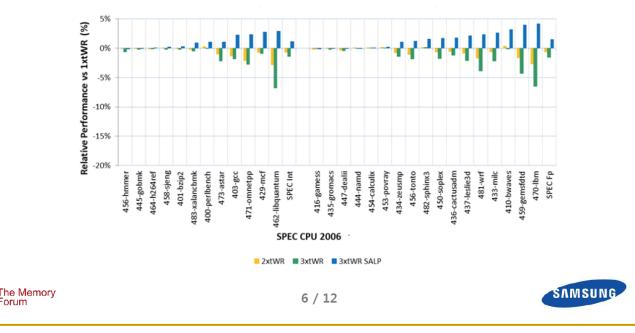

### **Sub-array Level Parallelism with tWR Relaxation**

#### tWR relaxation

SAFAR

- Relaxing tWR results in DRAM yield improvement but can degrade performance requiring new compensating features

- By increasing tWR 5X (from 15ns to 75ns), fail bit counts are expected to reduce by 1 to 2 orders of magnitudes

#### Sub-array level parallelism (SALP)

- Allows a page in another sub-array in the same bank to be opened in parallel with the currently activated sub-array

- Results in performance gain by increasing the row access parallelism within a bank

⇒ Used to compensate for the performance loss caused by tWR relaxation

#### **Performance Impact of SALP and tWR relaxation**

- Performance simulations run for various workloads when tWR is relaxed by 2X and 3X, and when SALP is applied with 2 sub-banks

- Results show that performance is reduced by ~5% and ~2% in average if tWR is relaxed by 3X and 2X, respectively

- Results also show that performance is compensated, and even improved to up to ~3% in average when SALP is applied, even with tWR relaxed by 3X

SAFARI

http://www.cs.utah.edu/thememoryforum/kang\_slides.pdf

**inte**

## Why the Long Memory Latency?

- Reason 1: Design of DRAM Micro-architecture

- Goal: Maximize capacity/area, not minimize latency

# Tackling the Fixed Latency Mindset

- Reliable operation latency is actually very heterogeneous

Across temperatures, chips, parts of a chip, voltage levels, ...

- Idea: Dynamically find out and use the lowest latency one can reliably access a memory location with

- Adaptive-Latency DRAM [HPCA 2015]

- Flexible-Latency DRAM [SIGMETRICS 2016]

- Design-Induced Variation-Aware DRAM [SIGMETRICS 2017]

- Voltron [SIGMETRICS 2017]

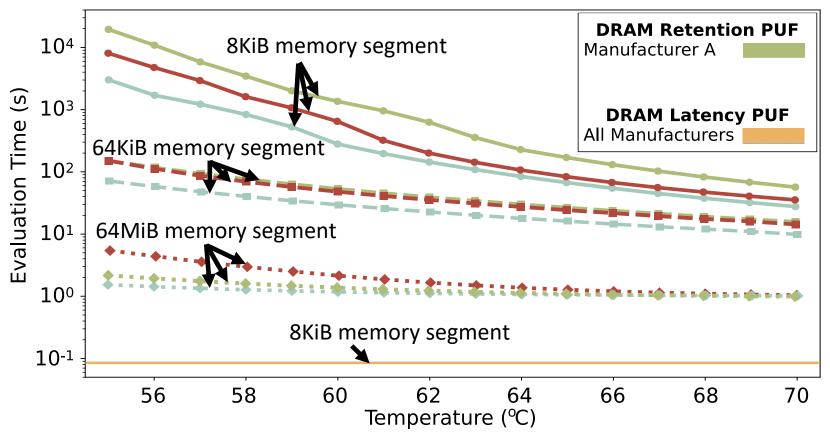

- DRAM Latency PUF [HPCA 2018]

- Solar DRAM [ICCD 2018]

- DRAM Latency True Random Number Generator [HPCA 2019]

•••

We would like to find sources of latency heterogeneity and exploit them to minimize latency (or create other benefits)

5AFARI

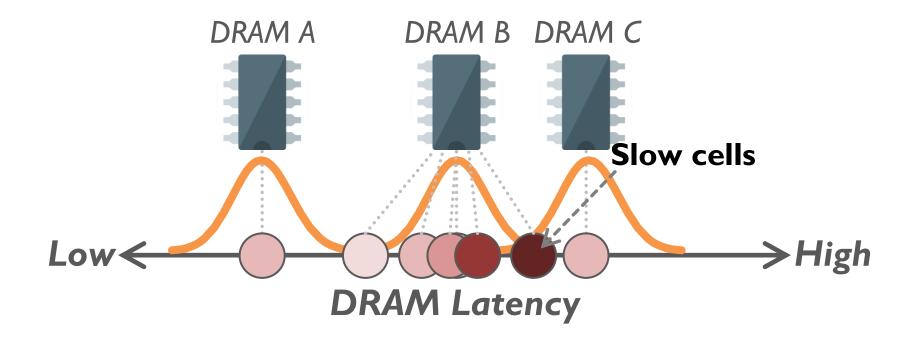

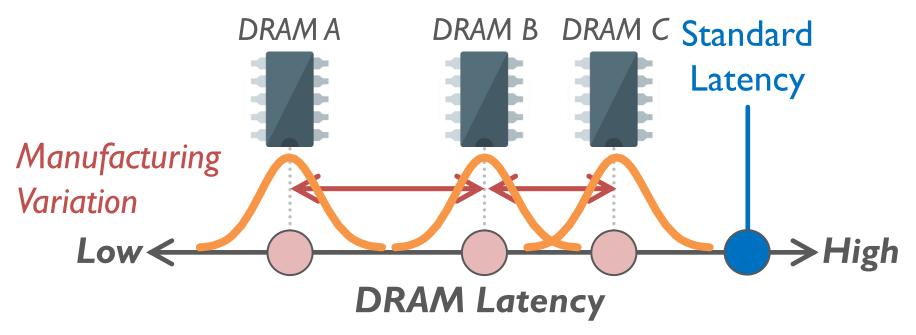

# Latency Variation in Memory Chips

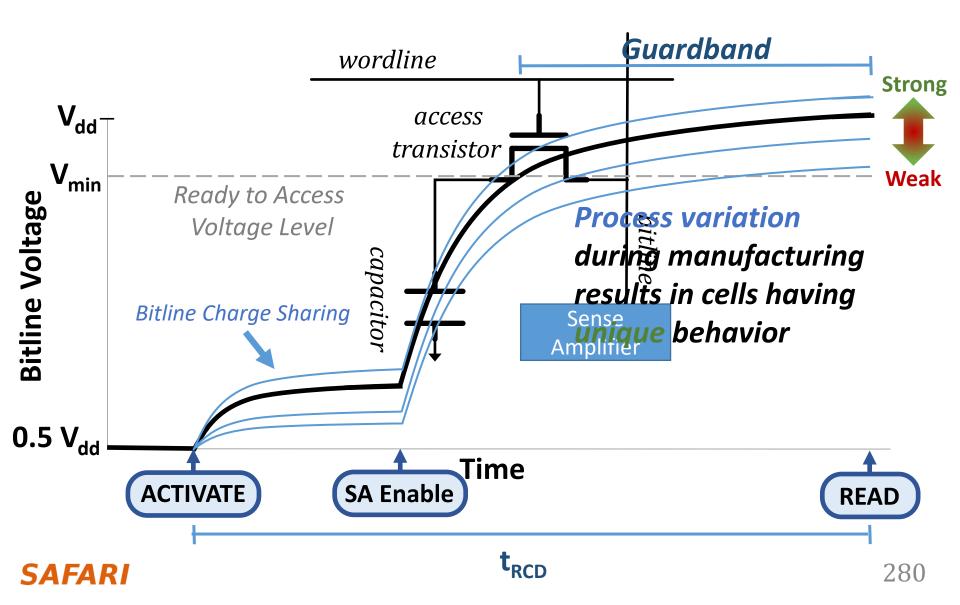

### Heterogeneous manufacturing & operating conditions → latency variation in timing parameters

# Why is Latency High?

- DRAM latency: Delay as specified in DRAM standards

- Doesn't reflect true DRAM device latency

- Imperfect manufacturing process  $\rightarrow$  latency variation

- High standard latency chosen to increase yield

## What Causes the Long Memory Latency?

### Conservative timing margins!

DRAM timing parameters are set to cover the worst case

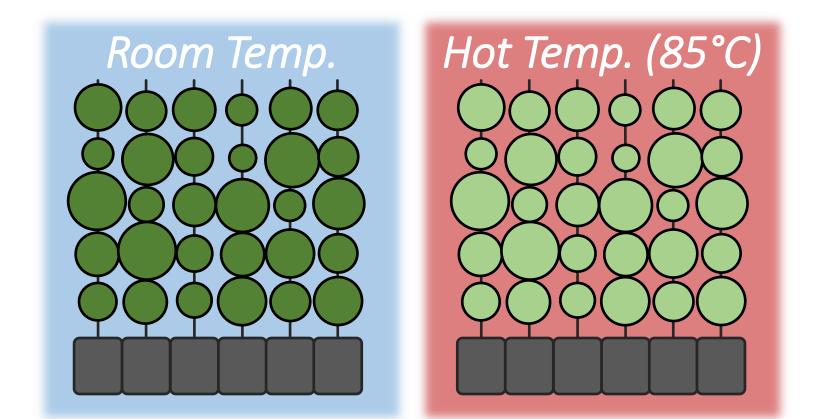

### Worst-case temperatures

- 85 degrees vs. common-case

- to enable a wide range of operating conditions

- Worst-case devices

- DRAM cell with smallest charge across any acceptable device

- to tolerate process variation at acceptable yield

- This leads to large timing margins for the common case

#### SAFARI

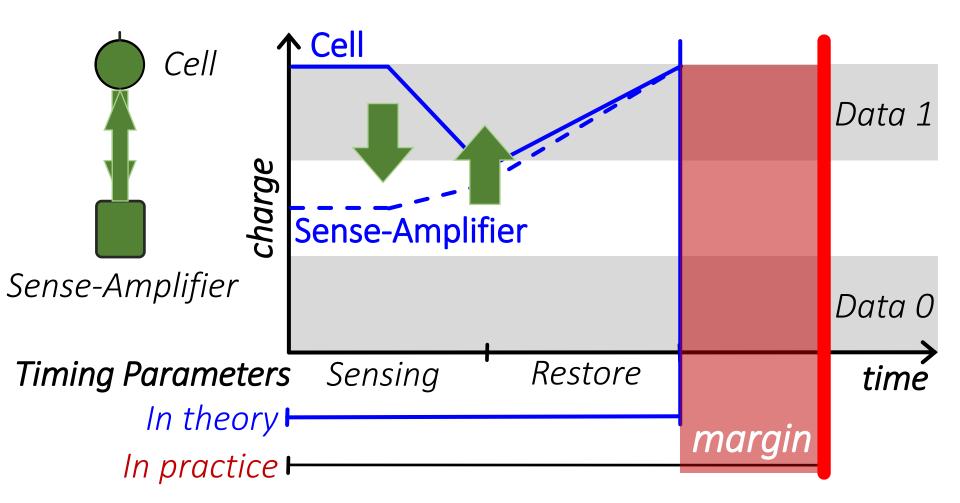

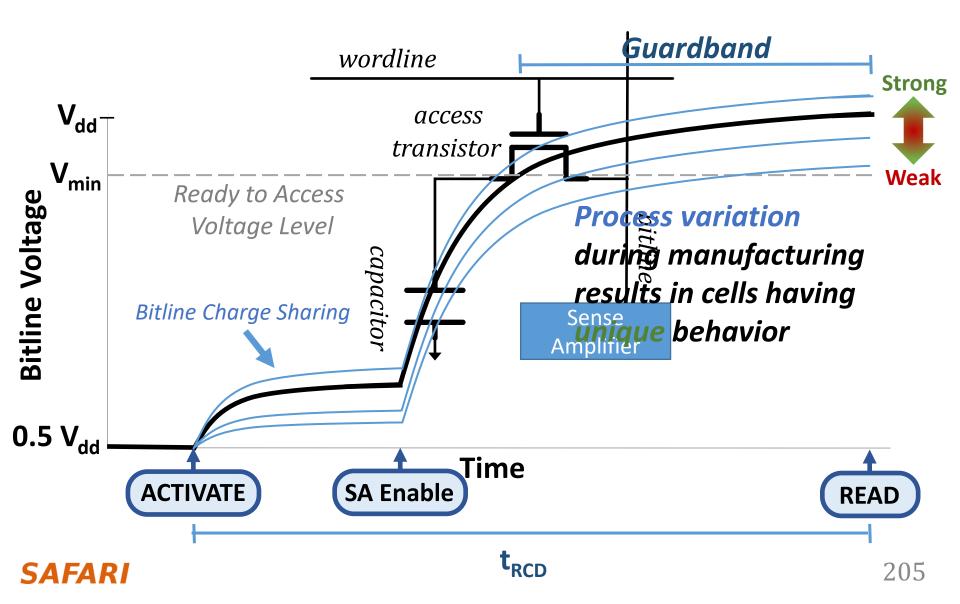

# Understanding and Exploiting Variation in DRAM Latency

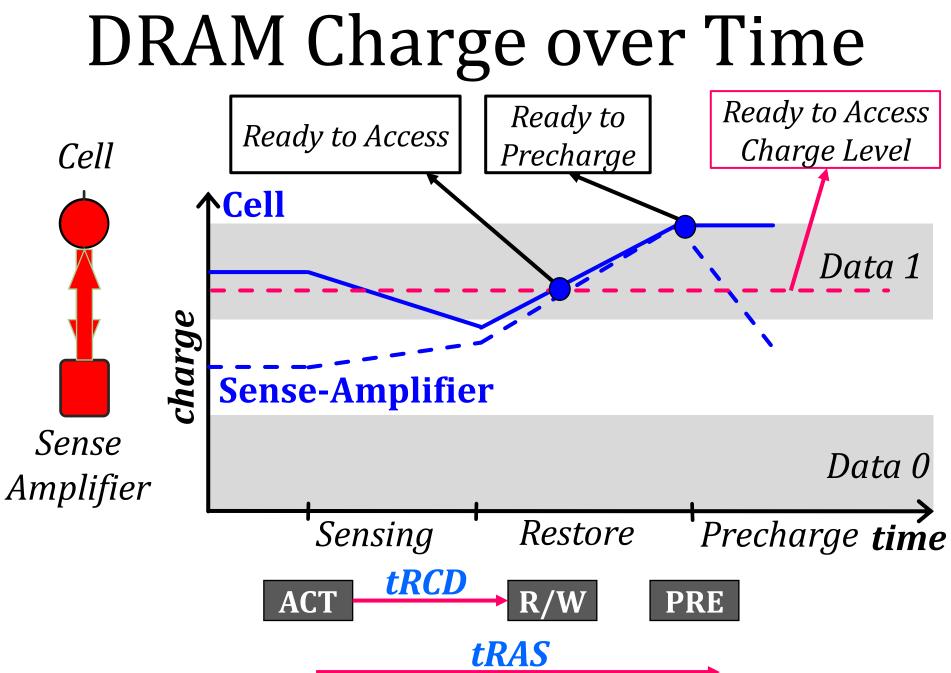

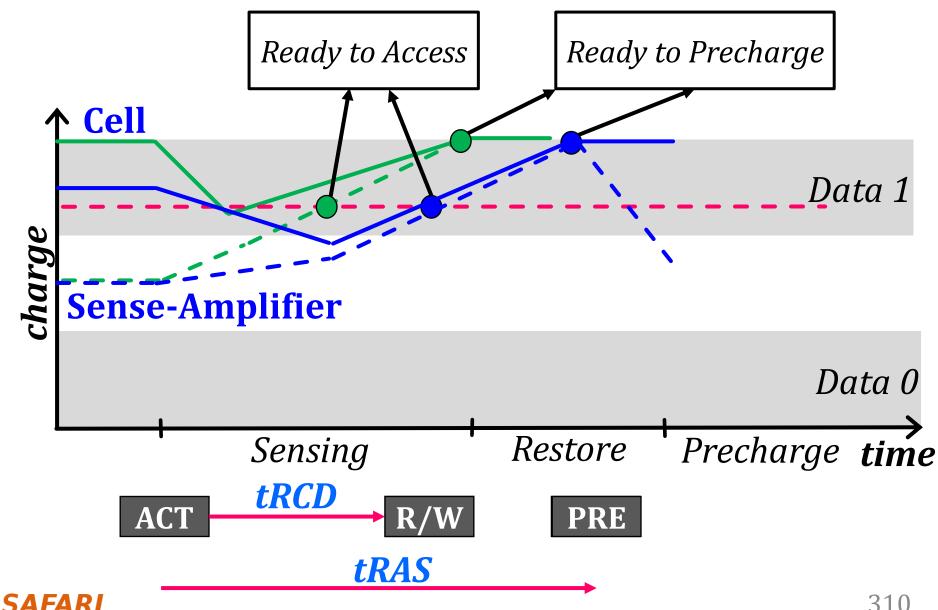

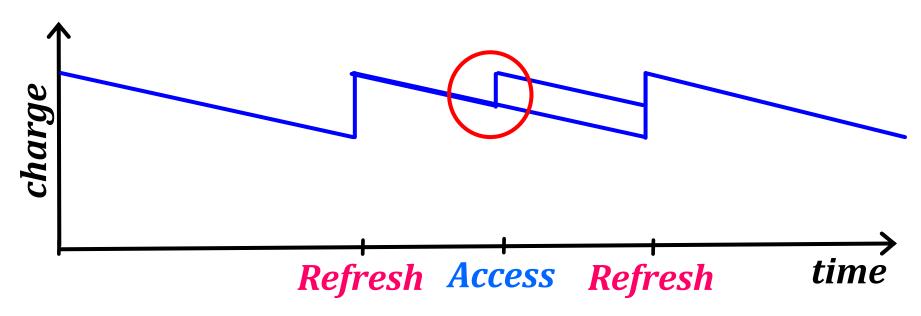

# DRAM Charge over Time

Why does DRAM need the extra timing margin?

### SAFARI

# Two Reasons for Timing Margin

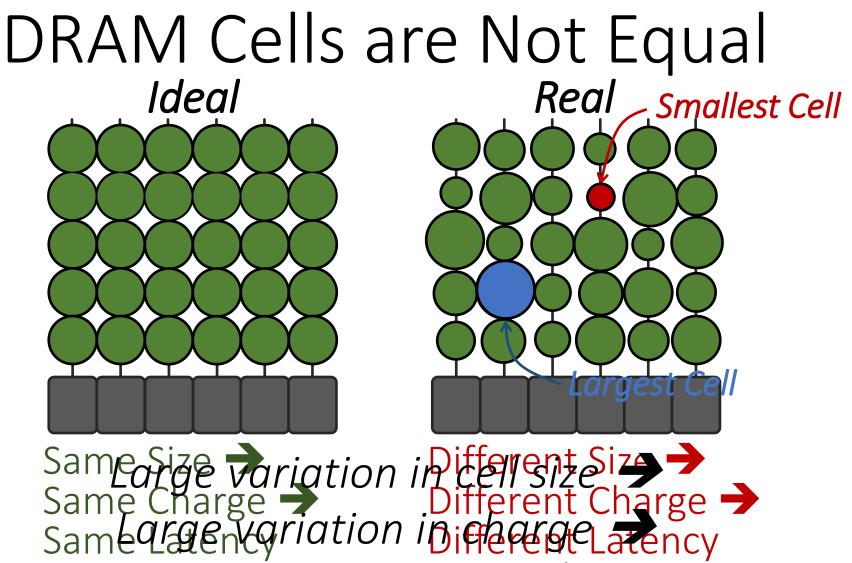

### **1. Process Variation**

- DRAM cells are not equal

- Leads to extra timing margin for a cell that can store a large amount of charge

- 2. Temperature Dependence

Large variation in access latency

# **Process Variation**

# Two Reasons for Timing Margin

### 1. Process Variation

- DRAM cells are not equal

- Leads to extra timing margin for a cell that can store a large amount of charge

### 2. Temperature Dependence

- DRAM leaks more charge at higher temperature

- Leads to extra timing margin for cells that operate at low temperature

# Charge Leakage vs. Temperature

Cells store is mailine temperature and large charge at low temperature Large variation in access latency SAFARI

# **DRAM Timing Parameters**

- DRAM timing parameters are dictated by the worst-case

- The smallest cell with the smallest charge <u>in</u> <u>all DRAM products</u>

- Operating at the highest temperature

• Large timing margin for the common-case

# Adaptive-Latency DRAM [HPCA 2015]

- Idea: Optimize DRAM timing for the common case

- Current temperature

- Current DRAM module

- Why would this reduce latency?

- A DRAM cell can store much more charge in the common case (low temperature, strong cell) than in the worst case

- More charge in a DRAM cell

- $\rightarrow$  Faster sensing, charge restoration, precharging

- $\rightarrow$  Faster access (read, write, refresh, ...)

# Extra Charge $\rightarrow$ Reduced Latency

# 1. Sensing

Sense cells with extra charge faster

→ Lower sensing latency

2. Restore

No need to fully restore cells with extra charge

→ Lower restoration latency

## 3. Precharge

No need to fully precharge bitlines for **cells with extra charge**

→ Lower precharge latency

### SAFARI

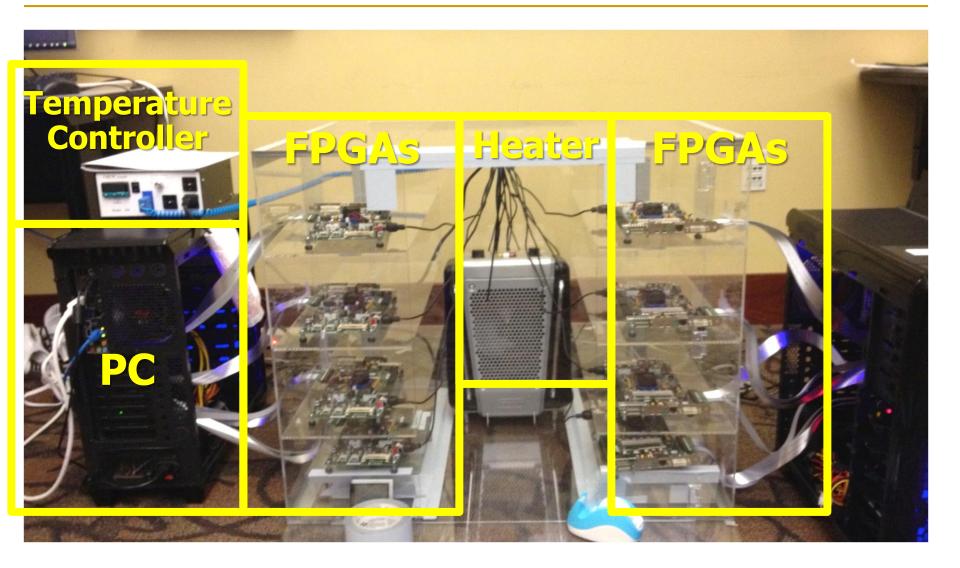

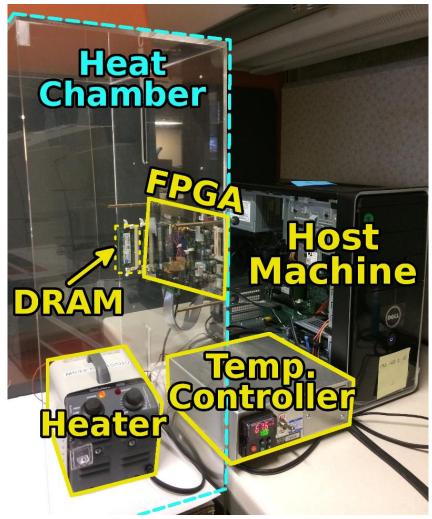

## DRAM Characterization Infrastructure

### **SAFARI**

Kim+, "Flipping Bits in Memory Without Accessing Them: An 136 Experimental Study of DRAM Disturbance Errors," ISCA 2014.

## DRAM Characterization Infrastructure

Hasan Hassan et al., <u>SoftMC: A</u> <u>Flexible and Practical Open-</u> <u>Source Infrastructure for</u> <u>Enabling Experimental DRAM</u> <u>Studies</u>, HPCA 2017.

- Flexible

- Easy to Use (C++ API)

- Open-source

github.com/CMU-SAFARI/SoftMC

## SoftMC: Open Source DRAM Infrastructure

<u>https://github.com/CMU-SAFARI/SoftMC</u>

### SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

Hasan Hassan<sup>1,2,3</sup> Nandita Vijaykumar<sup>3</sup> Samira Khan<sup>4,3</sup> Saugata Ghose<sup>3</sup> Kevin Chang<sup>3</sup> Gennady Pekhimenko<sup>5,3</sup> Donghyuk Lee<sup>6,3</sup> Oguz Ergin<sup>2</sup> Onur Mutlu<sup>1,3</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>TOBB University of Economics & Technology <sup>3</sup>Carnegie Mellon University <sup>4</sup>University of Virginia <sup>5</sup>Microsoft Research <sup>6</sup>NVIDIA Research

# **Observation 1. Faster Sensing**

*Typical DIMM at Low Temperature*

SAFARI

115 DIMM Characterization

Timing

(tRCD)

More Charge

Strong Charge Flow

**Faster Sensing**

17% ↓ No Errors

Typical DIMM at Low Temperature More charge

Faster sensing

# **Observation 2. Reducing Restore Time**

*Typical DIMM at Low Temperature*

Less Leakage -> Extra Charge

No Need to Fully Restore Charge 115 DIMM Characterization

Read (tRAS) 37% ↓

Write (tWR) 54% ↓ No Errors

Typical DIMM at lower temperature More charge

Restore time reduction

SAFARI

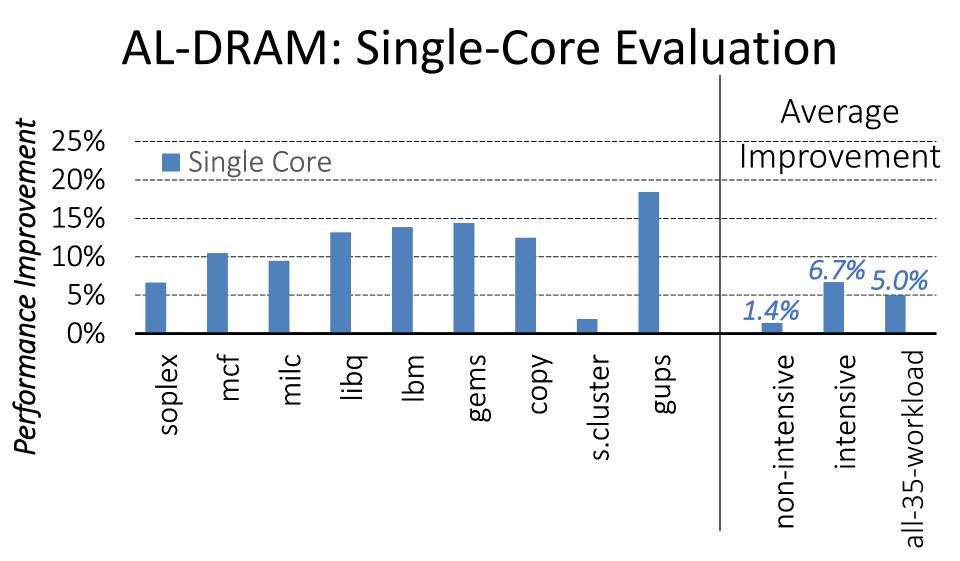

## **AL-DRAM**

- Key idea

- Optimize DRAM timing parameters online

- Two components

- DRAM manufacturer provides multiple sets of reliable DRAM timing parameters at different temperatures for each DIMM

- System monitors DRAM temperature & uses appropriate DRAM timing parameters

# **DRAM** Temperature

- DRAM temperature measurement

- Server cluster: Operates at under **34°C**

- Desktop: Operates at under **50°C**

- DRAM standard optimized for 85 ℃

# DRAM operates at low temperatures in the common-case

- Previous works Maintain low DRAM temperature

- David+ ICAC 2011

- Liu+ ISCA 2007

- Zhu+ ITHERM 2008

#### **SAFARI**

# Latency Reduction Summary of 115 DIMMs

- Latency reduction for read & write (55°C)

- Read Latency: **32.7%**

- Write Latency: 55.1%

- Latency reduction for each timing parameter (55°C)

- Sensing: **17.3%**

- Restore: 37.3% (read), 54.8% (write)

- Precharge: **35.2%**

**SAFARI** Lee+, "Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case," HPCA 143 2015.

## **AL-DRAM: Real System Evaluation**

• System

### - CPU: AMD 4386 ( 8 Cores, 3.1GHz, 8MB LLC)

| D18F2x200_dct[0]_mp[1:0] DDR3 DRAM Timing 0 |                                              |                                                                                                                                                                                                                                   |  |

|---------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset: 0                                    | )F05_0505h. Se                               | e 2.9.3 [DCT Configuration Registers].                                                                                                                                                                                            |  |

|                                             |                                              |                                                                                                                                                                                                                                   |  |

| Bits                                        | Description                                  |                                                                                                                                                                                                                                   |  |

| 31:30                                       | Reserved.                                    |                                                                                                                                                                                                                                   |  |

| 29:24                                       | the minimum to<br>to the same chi            | <b>ras: row active strobe</b> . Read-write. BIOS: See 2.9.7.5 [SPD ROM-Based Configuration]. Specifies ne minimum time in memory clock cycles from an activate command to a precharge command, both to the same chip select bank. |  |

|                                             | <u>Bits</u><br>07h-00h<br>2Ah-08h<br>3Fh-2Bh | Description<br>Reserved<br><tras> clocks<br/>Reserved</tras>                                                                                                                                                                      |  |

23:21 Reserved.

20:16 **Trp: row precharge time**. Read-write. BIOS: See 2.9.7.5 [SPD ROM-Based Configuration]. Specifies the minimum time in memory clock cycles from a precharge command to an activate command or auto refresh command, both to the same bank.

AL-DRAM improves performance on a real system

#### SAFARI

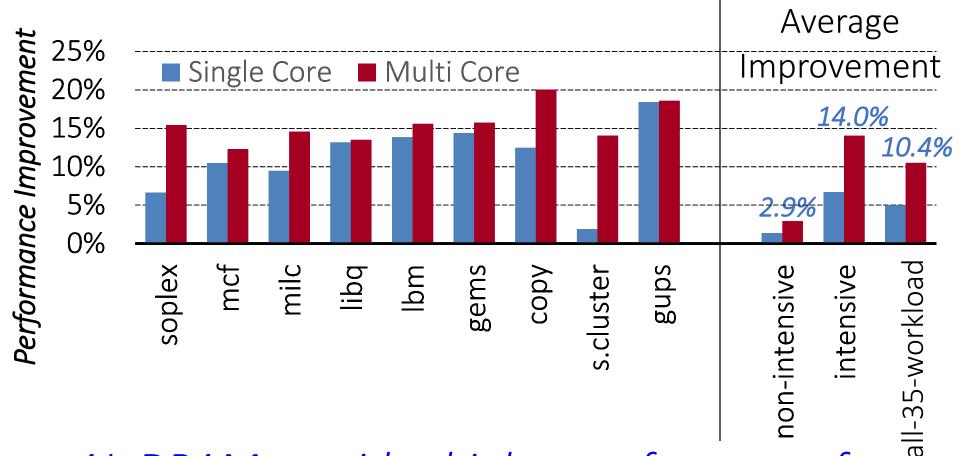

## AL-DRAM: Multi-Core Evaluation

AL-DRAM provides higher performance for " multi-programmed & multi-threaded workloads SAFARI

# Reducing Latency Also Reduces Energy

- AL-DRAM reduces DRAM power consumption by 5.8%

- Major reason: reduction in row activation time

## AL-DRAM: Advantages & Disadvantages

#### Advantages

- + Simple mechanism to reduce latency

- + Significant system performance and energy benefits

- + Benefits higher at low temperature

- + Low cost, low complexity

## Disadvantages

- Need to determine reliable operating latencies for different temperatures and different DIMMs  $\rightarrow$  higher testing cost

(might not be that difficult for low temperatures)

#### SAFARI

## More on AL-DRAM

Donghyuk Lee, Yoongu Kim, Gennady Pekhimenko, Samira Khan, Vivek Seshadri, Kevin Chang, and Onur Mutlu,

"Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case"

Proceedings of the <u>21st International Symposium on High-</u> Performance Computer Architecture (HPCA), Bay Area, CA,

February 2015. [<u>Slides (pptx) (pdf)</u>] [<u>Full data sets</u>]

#### Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case

Donghyuk LeeYoongu KimGennady PekhimenkoSamira KhanVivek SeshadriKevin ChangOnur Mutlu

Carnegie Mellon University

## Different Types of Latency Variation

- AL-DRAM exploits latency variation

- Across time (different temperatures)

- Across chips

- Is there also latency variation within a chip?

- Across different parts of a chip

## Why the Long Memory Latency?

- Reason 1: Design of DRAM Micro-architecture

- □ Goal: Maximize capacity/area, not minimize latency

- Reason 2: "One size fits all" approach to latency specification

- Same latency parameters for all temperatures

- Same latency parameters for all DRAM chips

- Same latency parameters for all parts of a DRAM chip

- Same latency parameters for all supply voltage levels

- Same latency parameters for all application data

•••

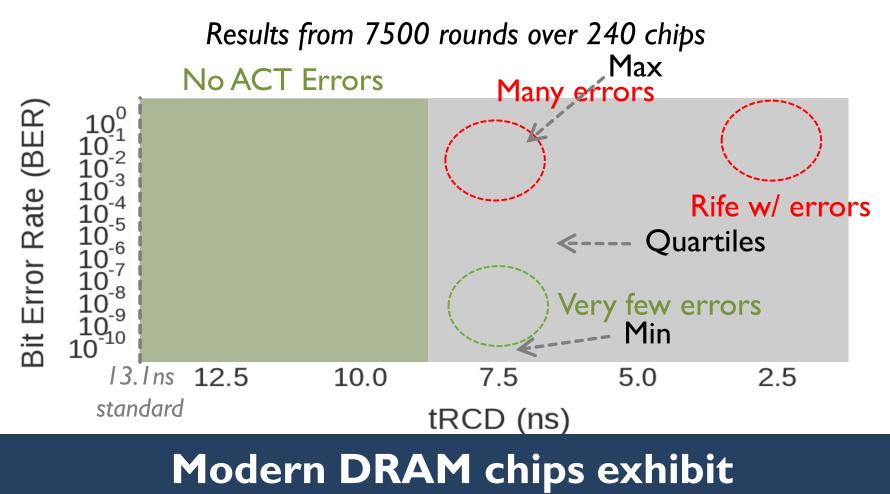

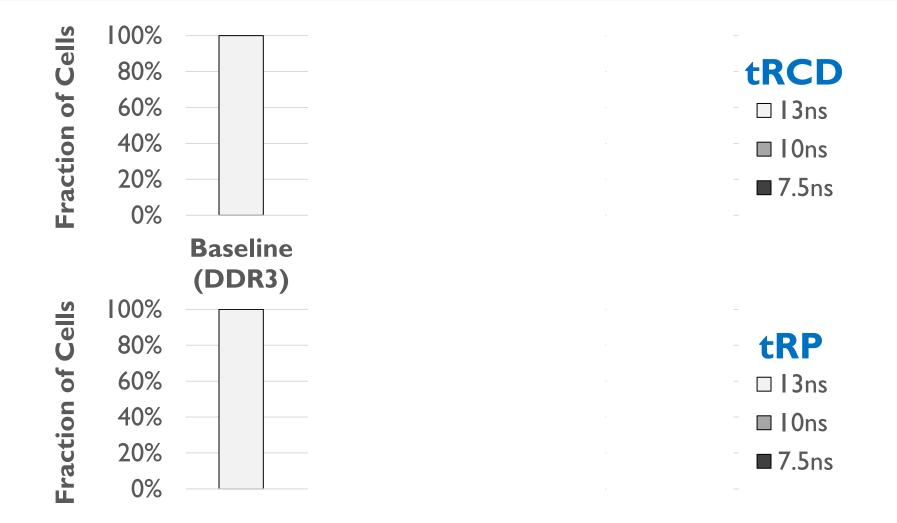

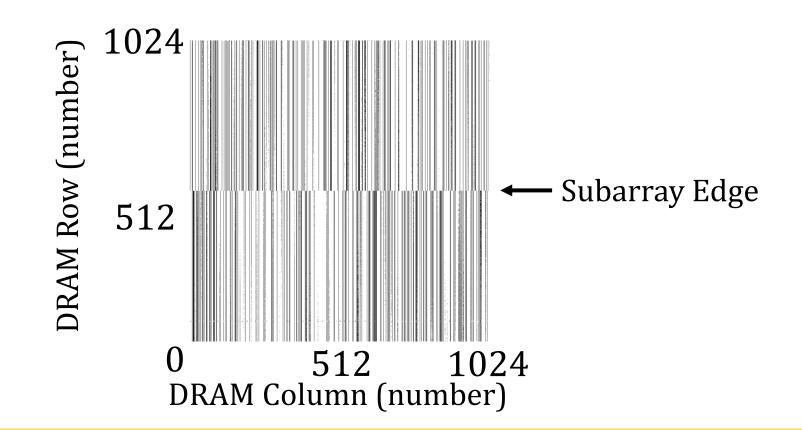

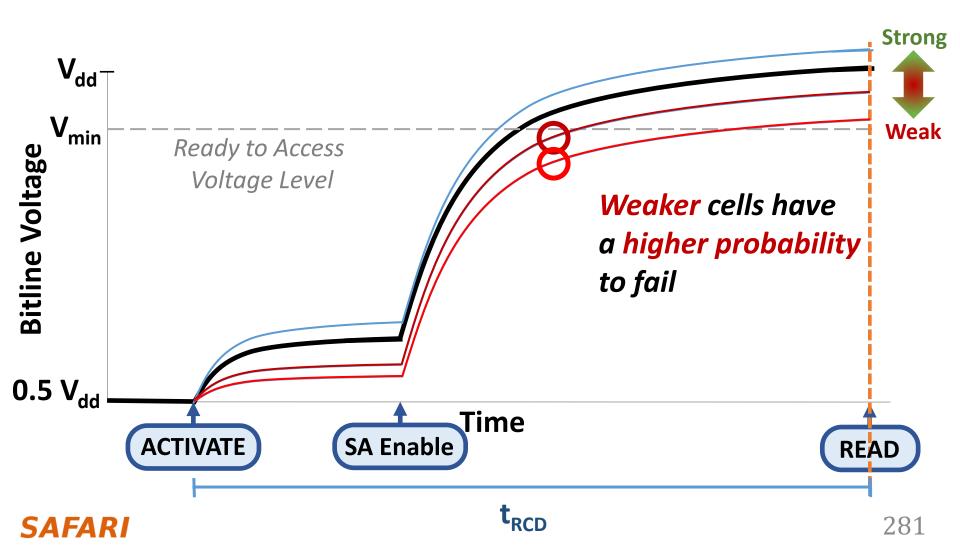

# Variation in Activation Errors

significant variation in activation latency

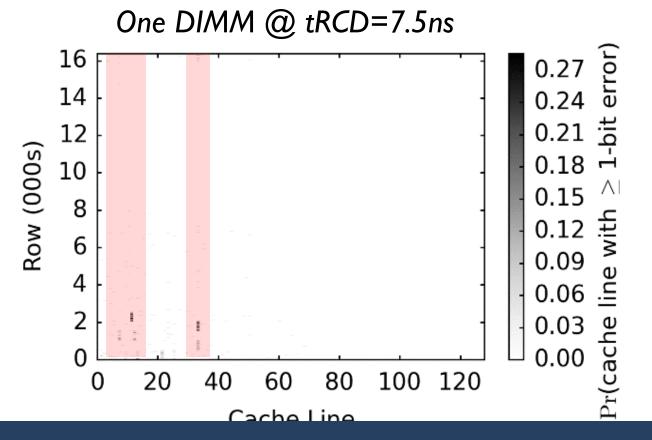

## **Spatial Locality of Activation Errors**

Activation errors are concentrated at certain columns of cells

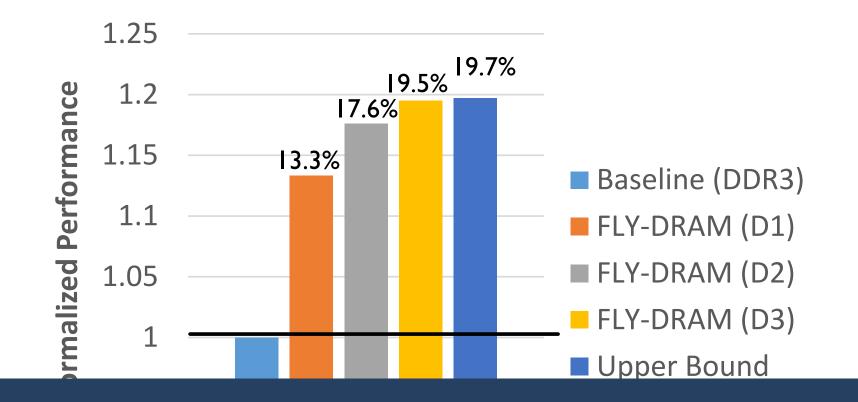

## Mechanism to Reduce DRAM Latency

- **Observation:** DRAM timing errors (slow DRAM cells) are concentrated in certain DRAM regions

- Flexible-LatencY (FLY) DRAM

- A software-transparent design that reduces latency

- Key idea:

- I) Divide memory into regions of different latencies

- 2) Memory controller: Use lower latency for regions without slow cells; higher latency for other regions

Chang+, "<u>Understanding Latency Variation in Modern DRAM Chips: Experimental</u> <u>Characterization, Analysis, and Optimization</u>"," SIGMETRICS 2016.

# **FLY-DRAM Configurations**

Chang+, "<u>Understanding Latency Variation in Modern DRAM Chips: Experimental</u> Characterization, Analysis, and Optimization"," SIGMETRICS 2016.

## Results

## FLY-DRAM improves performance by exploiting spatial latency variation in DRAM

Chang+, "Understanding Latency Variation in Modern DRAM Chips: Experimental Characterization, Analysis, and Optimization"," SIGMETRICS 2016.

## FLY-DRAM: Advantages & Disadvantages

#### Advantages

+ Reduces latency significantly

+ Exploits significant within-chip latency variation

## Disadvantages

- Need to determine reliable operating latencies for different parts of a chip  $\rightarrow$  higher testing cost

- More complicated controller

## Analysis of Latency Variation in DRAM Chips

- Kevin Chang, Abhijith Kashyap, Hasan Hassan, Samira Khan, Kevin Hsieh, Donghyuk Lee, Saugata Ghose, Gennady Pekhimenko, Tianshi Li, and Onur Mutlu,

- **<u>"Understanding Latency Variation in Modern DRAM Chips:</u> Experimental Characterization, Analysis, and Optimization"</u>**

- Proceedings of the <u>ACM International Conference on Measurement and</u> <u>Modeling of Computer Systems</u> (**SIGMETRICS**), Antibes Juan-Les-Pins, France, June 2016. [<u>Slides (pptx) (pdf)</u>] [<u>Source Code</u>]

## Understanding Latency Variation in Modern DRAM Chips: Experimental Characterization, Analysis, and Optimization

Kevin K. Chang<sup>1</sup> Abhijith Kashyap<sup>1</sup> Hasan Hassan<sup>1,2</sup> Saugata Ghose<sup>1</sup> Kevin Hsieh<sup>1</sup> Donghyuk Lee<sup>1</sup> Tianshi Li<sup>1,3</sup> Gennady Pekhimenko<sup>1</sup> Samira Khan<sup>4</sup> Onur Mutlu<sup>5,1</sup> <sup>1</sup>Carnegie Mellon University <sup>2</sup>TOBB ETÜ <sup>3</sup>Peking University <sup>4</sup>University of Virginia <sup>5</sup>ETH Zürich SAFARI

# Putting It All Together: Solar-DRAM

# Solar-DRAM: Putting It Together

Jeremie S. Kim, Minesh Patel, Hasan Hassan, and Onur Mutlu, "Solar-DRAM: Reducing DRAM Access Latency by <u>Exploiting the Variation in Local Bitlines</u>" *Proceedings of the <u>36th IEEE International Conference on</u> <u>Computer Design</u> (ICCD), Orlando, FL, USA, October 2018. [Slides (pptx) (pdf)] [Talk Video (16 minutes)]*

## Solar-DRAM: Reducing DRAM Access Latency by Exploiting the Variation in Local Bitlines

Jeremie S. Kim<sup>‡§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§‡</sup> <sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

## More on Solar DRAM

How are activation failures spatially distributed in DRAM?

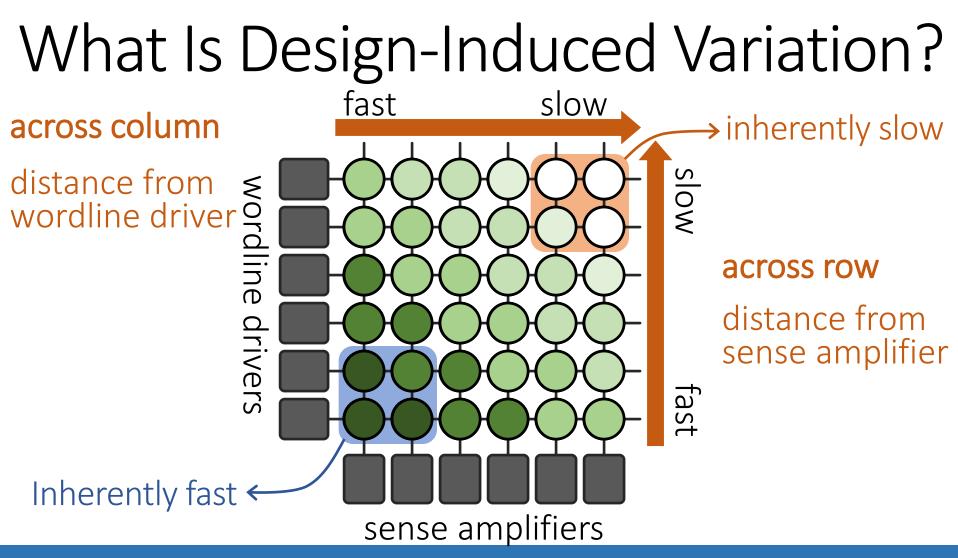

# Why Is There Spatial Latency Variation Within a Chip?

*Systematic variation* in cell access times caused by the *physical organization* of DRAM

#### SAFARI

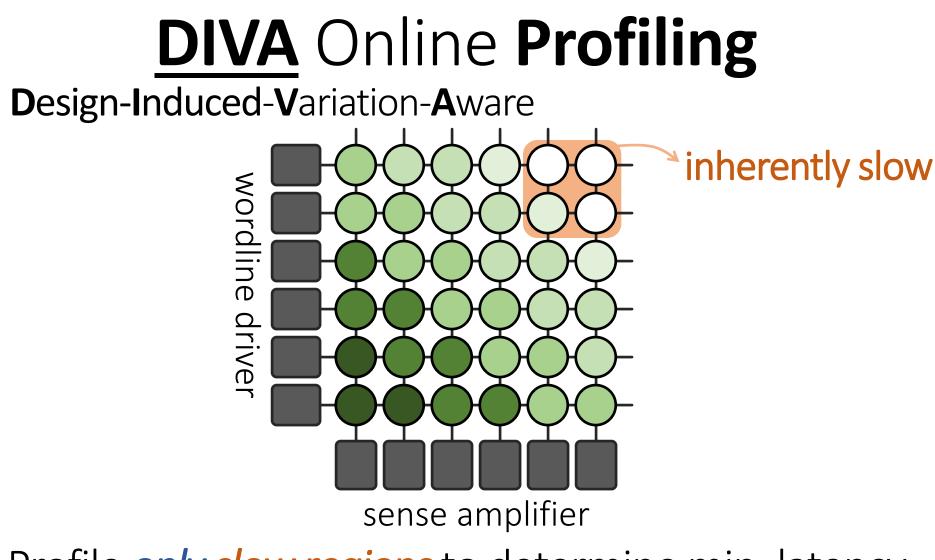

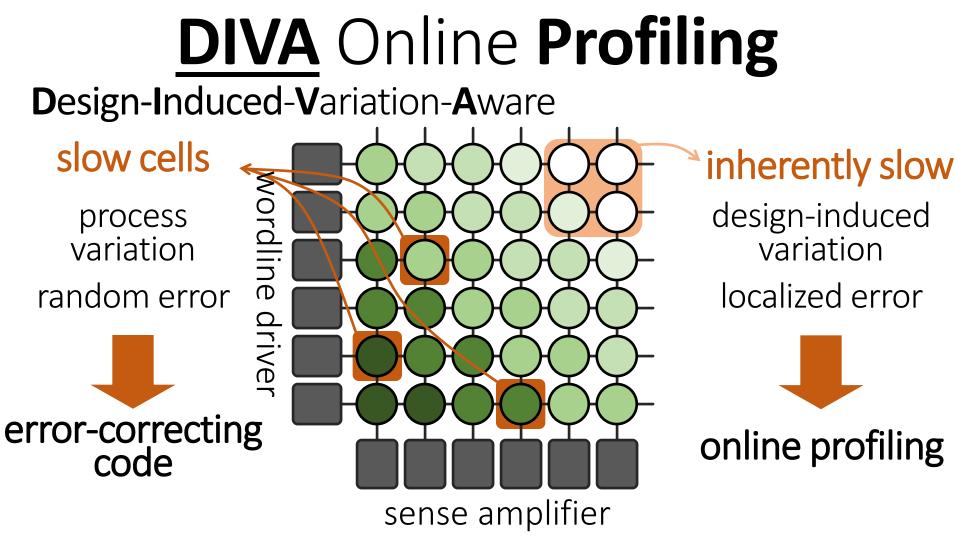

Profile only slow regions to determine min. latency → Dynamic & low cost latency optimization

Combine error-correcting codes & online profiling → Reliably reduce DRAM latency

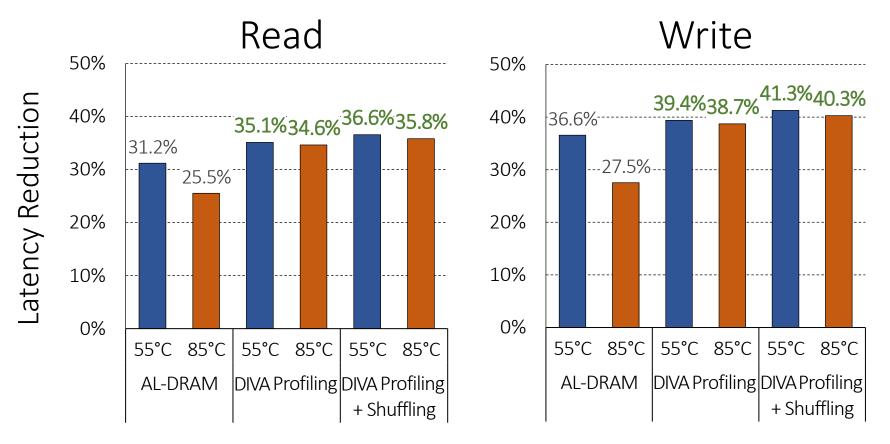

# **DIVA-DRAM Reduces Latency**

DIVA-DRAM *reduces latency more aggressively* and uses ECC to correct random slow cells

#### SAFARI

### Advantages

++ Automatically finds the lowest reliable operating latency at system runtime (lower production-time testing cost)

- + Reduces latency more than prior methods (w/ ECC)

- + Reduces latency at high temperatures as well

## Disadvantages

- Requires knowledge of inherently-slow regions

- Requires ECC (Error Correcting Codes)

- Imposes overhead during runtime profiling

- More complicated memory controller (capable of profiling)

## Design-Induced Latency Variation in DRAM

- Donghyuk Lee, Samira Khan, Lavanya Subramanian, Saugata Ghose, Rachata Ausavarungnirun, Gennady Pekhimenko, Vivek Seshadri, and Onur Mutlu,

- "Design-Induced Latency Variation in Modern DRAM Chips: Characterization, Analysis, and Latency Reduction Mechanisms" Proceedings of the <u>ACM International Conference on Measurement and</u> <u>Modeling of Computer Systems</u> (SIGMETRICS), Urbana-Champaign, IL, USA, June 2017.

#### Design-Induced Latency Variation in Modern DRAM Chips: Characterization, Analysis, and Latency Reduction Mechanisms

Donghyuk Lee, NVIDIA and Carnegie Mellon University

Samira Khan, University of Virginia

Lavanya Subramanian, Saugata Ghose, Rachata Ausavarungnirun, Carnegie Mellon University Gennady Pekhimenko, Vivek Seshadri, Microsoft Research

Onur Mutlu, ETH Zürich and Carnegie Mellon University

#### SAFARI

## Why the Long Memory Latency?

- Reason 1: Design of DRAM Micro-architecture

- □ Goal: Maximize capacity/area, not minimize latency

- Reason 2: "One size fits all" approach to latency specification

- Same latency parameters for all temperatures

- Same latency parameters for all DRAM chips

- Same latency parameters for all parts of a DRAM chip

- Same latency parameters for all supply voltage levels

- □ Same latency parameters for all application data

• • • • •

#### **SAFARI**

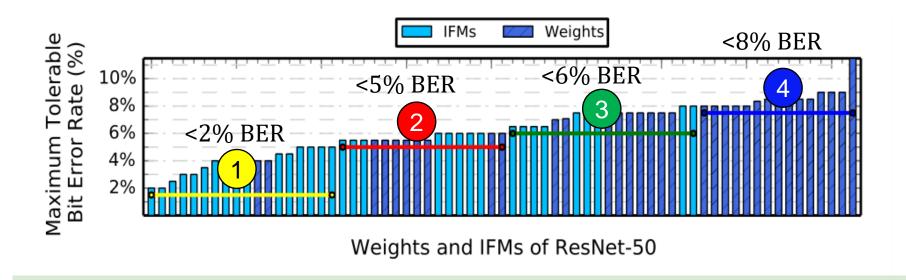

## Data-Aware DRAM Latency for DNN Inference

- Deep Neural Network evaluation is very DRAM-intensive (especially for large networks)

- 1. Some data and layers in DNNs are very tolerant to errors

- 2. Reduce DRAM latency and voltage on such data and layers

3. While still achieving a user-specified DNN accuracy target by making training DRAM-error-aware

#### Data-aware management of DRAM latency and voltage for Deep Neural Network Inference

## **Example DNN Data Type to DRAM Mapping**

#### Mapping example of ResNet-50:

## Map more error-tolerant DNN layers to DRAM partitions with lower voltage/latency

4 DRAM partitions with different error rates

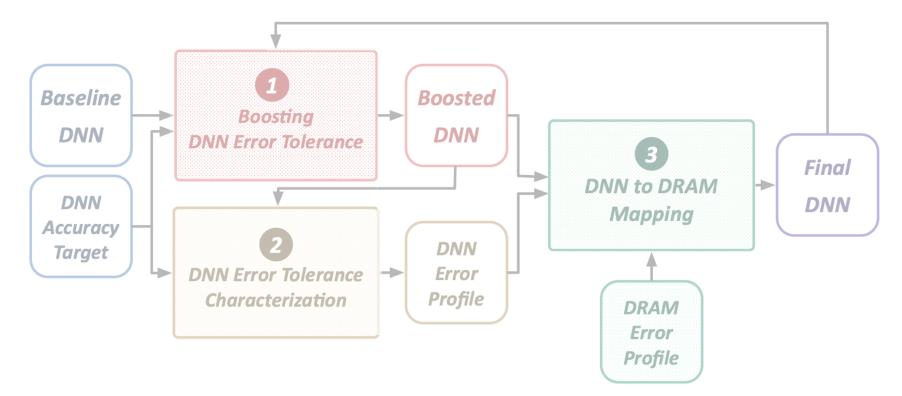

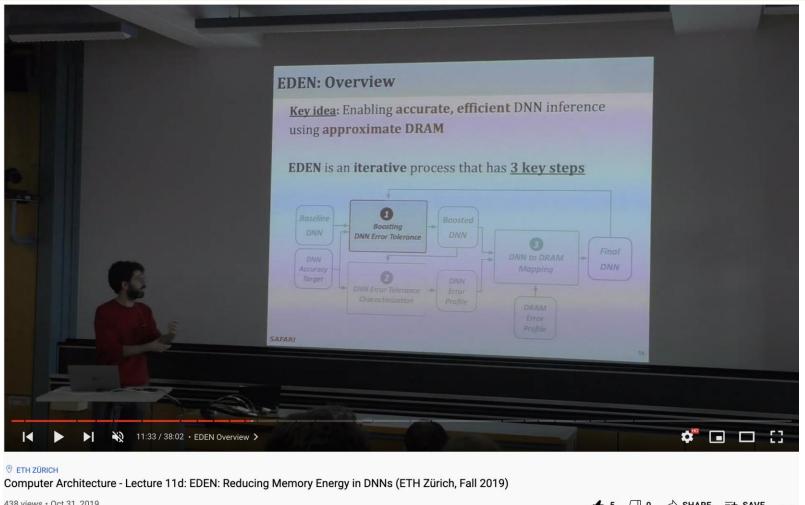

## **EDEN: Overview**

<u>Key idea</u>: Enable accurate, efficient DNN inference using approximate DRAM

### EDEN is an iterative process that has <u>3 key steps</u>

#### SAFARI

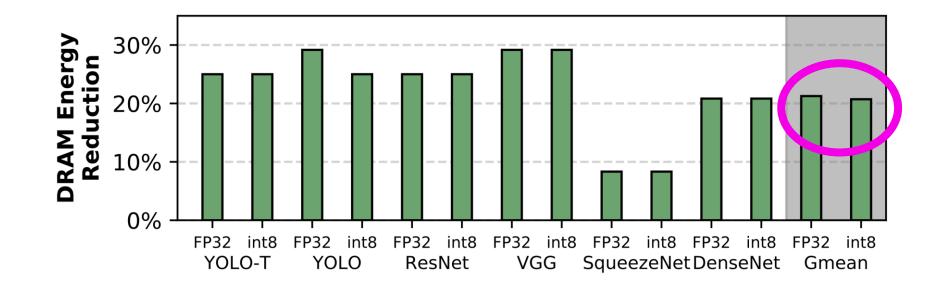

## **CPU: DRAM Energy Evaluation**

**Average 21% DRAM energy reduction** maintaining accuracy within 1% of original

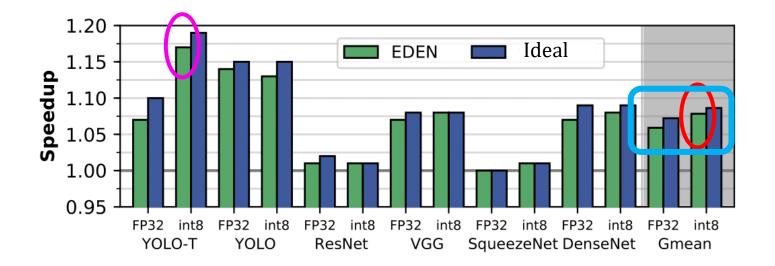

## **CPU: Performance Evaluation**

Average 8% system speedup Some workloads achieve 17% speedup

EDEN achieves **close to the ideal** speedup possible via tRCD scaling

## **GPU, Eyeriss, and TPU: Energy Evaluation**

• **<u>GPU</u>**: average **37% energy reduction**

• **Everiss**: average **31% energy reduction**

**TPU**: average **32% energy reduction**

•

## EDEN: Data-Aware Efficient DNN Inference

Skanda Koppula, Lois Orosa, A. Giray Yaglikci, Roknoddin Azizi, Taha Shahroodi, Konstantinos Kanellopoulos, and Onur Mutlu, "EDEN: Enabling Energy-Efficient, High-Performance Deep Neural Network Inference Using Approximate DRAM" Proceedings of the 52nd International Symposium on Microarchitecture (MICRO), Columbus, OH, USA, October 2019.

[Lightning Talk Slides (pptx) (pdf)]

[Lightning Talk Video (90 seconds)]

### EDEN: Enabling Energy-Efficient, High-Performance Deep Neural Network Inference Using Approximate DRAM

Skanda Koppula Lois Orosa A. Giray Yağlıkçı Roknoddin Azizi Taha Shahroodi Konstantinos Kanellopoulos Onur Mutlu ETH Zürich

## More on EDEN

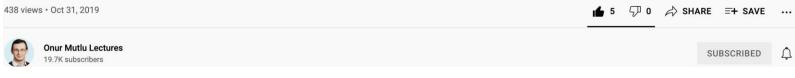

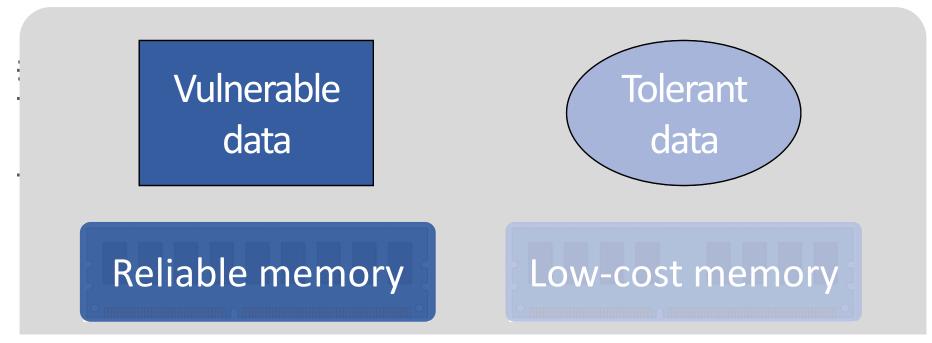

## Recall: Exploiting Memory Error Tolerance with Hybrid Memory Systems

On Microsoft's Web Search workload Reduces server hardware cost by 4.7 % Achieves single server availability target of 99.90 % Heterogeneous-Reliability Memory [DSN 2014]

# Recall: Heterogeneous-Reliability Memory

## More on Heterogeneous-Reliability Memory

Yixin Luo, Sriram Govindan, Bikash Sharma, Mark Santaniello, Justin Meza, Aman Kansal, Jie Liu, Badriddine Khessib, Kushagra Vaid, and Onur Mutlu,

"Characterizing Application Memory Error Vulnerability to Optimize

Data Center Cost via Heterogeneous-Reliability Memory"

Proceedings of the <u>44th Annual IEEE/IFIP International Conference on</u>

Dependable Systems and Networks (DSN), Atlanta, GA, June 2014. [Summary]

[Slides (pptx) (pdf)] [Coverage on ZDNet]

#### Characterizing Application Memory Error Vulnerability to Optimize Datacenter Cost via Heterogeneous-Reliability Memory

Yixin Luo Sriram Govindan<sup>\*</sup> Bikash Sharma<sup>\*</sup> Mark Santaniello<sup>\*</sup> Justin Meza Aman Kansal<sup>\*</sup> Jie Liu<sup>\*</sup> Badriddine Khessib<sup>\*</sup> Kushagra Vaid<sup>\*</sup> Onur Mutlu Carnegie Mellon University, yixinluo@cs.cmu.edu, {meza, onur}@cmu.edu \*Microsoft Corporation, {srgovin, bsharma, marksan, kansal, jie.liu, bkhessib, kvaid}@microsoft.com

## Why the Long Memory Latency?

- Reason 1: Design of DRAM Micro-architecture

- □ Goal: Maximize capacity/area, not minimize latency

- Reason 2: "One size fits all" approach to latency specification

- Same latency parameters for all temperatures

- Same latency parameters for all DRAM chips

- Same latency parameters for all parts of a DRAM chip

- Same latency parameters for all supply voltage levels

- Same latency parameters for all application data

...

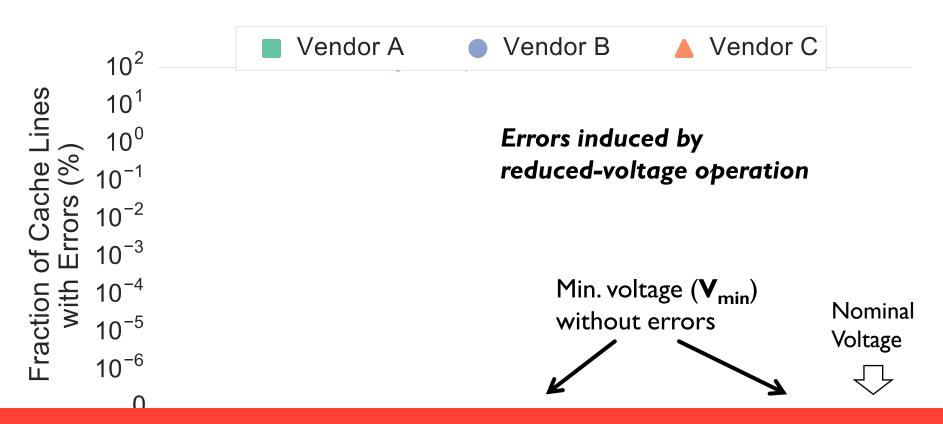

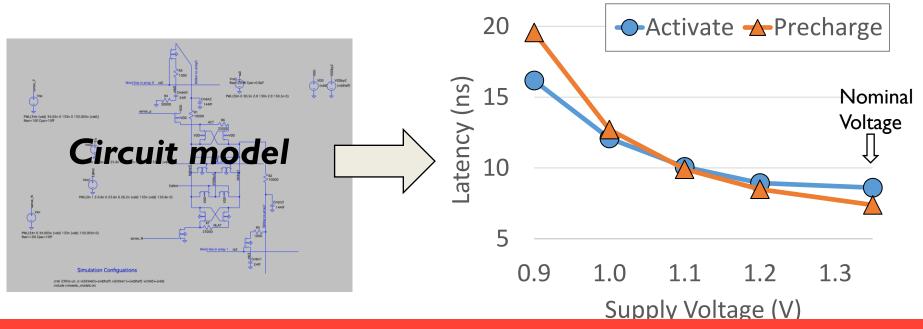

# Understanding & Exploiting the Voltage-Latency-Reliability Relationship

### Analysis of Latency-Voltage in DRAM Chips

Kevin Chang, A. Giray Yaglikci, Saugata Ghose, Aditya Agrawal, Niladrish Chatterjee, Abhijith Kashyap, Donghyuk Lee, Mike O'Connor, Hasan Hassan, and Onur Mutlu,

<u>"Understanding Reduced-Voltage Operation in Modern DRAM</u> <u>Devices: Experimental Characterization, Analysis, and</u> <u>Mechanisms"</u>

*Proceedings of the <u>ACM International Conference on Measurement and</u> <u>Modeling of Computer Systems</u> (SIGMETRICS), Urbana-Champaign, IL, USA, June 2017.*

#### Understanding Reduced-Voltage Operation in Modern DRAM Chips: Characterization, Analysis, and Mechanisms

Kevin K. Chang<sup>†</sup> Abdullah Giray Yağlıkçı<sup>†</sup> Saugata Ghose<sup>†</sup> Aditya Agrawal<sup>¶</sup> Niladrish Chatterjee<sup>¶</sup> Abhijith Kashyap<sup>†</sup> Donghyuk Lee<sup>¶</sup> Mike O'Connor<sup>¶,‡</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§,†</sup>

<sup>†</sup>Carnegie Mellon University <sup>¶</sup>NVIDIA <sup>‡</sup>The University of Texas at Austin <sup>§</sup>ETH Zürich

## **Key Questions**

How does reducing voltage affect reliability (errors)?

How does reducing voltage affect DRAM latency?

How do we design a new DRAM energy reduction mechanism?

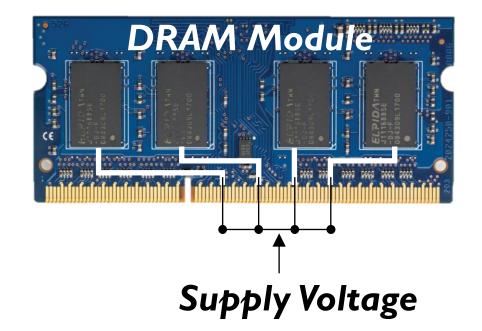

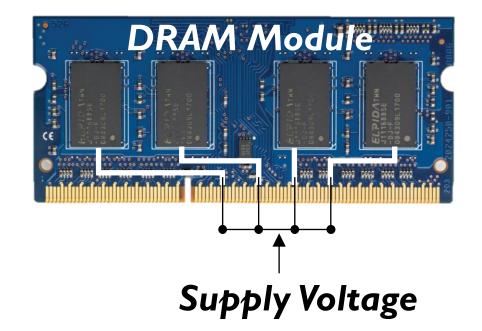

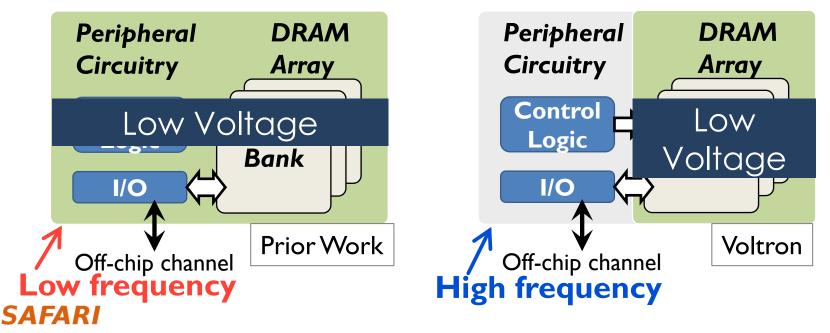

## Supply Voltage Control on DRAM

Adjust the supply voltage to every chip on the same module

#### SAFARI

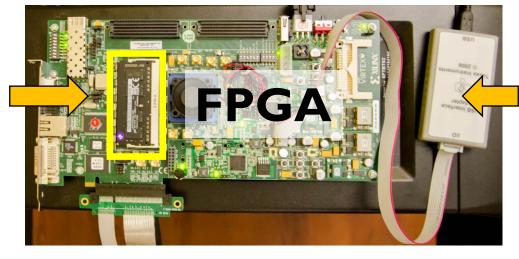

## **Custom Testing Platform**

**SoftMC** [Hassan+, HPCA'17]: FPGA testing platform to

- I) Adjust supply voltage to DRAM modules

- 2) Schedule DRAM commands to DRAM modules

Existing systems: DRAM commands not exposed to users

DRAM module

Voltage controller

https://github.com/CMU-SAFARI/DRAM-Voltage-Study

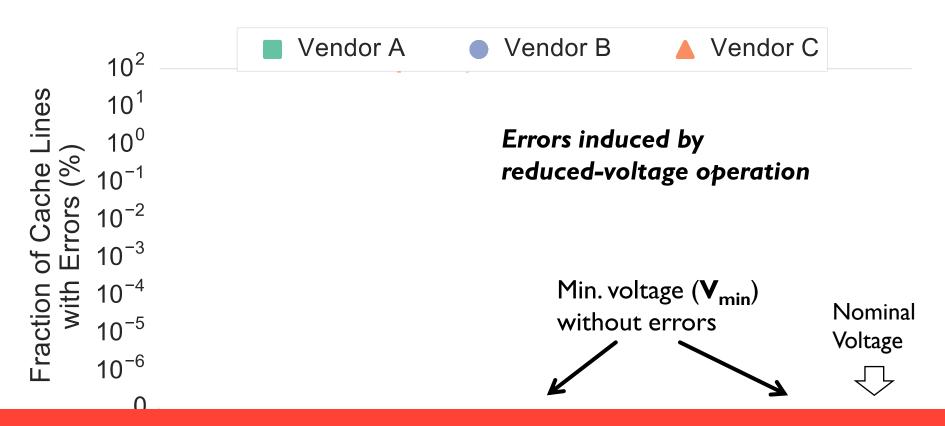

## **Tested DRAM Modules**

- **I24 DDR3L** (low-voltage) DRAM chips

- 31 SO-DIMMs

- I.35V (DDR3 uses I.5V)

- Density: 4Gb per chip

- Three major vendors/manufacturers

- Manufacturing dates: 2014-2016

- Iteratively read every bit in each 4Gb chip under a wide range of supply voltage levels: 1.35V to 1.0V (-26%)

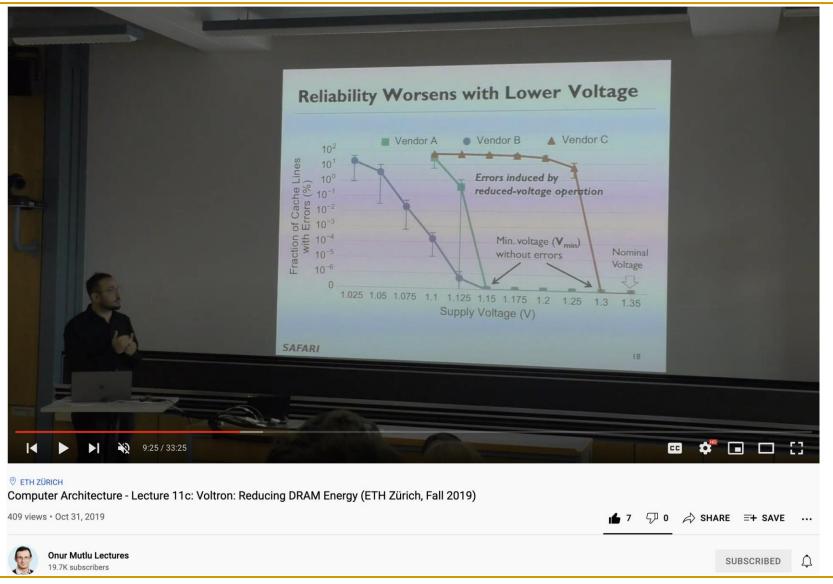

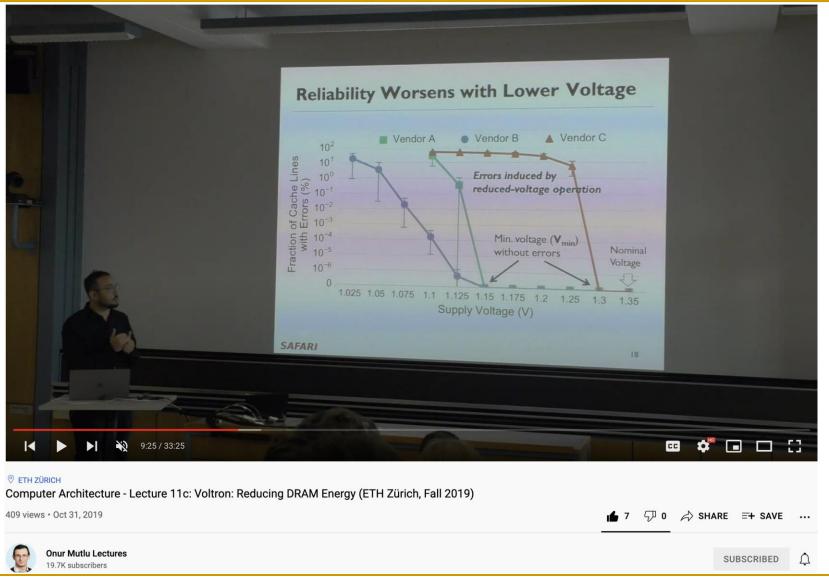

#### **Reliability Worsens with Lower Voltage**

Reducing voltage below V<sub>min</sub> causes an increasing number of errors

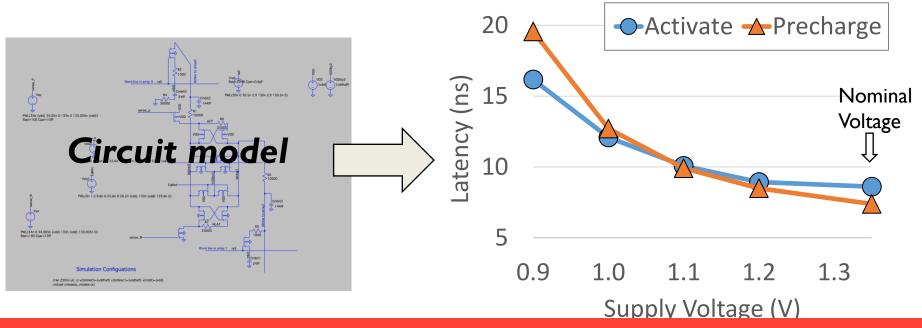

## **Source of Errors**

Detailed circuit simulations (SPICE) of a DRAM cell array to model the behavior of DRAM operations <u>https://github.com/CMU-SAFARI/DRAM-Voltage-Study</u>

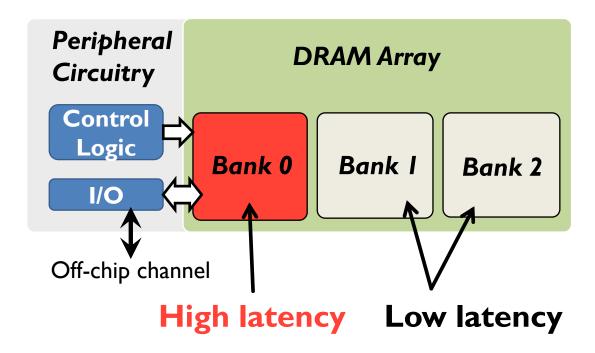

Reliable low-voltage operation requires higher latency

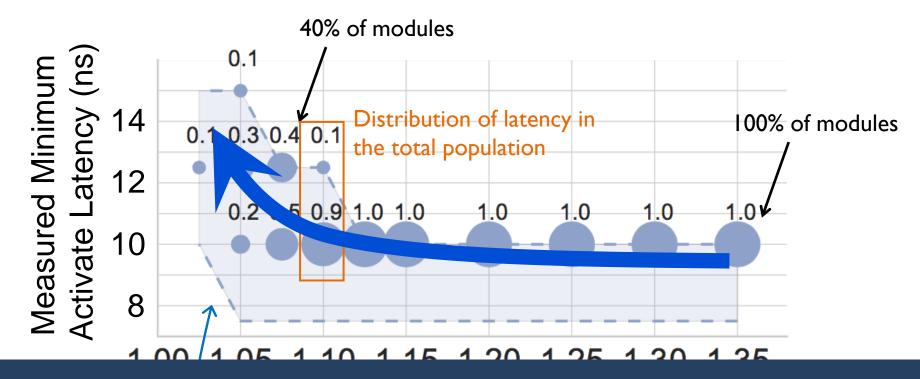

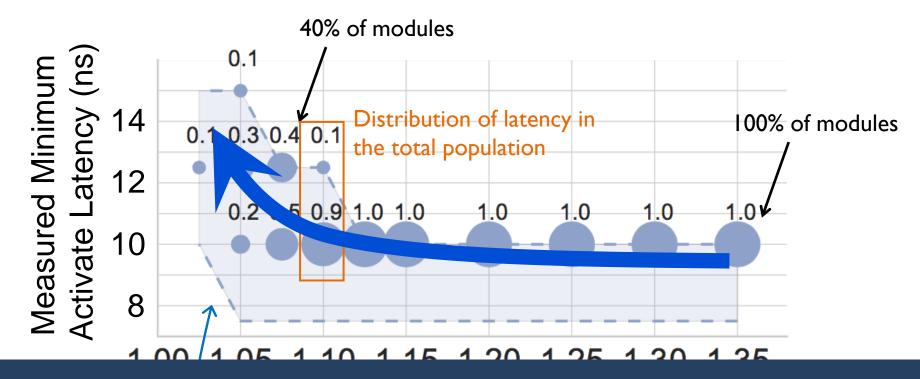

# **DIMMs Operating at Higher Latency**

Measured minimum latency that does not cause errors in DRAM modules

DRAM requires longer latency to access data without errors at lower voltage

#### SAFARI

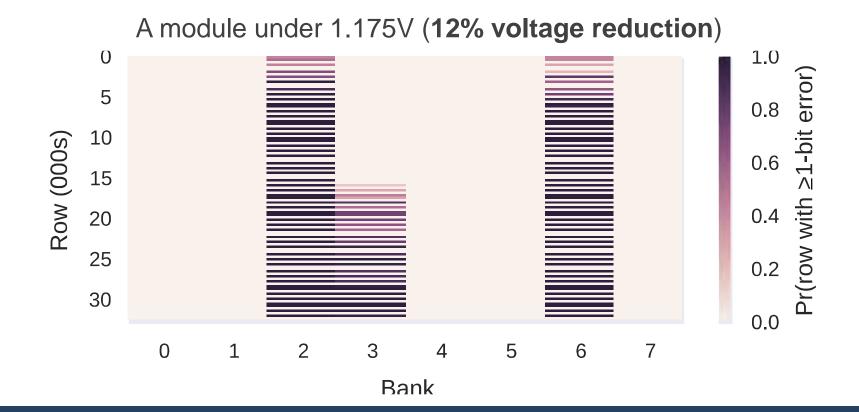

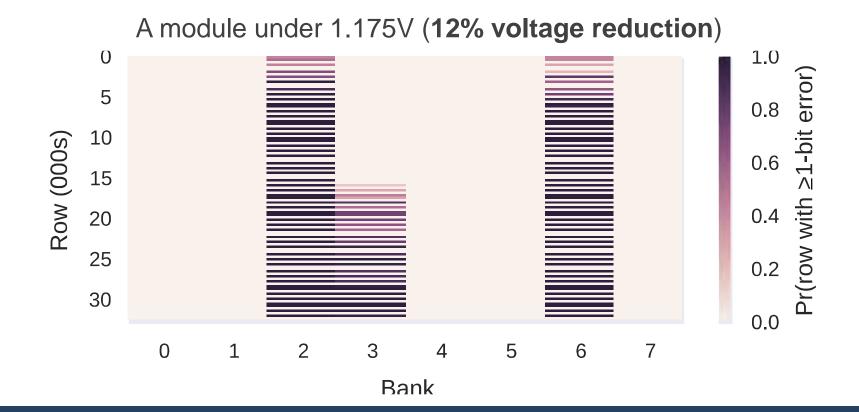

## **Spatial Locality of Errors**

Errors concentrate in certain regions

#### SAFARI

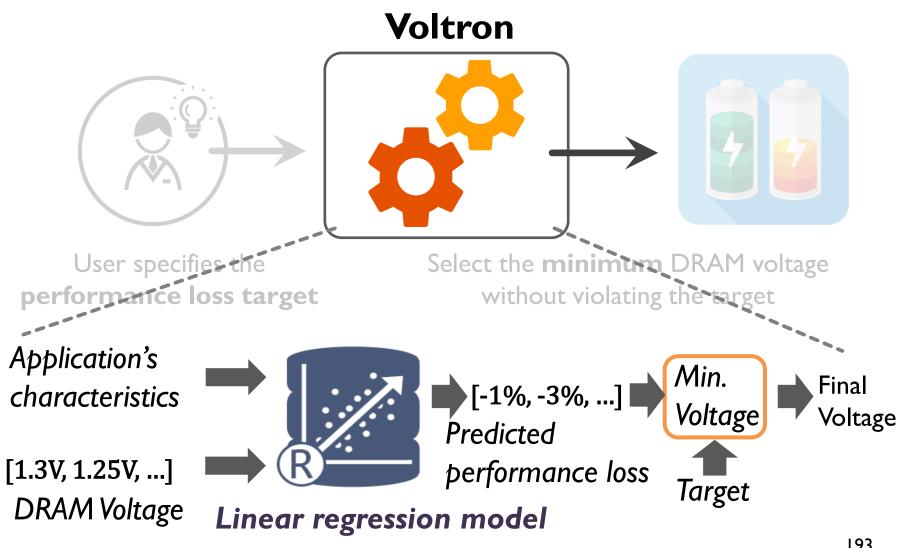

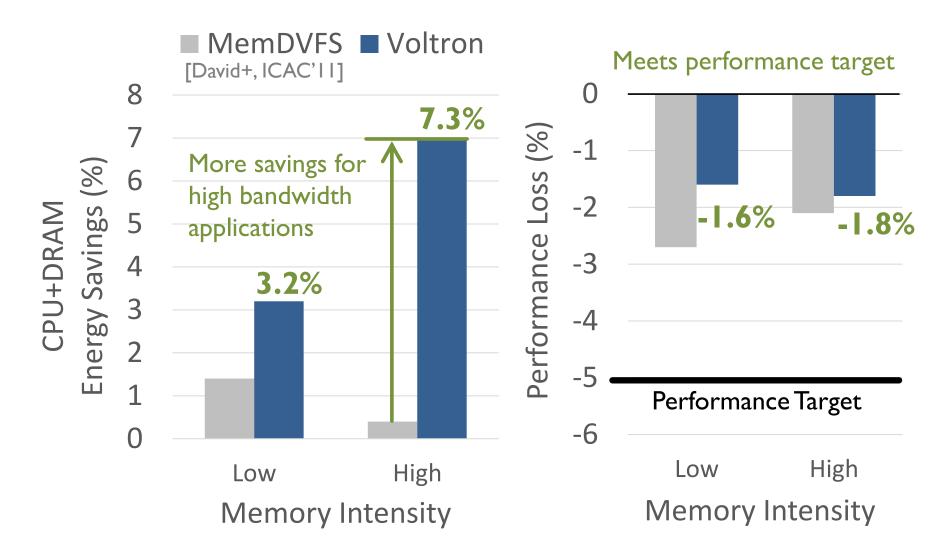

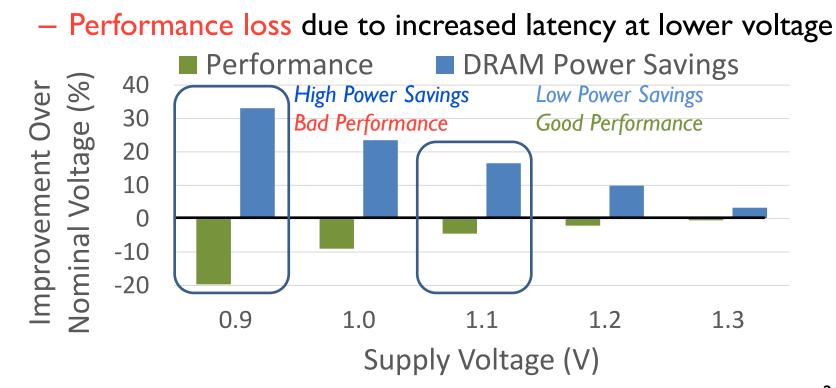

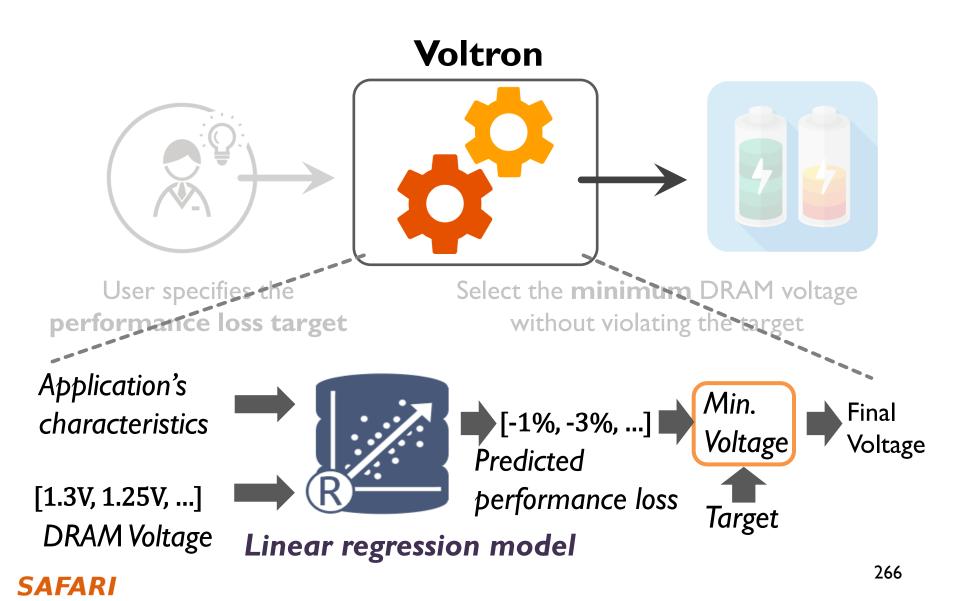

## **Voltron Overview**

User specifies the **performance loss target**

Select the **minimum** DRAM voltage without violating the target

# How do we predict performance loss due to increased latency under low DRAM voltage?

#### Linear Model to Predict Performance

#### SAFARI

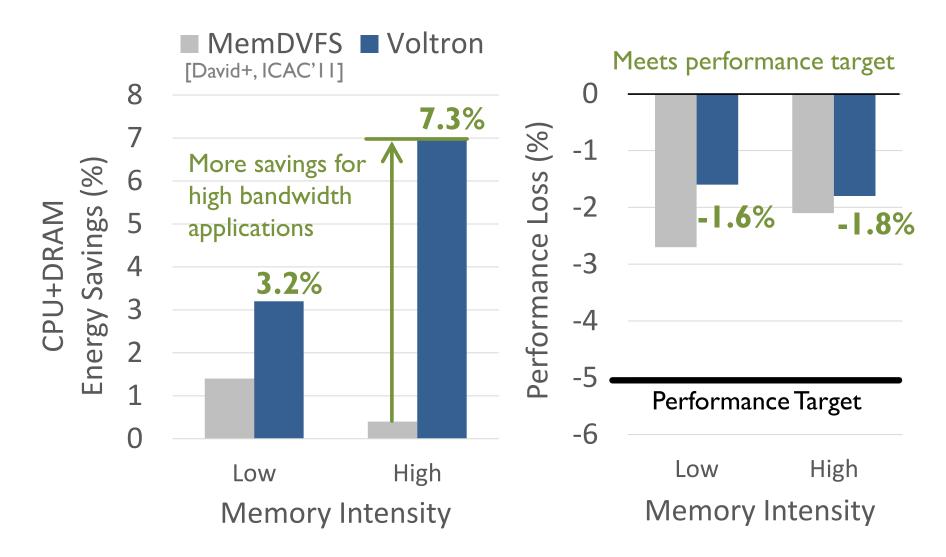

#### **Energy Savings with Bounded Performance**

#### Advantages

+ Can trade-off between voltage and latency to improve energy or performance

+ Can exploit the high voltage margin present in DRAM

#### Disadvantages

- Requires finding the reliable operating voltage for each chip  $\rightarrow$  higher testing cost

- More complicated memory controller

#### More on Voltron

SAFARI

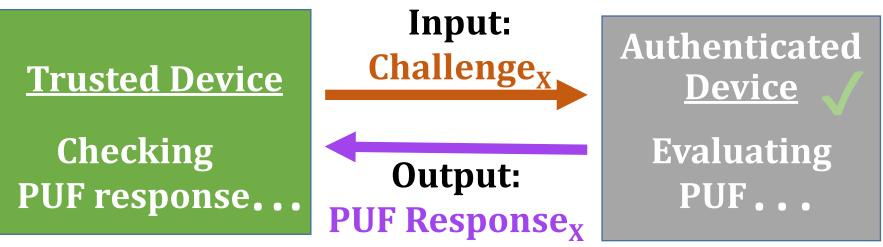

# Reducing Memory Latency to Support Security Primitives

## Using Memory for Security

- Generating True Random Numbers (using DRAM)

- Kim et al., HPCA 2019

- Olgun et al., ISCA 2021

Evaluating Physically Unclonable Functions (using DRAM)

Kim et al., HPCA 2018

Quickly Destroying In-Memory Data (using DRAM)

Orosa et al., arxiv 2019 + ISCA 2021

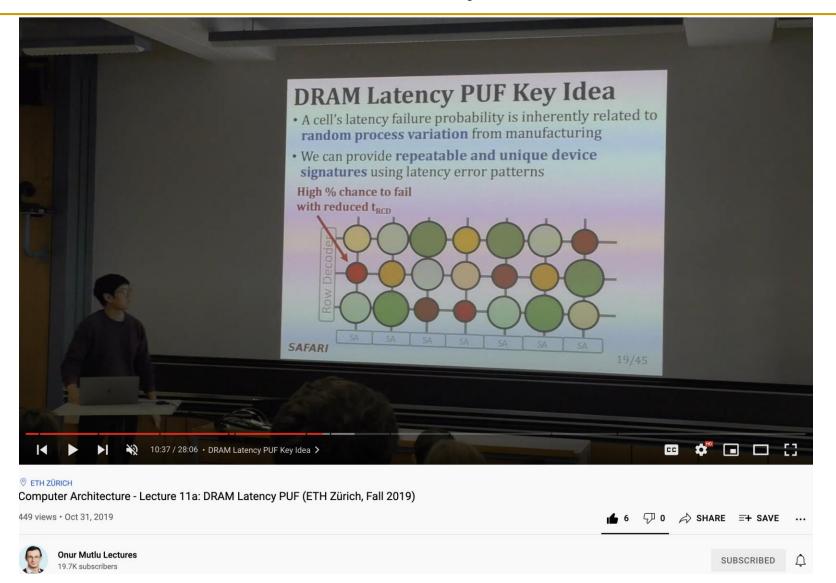

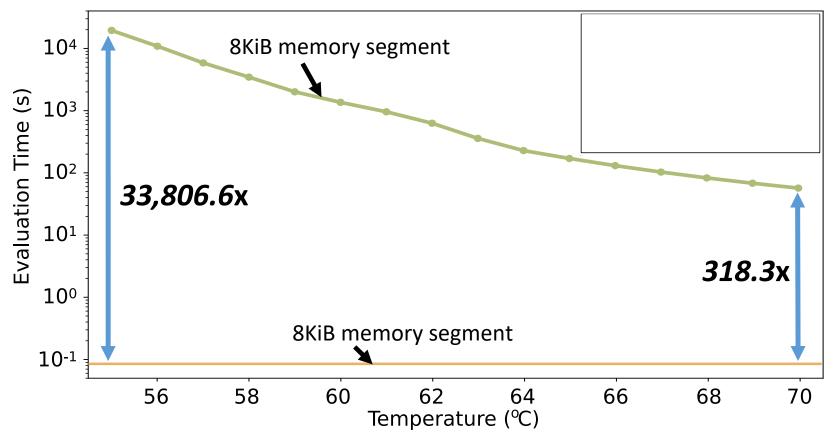

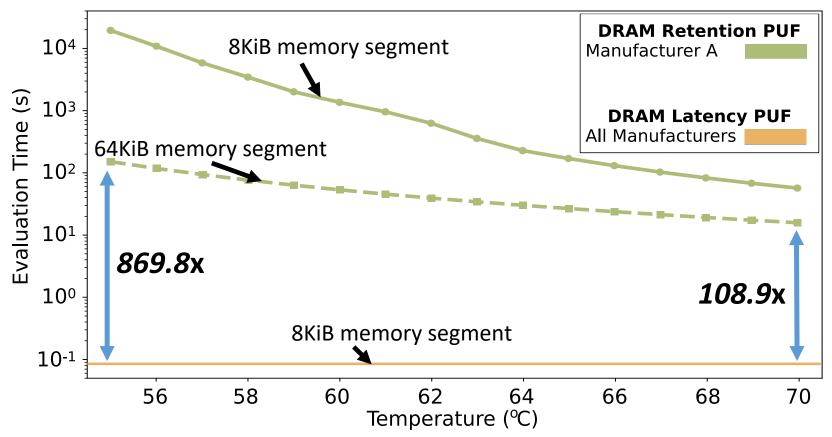

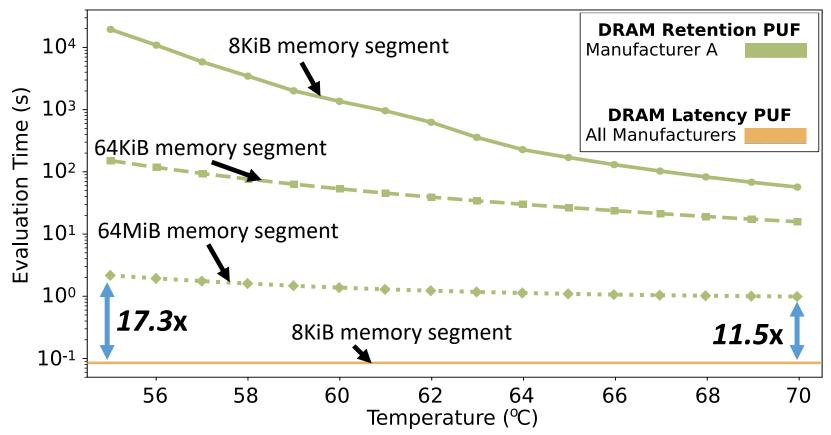

## DRAM Latency PUFs

Jeremie S. Kim, Minesh Patel, Hasan Hassan, and Onur Mutlu, "The DRAM Latency PUF: Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern DRAM <u>Devices"</u> Proceedings of the <u>24th International Symposium on High-Performance Computer</u> <u>Architecture</u> (HPCA), Vienna, Austria, February 2018. [Lightning Talk Video] [Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

[Full Talk Lecture Video (28 minutes)]

#### The DRAM Latency PUF:

#### Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern Commodity DRAM Devices

Jeremie S. Kim<sup>†§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§†</sup> <sup>†</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

### More on DRAM Latency PUFs

SAFARI

200

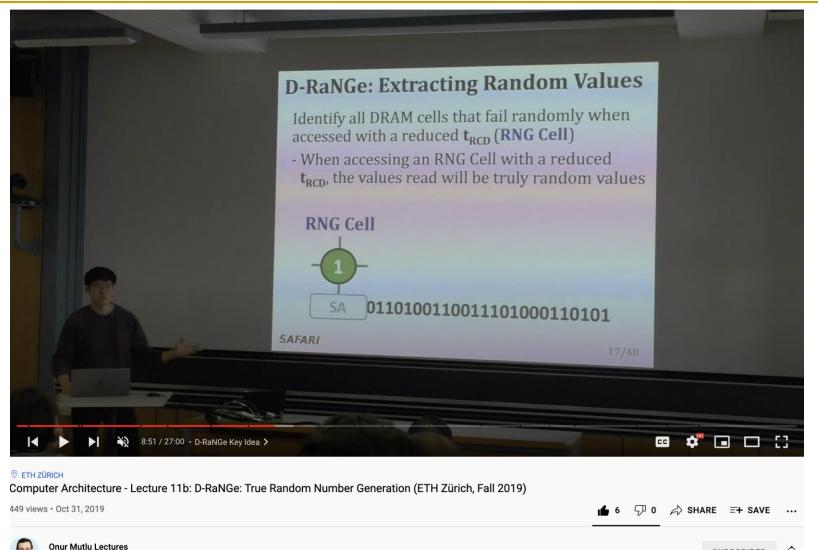

#### DRAM Latency True Random Number Generator

Jeremie S. Kim, Minesh Patel, Hasan Hassan, Lois Orosa, and Onur Mutlu, "D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput" Proceedings of the 25th International Symposium on High-Performance Computer Architecture (HPCA), Washington, DC, USA, February 2019. [Slides (pptx) (pdf)] [Full Talk Video (21 minutes)] [Full Talk Lecture Video (27 minutes)] Top Picks Honorable Mention by IEEE Micro.

#### D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

Jeremie S. Kim<sup>‡§</sup>

Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§‡</sup> <sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

#### Jeremie S. Kim Minesh Patel Hasan Hassan Lois Orosa Onur Mutlu HPCA 2019 SAFARI

# **D-RaNGe Executive Summary**

- <u>Motivation</u>: High-throughput true random numbers enable system security and various randomized algorithms.

- Many systems (e.g., IoT, mobile, embedded) do not have dedicated True Random Number Generator (TRNG) hardware but have DRAM devices

- **<u>Problem</u>**: Current DRAM-based TRNGs either

- 1. do **not** sample a fundamentally non-deterministic entropy source

- 2. are **too slow** for continuous high-throughput operation

- <u>Goal</u>: A novel and effective TRNG that uses existing commodity DRAM to provide random values with 1) high-throughput, 2) low latency and 3) no adverse effect on concurrently running applications

- **<u>D-RaNGe</u>**: Reduce DRAM access latency **below reliable values** and exploit DRAM cells' failure probabilities to generate random values

- Evaluation:

- 1. Experimentally characterize **282 real LPDDR4 DRAM devices**

- 2. **D-RaNGe (717.4 Mb/s)** has significantly higher throughput **(211x)**

- 3. **D-RaNGe (100ns)** has significantly lower latency **(180x) SAFARI**

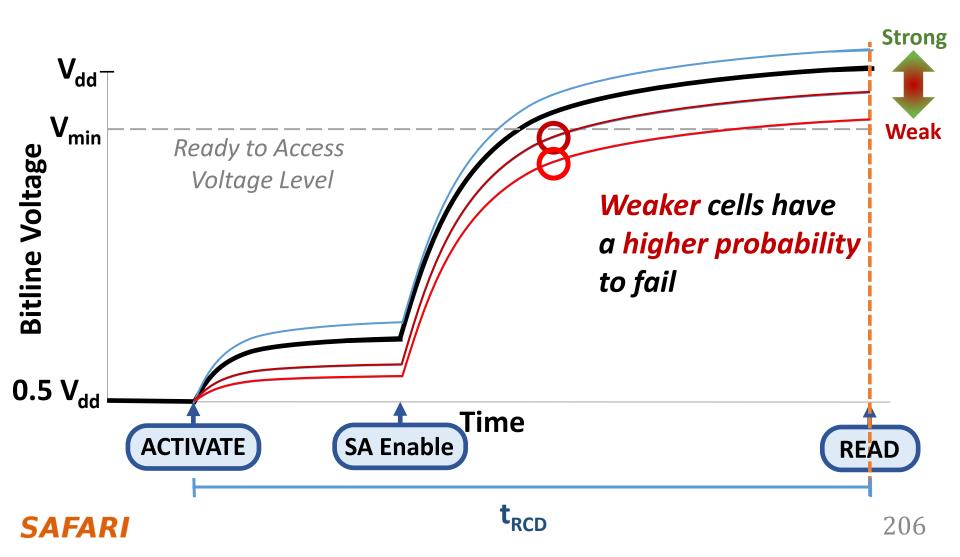

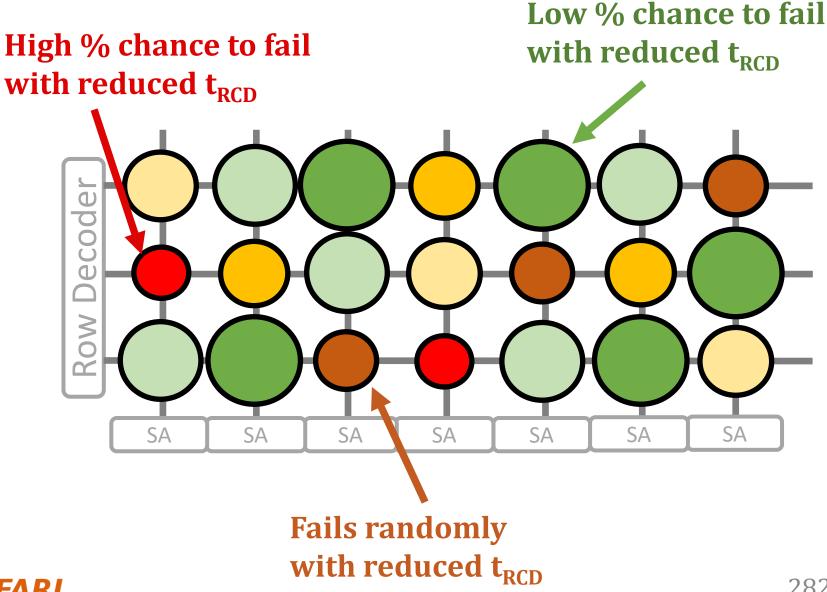

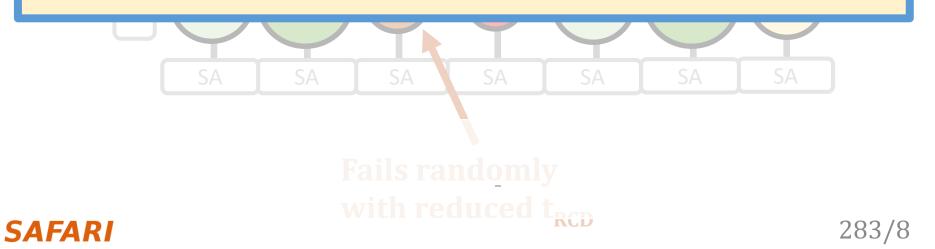

# DRAM Latency Characterization of 282 LPDDR4 DRAM Devices

• Latency failures come from accessing DRAM with **reduced** timing parameters.

- Key Observations:

- 1. A cell's **latency failure** probability is determined by **random process variation**

- 2. Some cells fail **randomly**

# **DRAM Accesses and Failures**

# **DRAM Accesses and Failures**

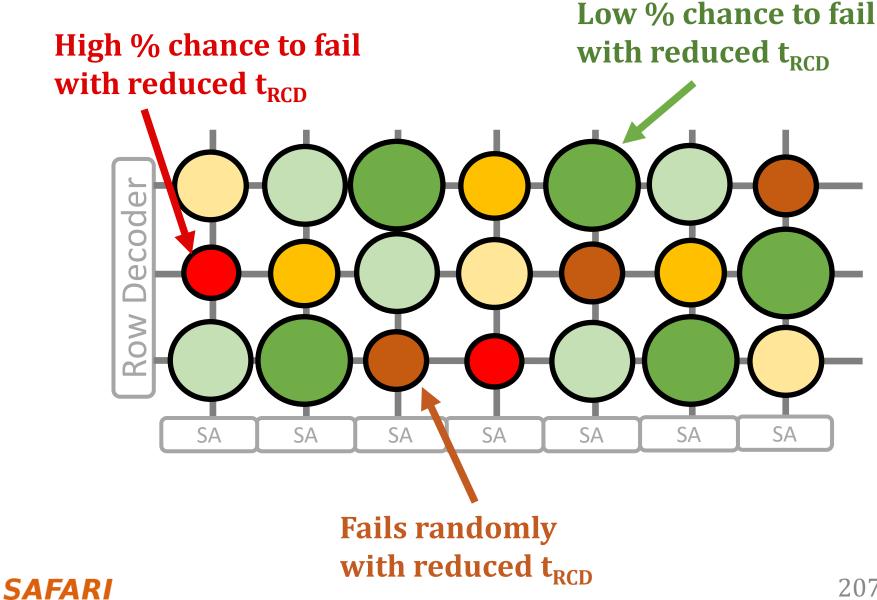

# **D-RaNGe Key Idea**

# **D-RaNGe Key Idea**

High % chance to fail with reduced t<sub>RCD</sub>

Low % chance to fail with reduced t<sub>RCD</sub>

#### We refer to cells that fail randomly when accessed with a reduced t<sub>RCD</sub> as RNG cells

# **Our D-RaNGe Evaluation**

- We generate random values by repeatedly accessing RNG cells and aggregating the data read

- The random data satisfies the NIST statistical test suite for randomness

- The **D-RaNGE** generates random numbers

- Throughput: 717.4 Mb/s

- **Latency**: 64 bits in <1us

- Power: 4.4 nJ/bit

#### SAFARI

D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

#### <u>Jeremie S. Kim</u> Minesh Patel Hasan Hassan Lois Orosa Onur Mutlu

# SAFARI HPCA 2019

**Carnegie Mellon**

#### More on D-RaNGe

Jeremie S. Kim, Minesh Patel, Hasan Hassan, Lois Orosa, and Onur Mutlu, "D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput" Proceedings of the 25th International Symposium on High-Performance Computer Architecture (HPCA), Washington, DC, USA, February 2019. [Slides (pptx) (pdf)] [Full Talk Video (21 minutes)] [Full Talk Lecture Video (27 minutes)] Top Picks Honorable Mention by IEEE Micro.

#### D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

Jeremie S. Kim<sup>‡§</sup>

Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§‡</sup> <sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

### More on DRAM Latency TRNGs

19.7K subscribers

SAFARI

SUBSCRIBED

https://www.youtube.com/watch?v=Y3hPv1I5f8Y&list=PL5Q2soXY2Zi-DyoI3HbqcdtUm9YWRR\_z-&index=16

#### In-DRAM True Random Number Generation

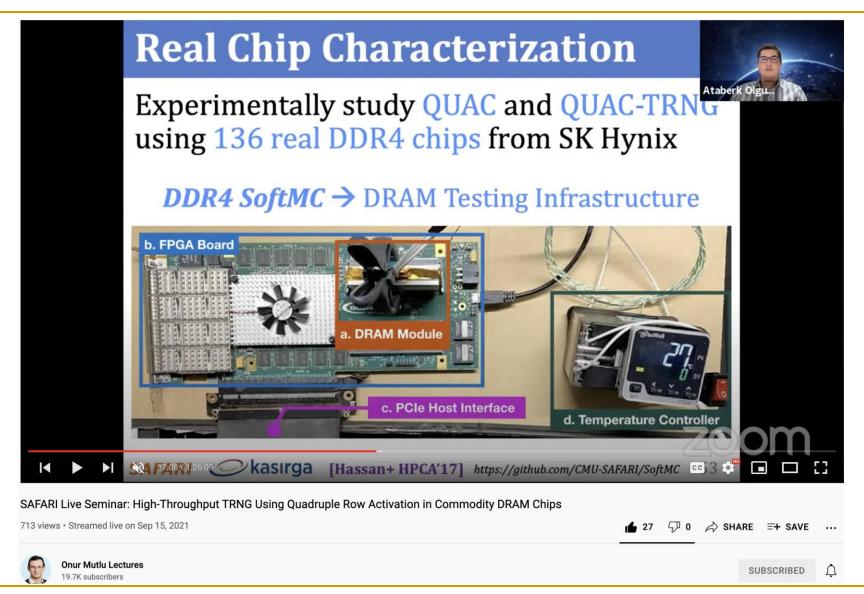

Ataberk Olgun, Minesh Patel, A. Giray Yaglikci, Haocong Luo, Jeremie S. Kim, F. Nisa Bostanci, Nandita Vijaykumar, Oguz Ergin, and Onur Mutlu, "QUAC-TRNG: High-Throughput True Random Number Generation Using Quadruple Row Activation in Commodity DRAM Chips" Proceedings of the <u>48th International Symposium on Computer Architecture</u> (ISCA), Virtual, June 2021.

[Slides (pptx) (pdf)]

[Short Talk Slides (pptx) (pdf)]

[Talk Video (25 minutes)]

[SAFARI Live Seminar Video (1 hr 26 mins)]

#### QUAC-TRNG: High-Throughput True Random Number Generation Using Quadruple Row Activation in Commodity DRAM Chips

Ataberk OlgunMinesh PatelA. Giray YağlıkçıHaocong LuoJeremie S. KimF. Nisa BostancıNandita VijaykumarOğuz ErginOnur Mutlu§ETH Zürich†TOBB University of Economics and TechnologyOUniversity of Toronto

## More on QUAC-TRNG

SAFARI

https://www.youtube.com/watch?v=snvF3g3GfkI&list=PL5Q2soXY2Zi\_tOTAYm--dYByNPL7JhwR9&index=6

# Reducing Refresh Latency

## Reducing Refresh Latency

Anup Das, Hasan Hassan, and Onur Mutlu, "VRL-DRAM: Improving DRAM Performance via Variable Refresh Latency" Proceedings of the <u>55th Design Automation</u> <u>Conference</u> (DAC), San Francisco, CA, USA, June 2018.

#### VRL-DRAM: Improving DRAM Performance via Variable Refresh Latency

Anup Das Drexel University Philadelphia, PA, USA anup.das@drexel.edu Hasan Hassan ETH Zürich Zürich, Switzerland hhasan@ethz.ch Onur Mutlu ETH Zürich Zürich, Switzerland omutlu@gmail.com

#### SAFARI

## Reducing Memory Latency by Exploiting Memory Access Patterns

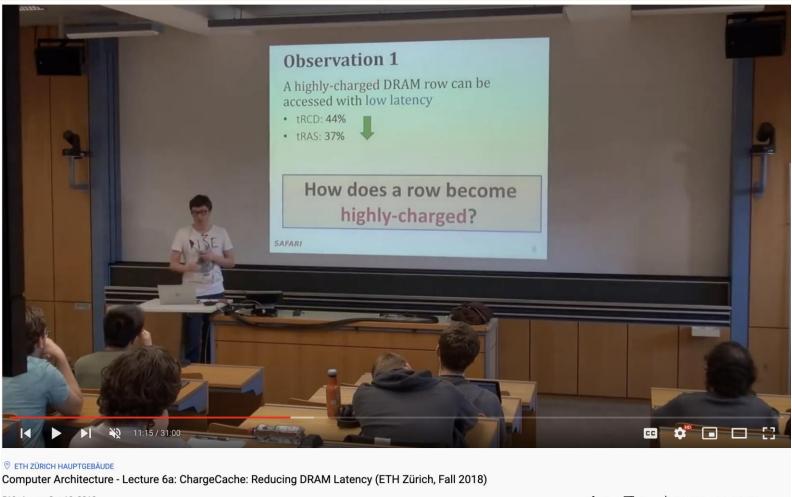

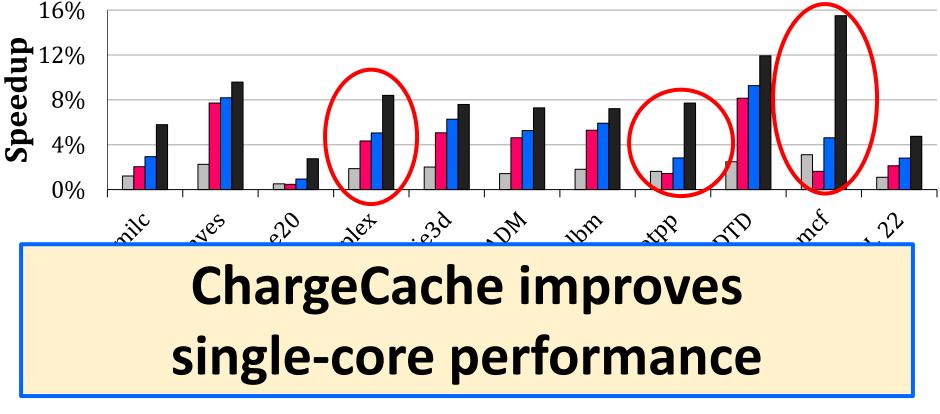

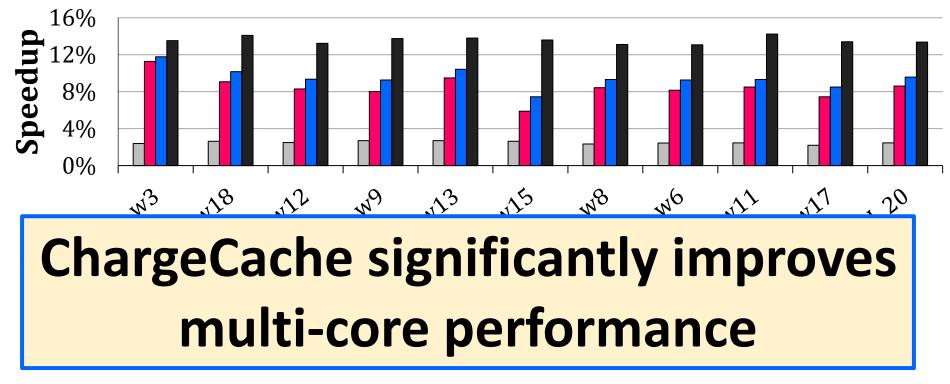

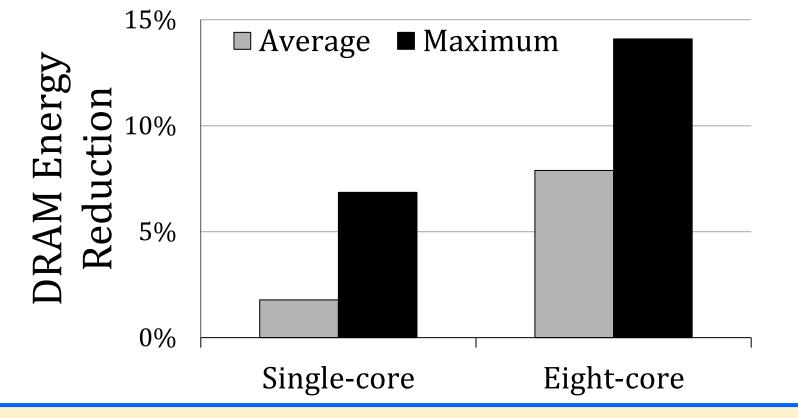

## ChargeCache: Exploiting Access Patterns

Hasan Hassan, Gennady Pekhimenko, Nandita Vijaykumar, Vivek Seshadri, Donghyuk Lee, Oguz Ergin, and Onur Mutlu, "ChargeCache: Reducing DRAM Latency by Exploiting Row Access Locality" Proceedings of the <u>22nd International Symposium on High-</u>

*Performance Computer Architecture (HPCA)*, Barcelona, Spain, March 2016. [<u>Slides (pptx) (pdf)</u>] [<u>Source Code</u>]

### ChargeCache: Reducing DRAM Latency by Exploiting Row Access Locality

Hasan Hassan<sup>†</sup>\*, Gennady Pekhimenko<sup>†</sup>, Nandita Vijaykumar<sup>†</sup> Vivek Seshadri<sup>†</sup>, Donghyuk Lee<sup>†</sup>, Oguz Ergin<sup>\*</sup>, Onur Mutlu<sup>†</sup>

<sup>†</sup>*Carnegie Mellon University*

\* TOBB University of Economics & Technology

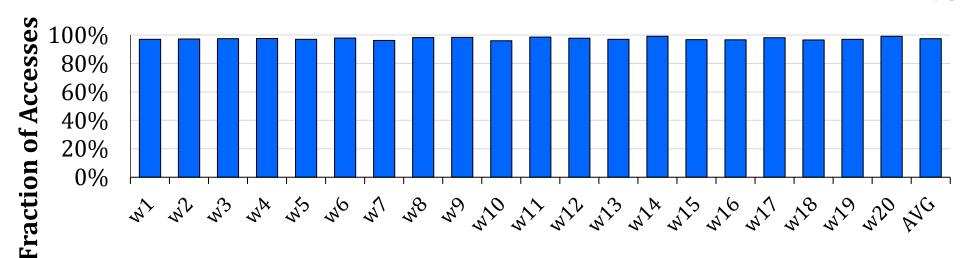

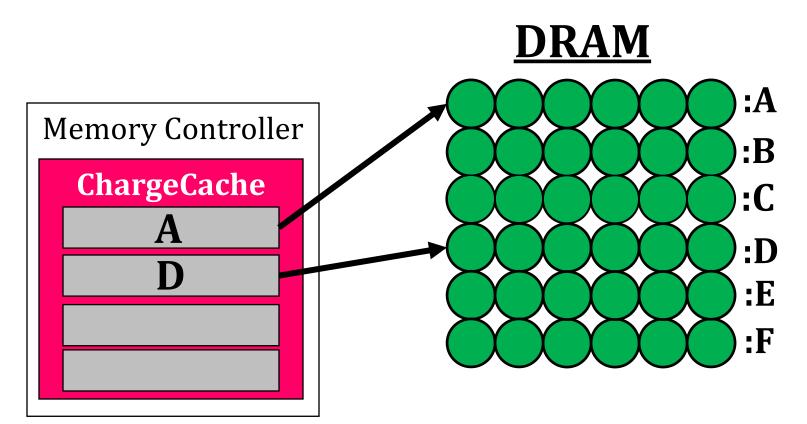

## ChargeCache: Executive Summary

• <u>**Goal</u>**: Reduce average DRAM access latency with no modification to the existing DRAM chips</u>

#### Observations:

- 1) A highly-charged DRAM row can be accessed with low latency

- 2) A row's charge is restored when the row is accessed

- A recently-accessed row is likely to be accessed again:

Row Level Temporal Locality (RLTL)

- <u>Key Idea</u>: Track recently-accessed DRAM rows and use lower timing parameters if such rows are accessed again

#### • <u>ChargeCache:</u>

- Low cost & no modifications to the DRAM

- Higher performance (**8.6-10.6%** on average for 8-core)

- Lower DRAM energy (7.9% on average)

#### SAFARI

## More on ChargeCache

SAFARI

220

## Partial Restoration of Cell Charge

- Yaohua Wang, Arash Tavakkol, Lois Orosa, Saugata Ghose, Nika Mansouri Ghiasi, Minesh Patel, Jeremie S. Kim, Hasan Hassan, Mohammad Sadrosadati, and Onur Mutlu,

- <u>"Reducing DRAM Latency via Charge-Level-Aware Look-Ahead</u> Partial Restoration"

Proceedings of the <u>51st International Symposium on</u> <u>Microarchitecture</u> (**MICRO**), Fukuoka, Japan, October 2018.

#### Reducing DRAM Latency via Charge-Level-Aware Look-Ahead Partial Restoration

Yaohua Wang<sup>†§</sup> Arash Tavakkol<sup>†</sup> Lois Orosa<sup>†\*</sup> Saugata Ghose<sup>‡</sup> Nika Mansouri Ghiasi<sup>†</sup> Minesh Patel<sup>†</sup> Jeremie S. Kim<sup>‡†</sup> Hasan Hassan<sup>†</sup> Mohammad Sadrosadati<sup>†</sup> Onur Mutlu<sup>†‡</sup>

> <sup>†</sup>ETH Zürich <sup>§</sup>National University of Defense Technology <sup>‡</sup>Carnegie Mellon University <sup>\*</sup>University of Campinas

#### SAFARI

## Parallelizing Refreshes and Accesses

Kevin Chang, Donghyuk Lee, Zeshan Chishti, Alaa Alameldeen, Chris Wilkerson, Yoongu Kim, and Onur Mutlu,

"Improving DRAM Performance by Parallelizing Refreshes with Accesses"

Proceedings of the <u>20th International Symposium on High-Performance</u> <u>Computer Architecture</u> (HPCA), Orlando, FL, February 2014.

[Summary] [Slides (pptx) (pdf)]

#### Reducing Performance Impact of DRAM Refresh by Parallelizing Refreshes with Accesses

Kevin Kai-Wei Chang Donghyuk Lee Zeshan Chishti† Alaa R. Alameldeen† Chris Wilkerson† Yoongu Kim Onur Mutlu Carnegie Mellon University †Intel Labs

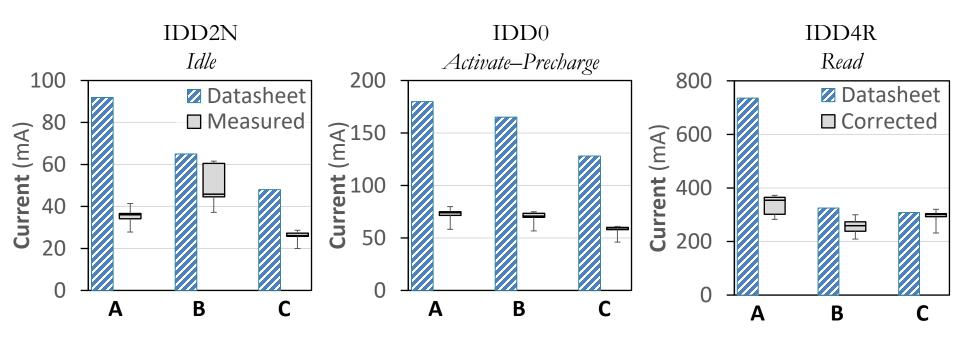

# On DRAM Power Consumption

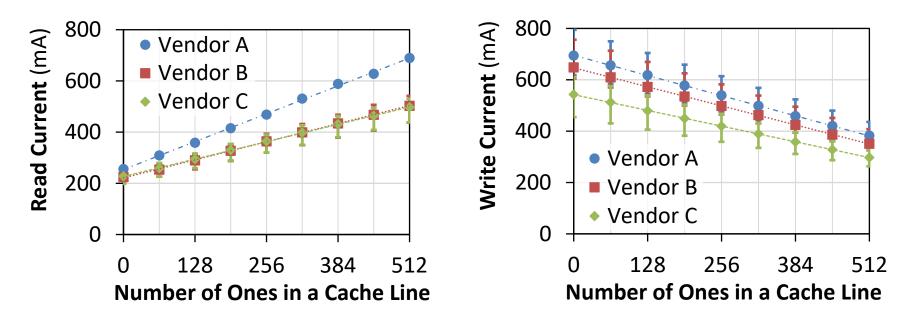

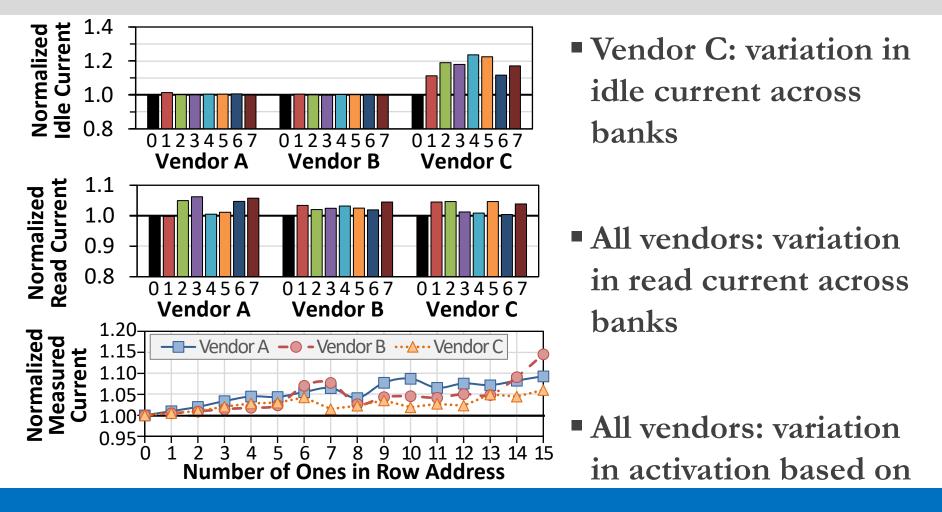

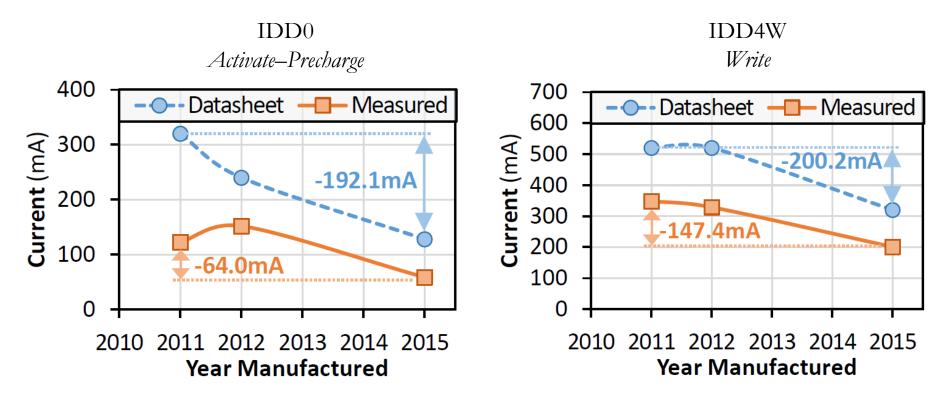

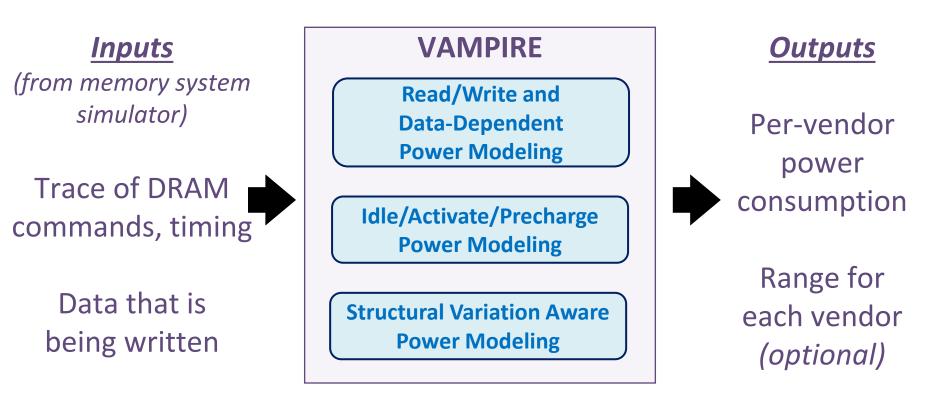

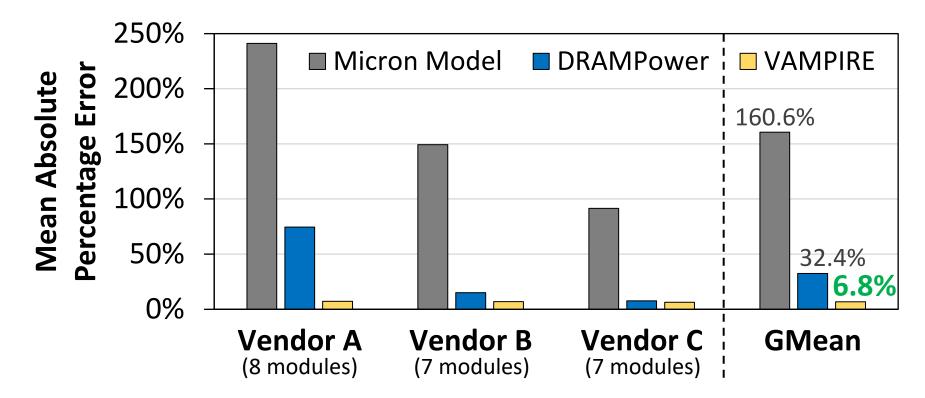

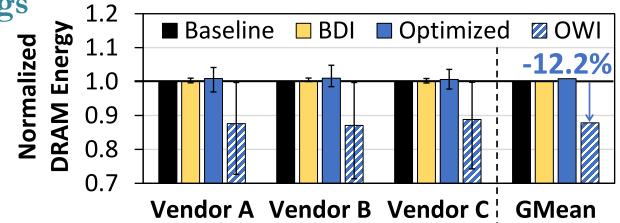

## VAMPIRE DRAM Power Model

Saugata Ghose, A. Giray Yaglikci, Raghav Gupta, Donghyuk Lee, Kais Kudrolli, William X. Liu, Hasan Hassan, Kevin K. Chang, Niladrish Chatterjee, Aditya Agrawal, Mike O'Connor, and Onur Mutlu,

"What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study"

Proceedings of the <u>ACM International Conference on Measurement and Modeling of</u> <u>Computer Systems</u> (SIGMETRICS), Irvine, CA, USA, June 2018.

[Abstract]

[POMACS Journal Version (same content, different format)]

[Slides (pptx) (pdf)]

VAMPIRE DRAM Power Model

#### What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study

Saugata Ghose<sup>†</sup> Abdullah Giray Yağlıkçı<sup>‡†</sup> Raghav Gupta<sup>†</sup> Donghyuk Lee<sup>§</sup> Kais Kudrolli<sup>†</sup> William X. Liu<sup>†</sup> Hasan Hassan<sup>‡</sup> Kevin K. Chang<sup>†</sup> Niladrish Chatterjee<sup>§</sup> Aditya Agrawal<sup>§</sup> Mike O'Connor<sup>§¶</sup> Onur Mutlu<sup>‡†</sup> <sup>†</sup>Carnegie Mellon University <sup>‡</sup>ETH Zürich <sup>§</sup>NVIDIA <sup>¶</sup>University of Texas at Austin

### Power Measurement Platform

The second second

5858

1111 2010 2 015 J 268.

SAFARI

Virtex 6 FPGA

## Summary: Low-Latency Memory

Challenge and Opportunity for Future

# Fundamentally Low Latency Computing Architectures

## Summary: Tackling Long Memory Latency

- Reason 1: Design of DRAM Micro-architecture

- Goal: Maximize capacity/area, not minimize latency

- Reason 2: "One size fits all" approach to latency specification

- Same latency parameters for all temperatures

- □ Same latency parameters for all DRAM chips (e.g., rows)

- □ Same latency parameters for all parts of a DRAM chip

- Same latency parameters for all supply voltage levels

- Same latency parameters for all application data

]...

# We Can Reduce Memory Latency with Change of Mindset

# Main Memory Needs Intelligent Controllers to Reduce Latency

## Some Solution Principles

- Data-centric design

- All components intelligent

- Better cross-layer communication, better interfaces

- Better-than-worst-case design

- Heterogeneity

- Flexibility, adaptability

## Four Key Current Directions

Fundamentally Secure/Reliable/Safe Architectures

Fundamentally Energy-Efficient Architectures

Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency and Predictable Architectures

Architectures for AI/ML, Genomics, Medicine, Health, ...

#### SAFARI

# We Stopped Here in Lecture. Remaining Slides are For Future.

## **Computer Architecture** Lecture 8b: Memory Latency

Prof. Onur Mutlu ETH Zürich Fall 2022 21 October 2022

## **Backup Slides**

## Solar-DRAM

## Solar-DRAM: Putting It Together

Jeremie S. Kim, Minesh Patel, Hasan Hassan, and Onur Mutlu, "Solar-DRAM: Reducing DRAM Access Latency by <u>Exploiting the Variation in Local Bitlines</u>" *Proceedings of the <u>36th IEEE International Conference on</u> <u>Computer Design</u> (ICCD), Orlando, FL, USA, October 2018. [Slides (pptx) (pdf)] [Talk Video (16 minutes)]*

## Solar-DRAM: Reducing DRAM Access Latency by Exploiting the Variation in Local Bitlines

Jeremie S. Kim<sup>‡§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§‡</sup> <sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

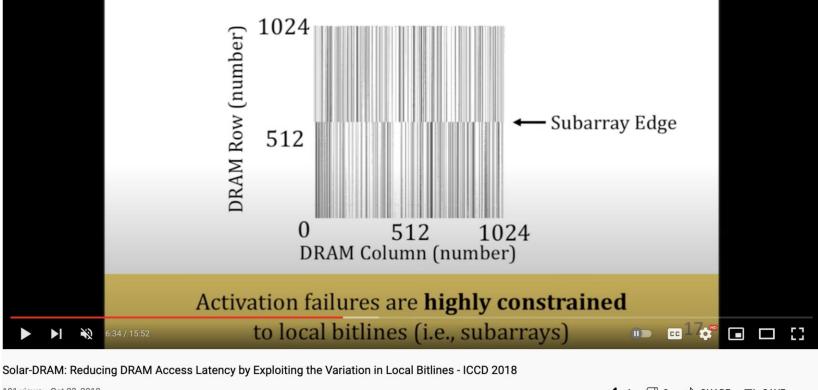

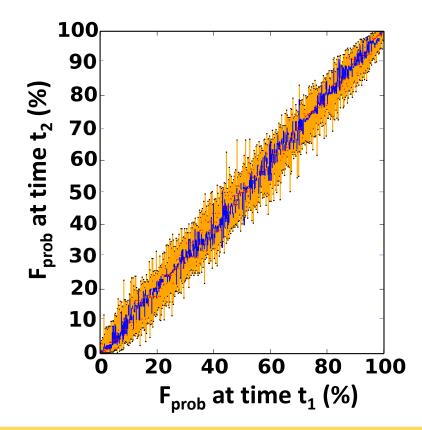

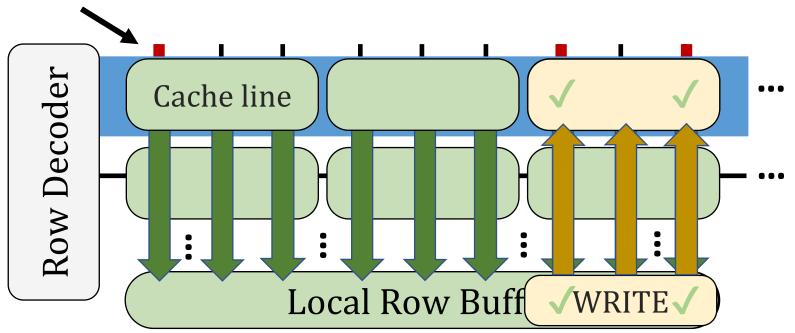

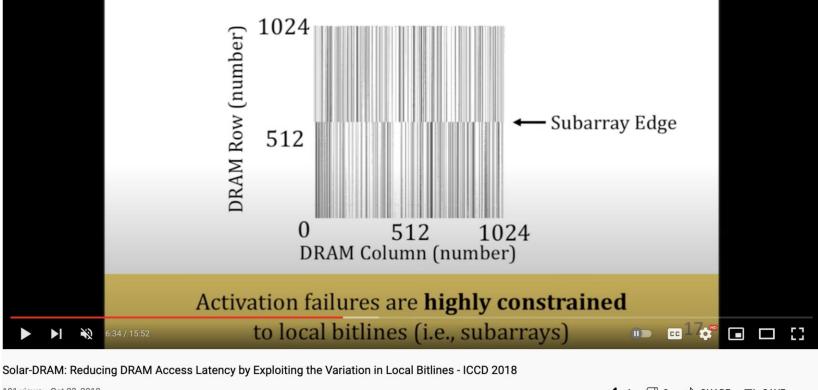

# **Spatial Distribution of Failures**

How are activation failures spatially distributed in DRAM?

Activation failures are **highly constrained** to local bitlines

## **Short-term Variation**

Does a bitline's probability of failure change over time?

A **weak bitline** is likely to remain **weak** and a **strong bitline** is likely to remain **strong** over time

## **Short-term Variation**

Does a bitline's probability of failure change over time?

We can rely on a **static profile** of weak bitlines to determine whether an access will cause failures

A **weak bitline** is likely to remain **weak** and a **strong bitline** is likely to remain **strong** over time

# Write Operations

How are write operations affected by reduced  $\mathbf{t}_{RCD}$ ?

#### Weak bitline

We can reliably issue write operations with significantly reduced **t<sub>RCD</sub>** (e.g., by 77%)

241

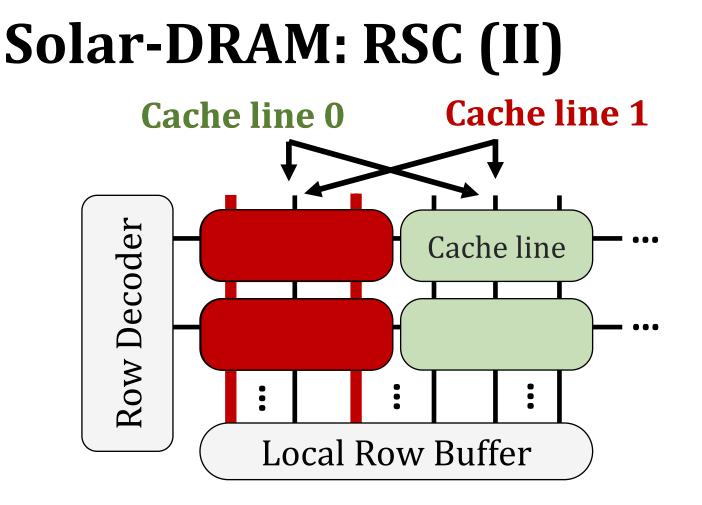

# **Solar-DRAM**

#### Uses a static profile of weak subarray columns

- Identifies subarray columns as weak or strong

- Obtained in a one-time profiling step

#### **Three Components**

- 1. Variable-latency cache lines (VLC)

- 2. Reordered subarray columns (RSC)

- 3. Reduced latency for writes (RLW)

# **Solar-DRAM**

#### Uses a static profile of weak subarray columns

- Identifies subarray columns as weak or strong

- Obtained in a one-time profiling step

#### **Three Components**

- 1. Variable-latency cache lines (VLC)

- 2. Reordered subarray columns (RSC)

- 3. Reduced latency for writes (RLW)

# Solar-DRAM: VLC (I)

Identify cache lines comprised of **strong bitlines** Access such cache lines with a **reduced t<sub>RCD</sub>**

# **Solar-DRAM**

#### Uses a static profile of weak subarray columns

- Identifies subarray columns as weak or strong

- Obtained in a one-time profiling step

#### **Three Components**

- 1. Variable-latency cache lines (VLC)

- 2. Reordered subarray columns (RSC)

- 3. Reduced latency for writes (RLW)

**Remap cache lines** across DRAM at the memory controller level so cache line 0 will likely map to a **strong** cache line 246

# **Solar-DRAM**

#### Uses a static profile of weak subarray columns

- Identifies subarray columns as weak or strong

- Obtained in a one-time profiling step

#### **Three Components**