# TRRespass: Exploiting the many sides of Target Row Refresh

Pietro Frigo, Emanuele Vannacci, Hasan Hassan, Victor van der Veen, Onur Mutlu, Cristiano Giuffrida, Herbert Bos, Kaveh Razavi

2020 IEEE Symposium on Security and Privacy

18-21 May 2020

Julian Müller

#### Motivation

- RowHammer discovered in 2014

- Used as attack vector in the wild

- Aim of the paper: Analyze and circumvent mitigation mechanisms

#### Overview

- DRAM

- RowHammer

- Exploiting RowHammer

- RowHammer based attacks

- Mitigation

- □ Target Row Refresh

- Hammering

- Analyzing TRR

- MC-based TRR (Intel's pTRR)

- ☐ In-DRAM TRR

- TRRespass

- Conclusion

- Paper analysis

- Discussion

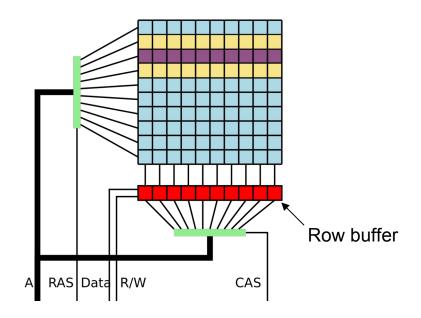

#### DRAM

- Organized into rows and columns

- Memory cells leak => refresh every 64ms

- Content of a row is loaded into row buffer

- Electromagnetic field produced by row activation increases leakage => bit may flip

RowHammer

Electromagnetic field produced by row activation increases leakage => bit may flip

- Alternately read addresses X and Y

- Flush the cache

- Clflush is an unprivileged instruction on x86

```

code1a:

mov (X), %eax // read from address X

mov (Y), %ebx // read from address Y

clflush (X) // flush cache for address X

clflush (Y) // flush cache for address Y

jmp code1a

```

#### Exploiting RowHammer

- Change contents of read-only memory, e.g. shared libaries

- Change contents of virtual pages of other processes/kernel

Without the OS noticing it

RowHammer breaks memory isolation!!!

# RowHammer based attacks

- Manipulate Page Tables to gain access to the whole physical Memory¹

- Breaking out of NaCl Sandbox¹

- Emulate clflush in a web browser using JavaScript<sup>2</sup>

- Read out secred data, e.g. an RSA-Key³

- 1. <u>M. Seaborn and T. Dullien, "Exploiting the DRAM Rowhammer Bugto Gain Kernel Privileges,"</u>

<u>Black Hat USA, 2015</u>

- 2. <u>D. Grusset al., "Rowhammer.js: A Remote Software-Induced FaultAttack in JavaScript," DIMVA, 2016</u>

- 3. A. Kwong et al., "RAMBleed: Reading Bits in Memory WithoutAccessing Them," in S&P, 2020

#### Mitigation (so far)

- Doubling (or even quadrupling) the refresh rate

- Only solution for existing circuits

- Energy consumption is proportional to refresh rate

- Latency increases

- □Time frame still too big

- □=>Ineffective

#### Mitigation (so far)

- ECC memory

- Can correct 1 bit flip per 64-bit word

- □Can detect 2 bit flips per 64-bit word

- □Cannot detect 3 or more bit flips

- RowHammer usually induces more bit flips

- □=>Ineffective

## Mitigation (so far)

- Doubling (or even quadrupling) the refresh rate

- □ =>Ineffective

- ECC memory

- =>Ineffective

- Target Row Refresh (TRR)

- Count accesses per row

- Issue extra refreshes to victim rows

- DRAM manufacturers advertise their chips as RowHammer-free

- DRAM manufacturers do not disclose their TRR implementations

#### Industry on RowHammer:

#### Hammering

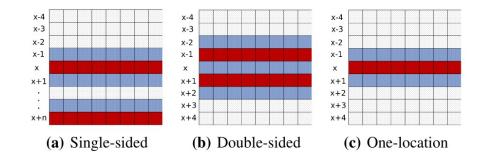

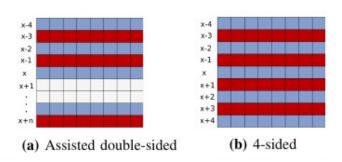

- Single sided: Standard pattern used in original demonstration

- Double sided: victim row in the middle experiences twice as many hammerings

#### Hammering DDR4

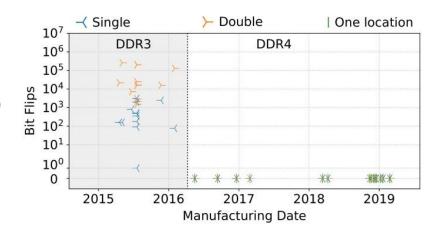

- 2016: 87% of all modules vulnerable (DDR3)

- Analysis of 42 recent modules (DDR4) (Samsung, Micron, Hynix)

- Standard hammering patterns

- No bit flips observable

#### Hammering DDR4

- Refreshing turned off

- Double sided hammering

- Bit flips at 25K activations per row

- 139K needed on DDR3

- Exponential growth

#### Intel's pTRR

- Only publicly advertised MCimplementation of TRR

- MAC-value inside DRAM chips:

- any positive number => issue refresh if that number is reached

- □ Untested => double refresh rate

- Unlimited => do nothing

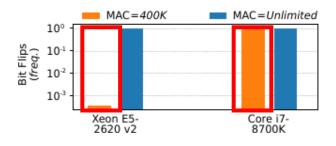

#### Intel's pTRR

- MAC=400k vs. MAC=Unlimited

- Core i7 vs. Xeon E5

- Xeon E5: almost no bit flips with MAC=400k

- Core i7: No difference

- No pTRR on consumer line CPUs

| CPU             | Family                  | Year | DRAM<br>generation | Defense |  |

|-----------------|-------------------------|------|--------------------|---------|--|

| Server Line     |                         |      |                    |         |  |

| Xeon E5-2620 v4 | Broadwell               | 2016 | DDR4               | REF×2   |  |

| Xeon E5-2620 v2 | 5-2620 v2 Ivy Bridge EP |      | DDR3               | pTRR    |  |

| Xeon E3-1270 v3 | Haswell                 | 2013 | DDR3               | -       |  |

| Consumer Line   |                         |      | _                  |         |  |

| Core i9-9900K   | Coffee Lake R           | 2018 | DDR4               | -       |  |

| Core i7-8700K   | 7-8700K Coffee Lake     |      | DDR4               | <u></u> |  |

| Core i7-7700K   | Kaby Lake               | 2017 | DDR4               | _       |  |

| Core i7-5775C   | ore i7-5775C Broadwell  |      | DDR3               | _       |  |

#### Reverse-engineering in-DRAM TRR

- Hypothesis:

- Sampler: detects potential aggressor rows

- Inhibitor: issues additional refreshes to victim rows

#### **TRRespass**

- New Version of RowHammer code

- Extends double-sided to n-sided access pattern

#MakeDoubleSidedGreatAgain

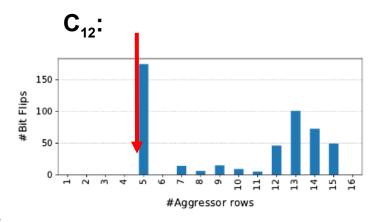

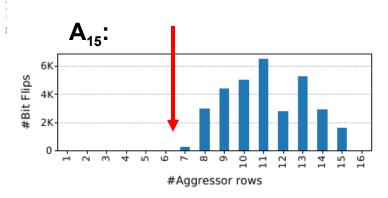

## Determining the size of the sampler

- Increasing n reveals sampler size

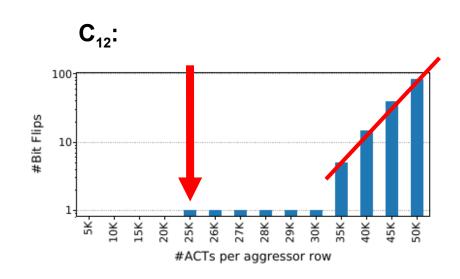

- □ 4 on C<sub>12</sub>

- $\Box$  6 on  $A_{15}$

- Exploitable

- Use n dummy aggressor rows

- Camouflage real aggressor rows

## **TRRespass**

## TRRespass: The full evaluation

- TRRespass running for 6 hours

- 13 of 42 modules vulnerable (31%)

- 87% after discovery

- Large divergence in # of bit flips

- 5 bit flips on B<sub>2</sub>

- 190k bit flips on C<sub>12</sub>

- Only 2 of C's modules vulnerable

TABLE II: TRRespass results. We report the number of patterns found and bit flips detected for the 42 DRAM modules in our set

| Module Dat                      | Date               | e Freq. | Size | Organization |       | Found      | Best Pattern | Corruptions |           |       | Double    |                   |          |

|---------------------------------|--------------------|---------|------|--------------|-------|------------|--------------|-------------|-----------|-------|-----------|-------------------|----------|

| Модине                          | (yy-ww)            | (MHz)   | (GB) | Ranks        | Banks | Pins       | MAC          | Patterns    | вем Рашет | Total | $1 \to 0$ | $0 \rightarrow 1$ | Refresh  |

| $A_{0,1,2,3}$                   | 16-37              | 2132    | 4    | 1            | 16    | $\times 8$ | UL           | _           | _         | _     | _         | _                 | _        |

| $\mathcal{A}_4$                 | 16-51              | 2132    | 4    | 1            | 16    | $\times 8$ | UL           | 4           | 9-sided   | 7956  | 4008      | 3948              | _        |

| $A_5$                           | 18-51              | 2400    | 4    | 1            | 8     | ×16        | UL           | _           | _         | _     | _         | _                 | _        |

| $A_{6,7}$                       | 18-15              | 2666    | 4    | 1            | 8     | ×16        | UL           | _           | _         | _     | _         | _                 | _        |

| $A_8$                           | 17-09              | 2400    | 8    | 1            | 16    | $\times 8$ | UL           | 33          | 19-sided  | 20808 | 10289     | 10519             | -        |

| $A_9$                           | 17-31              | 2400    | 8    | 1            | 16    | $\times 8$ | UL           | 33          | 19-sided  | 24854 | 12580     | 12274             | _        |

| $A_{10}$                        | 19-02              | 2400    | 16   | 2            | 16    | $\times 8$ | UL           | 488         | 10-sided  | 11342 | 1809      | 11533             | ✓        |

| $A_{11}$                        | 19-02              | 2400    | 16   | 2            | 16    | $\times 8$ | UL           | 523         | 10-sided  | 12830 | 1682      | 11148             | ✓        |

| $A_{12,13}$                     | 18-50              | 2666    | 8    | 1            | 16    | $\times 8$ | UL           | _           | _         | _     | _         | _                 | _        |

| $A_{14}$                        | 19-08 <sup>†</sup> | 3200    | 16   | 2            | 16    | ×          |              |             |           |       |           |                   |          |

| ${\mathcal{A}_{15}}^{\ddagger}$ | 17-08              | 2132    | 4    | 1            | 16    | ×          | 3-sic        | led         | 17        |       | 10        | ,                 | 7        |

| $\mathcal{B}_0$                 | 18-11              | 2666    | 16   | 2            | 16    | ×          | 2 01         | l.d         | 22        |       | 16        |                   | <i>c</i> |

| $\mathcal{B}_1$                 | 18-11              | 2666    | 16   | 2            | 16    | ×          | 3-sic        | iea         | 22        |       | 16        |                   | 6        |

| $\mathcal{B}_2$                 | 18-49              | 3000    | 16   | 2            | 16    | ×          | 3-sic        | lad         | 5         |       | 2         |                   | 3        |

| $\mathcal{B}_3$                 | 19-08 <sup>†</sup> | 3000    | 8    | 1            | 16    | ×          | 5-810        | ieu         | ٠         |       | 2         |                   | 3        |

| $B_{4,5}$                       | 19-08 <sup>†</sup> | 2666    | 8    | 2            | 16    | Χo         | UГ           | _           | _         |       | _         | _                 | _        |

| $B_{6,7}$                       | 19-08 <sup>†</sup> | 2400    | 4    | 1            | 16    | $\times 8$ | UL           | _           | _         | _     | -         | _                 | _        |

| $\mathcal{B}_8^{\circ}$         | 19-08 <sup>†</sup> | 2400    | 8    | 1            | 16    | $\times 8$ | UL           | _           | _         | _     |           | _                 | _        |

| $\mathcal{B}_9^{\diamond}$      | 19-08 <sup>†</sup> | 2400    | 8    | 1            | 16    | $\times 8$ | UL           | 2           | 3-sided   | 12    | _         | 12                | ✓        |

| $B_{10,11}$                     | 16-13 <sup>†</sup> | 2132    | 8    | 2            | 16    | $\times 8$ | UL           | _           | _         | _     | _         | _                 | _        |

| $C_{0,1}$                       | 18-46              | 2666    | 16   | 2            | 16    | ×8         | UL           | _           | _         | _     | _         | _                 | _        |

| $C_{2,3}$                       | 19-08 <sup>†</sup> | 2800    | 4    | 1            | 16    | $\times 8$ | UL           | _           | _         | _     | _         | _                 | _        |

| $C_{4,5}$                       | 19-08 <sup>†</sup> | 3000    | 8    | 1            | 16    | $\times 8$ | UL           | _           | _         | _     | _         | _                 | _        |

| $C_{6,7}$                       | 19-08 <sup>†</sup> | 3000    | 16   | 2            | 16    | $\times 8$ | UL           | _           | _         | _     | _         | _                 | _        |

| $C_8$                           | 19-08 <sup>†</sup> | 3200    | 16   | 2            | 16    | $\times 8$ | UL           | _           | _         | _     | _         | _                 | _        |

| $C_9$                           | 18-47              | 2666    | 16   | 2            | 16    | $\times 8$ | UL           | _           | _         | _     | _         | _                 | _        |

| $C_{10,11}$                     | 19-04              | 2933    | 8    | 1            | 16    | $\times 8$ | UL           | _           | _         | _     | _         | _                 | _        |

| $C_{12}^{\dagger}$              | 15-01 <sup>†</sup> | 2132    | 4    | 1            | 16    | ×8.1       | 10-si        | ded         | 190037    | 63    | 3904      | 12/               | 5133     |

| $C_{13}^{\ddagger}$             | 18-49              | 2132    | 4    | 1            | 16    | -×8        | 10-51        | ucu         | 1 2003 /  | 0.    | 7704      | 120               | 0133     |

Analyzed using the FPGA-based SoftMC.

The system runs with double refresh frequency in standard conditions. We configured the refresh interval to be 64 ms in the BIOS set

#### TRRespass on phones

- 13 models tested

- Only Android

- 5 of 13 vulnerable (38%)

- Different DRAM chips accross the same model

| Mobile<br>Phone            | Year | SoC            | Memory<br>(GB) | Found<br>Patterns |

|----------------------------|------|----------------|----------------|-------------------|

| Google Pixel               | 2016 | MSM8996        | 4†             | ✓                 |

| Google Pixel 2             | 2017 | MSM8998        | 4              | _                 |

| Samsung<br>G960F/DS        | 2018 | Exynos<br>9810 | 4              | _                 |

| Huawei P20 DS              | 2018 | Kirin 970      | 4              | _                 |

| Sony XZ3                   | 2018 | SDM845         | 4              | _                 |

| HTC U12+                   | 2018 | SDM845         | 6              | _                 |

| LG G7 ThinQ                | 2018 | SDM845         | 4 <sup>†</sup> | ✓                 |

| Google Pixel 3             | 2018 | SDM845         | 4              | ✓                 |

| Google Pixel 4             | 2019 | SM8150         | 6              | _                 |

| OnePlus 7                  | 2019 | SM8150         | 8              | ✓                 |

| Samsung<br>G970F/DS        | 2019 | Exynos<br>9820 | 6              | ✓                 |

| Huawei P30 DS              | 2019 | Kirin 980      | 6              | _                 |

| Xiaomi Redmi<br>Note 8 Pro | 2019 | Helio<br>G90T  | 6              | _                 |

<sup>†</sup> LPDDR4 (not LPDDR4X)

# Mounting real-world attacks using TRRespass

- Attacks tested:

- Manipulating page tables

- Corrupting RSA-Key

- Circumventing sudo checks

- Most and least vulnerable modules from each vendor

- All attacks failed on B's modules

- Time span between 2s and 3h

**TABLE IV: Time to exploit.** Time to find the first exploitable template on two sample modules from each DRAM vendor.

| Module             | $\tau(ms)$ | PTE [81] | RSA-2048 [79] | sudo <b>[27</b> ] |

|--------------------|------------|----------|---------------|-------------------|

| $\mathcal{A}_{14}$ | 188.7      | 4.9s     | 6m 27s        | _                 |

| $\mathcal{A}_4$    | 180.8      | 38.8s    | 39m 28s       | _                 |

| $\mathcal{B}_1$    | 360.7      | _        | _             | _                 |

| $\mathcal{B}_2$    | 331.2      | _        | _             | _                 |

| $C_{12}$           | 300.0      | 2.3s     | 74.6s         | 54m16s            |

| $\mathcal{C}_{13}$ | 180.9      | 3h 15m   | _             | _                 |

τ: Time to template a single row: time to fill the victim and aggressor rows + hammer time + time to scan the row.

#### 7

#### Conclusion

#### Industry:

- RowHammer is still a problem

- Partially worse

- 2016: 139k activations for bit flips

- □ 2020: 50k

- Partially better

- 2016: 87% of all modules vulnerable

- □ 2020: 31%

#### Researchers:

#### Strengths

- Addressing a serious security issue

- Very detailed analysis and reverse engineering of mostly undocumented hardware

- Proving manufacturers wrong

#### Weaknesses

- No statement about what DRAM manufacturers did wrong

- No improvement suggestions

- TRRespass vs. pTRR??

- TRRespass vs. iPhone??

- Real-world attacks on phones??

- No disclosure of the manufacturers

#### Discussion

- Is such detailed public disclosure of vulnerabilities a good idea?

- Is TRR the right way to go?

- Will RowHammer kill DRAM?