Center for Reliable and High-Performance Computing

# IMPACT: AN ARCHITECTURAL FRAMEWORK FOR MULTIPLE-INSTRUCTION-ISSUE PROCESSORS

Pohua P. Chang Scott A. Mahlke William Y. Chen Nancy J. Warter Wen-mei W. Hwu

Coordinated Science Laboratory

College of Engineering

UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

| SECURITY CL                                        | ASSIFICATION C                                                                                                                       | OF THIS PAGE                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                   |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                                                    |                                                                                                                                      |                                                                                                                                                                                                                             | REPORT DOCL                                                                                                                                                                                                                                                       | MENTATION                                                                                                                                                      | PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |                                                                                    |

|                                                    | SECURITY CLAS                                                                                                                        | SIFICATION                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                   | 16. RESTRICTIVE                                                                                                                                                | MARKINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                        |                                                                                    |

| Unclassified 2a. SECURITY CLASSIFICATION AUTHORITY |                                                                                                                                      |                                                                                                                                                                                                                             | None                                                                                                                                                                                                                                                              |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

| Za. SECURIT                                        | 2b. DECLASSIFICATION / DOWNGRADING SCHEDULE                                                                                          |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                   | 3. DISTRIBUTION/AVAILABILITY OF REPORT  Approved for public release; distribution unlimited                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

| 2b. DECLASS                                        |                                                                                                                                      |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                   |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

| 4. PERFORM                                         | ING ORGANIZA                                                                                                                         | TION REPORT NUMB                                                                                                                                                                                                            | ER(S)                                                                                                                                                                                                                                                             | 5. MONITORING ORGANIZATION REPORT NUMBER(S)                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

| UILU-                                              | ENG-91-220                                                                                                                           | )8                                                                                                                                                                                                                          | CRHC-91-4                                                                                                                                                                                                                                                         |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

|                                                    |                                                                                                                                      | ORGANIZATION                                                                                                                                                                                                                | 6b. OFFICE SYMBOL                                                                                                                                                                                                                                                 | 7a. NAME OF N                                                                                                                                                  | MONITORING ORG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ANIZATION                                                                                                                              |                                                                                    |

|                                                    | inated Sci                                                                                                                           |                                                                                                                                                                                                                             | (If applicable)                                                                                                                                                                                                                                                   | NASA,                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

|                                                    |                                                                                                                                      |                                                                                                                                                                                                                             | N/A                                                                                                                                                                                                                                                               |                                                                                                                                                                | Science For                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                        |                                                                                    |

|                                                    | (City, State, an                                                                                                                     |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                   | 7b. ADDRESS (C.                                                                                                                                                | ity, State, and ZII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Code)                                                                                                                                  |                                                                                    |

|                                                    | s, IL 618                                                                                                                            | ield Avenue<br>01                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                   | NASA Langley Res. Ctr., Hampton VA 23665<br>NSF 1800 G St. Washington DC 20552                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

| 8a. NAME OF                                        | FUNDING/SPC                                                                                                                          | INSORING                                                                                                                                                                                                                    | 8b. OFFICE SYMBOL                                                                                                                                                                                                                                                 | 9 PROCUREMEN                                                                                                                                                   | IT INSTRUMENT I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DENTIFICATIO                                                                                                                           |                                                                                    |

| ORGANIZ                                            |                                                                                                                                      |                                                                                                                                                                                                                             | (If applicable)                                                                                                                                                                                                                                                   | NASA NAS                                                                                                                                                       | T INSTRUMENT II<br>SA NAG 1-613                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DENTIFICATION                                                                                                                          | N NUMBER                                                                           |

|                                                    | NASA and NSF  Bc. ADDRESS (City, State, and ZIP Code)                                                                                |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                   | NSF: MIP-88-09478                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

| 8c. ADDRESS<br>see 7                               |                                                                                                                                      | I ZIP Code)                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                   |                                                                                                                                                                | PROJECT TASK WORK LINIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                        |                                                                                    |

| see /                                              | D •                                                                                                                                  |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                   | PROGRAM<br>ELEMENT NO.                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        | WORK UNIT<br>ACCESSION NO.                                                         |

| 12. PERSONA  13a. TYPE OF  Techni                  | REPORT                                                                                                                               | nang, Pohua P.  13b. TIME CO                                                                                                                                                                                                | ork for Multiple .; Mahlke, Scott  OVEREDTO                                                                                                                                                                                                                       | A.; Chen, W                                                                                                                                                    | illiam, Wart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | er, Nancy                                                                                                                              | J.; Hwu, W. AGE COUNT 38                                                           |

|                                                    |                                                                                                                                      |                                                                                                                                                                                                                             | est and the                                                                                                                                                                                                                                                       |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

| 17.                                                | COSATI                                                                                                                               |                                                                                                                                                                                                                             | 18. SUBJECT TERMS (                                                                                                                                                                                                                                               | Continue on revers                                                                                                                                             | e if necessary and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d identify by                                                                                                                          | block number)                                                                      |

| FIELD                                              | GROUP                                                                                                                                | SUB-GROUP  Multiple-instruction issue processors, optimizing, compiler code, scheduling code, transformation concurrency                                                                                                    |                                                                                                                                                                                                                                                                   |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

|                                                    |                                                                                                                                      |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                   | scheddling code, transformation concurrency                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

| 19. ABSTRACT                                       | (Continue on                                                                                                                         | reverse if necessary                                                                                                                                                                                                        | and identify by block r                                                                                                                                                                                                                                           | number)                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |                                                                                    |

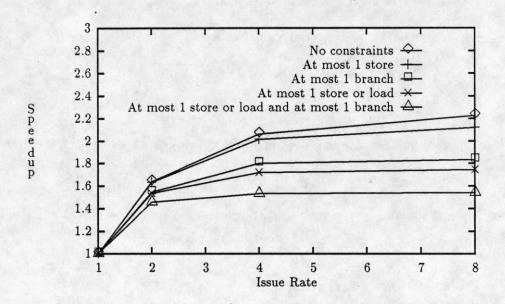

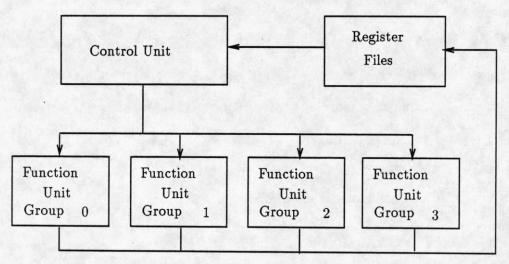

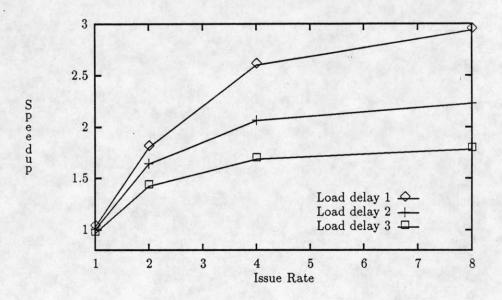

| the                                                | otimizing C compiler is summance of multipstruction-issue or.  To addresse code schedulons. Based on patures that besirs. By support | mpiler to exploit in marized in this papule-instruction-issue processors have act architecture designing model, the instruction model, the instruction model in the experimental rest support the IMPA ting these architect | ent hardware. In the II astruction level concurrer. Using the IMPACT processors executing chieved solid speedup in issues, we ran experiuction issue rate, the misults, we propose the ICT-I C compiler to genural features, multiple inpilation support from the | rency. The optimic over a high-performents to charact temory load latence impact and impact and impact and impact and impact are efficient construction issue. | ve have developed ization capabilities and experiments non-numerical promance single-independent of the control | ed IMPACT-les of the IMP<br>s to analyze the<br>ograms. The<br>struction-issur-<br>ering tradeoff<br>on unit resour<br>c, a set of arc | , a highly PACT-I C he perfor- multiple- e proces- s such as ce limita- hitectural |