# Digital Design & Computer Arch.

Lecture 15b: Out-of-Order Execution, DataFlow & Load/Store Handling

Prof. Onur Mutlu

ETH Zürich Spring 2020 9 April 2020

## Required Readings

#### This week

- Out-of-order execution

- H&H, Chapter 7.8-7.9

- Smith and Sohi, "The Microarchitecture of Superscalar Processors," Proceedings of the IEEE, 1995

- More advanced pipelining

- Interrupt and exception handling

- Out-of-order and superscalar execution concepts

### Optional

Kessler, "The Alpha 21264 Microprocessor," IEEE Micro 1999.

#### Next Week

McFarling, "Combining Branch Predictors," DEC WRL Technical Report, 1993.

## Reminder: Optional Homeworks

- Posted online

- 3 Optional Homeworks. One more coming out next week

- Optional

- Good for your learning

- https://safari.ethz.ch/digitaltechnik/spring2020/doku.php?id

=homeworks

# Agenda for Today & Next Few Lectures

- Single-cycle Microarchitectures

- Multi-cycle and Microprogrammed Microarchitectures

- Pipelining

- Issues in Pipelining: Control & Data Dependence Handling,

State Maintenance and Recovery, ...

- Out-of-Order Execution

- Other Execution Paradigms

### Recall: An Exercise

```

MUL R3 \leftarrow R1, R2

ADD R5 \leftarrow R3, R4

ADD R7 \leftarrow R2, R6

ADD R10 \leftarrow R8, R9

MUL R11 \leftarrow R7, R10

ADD R5 \leftarrow R5, R11

```

- Assume ADD (4 cycle execute), MUL (6 cycle execute)

- Assume one adder and one multiplier

- How many cycles

- in a non-pipelined machine

- in an in-order-dispatch pipelined machine with imprecise exceptions (no forwarding and full forwarding)

- in an out-of-order dispatch pipelined machine imprecise exceptions (full forwarding)

### Recall: Exercise Continued

```

FD123456W

--- - D1234W

- - - D123 4 W

FD1234W

FD---- D123456 W

D1234W

Execution timeline w/ scareboarding

FD123456W

E, 12134 W

D 1 23 4 W

F D 1 2 3 4 W

234 5 6 W

```

### Recall: Exercise Continued

```

MUL R3 \leftarrow R1, R2

ADD R5 \leftarrow R3, R4

ADD R7 \leftarrow R2, R6

ADD R10 \leftarrow R8, R9

MUL R11 \leftarrow R7, R10

ADD R5 \leftarrow R5, R11

```

```

FD 123456W

FD 1234W

FD 1234W

FD 1234W

FD 1234W

FD 1234W

Tamosdo's algorithm + FM Annorthing

20 cycles

```

### Recall: Our First OoO Machine Simulation

#### Program We Will Simulate

| MUL | R1, | R2  | $\rightarrow$ | R3  |

|-----|-----|-----|---------------|-----|

| ADD | R3, | R4  | $\rightarrow$ | R5  |

| ADD | R2, | R6  | $\rightarrow$ | R7  |

| ADD | R8, | R9  | $\rightarrow$ | R10 |

| MUL | R7, | R10 | $\rightarrow$ | R11 |

| ADD | R5, | R11 | $\rightarrow$ | R5  |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 3     |

| R4       | 1     |     | 4     |

| R5       | 1     |     | 5     |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 7     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 10    |

| R11      | 1     |     | 11    |

Register Alias Table

#### Initially:

- 1. RS's are all Invalid (Empty)

- 2. All Registers are Valid

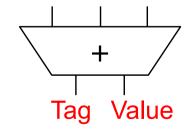

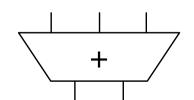

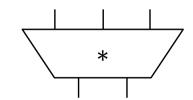

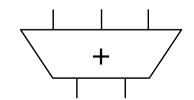

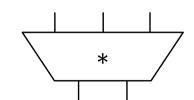

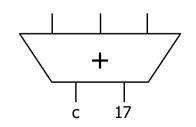

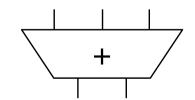

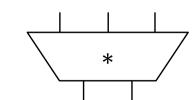

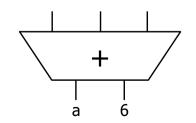

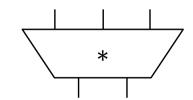

#### **RS for ADD Unit**

|   | Source 1 |     |       | 9, | Source | 2     |

|---|----------|-----|-------|----|--------|-------|

|   | V        | Tag | Value | ٧  | Tag    | Value |

| а |          |     |       |    |        |       |

| b |          |     |       |    |        |       |

| С |          |     |       |    |        |       |

| d |          |     |       |    |        |       |

|   |          |     |       |    |        |       |

#### **RS for MUL Unit**

|   | Source 1    |  |   | Source 2 |       |  |

|---|-------------|--|---|----------|-------|--|

|   | V Tag Value |  | ٧ | Tag      | Value |  |

| Х |             |  |   |          |       |  |

| У |             |  |   |          |       |  |

| Z |             |  |   |          |       |  |

| t |             |  |   |          |       |  |

ADD and MUL Execution Units

Cycle

| MUL | R1, | R2  | $\rightarrow$ | R3  |

|-----|-----|-----|---------------|-----|

| ADD | R3, | R4  | $\rightarrow$ | R5  |

| ADD | R2, | R6  | $\rightarrow$ | R7  |

| ADD | R8, | R9  | $\rightarrow$ | R10 |

| MUL | R7, | R10 | $\rightarrow$ | R11 |

| ADD | R5, | R11 | $\rightarrow$ | R5  |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 3     |

| R4       | 1     |     | 4     |

| R5       | 1     |     | 5     |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 7     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 10    |

| R11      | 1     |     | 11    |

|   | Source 1    |  |   | •,  | Source | 2 |

|---|-------------|--|---|-----|--------|---|

|   | V Tag Value |  | ٧ | Tag | Value  |   |

| а |             |  |   |     |        |   |

| b |             |  |   |     |        |   |

| С |             |  |   |     |        |   |

| d |             |  |   |     | ·      | · |

|   | Source 1    |  |   | 9   | Source | 2 |

|---|-------------|--|---|-----|--------|---|

|   | V Tag Value |  | V | Tag | Value  |   |

| х |             |  |   |     |        |   |

| У |             |  |   |     |        |   |

| z |             |  |   |     |        |   |

| t |             |  |   |     |        |   |

|     |     |     |               | Cycle | 1 |

|-----|-----|-----|---------------|-------|---|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 3     |

| R4       | 1     |     | 4     |

| R5       | 1     |     | 5     |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 7     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 10    |

| R11      | 1     |     | 11    |

|   | Source 1    |  |   | 9   | Source | 2 |

|---|-------------|--|---|-----|--------|---|

|   | V Tag Value |  | V | Tag | Value  |   |

| а |             |  |   |     |        |   |

| b |             |  |   |     |        |   |

| С |             |  |   |     |        |   |

| d |             |  |   |     |        |   |

|   | Source 1    |  |   | Source 2 |       |  |

|---|-------------|--|---|----------|-------|--|

|   | V Tag Value |  | V | Tag      | Value |  |

| х |             |  |   |          |       |  |

| У |             |  |   |          |       |  |

| Z |             |  |   |          |       |  |

| t |             |  |   |          |       |  |

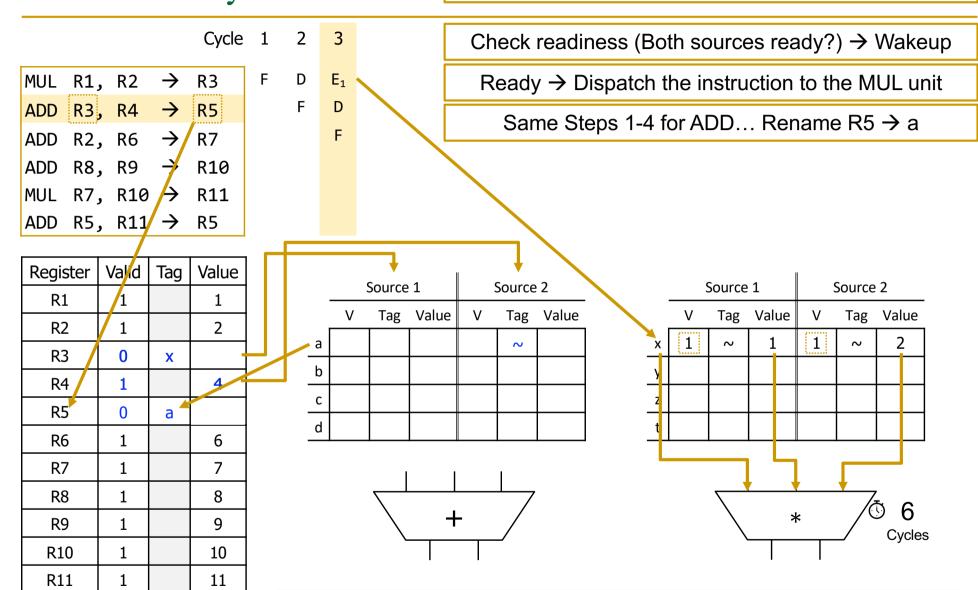

MUL gets decoded and allocated into RS x

Step 1: Check if reservation station available. Yes: x

Cycle 1 2

R2

R1,

F3, K4

MUL

ADD

ADD R8, R9

$$\rightarrow$$

R10

MUL R7, R10

$$\rightarrow$$

R11

ADD R5, R11  $\rightarrow$  R5

Step 2: Access the Register Alias Table

Step 3: Put source registers into reservation station x.

Step 4: Rename destination register R3  $\rightarrow$  x

R3 is now renamed to x.

Its new value will produced by the *reservation station* that is identified by tag x.

| Reg | Register |   | Tag | Value |

|-----|----------|---|-----|-------|

| R1  |          | 1 |     | 1 -   |

| R2  | 2        | 1 |     | 2 -   |

| R3  | 3        | 0 | X   |       |

| R4  | 1        | 1 |     | 4     |

| R5  | 5        | 1 |     | 5     |

| Re  | 5        | 1 |     | 6     |

| R7  | 7        | 1 |     | 7     |

| R8  | 3        | 1 |     | 8     |

| R9  | 9        | 1 |     | 9     |

| R10 |          | 1 |     | 10    |

| R1  | 1        | 1 |     | 11    |

| ag | Value | V | Tag | Value |

|----|-------|---|-----|-------|

|    |       |   |     |       |

|    |       |   |     |       |

|    |       |   |     |       |

|    |       |   |     |       |

|    |       |   |     |       |

|    |       |   |     |       |

|   |   | Source | 1     |   | Source | 2     |

|---|---|--------|-------|---|--------|-------|

|   | V | Tag    | Value | V | Tag    | Value |

| Х |   | 2      |       |   | 2      |       |

| У |   |        |       |   |        |       |

| Z |   |        |       |   |        |       |

| t |   |        |       |   |        |       |

MUL in RS x is ready to execute in the next cycle!

#### 1. MUL in RS x starts executing

#### 2. ADD gets decoded and allocated into RS a

ADD in RS a cannot execute in the next cycle: one source is not valid

Cycle 1 2 3 4

ADD in RS a waits because one source is not valid.

MUL R1, R2  $\rightarrow$  R3 ADD R3, R4  $\rightarrow$  R5 D E<sub>1</sub> E<sub>2</sub> F D -

D

Rename R7 → b

ADD R2, R6  $\rightarrow$  R7

ADD R8, R9 → R10

MUL R7, R10  $\rightarrow$  R11

ADD R5, R11 → R5

Valid

1

0

1

Tag

Χ

a

Value

2

4

6

8

9

10

11

Register

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

|   |   |   | •      |       | <b>,</b> |     |       |  |  |

|---|---|---|--------|-------|----------|-----|-------|--|--|

|   |   |   | Source | 1     | Source 2 |     |       |  |  |

|   |   | V | Tag    | Value | ٧        | Tag | Value |  |  |

|   | а | 0 | Х      |       | 1        | 2   | 4     |  |  |

|   | b |   | 2      |       |          | 2   |       |  |  |

|   | С |   |        |       |          |     |       |  |  |

| , | d |   |        |       |          |     |       |  |  |

|   |   |   |        |       |          |     |       |  |  |

|   |             | Source | 1 | Source 2      |   |   |  |

|---|-------------|--------|---|---------------|---|---|--|

|   | V Tag Value |        |   | / Tag Value V |   |   |  |

| х | 1           | 2      | 1 | 1             | ~ | 2 |  |

| У |             |        |   |               |   |   |  |

| Z |             |        |   |               |   |   |  |

| t |             |        |   |               |   |   |  |

ADD in RS b is ready to execute in the next cycle!

It will be executed out of order in the next cycle.

|     |     |     |               | Cycle | 1 | 2 | 3              | 4     | 5                     |

|-----|-----|-----|---------------|-------|---|---|----------------|-------|-----------------------|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | E <sub>1</sub> | $E_2$ | <b>E</b> <sub>3</sub> |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D              | -     | -                     |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F              | D     | $E_1$                 |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |                | F     | D                     |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |                |       | F                     |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |                |       |                       |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 0     | Х   |       |

| R4       | 1     |     | 4     |

| R5       | 0     | а   |       |

| R6       | 1     |     | 6     |

| R7       | 0     | b   |       |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 0     | U   |       |

| R11      | 1     |     | 11    |

|    |   | 9 | Source | 1   |     | Source 2 |     |                 |    |

|----|---|---|--------|-----|-----|----------|-----|-----------------|----|

|    |   | V | Tag    | Val | lue | V        | Tag | Value           |    |

| a  | 9 | 0 | Х      |     |     | 1        | ~   | 4               |    |

| _b | ) | 1 | 2      | 2   | 2   | 1        | 2   | 6               |    |

|    | , | 1 | 2      |     | }   | 1        | 2   | 9               |    |

|    | ł |   |        |     |     |          |     |                 |    |

|    |   |   |        |     | +   | -<br>    |     | 5   4     Cycle | es |

|   |             | Source | 1 | Source 2 |       |   |  |

|---|-------------|--------|---|----------|-------|---|--|

|   | V Tag Value |        | V | Tag      | Value |   |  |

| х | 1           | >      | 1 | 1        | ~     | 2 |  |

| У |             |        |   |          |       |   |  |

| Z |             |        |   |          |       |   |  |

| t |             |        |   |          |       |   |  |

ADD in RS c is ready to execute in the next cycle!

|     |     |     |               | Cycle | 1 | 2 | 3     | 4     | 5              | 6     |

|-----|-----|-----|---------------|-------|---|---|-------|-------|----------------|-------|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | $E_1$ | $E_2$ | $E_3$          | $E_4$ |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D     | -     | -              | -     |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F     | D     | E <sub>1</sub> | $E_2$ |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |       | F     | D              | $E_1$ |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |       |       | F              | D     |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |       |       |                | F     |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 0     | Х   |       |

| R4       | 1     |     | 4     |

| R5       | 0     | а   |       |

| R6       | 1     |     | 6     |

| R7       | 0     | b   |       |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 0     | C   |       |

| R11      | 0     | у   |       |

|   |   | Source      | 1 | Source 2 |     |       |  |

|---|---|-------------|---|----------|-----|-------|--|

|   | V | V Tag Value |   |          | Tag | Value |  |

| а | 0 | х           |   | 1        | ~   | 4     |  |

| b | 1 | ~           | 2 | 1        | ~   | 6     |  |

| С | 1 | ~           | 8 | 1        | ~   | 9     |  |

| d |   |             |   |          |     |       |  |

|   | 9 | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| х | 1 | 2      | 1     | 1        | 2   | 2     |  |

| У | 0 | b      |       | 0        | С   |       |  |

| Z |   |        |       |          |     |       |  |

| t |   | ·      |       |          |     |       |  |

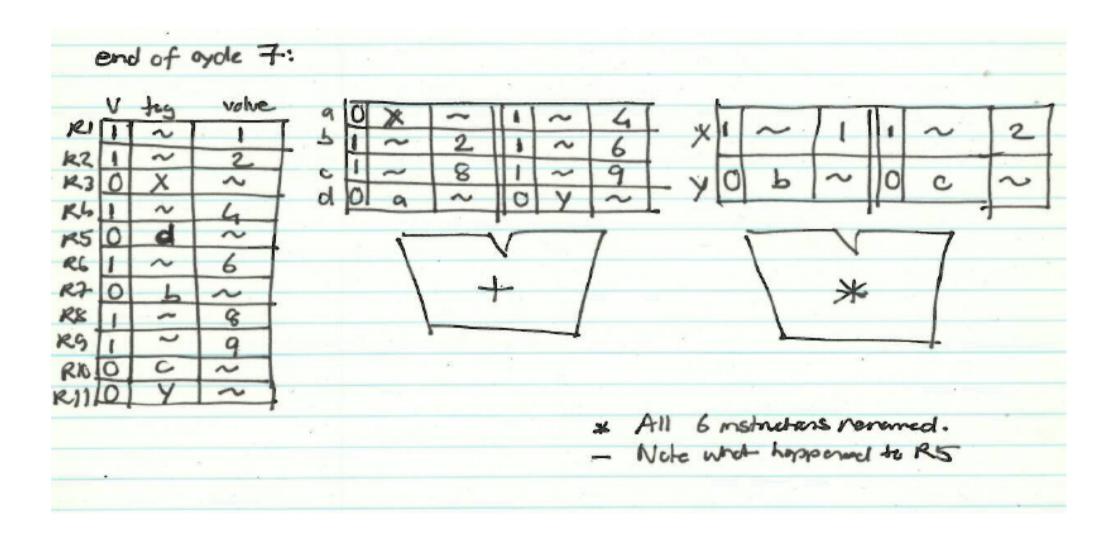

#### All 6 instructions are now decoded and renamed

#### Note what happened to R5!

Cycle 1 2 3 4 5 6 7

MUL R1, R2

$$\rightarrow$$

R3 F

ADD R3, R4  $\rightarrow$  R5

ADD R2, R6  $\rightarrow$  R7

ADD R8, R9  $\rightarrow$  R10

MUL R7, R10  $\rightarrow$  R11

ADD R5, R11  $\rightarrow$  R5

| D | E <sub>1</sub> | $E_2$ | $E_3$        | $E_4$                      | <b>E</b> <sub>5</sub>                                 |

|---|----------------|-------|--------------|----------------------------|-------------------------------------------------------|

| F | D              | -     | -            | -                          | -                                                     |

|   | F              | D     | $E_1$        | $E_2$                      | $E_3$                                                 |

|   |                | F     | D            | $E_1$                      | $E_2$                                                 |

|   |                |       | F            | D                          | -                                                     |

|   |                |       |              | F                          | D                                                     |

|   |                | F D   | F D -<br>F D | F D F D E <sub>1</sub> F D | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 0     | Х   |       |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 0     | b   |       |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 0     | С   |       |

| R11      | 0     | У   |       |

|   |   | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| а | 0 | Х      |       | 1        | ~   | 4     |  |

| b | 1 | ~      | 2     | 1        | ~   | 6     |  |

| С | 1 | ~      | 8     | 1        | ~   | 9     |  |

| d | 0 | a      |       | 0        | у   |       |  |

|   |   | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| х | 1 | 2      | 1     | 1        | ~   | 2     |  |

| У | 0 | b      |       | 0        | С   |       |  |

| Z |   |        |       |          |     |       |  |

| t |   |        | ·     |          |     |       |  |

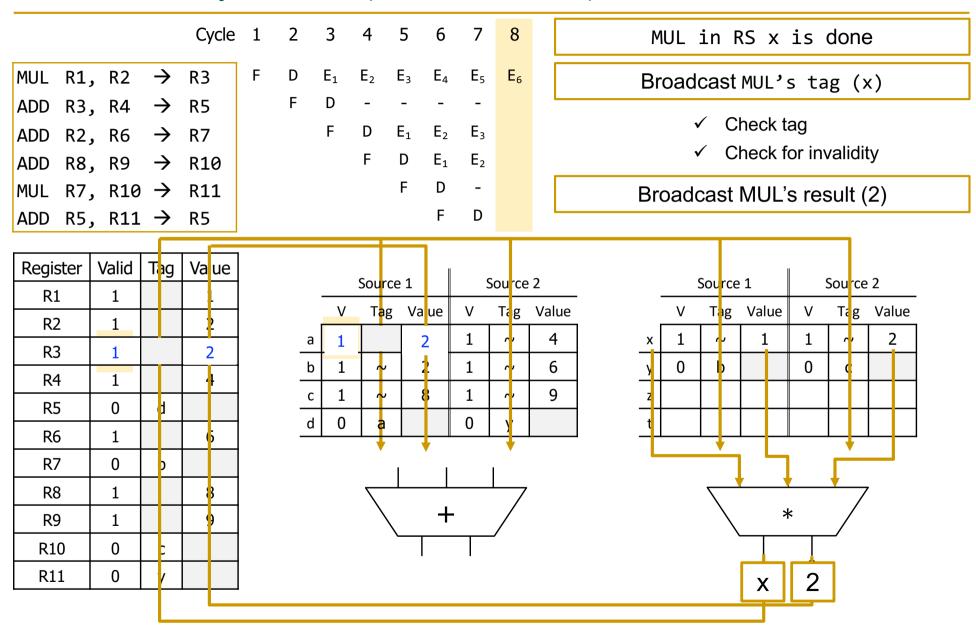

# Recall: Cycle 8 (First Slide)

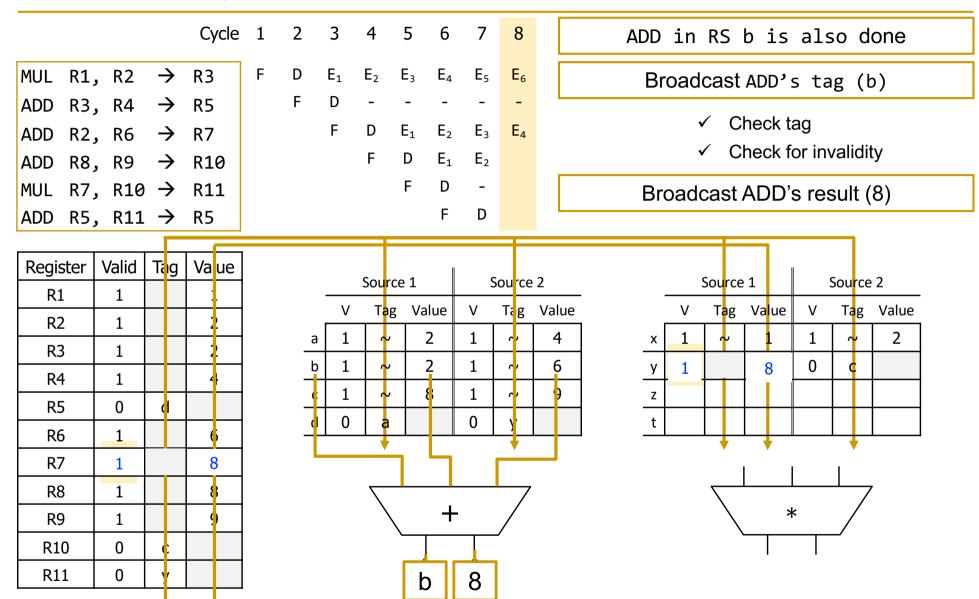

# Recall: Cycle 8 (Second Slide)

# Recall: Cycle 8 (Third Slide)

|     |     |     |               | Cycle | 1 | 2 | 3     | 4     | 5     | 6     | 7              | 8     |

|-----|-----|-----|---------------|-------|---|---|-------|-------|-------|-------|----------------|-------|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | $E_1$ | $E_2$ | $E_3$ | $E_4$ | E <sub>5</sub> | $E_6$ |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D     | -     | -     | -     | -              | -     |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F     | D     | $E_1$ | $E_2$ | $E_3$          | $E_4$ |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |       | F     | D     | $E_1$ | $E_2$          | $E_3$ |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |       |       | F     | D     | -              | -     |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |       |       |       | F     | D              | -     |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 0     | C   |       |

| R11      | 0     | у   |       |

|   | 9 | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| а | 1 | 2      | 2     | 1        | 2   | 4     |  |

| b | 1 | >      | 2     | 1        | >   | 6     |  |

| С | 1 | >      | 8     | 1        | >   | 9     |  |

| d | 0 | a      |       | 0        | у   |       |  |

|   |   | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| х | 1 | 2      | 1     | 1        | ~   | 2     |  |

| У | 1 | >      | 8     | 0        | С   |       |  |

| Z |   |        |       |          |     |       |  |

| t |   |        | ·     |          |     |       |  |

Cycle 1

MUL R1, R2  $\rightarrow$  R3 F

ADD R3, R4  $\rightarrow$  R5

ADD R2, R6  $\rightarrow$  R7

ADD R8, R9  $\rightarrow$  R10

MUL R7, R10  $\rightarrow$  R11

ADD R5, R11  $\rightarrow$  R5

| _ |   |       |       |       |       |       |       |       |

|---|---|-------|-------|-------|-------|-------|-------|-------|

| F | D | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_5$ | $E_6$ | W     |

|   | F | D     | -     | -     | -     | -     | -     | $E_1$ |

|   |   | F     | D     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |

|   |   |       | F     | D     | $E_1$ | $E_2$ | $E_3$ | $E_4$ |

|   |   |       |       | F     | D     | -     | -     | -     |

|   |   |       |       |       | F     | D     | -     | -     |

2 3 4 5 6

Broadcast and Update

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 0     | у   |       |

|   | Ç | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | >        | Tag | Value |  |

| а | 1 | 2      | 2     | 1        | ~   | 4     |  |

| b | 1 | 2      | 2     | 1        | ~   | 6     |  |

| С | 1 | ~      | 8     | 1        | ~   | 9     |  |

| d | 0 | a      |       | 0        | У   |       |  |

|   |   | Source | 1     | Source 2 |     |       |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|

|   | V | Tag    | Value | ٧        | Tag | Value |  |  |

| х | 1 | 2      | 1     | 1        | 2   | 2     |  |  |

| У | 1 | 2      | 8     | 1        | 2   | 17    |  |  |

| Z |   |        |       |          |     |       |  |  |

| t |   |        |       |          |     |       |  |  |

MUL in RS y is ready to execute in the next cycle!

|     |     |     |               | Cycle | 1 | 2 | 3              | 4     | 5     | 6     | 7                     | 8     | 9     | 10    |

|-----|-----|-----|---------------|-------|---|---|----------------|-------|-------|-------|-----------------------|-------|-------|-------|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | E <sub>1</sub> | $E_2$ | $E_3$ | $E_4$ | <b>E</b> <sub>5</sub> | $E_6$ | W     |       |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D              | -     | -     | -     | -                     | -     | $E_1$ | $E_2$ |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F              | D     | $E_1$ | $E_2$ | $E_3$                 | $E_4$ | W     |       |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |                | F     | D     | $E_1$ | $E_2$                 | $E_3$ | $E_4$ | W     |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |                |       | F     | D     | -                     | -     | -     | $E_1$ |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |                |       |       | F     | D                     | -     | -     | -     |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 0     | у   |       |

|   | 9 | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| а | 1 | 2      | 2     | 1        | 2   | 4     |  |

| b | 1 | 2      | 2     | 1        | 2   | 6     |  |

| С | 1 | 2      | 8     | 1        | 2   | 9     |  |

| d | 0 | a      |       | 0        | у   |       |  |

|   |   | Source | 1     | Source 2 |     |       |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|

|   | V | Tag    | Value | ٧        | Tag | Value |  |  |

| х | 1 | 2      | 1     | 1        | 2   | 2     |  |  |

| У | 1 | 2      | 8     | 1        | 2   | 17    |  |  |

| Z |   |        |       |          |     |       |  |  |

| t |   |        |       |          |     |       |  |  |

|     |     |     |               | Cycle | 1 | 2 | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | 11                    |

|-----|-----|-----|---------------|-------|---|---|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_5$ | $E_6$ | W     |       |                       |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D     | -     | -     | -     | -     | -     | $E_1$ | $E_2$ | <b>E</b> <sub>3</sub> |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F     | D     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |       |                       |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |       | F     | D     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |                       |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |       |       | F     | D     | -     | -     | -     | $E_1$ | E <sub>2</sub>        |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |       |       |       | F     | D     | -     | -     | -     | -                     |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 0     | у   |       |

|   |   | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| a | 1 | ~      | 2     | 1        | ~   | 4     |  |

| b | 1 | ~      | 2     | 1        | ~   | 6     |  |

| С | 1 | ~      | 8     | 1        | ~   | 9     |  |

| d | 0 | a      |       | 0        | у   |       |  |

|   |   | Source | 1     | Source 2 |     |       |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|

|   | V | Tag    | Value | V        | Tag | Value |  |  |

| х | 1 | 2      | 1     | 1        | 2   | 2     |  |  |

| У | 1 | 2      | 8     | 1        | 2   | 17    |  |  |

| Z |   |        |       |          |     |       |  |  |

| t |   |        |       |          |     |       |  |  |

Cycle 1 2 3 4 5 6 7 8 9 10 11 12

MUL R1, R2  $\rightarrow$  R3 ADD R3, R4  $\rightarrow$  R5 ADD R2, R6  $\rightarrow$  R7 ADD R8, R9  $\rightarrow$  R10 MUL R7, R10  $\rightarrow$  R11 ADD R5, R11  $\rightarrow$  R5

Broadcast and Update

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 0     | у   |       |

|   | Ç | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| а | 1 | 2      | 2     | 1        | 2   | 4     |  |

| b | 1 | 2      | 2     | 1        | >   | 6     |  |

| С | 1 | 2      | 8     | 1        | >   | 9     |  |

| d | 1 | 2      | 6     | 0        | у   |       |  |

|   |   | Source | 1     | Source 2 |     |       |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|

|   | V | Tag    | Value | V        | Tag | Value |  |  |

| х | 1 | >      | 1     | 1        | ~   | 2     |  |  |

| У | 1 | 2      | 8     | 1        | ~   | 17    |  |  |

| Z |   |        |       |          |     |       |  |  |

| t |   |        |       |          |     |       |  |  |

```

Cycle 1

8

9

10 11 12 13

5

6

7

MUL R1, R2 → R3

D

E_1 E_2 E_3 E_4 E_5 E_6

ADD R3, R4 \rightarrow R5

E_1 E_2 E_3 E_4 W

D \quad E_1 \quad E_2 \quad E_3 \quad E_4

ADD R2, R6 \rightarrow R7

ADD R8, R9 → R10

E_1 E_2 E_3 E_4

MUL R7, R10 \rightarrow R11

- - E<sub>1</sub> E<sub>2</sub> E<sub>3</sub> E<sub>4</sub>

ADD R5, R11 → R5

```

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 0     | У   |       |

|   | 9 | Source | 1     | 9 | Source | 2     |

|---|---|--------|-------|---|--------|-------|

|   | V | Tag    | Value | V | Tag    | Value |

| а | 1 | 2      | 2     | 1 | 2      | 4     |

| b | 1 | 2      | 2     | 1 | 2      | 6     |

| C | 1 | 2      | 8     | 1 | ~      | 9     |

| d | 1 | 2      | 6     | 0 | у      |       |

|   |   | Source | 1     | Source 2 |     |       |  |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|--|

|   | V | Tag    | Value | V        | Tag | Value |  |  |  |

| х | 1 | 2      | 1     | 1        | 2   | 2     |  |  |  |

| У | 1 | >      | 8     | 1        | ~   | 17    |  |  |  |

| Z |   |        |       |          |     |       |  |  |  |

| t |   |        |       |          |     |       |  |  |  |

|     |     |     |               | Cycle | 1 | 2 | 3              | 4     | 5     | 6     | /              | 8     | 9     | 10    | 11    | 12    | 13    | 14                    |

|-----|-----|-----|---------------|-------|---|---|----------------|-------|-------|-------|----------------|-------|-------|-------|-------|-------|-------|-----------------------|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | E <sub>1</sub> | $E_2$ | $E_3$ | $E_4$ | E <sub>5</sub> | $E_6$ | W     |       |       |       |       |                       |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D              | -     | -     | -     | -              | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |                       |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F              | D     | $E_1$ | $E_2$ | $E_3$          | $E_4$ | W     |       |       |       |       |                       |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |                | F     | D     | $E_1$ | $E_2$          | $E_3$ | $E_4$ | W     |       |       |       |                       |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |                |       | F     | D     | -              | -     | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | <b>E</b> <sub>5</sub> |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |                |       |       | F     | D              | -     | -     | -     | -     | -     | -     | -                     |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 0     | У   |       |

|   |   | Source | 1     | •,       | Source | 2     |

|---|---|--------|-------|----------|--------|-------|

|   | V | Tag    | Value | <b>V</b> | Tag    | Value |

| a | 1 | ~      | 2     | 1        | 2      | 4     |

| b | 1 | ~      | 2     | 1        | 2      | 6     |

| С | 1 | ~      | 8     | 1        | ~      | 9     |

| d | 1 | ~      | 6     | 0        | у      |       |

|   |   | Source | 1     | Source 2 |     |       |  |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|--|

|   | V | Tag    | Value | V        | Tag | Value |  |  |  |

| х | 1 | 2      | 1     | 1        | ~   | 2     |  |  |  |

| У | 1 | 2      | 8     | 1        | ~   | 17    |  |  |  |

| Z |   |        |       |          |     |       |  |  |  |

| t |   |        | ·     |          |     |       |  |  |  |

|     |     |     |               | Cycle | 1 | 2 | 3              | 4     | 5     | 6     | 7                     | 8     | 9     | 10    | 11    | 12    | 13    | 14    | 15    |                      |

|-----|-----|-----|---------------|-------|---|---|----------------|-------|-------|-------|-----------------------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | E <sub>1</sub> | $E_2$ | $E_3$ | $E_4$ | <b>E</b> <sub>5</sub> | $E_6$ | W     |       |       |       |       |       |       |                      |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D              | -     | -     | -     | -                     | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |       |       |                      |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F              | D     | $E_1$ | $E_2$ | $E_3$                 | $E_4$ | W     |       |       |       |       |       |       |                      |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |                | F     | D     | $E_1$ | $E_2$                 | $E_3$ | $E_4$ | W     |       |       |       |       |       |                      |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |                |       | F     | D     | -                     | -     | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_5$ | $E_6$ | Broadcast and Update |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |                |       |       | F     | D                     | -     | -     | -     | -     | -     | -     | -     | -     |                      |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

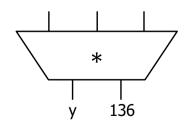

| R11      | 1     |     | 136   |

|   | Ç | Source | 1     |   | Source | 2     |

|---|---|--------|-------|---|--------|-------|

|   | V | Tag    | Value | V | Tag    | Value |

| а | 1 | 2      | 2     | 1 | ~      | 4     |

| b | 1 | >      | 2     | 1 | ~      | 6     |

| С | 1 | >      | 8     | 1 | ~      | 9     |

| d | 1 | ~      | 6     | 1 | 2      | 136   |

| + |  |

|---|--|

|   |  |

|   |   | Source | 1     | Source 2 |     |       |  |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|--|

|   | V | Tag    | Value | V        | Tag | Value |  |  |  |

| х | 1 | 2      | 1     | 1        | ~   | 2     |  |  |  |

| У | 1 | 2      | 8     | 1        | ~   | 17    |  |  |  |

| Z |   |        |       |          |     |       |  |  |  |

| t |   |        | ·     |          |     |       |  |  |  |

ADD in RS d is ready to execute in the next cycle!

```

Cycle 1

9 10 11 12 13 14 15 16

5

6

8

MUL R1, R2 → R3

D

\mathsf{E}_1 \mathsf{E}_2 \mathsf{E}_3 \mathsf{E}_4 \mathsf{E}_5 \mathsf{E}_6

E_1 E_2 E_3 E_4 W

ADD R3, R4 \rightarrow R5

D \quad E_1 \quad E_2 \quad E_3 \quad E_4

ADD R2, R6 \rightarrow R7

F

D

E_1 E_2 E_3 E_4

W

ADD R8, R9 \rightarrow R10

MUL R7, R10 \rightarrow R11

- - E<sub>1</sub> E<sub>2</sub> E<sub>3</sub> E<sub>4</sub> E<sub>5</sub> E<sub>6</sub>

ADD R5, R11 \rightarrow R5

```

7

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 1     |     | 136   |

|   |   | Source | 1     |                                     | Source    | 2   |  |  |  |

|---|---|--------|-------|-------------------------------------|-----------|-----|--|--|--|

|   | V | Tag    | Value | V                                   | Tag Value |     |  |  |  |

| a | 1 | 2      | 2     | Source 2  V Tag  1 ~  1 ~  1 ~  1 ~ | 4         |     |  |  |  |

| b | 1 | >      | 2     | 1                                   | >         | 6   |  |  |  |

| С | 1 | >      | 8     | 1                                   | >         | 9   |  |  |  |

| d | 1 | ~      | 6     | 1                                   | 2         | 136 |  |  |  |

|   |   | Source | 1     |   | Source 2 |       |  |  |

|---|---|--------|-------|---|----------|-------|--|--|

|   | V | Tag    | Value | V | Tag      | Value |  |  |

| х | 1 | 2      | 1     | 1 | 2        | 2     |  |  |

| У | 1 | >      | 8     | 1 | ~        | 17    |  |  |

| Z |   |        |       |   |          |       |  |  |

| t |   |        |       |   |          |       |  |  |

|     |     |     |               | Cycle | 1 | 2 | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | 11    | 12    | 13    | 14      | 15    | 16    | 17             |  |

|-----|-----|-----|---------------|-------|---|---|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------|-------|-------|----------------|--|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_5$ | $E_6$ | W     |       |       |       |       |         |       |       |                |  |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D     | -     | -     | -     | -     | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |         |       |       |                |  |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F     | D     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |       |       |       |       |         |       |       |                |  |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |       | F     | D     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |       |       |       |         |       |       |                |  |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |       |       | F     | D     | -     | -     | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_{5}$ | $E_6$ | W     |                |  |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |       |       |       | F     | D     | -     | -     | -     | -     | -     | -     | -       | -     | $E_1$ | E <sub>2</sub> |  |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 1     |     | 136   |

|   |   | Source | 1     | Source 2  alue V Tag Value 2 1 ~ 4 2 1 ~ 6 8 1 ~ 9 6 1 ~ 136 |     |       |

|---|---|--------|-------|--------------------------------------------------------------|-----|-------|

|   | V | Tag    | Value | <b>V</b>                                                     | Tag | Value |

| a | 1 | 2      | 2     | 1                                                            | 2   | 4     |

| b | 1 | 2      | 2     | 1                                                            | 2   | 6     |

| С | 1 | ~      | 8     | 1                                                            | 2   | 9     |

| d | 1 | ~      | 6     | 1                                                            | ~   | 136   |

|   |   | Source | 1     | Source 2 |     |       |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|

|   | V | Tag    | Value | V        | Tag | Value |  |  |

| Х | 1 | 2      | 1     | 1        | 2   | 2     |  |  |

| У | 1 | >      | 8     | 1        | ~   | 17    |  |  |

| Z |   |        |       |          |     |       |  |  |

| t |   |        |       |          |     |       |  |  |

9 Cycle 1 MUL R1, R2 → R3 D  $E_1$   $E_2$   $E_3$   $E_4$   $E_5$   $E_6$  $E_1$   $E_2$   $E_3$   $E_4$  WADD R3, R4  $\rightarrow$  R5  $D \quad E_1 \quad E_2 \quad E_3 \quad E_4$ ADD R2, R6  $\rightarrow$  R7  $E_1$   $E_2$   $E_3$   $E_4$ W ADD R8, R9  $\rightarrow$  R10 MUL R7, R10  $\rightarrow$  R11  $- \quad - \quad \mathsf{E_1} \quad \mathsf{E_2} \quad \mathsf{E_3} \quad \mathsf{E_4} \quad \mathsf{E_5} \quad \mathsf{E_6}$  $E_1$   $E_2$   $E_3$ ADD R5, R11  $\rightarrow$  R5

6

7

8

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 1     |     | 136   |

|   | Ç | Source | 1     |   | Source    | 2   |  |  |  |

|---|---|--------|-------|---|-----------|-----|--|--|--|

|   | V | Tag    | Value | V | Tag Value |     |  |  |  |

| а | 1 | 2      | 2     | 1 | 2         | 4   |  |  |  |

| b | 1 | >      | 2     | 1 | ٧         | 6   |  |  |  |

| С | 1 | >      | 8     | 1 | ٧         | 9   |  |  |  |

| d | 1 | ~      | 6     | 1 | ~         | 136 |  |  |  |

|   |   | Source | 1     | Source 2 |     |       |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|

|   | V | Tag    | Value | V        | Tag | Value |  |  |

| х | 1 | 2      | 1     | 1        | 2   | 2     |  |  |

| У | 1 | >      | 8     | 1        | ~   | 17    |  |  |

| Z |   |        |       |          |     |       |  |  |

| t | · | ·      |       |          |     |       |  |  |

10 11 12 13 14 15 16 17 18

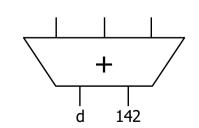

Cycle 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

| MUL | R1, | R2  | $\rightarrow$ | R3  |

|-----|-----|-----|---------------|-----|

| ADD | R3, | R4  | $\rightarrow$ | R5  |

| ADD | R2, | R6  | $\rightarrow$ | R7  |

| ADD | R8, | R9  | $\rightarrow$ | R10 |

| MUL | R7, | R10 | $\rightarrow$ | R11 |

| ADD | R5, | R11 | $\rightarrow$ | R5  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                            |   |       |       |       |       |         |       |       |       |       |       |       |         |       |       |       |       |                |

|-------------------------------------------------------------------------------------------------|---|-------|-------|-------|-------|---------|-------|-------|-------|-------|-------|-------|---------|-------|-------|-------|-------|----------------|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                           | D | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_{5}$ | $E_6$ | W     |       |       |       |       |         |       |       |       |       |                |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                           | F | D     | -     | -     | -     | -       | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |         |       |       |       |       |                |

| F D E <sub>1</sub> E <sub>2</sub> E <sub>3</sub> E <sub>4</sub> E <sub>5</sub> E <sub>6</sub> W |   | F     | D     | $E_1$ | $E_2$ | $E_3$   | $E_4$ | W     |       |       |       |       |         |       |       |       |       |                |

|                                                                                                 |   |       | F     | D     | $E_1$ | $E_2$   | $E_3$ | $E_4$ | W     |       |       |       |         |       |       |       |       |                |

| F D E <sub>1</sub> E <sub>2</sub> E <sub>3</sub> E <sub>4</sub>                                 |   |       |       | F     | D     | -       | -     | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_{5}$ | $E_6$ | W     |       |       |                |

|                                                                                                 |   |       |       |       | F     | D       | -     | -     | -     | -     | -     | -     | -       | -     | $E_1$ | $E_2$ | $E_3$ | E <sub>4</sub> |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 1     |     | 142   |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 1     |     | 136   |

|   | 9 | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| а | 1 | 2      | 2     | 1        | ~   | 4     |  |

| b | 1 | 2      | 2     | 1        | ~   | 6     |  |

| С | 1 | 2      | 8     | 1        | ~   | 9     |  |

| d | 1 | ~      | 6     | 1        | ~   | 136   |  |

|   |   | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| Х | 1 | 2      | 1     | 1        | 2   | 2     |  |

| У | 1 | >      | 8     | 1        | ~   | 17    |  |

| Z |   |        |       |          |     |       |  |

| t |   |        |       |          |     |       |  |

Broadcast and Update

Cycle 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

| MUL | R1, | R2  | $\rightarrow$ | R3  |

|-----|-----|-----|---------------|-----|

| ADD | R3, | R4  | $\rightarrow$ | R5  |

| ADD | R2, | R6  | $\rightarrow$ | R7  |

| ADD | R8, | R9  | $\rightarrow$ | R10 |

| MUL | R7, | R10 | $\rightarrow$ | R11 |

| ADD | R5, | R11 | $\rightarrow$ | R5  |

F

| D | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_{5}$ | $E_6$ | W     |       |       |       |       |         |       |    |    |    |    |   |

|---|-------|-------|-------|-------|---------|-------|-------|-------|-------|-------|-------|---------|-------|----|----|----|----|---|

| F | D     | -     | -     | -     | -       | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | W     |         |       |    |    |    |    |   |

|   | F     | D     | $E_1$ | $E_2$ | $E_3$   | $E_4$ | W     |       |       |       |       |         |       |    |    |    |    |   |

|   |       | F     | D     | $E_1$ | $E_2$   | $E_3$ | $E_4$ | W     |       |       |       |         |       |    |    |    |    |   |

|   |       |       | F     | D     | -       | -     | -     | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_{5}$ | $E_6$ | W  |    |    |    |   |

|   |       |       |       | F     | D       | _     | _     | _     | _     | _     | _     | _       | _     | E₁ | E۵ | E۶ | Ε₄ | W |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 1     |     | 2     |

| R4       | 1     |     | 4     |

| R5       | 1     |     | 142   |

| R6       | 1     |     | 6     |

| R7       | 1     |     | 8     |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 1     |     | 17    |

| R11      | 1     |     | 136   |

|   |   | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| a | 1 | 2      | 2     | 1        | 2   | 4     |  |

| b | 1 | >      | 2     | 1        | >   | 6     |  |

| С | 1 | >      | 8     | 1        | >   | 9     |  |

| d | 1 | ~      | 6     | 1        | 2   | 136   |  |

|   |   | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | ٧        | Tag | Value |  |

| х | 1 | 2      | 1     | 1        | ~   | 2     |  |

| У | 1 | 2      | 8     | 1        | 2   | 17    |  |

| Z |   |        |       |          |     |       |  |

| t |   |        | ·     |          |     |       |  |

### Some Questions

- What is needed in hardware to perform tag broadcast and value capture?

- → make a value valid

- → wake up an instruction

- Does the tag have to be the ID of the Reservation Station Entry?

- What can potentially become the critical path?

- □ Tag broadcast → value capture → instruction wake up

- How can you reduce the potential critical paths?

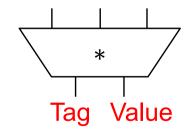

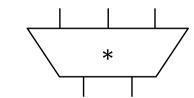

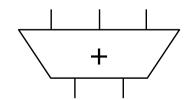

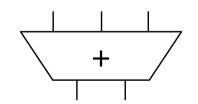

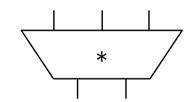

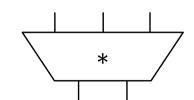

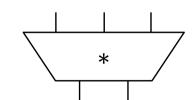

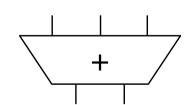

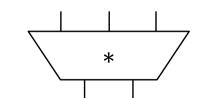

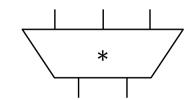

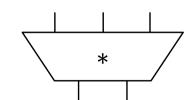

### Dataflow Graph for Our Example

```

MUL R3 \leftarrow R1, R2

ADD R5 \leftarrow R3, R4

ADD R7 \leftarrow R2, R6

ADD R10 \leftarrow R8, R9

MUL R11 \leftarrow R7, R10

ADD R5 \leftarrow R5, R11

```

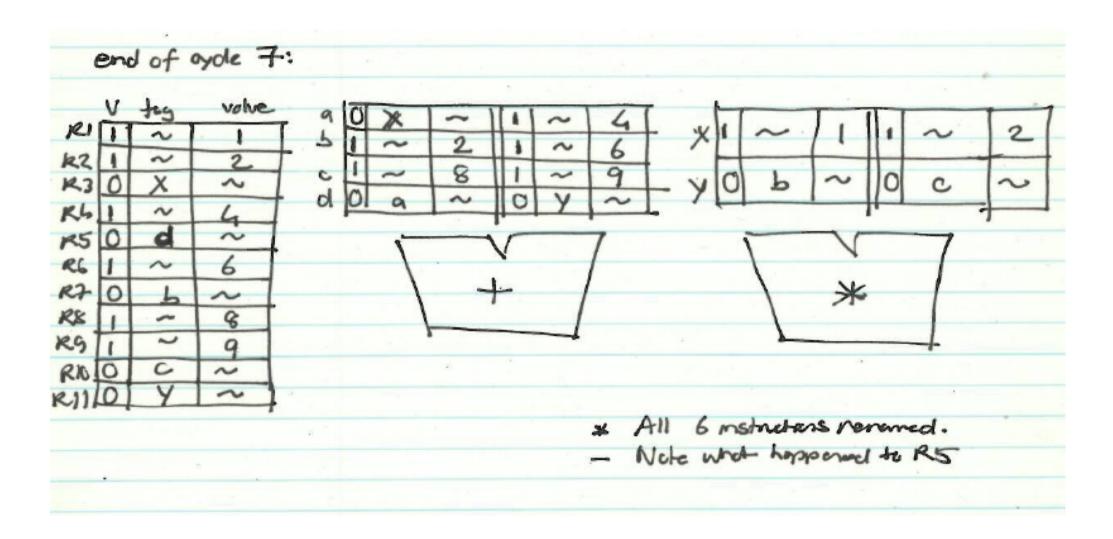

# State of RAT and RS in Cycle 7

# State of RAT and RS in Cycle 7

|     |     |     |               | Cycle | 1 | 2 | 3     | 4     | 5     | 6     | 7                     |

|-----|-----|-----|---------------|-------|---|---|-------|-------|-------|-------|-----------------------|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | $E_1$ | $E_2$ | $E_3$ | $E_4$ | <b>E</b> <sub>5</sub> |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D     | -     | -     | -     | -                     |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F     | D     | $E_1$ | $E_2$ | $E_3$                 |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |       | F     | D     | $E_1$ | $E_2$                 |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |       |       | F     | D     | -                     |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |       |       |       | F     | D                     |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 0     | Х   |       |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 0     | b   |       |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 0     | С   |       |

| R11      | 0     | у   |       |

|   |   | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | ٧        | Tag | Value |  |

| а | 0 | Х      |       | 1        | 2   | 4     |  |

| b | 1 | 2      | 2     | 1        | ~   | 6     |  |

| С | 1 | 2      | 8     | 1        | 2   | 9     |  |

| d | 0 | a      |       | 0        | у   |       |  |

|   |   | Source | 1     | Source 2 |     |       |  |

|---|---|--------|-------|----------|-----|-------|--|

|   | V | Tag    | Value | V        | Tag | Value |  |

| х | 1 | 2      | 1     | 1        | ~   | 2     |  |

| У | 0 | b      |       | 0        | С   |       |  |

| Z |   |        |       |          |     |       |  |

| t |   |        | ·     |          |     |       |  |

### Corresponding Dataflow Graph (Reverse Engineered)

## Some More Questions (Design Choices)

- When is a reservation station entry deallocated?

- Should the reservation stations be dedicated to each functional unit or global across functional units?

- Centralized vs. Distributed: What are the tradeoffs?

- Should reservation stations and ROB store data values or should there be a centralized physical register file where all data values are stored?

- What are the tradeoffs?

- Timing: Exactly when does an instruction broadcast its tag?

- Many other design choices for OoO engines

## For You: An Exercise, w/ Precise Exceptions

```

MUL R3 \leftarrow R1, R2

ADD R5 \leftarrow R3, R4

ADD R7 \leftarrow R2, R6

ADD R10 \leftarrow R8, R9

MUL R11 \leftarrow R7, R10

ADD R5 \leftarrow R5, R11

```

- Assume ADD (4 cycle execute), MUL (6 cycle execute)

- Assume one adder and one multiplier

- How many cycles

- in a non-pipelined machine

- in an in-order-dispatch pipelined machine with reorder buffer (no forwarding and full forwarding)

- in an out-of-order dispatch pipelined machine with reorder buffer (full forwarding)

#### Out-of-Order Execution with Precise Exceptions

- Idea: Use a reorder buffer to reorder instructions before committing them to architectural state

- An instruction updates the RAT when it completes execution

- Also called frontend register file

- An instruction updates a separate architectural register file when it retires

- i.e., when it is the oldest in the machine and has completed execution

- In other words, the architectural register file is always updated in program order

- On an exception: flush pipeline, copy architectural register file into frontend register file

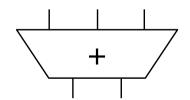

#### Out-of-Order Execution with Precise Exceptions

- Hump 1: Reservation stations (scheduling window)

- Hump 2: Reordering (reorder buffer, aka instruction window or active window)

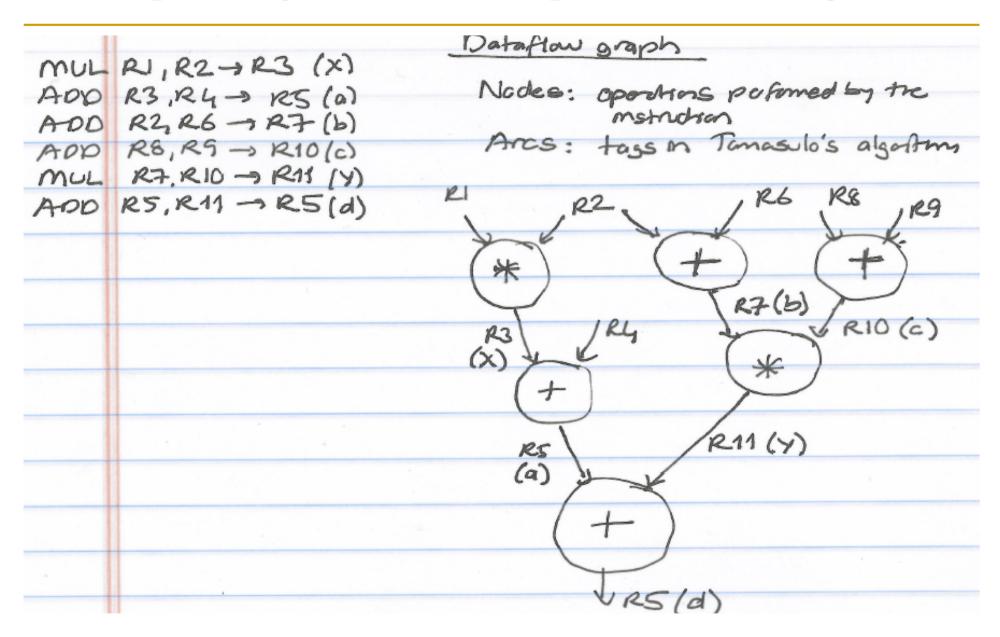

## Two Humps in a Modern Pipeline

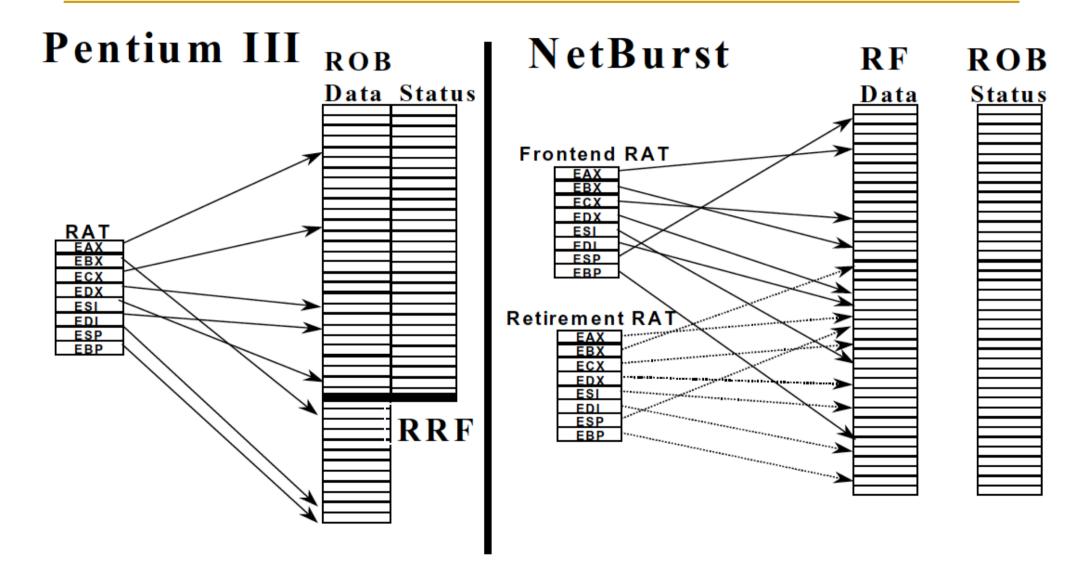

#### Modern OoO Execution w/ Precise Exceptions

- Most modern processors use the following

- Reorder buffer to support in-order retirement of instructions

- A single register file to store all registers

- Both speculative and architectural registers

- INT and FP are still separate

- Two register maps

- □ Future/frontend register map → used for renaming

- □ Architectural register map → used for maintaining precise state

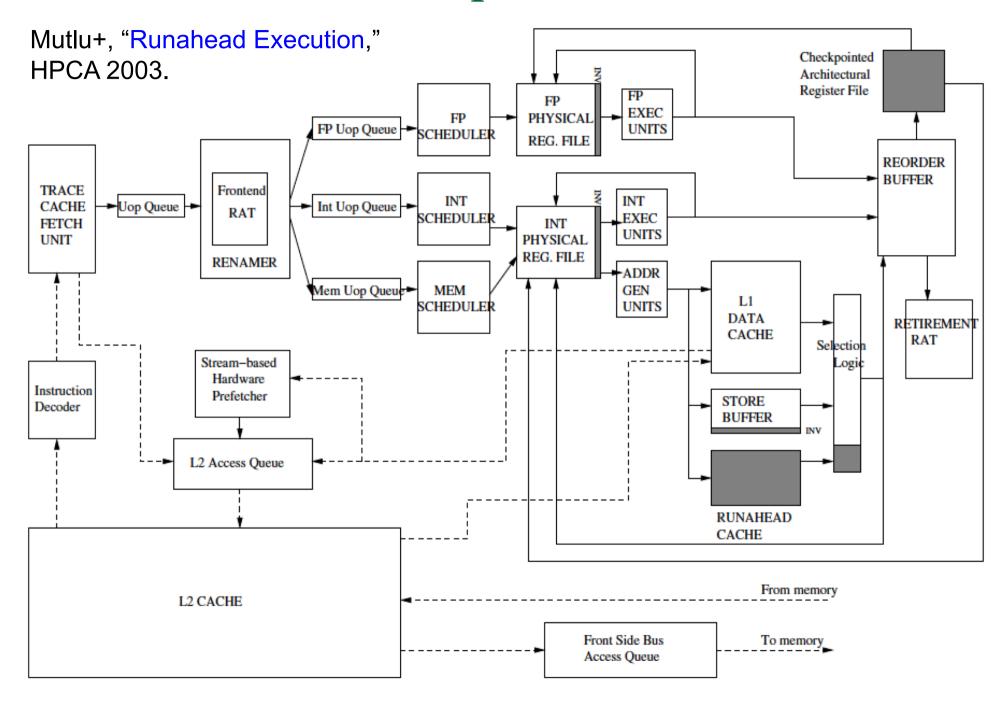

## An Example from Modern Processors

Boggs et al., "The Microarchitecture of the Pentium 4 Processor," Intel Technology Journal, 2001.

## Enabling OoO Execution, Revisited

- 1. Link the consumer of a value to the producer

- Register renaming: Associate a "tag" with each data value

- 2. Buffer instructions until they are ready

- Insert instruction into reservation stations after renaming

- 3. Keep track of readiness of source values of an instruction

- Broadcast the "tag" when the value is produced

- □ Instructions compare their "source tags" to the broadcast tag

→ if match, source value becomes ready

- 4. When all source values of an instruction are ready, dispatch the instruction to functional unit (FU)

- Wakeup and select/schedule the instruction

## Summary of OOO Execution Concepts

- Register renaming eliminates false dependencies, enables linking of producer to consumers

- Buffering in reservation stations enables the pipeline to move for independent instructions

- Tag broadcast enables communication (of readiness of produced value) between instructions

- Wakeup and select enables out-of-order dispatch

#### OOO Execution: Restricted Dataflow

- An out-of-order engine dynamically builds the dataflow graph of a piece of the program

- which piece?

- The dataflow graph is limited to the instruction window

- Instruction window: all decoded but not yet retired instructions

- Can we do it for the whole program?

- Why would we like to?

- In other words, how can we have a large instruction window?

- Can we do it efficiently with Tomasulo's algorithm?

## Recall: Dataflow Graph for Our Example

```

MUL R3 \leftarrow R1, R2

ADD R5 \leftarrow R3, R4

ADD R7 \leftarrow R2, R6

ADD R10 \leftarrow R8, R9

MUL R11 \leftarrow R7, R10

ADD R5 \leftarrow R5, R11

```

## Recall: State of RAT and RS in Cycle 7

## Recall: State of RAT and RS in Cycle 7

|     |     |     |               | Cycle | 1 | 2 | 3     | 4     | 5     | 6              | 7     |

|-----|-----|-----|---------------|-------|---|---|-------|-------|-------|----------------|-------|

| MUL | R1, | R2  | $\rightarrow$ | R3    | F | D | $E_1$ | $E_2$ | $E_3$ | $E_4$          | $E_5$ |

| ADD | R3, | R4  | $\rightarrow$ | R5    |   | F | D     | -     | -     | -              | -     |

| ADD | R2, | R6  | $\rightarrow$ | R7    |   |   | F     | D     | $E_1$ | $E_2$          | $E_3$ |

| ADD | R8, | R9  | $\rightarrow$ | R10   |   |   |       | F     | D     | E <sub>1</sub> | $E_2$ |

| MUL | R7, | R10 | $\rightarrow$ | R11   |   |   |       |       | F     | D              | -     |

| ADD | R5, | R11 | $\rightarrow$ | R5    |   |   |       |       |       | F              | D     |

| Register | Valid | Tag | Value |

|----------|-------|-----|-------|

| R1       | 1     |     | 1     |

| R2       | 1     |     | 2     |

| R3       | 0     | Х   |       |

| R4       | 1     |     | 4     |

| R5       | 0     | d   |       |

| R6       | 1     |     | 6     |

| R7       | 0     | b   |       |

| R8       | 1     |     | 8     |

| R9       | 1     |     | 9     |

| R10      | 0     | С   |       |

| R11      | 0     | У   |       |

|   | Ç | Source | 1     | Source 2 |     |       |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|

|   | V | Tag    | Value | V        | Tag | Value |  |  |

| а | 0 | х      |       | 1        | ~   | 4     |  |  |

| b | 1 | >      | 2     | 1        | ~   | 6     |  |  |

| С | 1 | >      | 8     | 1        | ~   | 9     |  |  |

| d | 0 | a      |       | 0        | У   |       |  |  |

|   |   | Source | 1     | Source 2 |     |       |  |  |

|---|---|--------|-------|----------|-----|-------|--|--|

|   | V | Tag    | Value | V        | Tag | Value |  |  |

| х | 1 | 2      | 1     | 1        | ~   | 2     |  |  |

| У | 0 | b      |       | 0        | С   |       |  |  |

| Z |   |        |       |          |     |       |  |  |

| t |   |        |       |          |     |       |  |  |

## Recall: Dataflow Graph

### Questions to Ponder

- Why is OoO execution beneficial?

- What if all operations take a single cycle?

- Latency tolerance: OoO execution tolerates the latency of multi-cycle operations by executing independent operations concurrently

- What if an instruction takes 1000 cycles?

- How large of an instruction window do we need to continue decoding?

- How many cycles of latency can OoO tolerate?

- What limits the latency tolerance scalability of Tomasulo's algorithm?

- Instruction window size: how many decoded but not yet retired instructions you can keep in the machine.

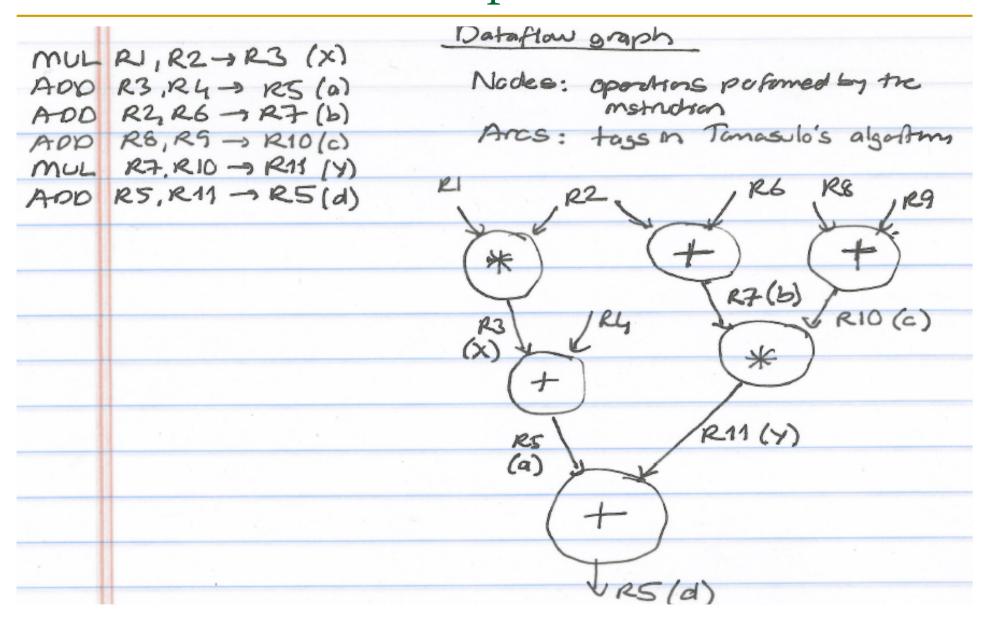

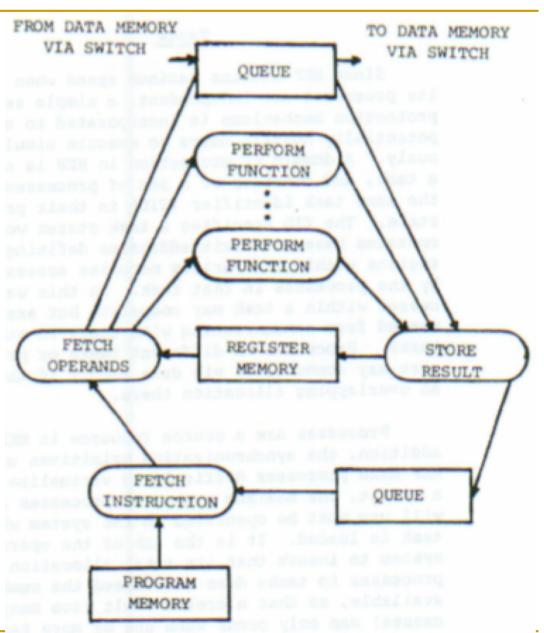

## General Organization of an OOO Processor

Smith and Sohi, "The Microarchitecture of Superscalar Processors," Proc. IEEE, Dec. 1995.

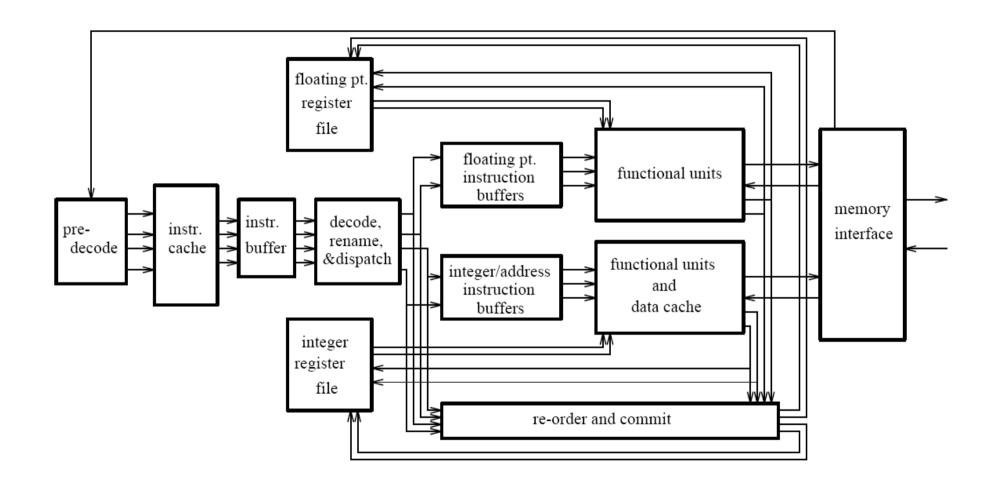

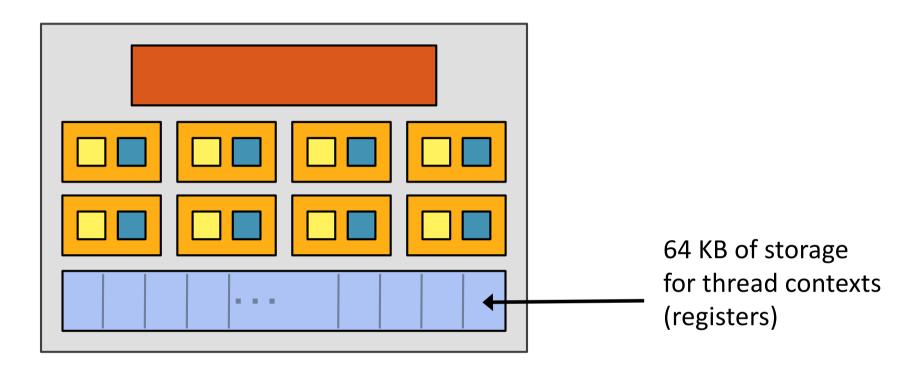

## A Modern OoO Design: Intel Pentium 4

Figure 4: Pentium® 4 processor microarchitecture

Boggs et al., "The Microarchitecture of the Pentium 4 Processor," Intel Technology Journal, 2001.

## Intel Pentium 4 Simplified

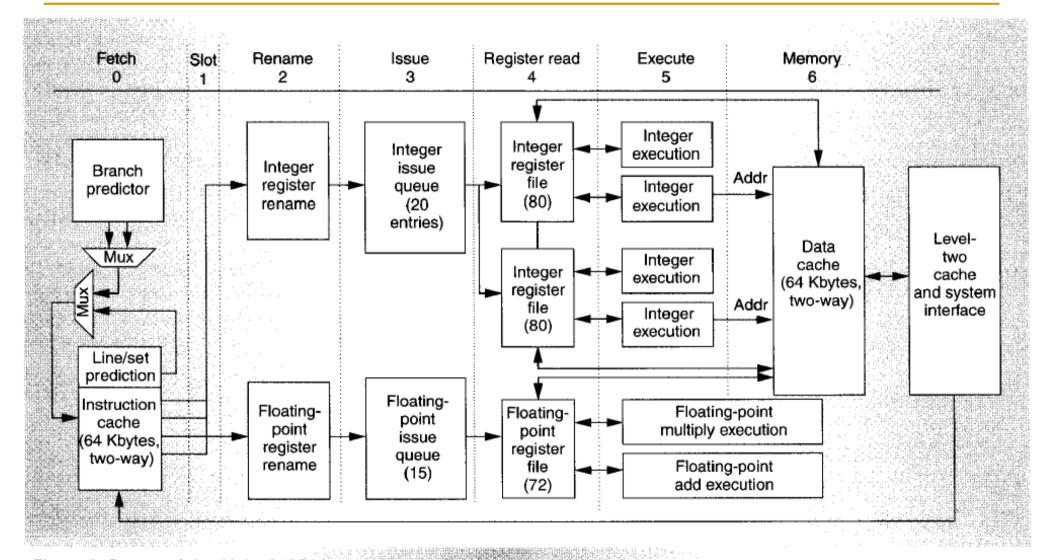

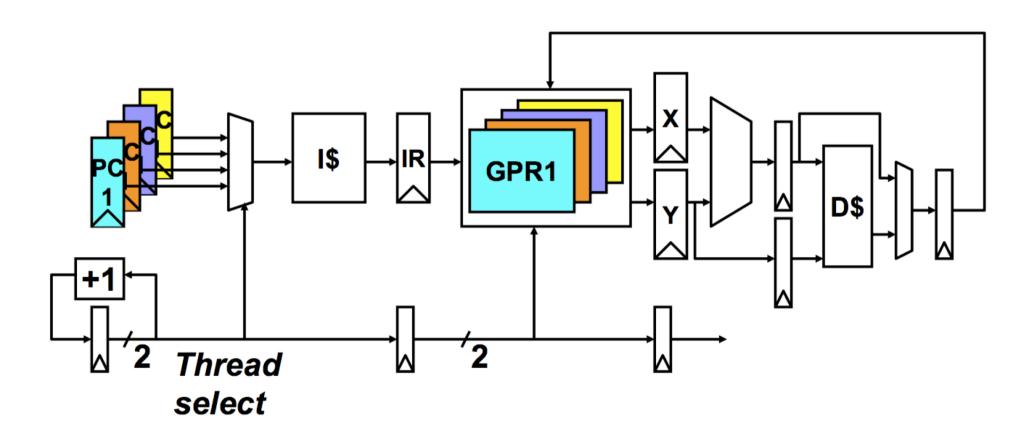

## Alpha 21264

Figure 2. Stages of the Alpha 21264 instruction pipeline.

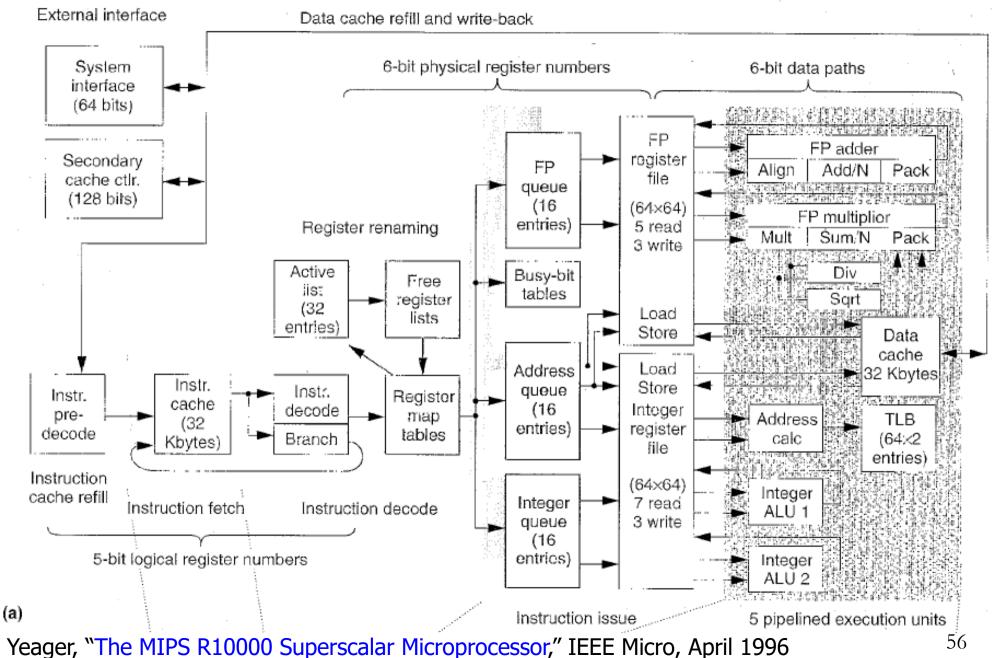

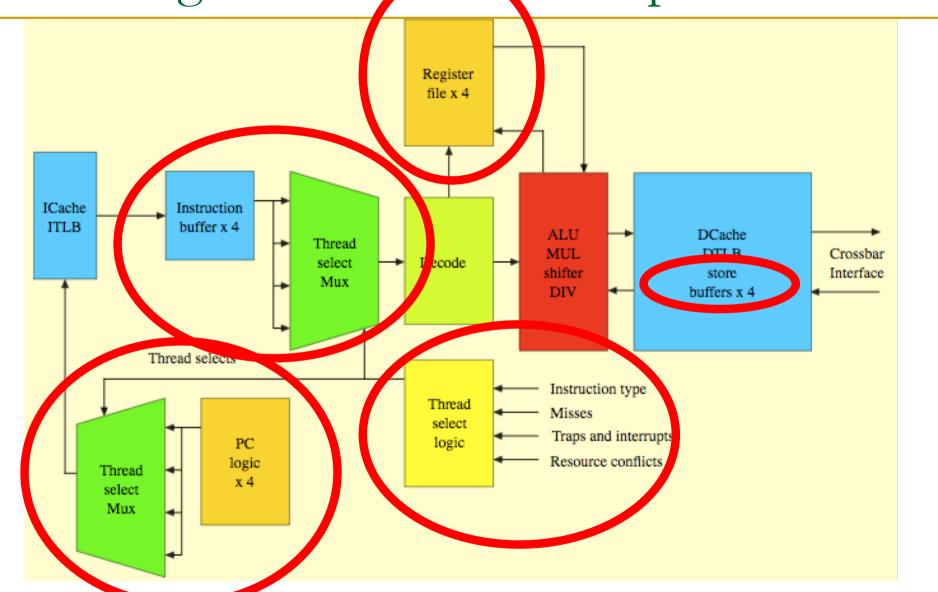

#### MIPS R10000

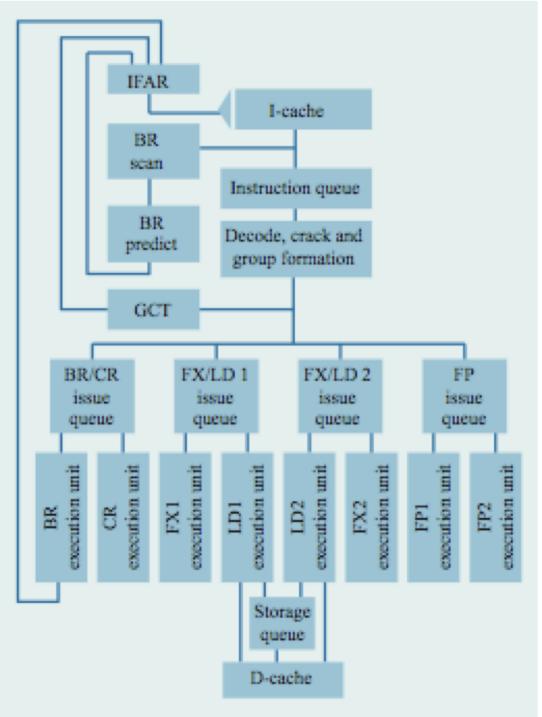

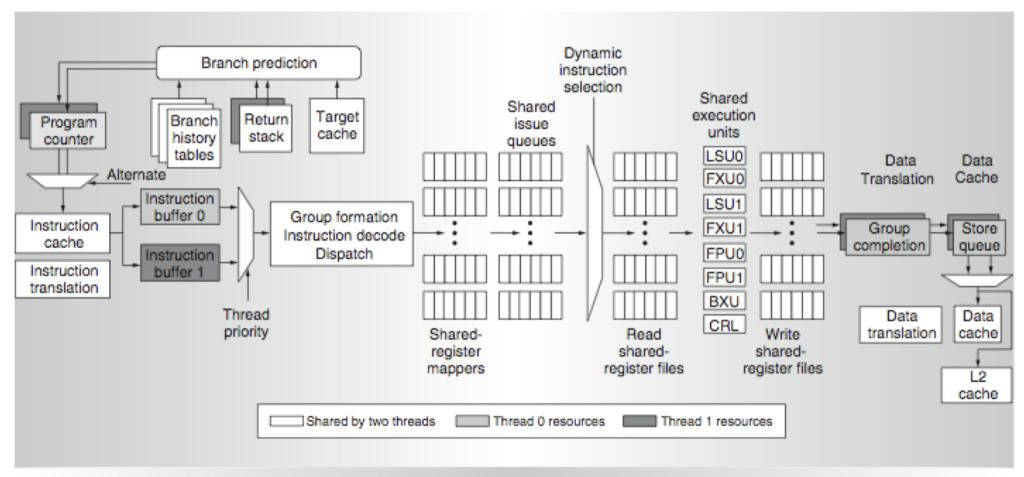

#### IBM POWER4

Tendler et al., "POWER4 system microarchitecture," IBM J R&D, 2002.

#### IBM POWER4

- 2 cores, out-of-order execution

- 100-entry instruction window in each core

- 8-wide instruction fetch, issue, execute

- Large, local+global hybrid branch predictor

- 1.5MB, 8-way L2 cache

- Aggressive stream based prefetching

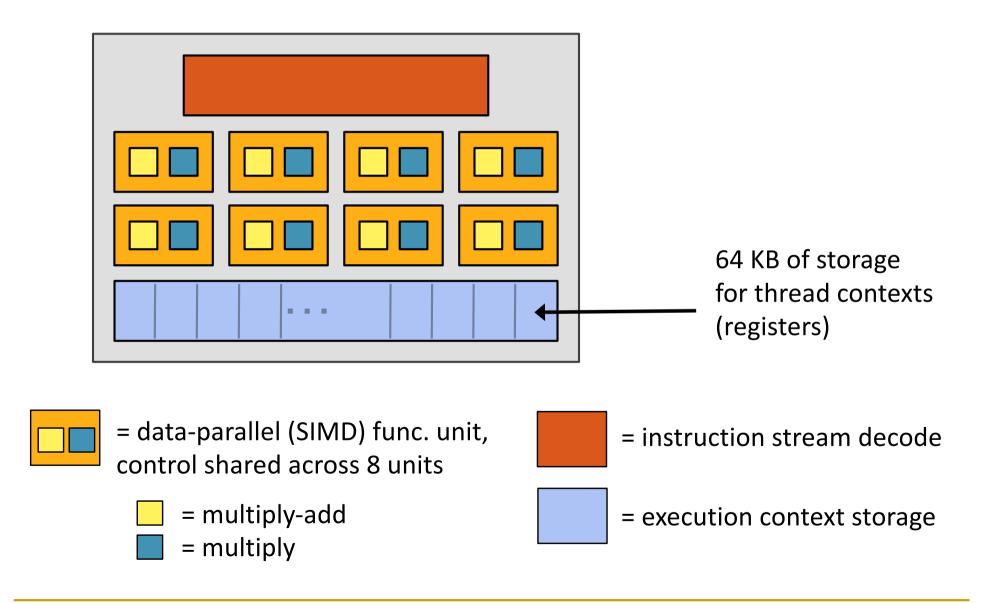

#### IBM POWER5

Kalla et al., "IBM Power5 Chip: A Dual-Core Multithreaded Processor," IEEE Micro 2004.

Figure 4. Power5 instruction data flow (BXU = branch execution unit and CRL = condition register logical execution unit).

## Handling Out-of-Order Execution of Loads and Stores

## Registers versus Memory

- So far, we considered mainly registers as part of state

- What about memory?

- What are the fundamental differences between registers and memory?

- Register dependences known statically memory dependences determined dynamically

- Register state is small memory state is large

- Register state is not visible to other threads/processors memory state is shared between threads/processors (in a shared memory multiprocessor)

## Memory Dependence Handling (I)

- Need to obey memory dependences in an out-of-order machine

- and need to do so while providing high performance

- Observation and Problem: Memory address is not known until a load/store executes

- Corollary 1: Renaming memory addresses is difficult

- Corollary 2: Determining dependence or independence of loads/stores has to be handled after their (partial) execution

- Corollary 3: When a load/store has its address ready, there may be older/younger stores/loads with unknown addresses in the machine

## Memory Dependence Handling (II)

- When do you schedule a load instruction in an OOO engine?

- Problem: A younger load can have its address ready before an older store's address is known

- Known as the memory disambiguation problem or the unknown address problem

#### Approaches

- Conservative: Stall the load until all previous stores have computed their addresses (or even retired from the machine)

- Aggressive: Assume load is independent of unknown-address stores and schedule the load right away

- Intelligent: Predict (with a more sophisticated predictor) if the load is dependent on any unknown address store

## Handling of Store-Load Dependences

- A load's dependence status is not known until all previous store addresses are available.

- How does the OOO engine detect dependence of a load instruction on a previous store?

- Option 1: Wait until all previous stores committed (no need to check for address match)

- Option 2: Keep a list of pending stores in a store buffer and check whether load address matches a previous store address

- How does the OOO engine treat the scheduling of a load instruction wrt previous stores?

- Option 1: Assume load dependent on all previous stores

- Option 2: Assume load independent of all previous stores

- Option 3: Predict the dependence of a load on an outstanding store

## Memory Disambiguation (I)

- Option 1: Assume load is dependent on all previous stores

- + No need for recovery

- -- Too conservative: delays independent loads unnecessarily

- Option 2: Assume load is independent of all previous stores

- + Simple and can be common case: no delay for independent loads

- -- Requires recovery and re-execution of load and dependents on misprediction

- Option 3: Predict the dependence of a load on an outstanding store

- + More accurate. Load store dependencies persist over time

- -- Still requires recovery/re-execution on misprediction

- Alpha 21264: Initially assume load independent, delay loads found to be dependent

- Moshovos et al., "Dynamic speculation and synchronization of data dependences," ISCA 1997.

- Chrysos and Emer, "Memory Dependence Prediction Using Store Sets," ISCA 1998.

## Memory Disambiguation (II)

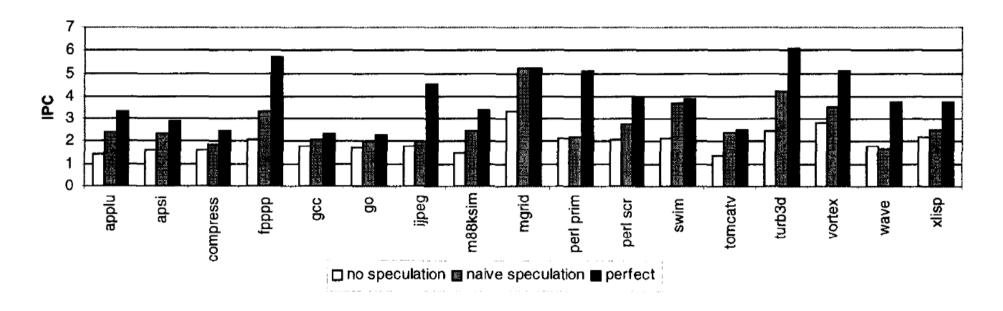

Chrysos and Emer, "Memory Dependence Prediction Using Store Sets," ISCA 1998.

- Predicting store-load dependencies important for performance

- Simple predictors (based on past history) can achieve most of the potential performance

## Data Forwarding Between Stores and Loads

- We cannot update memory out of program order

- → Need to buffer all store and load instructions in instruction window

- Even if we know all addresses of past stores when we generate the address of a load, two questions still remain:

- 1. How do we check whether or not it is dependent on a store

- 2. How do we forward data to the load if it is dependent on a store

- Modern processors use a LQ (load queue) and a SQ for this

- Can be combined or separate between loads and stores

- A load searches the SQ after it computes its address. Why?

- A store searches the LQ after it computes its address. Why?

## Out-of-Order Completion of Memory Ops

- When a store instruction finishes execution, it writes its address and data in its reorder buffer entry (or SQ entry)

- When a later load instruction generates its address, it:

- searches the SQ with its address

- accesses memory with its address

- receives the value from the youngest older instruction that wrote to that address (either from ROB or memory)

- This is a complicated "search logic" implemented as a Content Addressable Memory

- Content is "memory address" (but also need size and age)

- Called store-to-load forwarding logic

## Store-Load Forwarding Complexity

- Content Addressable Search (based on Load Address)

- Range Search (based on Address and Size of both the Load and earlier Stores)

- Age-Based Search (for last written values)

- Load data can come from a combination of multiple places

- One or more stores in the Store Buffer (SQ)

- Memory/cache

## Digital Design & Computer Arch.

Lecture 15b: Out-of-Order Execution, DataFlow & Load/Store Handling

Prof. Onur Mutlu

ETH Zürich Spring 2020 9 April 2020 We did not cover the following slides. They are for your preparation for the next lecture.

# Other Approaches to Concurrency (or Instruction Level Parallelism)

#### Approaches to (Instruction-Level) Concurrency

- Pipelining

- Out-of-order execution

- Dataflow (at the ISA level)

- Superscalar Execution

- VLIW

- Fine-Grained Multithreading

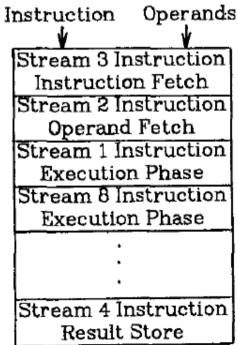

- SIMD Processing (Vector and array processors, GPUs)

- Decoupled Access Execute

- Systolic Arrays

## Review: Data Flow: Exploiting Irregular Parallelism

#### Data Flow Summary

- Availability of data determines order of execution

- A data flow node fires when its sources are ready

- Programs represented as data flow graphs (of nodes)

- Data Flow at the ISA level has not been (as) successful

- Data Flow implementations at the microarchitecture level (while preserving Von Neumann semantics) have been very successful

- Out of order execution is the prime example

## Pure Data Flow Advantages/Disadvantages

#### Advantages

- Very good at exploiting irregular parallelism

- Only real dependencies constrain processing

- More parallelism can be exposed than Von Neumann model

#### Disadvantages

- No precise state semantics

- Debugging very difficult

- Interrupt/exception handling is difficult (what is precise state semantics?)

- Too much parallelism? (Parallelism control needed)

- High bookkeeping overhead (tag matching, data storage)

**-** ...

#### Approaches to (Instruction-Level) Concurrency

- Pipelining

- Out-of-order execution

- Dataflow (at the ISA level)

- Superscalar Execution

- VLIW

- Fine-Grained Multithreading

- SIMD Processing (Vector and array processors, GPUs)

- Decoupled Access Execute

- Systolic Arrays

## Superscalar Execution

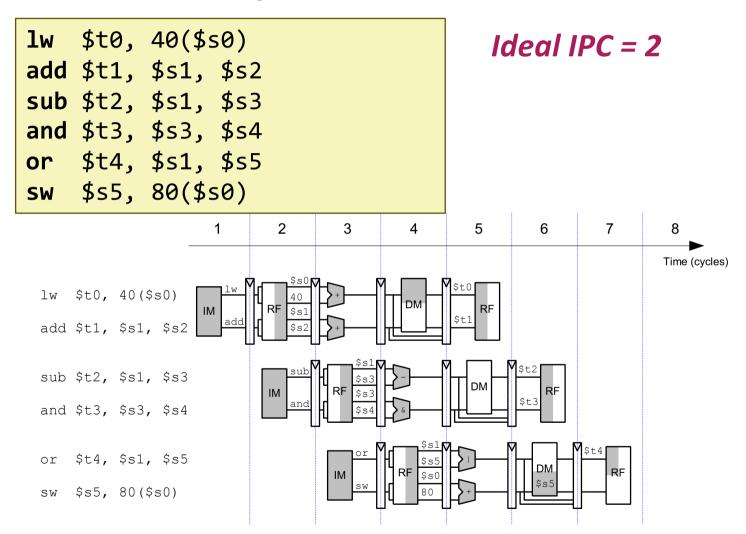

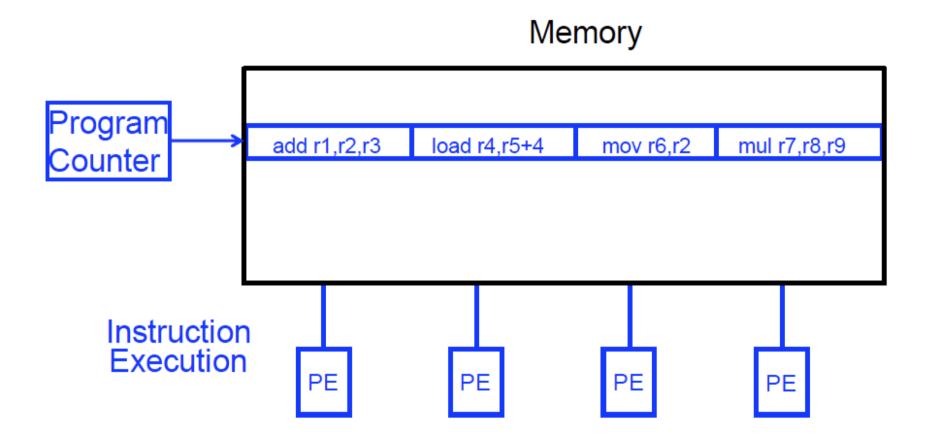

#### Superscalar Execution

- Idea: Fetch, decode, execute, retire multiple instructions per cycle

- □ N-wide superscalar → N instructions per cycle

- Need to add the hardware resources for doing so

- Hardware performs the dependence checking between concurrently-fetched instructions

- Superscalar execution and out-of-order execution are orthogonal concepts

- Can have all four combinations of processors:

[in-order, out-of-order] x [scalar, superscalar]

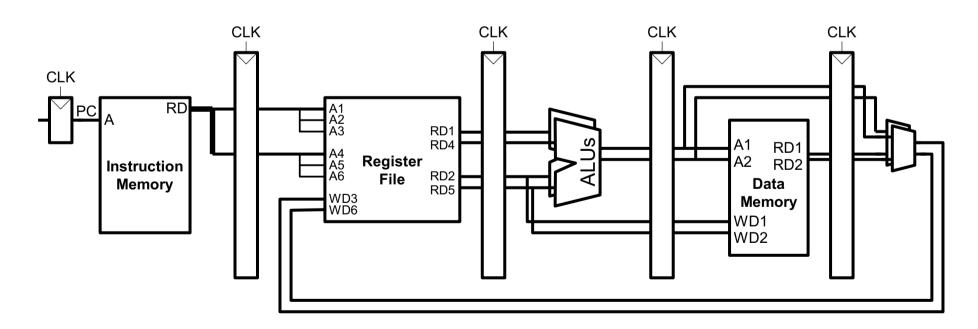

#### **In-Order Superscalar Processor Example**

- Multiple copies of datapath: Can fetch/decode/execute multiple instructions per cycle

- Dependencies make it tricky to issue multiple instructions at once

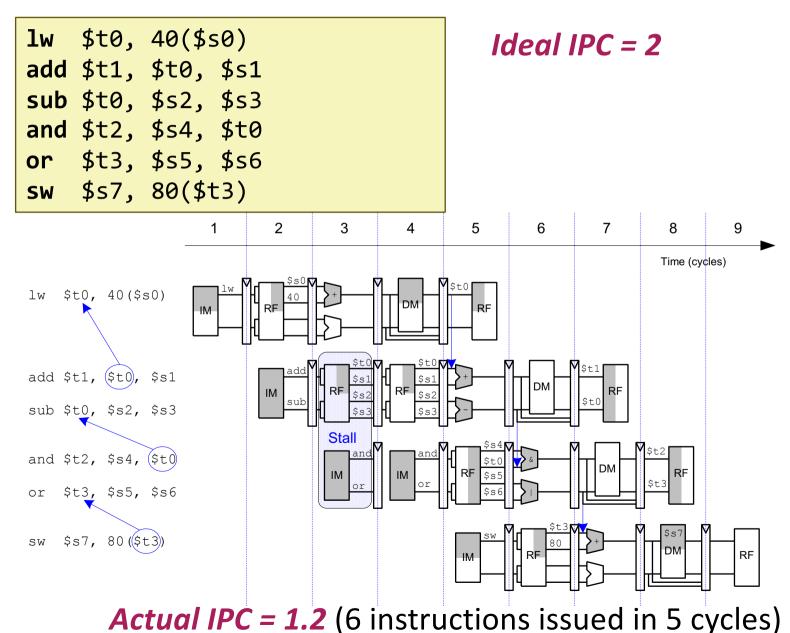

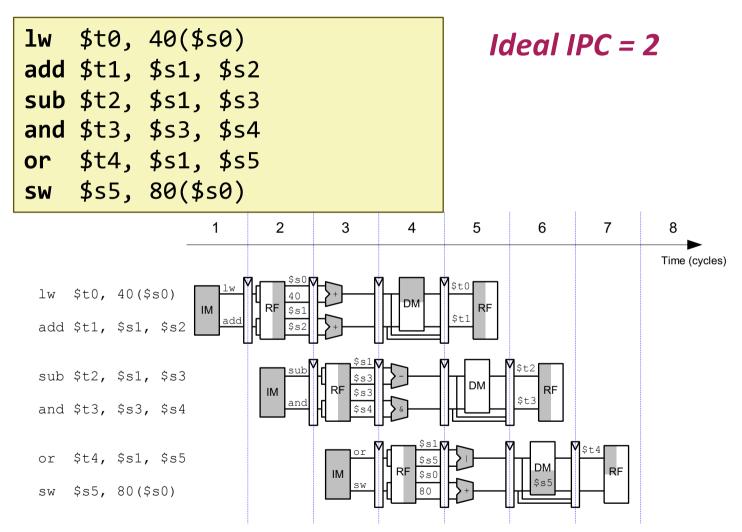

#### **In-Order Superscalar Performance Example**

#### **Superscalar Performance with Dependencies**

## Superscalar Execution Tradeoffs

- Advantages

- Higher IPC (instructions per cycle)

- Disadvantages

- Higher complexity for dependency checking

- Require checking within a pipeline stage

- Renaming becomes more complex in an OoO processor

- More hardware resources needed

#### Approaches to (Instruction-Level) Concurrency

- Pipelining

- Out-of-order execution

- Dataflow (at the ISA level)

- Superscalar Execution

- VLIW

- Fine-Grained Multithreading

- SIMD Processing (Vector and array processors, GPUs)

- Decoupled Access Execute

- Systolic Arrays

## VLIW

#### VLIW Concept

- Superscalar

- Hardware fetches multiple instructions and checks dependencies between them

- VLIW (Very Long Instruction Word)

- Software (compiler) packs independent instructions in a larger "instruction bundle" to be fetched and executed concurrently

- Hardware fetches and executes the instructions in the bundle concurrently

- No need for hardware dependency checking between concurrently-fetched instructions in the VLIW model

#### VLIW Concept

- Fisher, "Very Long Instruction Word architectures and the ELI-512," ISCA 1983.

- ELI: Enormously longword instructions (512 bits)

## VLIW (Very Long Instruction Word)

- A very long instruction word consists of multiple independent instructions packed together by the compiler

- Packed instructions can be logically unrelated (contrast with SIMD/vector processors, which we will see soon)

- Idea: Compiler finds independent instructions and statically schedules (i.e. packs/bundles) them into a single VLIW instruction

- Traditional Characteristics

- Multiple functional units

- All instructions in a bundle are executed in lock step

- Instructions in a bundle statically aligned to be directly fed into the functional units

#### VLIW Performance Example (2-wide bundles)

#### VLIW Lock-Step Execution

- Lock-step (all or none) execution: If any operation in a VLIW instruction stalls, all instructions stall

- In a truly VLIW machine, the compiler handles all dependency-related stalls, hardware does **not** perform dependency checking

- What about variable latency operations?

#### VLIW Philosophy

- Philosophy similar to RISC (simple instructions and hardware)

- Except multiple instructions in parallel

- RISC (John Cocke, 1970s, IBM 801 minicomputer)

- Compiler does the hard work to translate high-level language code to simple instructions (John Cocke: control signals)

- And, to reorder simple instructions for high performance

- □ Hardware does little translation/decoding → very simple

- VLIW (Josh Fisher, ISCA 1983)

- Compiler does the hard work to find instruction level parallelism

- Hardware stays as simple and streamlined as possible

- Executes each instruction in a bundle in lock step

- Simple → higher frequency, easier to design

#### Commercial VLIW Machines

- Multiflow TRACE, Josh Fisher (7-wide, 28-wide)

- Cydrome Cydra 5, Bob Rau

- Transmeta Crusoe: x86 binary-translated into internal VLIW

- TI C6000, Trimedia, STMicro (DSP & embedded processors)

- Most successful commercially

#### Intel IA-64

- Not fully VLIW, but based on VLIW principles

- EPIC (Explicitly Parallel Instruction Computing)

- Instruction bundles can have dependent instructions

- A few bits in the instruction format specify explicitly which instructions in the bundle are dependent on which other ones

#### VLIW Tradeoffs

#### Advantages

- + No need for dynamic scheduling hardware → simple hardware

- + No need for dependency checking within a VLIW instruction -> simple hardware for multiple instruction issue + no renaming

- + No need for instruction alignment/distribution after fetch to different functional units → simple hardware

#### Disadvantages

- -- Compiler needs to find N independent operations per cycle

- -- If it cannot, inserts NOPs in a VLIW instruction

- -- Parallelism loss AND code size increase

- -- Recompilation required when execution width (N), instruction latencies, functional units change (Unlike superscalar processing)

- -- Lockstep execution causes independent operations to stall

- -- No instruction can progress until the longest-latency instruction completes

#### VLIW Summary

- VLIW simplifies hardware, but requires complex compiler techniques

- Solely-compiler approach of VLIW has several downsides that reduce performance

- -- Too many NOPs (not enough parallelism discovered)

- -- Static schedule intimately tied to microarchitecture

- -- Code optimized for one generation performs poorly for next

- -- No tolerance for variable or long-latency operations (lock step)

- ++ Most compiler optimizations developed for VLIW employed in optimizing compilers (for superscalar compilation)

- Enable code optimizations

- ++ VLIW successful when parallelism is easier to find by the compiler (traditionally embedded markets, DSPs)

## An Example Work: Superblock

The Superblock: An Effective Technique

for VLIW and Superscalar Compilation

```

Wen-mei W. Hwu Scott A. Mahlke William Y. Chen Pohua P. Chang

Nancy J. Warter Roger A. Bringmann Roland G. Ouellette Richard E. Hank

Tokuzo Kiyohara Grant E. Haab John G. Holm Daniel M. Lavery *

```

Hwu et al., The superblock: An effective technique for VLIW and superscalar compilation. The Journal of Supercomputing, 1993.

- Lecture Video on Static Instruction Scheduling

- https://www.youtube.com/watch?v=isBEVkIjgGA

## Another Example Work: IMPACT

#### IMPACT: An Architectural Framework for Multiple-Instruction-Issue Processors

Pohua P. Chang

Scott A. Mahlke

William Y. Chen

Nancy J. Warter

Wen-mei W. Hwu

Center for Reliable and High-Performance Computing

University of Illinois

Urbana, IL 61801