## DIGITAL DESIGN AND COMPUTER ARCHITECTURE (252-0028-00L), SPRING 2020 OPTIONAL HW 7: CACHES AND VIRTUAL MEMORY

Instructor: Prof. Onur Mutlu

TAs: Mohammed Alser, Rahul Bera, Can Firtina, Juan Gomez-Luna, Jawad Haj-Yahya, Hasan Hassan, Konstantinos Kanellopoulos, Lois Orosa, Jisung Park, Geraldo De Oliveira Junior, Minesh Patel, Giray Yaglikci

Released: Saturday, May 30, 2020

#### 1 Instruction and Data Caches

Consider the following loop is executed on a system with a small instruction cache (I-cache) of size 16 B. The data cache (D-cache) is fully associative of size 1 KB. Both caches use 16-byte blocks. The instruction length and data word size are 4 B. The initial value of register \$1 is 40. The value of \$0 is 0. (Note: Assume that the first instruction of the loop is aligned to the beginning of a cache block).

```

Loop: lw $6, X($1)

addi $6, $6, 1

sw $6, Y($1)

subi $1, $1, 4

beq $1, $0, Exit

j Loop

Exit: ...

```

- (a) Compute I-cache and D-cache miss rates, considering:

- X and Y are different arrays.

- X and Y are the same array.

| (b) | Compute the average number of cycles per instruction (CPI), using a baseline ideal CPI (ideal caches) equal to 2, and a miss latency equal to 10 clock cycles. |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                |

|     |                                                                                                                                                                |

| (c) | A compiler could unroll this loop for optimization. How would this affect CPI?                                                                                 |

|     |                                                                                                                                                                |

|     |                                                                                                                                                                |

|     |                                                                                                                                                                |

| (d) | How would the result of part (a) change with a 32-byte I-cache?                                                                                                |

|     |                                                                                                                                                                |

|     |                                                                                                                                                                |

#### Reverse Engineering Caches I $\mathbf{2}$

You're trying to reverse-engineer the characteristics of a cache in a system so that you can design a more efficient, machine-specific implementation of an algorithm you're working on. To do so, you've come up with four patterns that access various bytes in the system in an attempt to determine the following four cache characteristics:

- Cache block size (8, 16, 32, 64, or 128 B)

- Cache associativity (2-, 4-, or 8-way)

- Cache size (4 or 8 KB)

- Cache replacement policy (LRU or FIFO)

However, the only statistic that you can collect on this system is cache hit rate after performing the access pattern. Here is what you observe:

| Access Pattern  |     | $Addresses\ Accessed\ (Oldest \rightarrow Youngest)$ |      |       |       |      |      |      |     | Hit Rate |

|-----------------|-----|------------------------------------------------------|------|-------|-------|------|------|------|-----|----------|

| A               | 0   | 4096                                                 | 8192 | 12288 | 16384 | 4096 | 0    |      |     | 1/7      |

| В               | 0   | 1024                                                 | 2048 | 3072  | 4096  | 5120 | 6144 | 3072 | 0   | 1/9      |

| $^{\mathrm{C}}$ | 0   | 4                                                    | 8    | 16    | 32    | 64   | 128  | 256  | 512 | 4/9      |

| D               | 128 | 1152                                                 | 2176 | 3200  | 128   | 4224 | 1152 |      |     | 2/7      |

Based on what you observe, what are the following characteristics of the cache? (Be sure to justify clearly

| you | r answer for full credit.)                  |

|-----|---------------------------------------------|

| (a) | Cache block size (8, 16, 32, 64, or 128 B)? |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

| (b) | Cache associativity (2-, 4-, or 8-way)?     |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

| (c) | Cache size (4 or 8KB)?                      |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

### 3 Reverse Engineering Caches II

You are trying to reverse-engineer the characteristics of a cache in a system, so that you can design a more efficient, machine-specific implementation of an algorithm you are working on. To do so, you have come up with three patterns that access various *bytes* in the system in an attempt to determine the following four cache characteristics:

- Cache block size (8, 16, 32, 64, or 128 B)

- Cache associativity (1-, 2-, 4-, or 8-way)

- Cache size (4 or 8 KB)

- Cache replacement policy (LRU or FIFO)

(a) Cache block size (8, 16, 32, 64, or 128 B)?

However, the only statistic that you can collect on this system is *cache hit rate* after performing the access pattern. Here is what you observe:

| Sequence       |                    | Addres         | ses Ac         | cessed (            | Oldest - | → Youn              | igest) |       | Hit Rate          |

|----------------|--------------------|----------------|----------------|---------------------|----------|---------------------|--------|-------|-------------------|

| 1.<br>2.<br>3. | $0 \\ 31 \\ 32768$ | 4<br>8192<br>0 | 8<br>63<br>129 | 16<br>16384<br>1024 |          | 128<br>8192<br>8192 | 64     | 16384 | 1/2<br>5/8<br>1/3 |

Assume that the cache is initially empty at the beginning of the first sequence, but not at the beginning of the second and third sequences. The sequences are executed back-to-back, i.e., no other accesses take place between the three sequences. Thus, at the beginning of the second (third) sequence, the contents are the same as at the end of the first (second) sequence.

Based on what you observe, what are the following characteristics of the cache?

| (b) | Cache associativity (1-, 2-, 4-, or 8-way)? |

|-----|---------------------------------------------|

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

| (c) | Cache size (4 or 8 KB)?                     |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

|     |                                             |

#### 4 Tracing the Cache

Assume you have three toy CPUs: 6808-D, 6808-T, and 6808-F. All three CPUs feature one level of cache. The cache size is 128 bytes, the cache block size is 32 bytes, and the cache uses LRU replacement. The only difference between the three CPUs is the associativity of the cache:

- 6808-D uses a direct mapped cache.

- 6808-T uses a two-way associative cache.

- 6808-F uses a fully associative cache.

You run the SPECMem3000 program to evaluate the CPUs. This benchmark program tests only memory read performance by issuing read requests to the cache. Assume that the cache is empty before you run the benchmark. The cache accesses generated by the program are as follows, in order of access from left to right:

A, B, A, H, B, G, H, H, A, E, H, D, H, G, C, C, G, C, A, B, H, D, E, C, C, B, A, D, E, F

Each letter represents a unique cache block. All 8 cache blocks are contiguous in memory. However, the ordering of the letters does not necessarily correspond to the ordering of the cache blocks in memory. For 6808-D, you observe the following cache misses in order of generation:

A, B, A, H, B, G, A, E, D, H, C, G, C, B, D, A, F

| Please be clea |                                  |                   |        |                |                   |

|----------------|----------------------------------|-------------------|--------|----------------|-------------------|

|                |                                  |                   |        |                |                   |

|                |                                  |                   |        |                |                   |

|                |                                  |                   |        |                |                   |

|                |                                  |                   |        |                |                   |

|                |                                  |                   |        |                |                   |

|                |                                  |                   |        |                |                   |

|                |                                  |                   |        |                |                   |

|                |                                  | <br>· c 11 (      | 2000 E | or in their or | der of generation |

|                | lown the sequence ight want to w | cache state after |        |                | der of Scheratic  |

|                |                                  |                   |        |                | der of generalic  |

|                |                                  |                   |        |                | uor or generalit  |

|                |                                  |                   |        |                | dor or generality |

|                |                                  |                   |        |                | uor or generalit  |

|                |                                  |                   |        |                | dor or general    |

|                |                                  |                   |        |                | dor or goriorant  |

|                |                                  |                   |        |                | dor or goriorant  |

|                |                                  |                   |        |                | dor or gonorant   |

|                |                                  |                   |        |                | dor or goriorant  |

|                |                                  |                   |        |                | dor or goriorant  |

|              | unately, your evaluation, |                   |                 |                |                |                |

|--------------|---------------------------|-------------------|-----------------|----------------|----------------|----------------|

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

| Please writ  | e down the sequen         | uce of cache mis  | ses for the 681 | 08-T processo  | in their order | of generation  |

| T Tease with |                           | ice of eache fine | sses for the oo | oo i processor | in their order | or generation. |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

|              |                           |                   |                 |                |                |                |

| e) | What is the cache miss rate for each processor? |

|----|-------------------------------------------------|

|    | 6808-D:                                         |

|    |                                                 |

|    |                                                 |

|    |                                                 |

|    |                                                 |

|    | 6808-T:                                         |

|    |                                                 |

|    |                                                 |

|    |                                                 |

|    |                                                 |

|    | 6808-F:                                         |

|    |                                                 |

|    |                                                 |

|    |                                                 |

|    |                                                 |

## 5 Analyzing Cache Structure

Below, we have given you four different sequences of addresses generated by a program running on a processor with a data cache. Cache hit ratio for each sequence is also shown below. Assuming that the cache is initially empty at the beginning of each sequence, find out the following parameters of the processor's data cache:

- Associativity (1, 2 or 4 ways)

- Block size (1, 2, 4, 8, 16, or 32 bytes)

- Total cache size (256 B, or 512 B)

- Replacement policy (LRU or FIFO)

Assumptions: all memory accesses are one byte accesses. All addresses are byte addresses.

| Sequence No. | Address Sequence                             | Hit Ratio |

|--------------|----------------------------------------------|-----------|

| 1            | 0, 2, 4, 8, 16, 32                           | 0.33      |

| 2            | 0, 512, 1024, 1536, 2048, 1536, 1024, 512, 0 | 0.33      |

| 3            | 0, 64, 128, 256, 512, 256, 128, 64, 0        | 0.33      |

| 4            | 0, 512, 1024, 0, 1536, 0, 2048, 512          | 0.25      |

| 11/23 |  |  |

|-------|--|--|

## 6 Caches

| set basis as a | single bit. (Hint | $: 4352 = 2^{12}$ | + 2 <sup>8</sup> .) |  |

|----------------|-------------------|-------------------|---------------------|--|

|                |                   |                   |                     |  |

|                |                   |                   |                     |  |

|                |                   |                   |                     |  |

|                |                   |                   |                     |  |

|                |                   |                   |                     |  |

|                |                   |                   |                     |  |

|                |                   |                   |                     |  |

|                |                   |                   |                     |  |

|                |                   |                   |                     |  |

|                |                   |                   |                     |  |

### 7 Cache Performance Analysis

We are going to microbenchmark the cache hierarchy of a computer with the following two codes. The array data contains 32-bit unsigned integer values. For simplicity, we consider that accesses to the array latency bypass all caches (i.e., latency is *not* cached). timer() returns a timestamp in cycles.

```

(1) j = 0;

for (i=0; i<size; i+=stride){

start = timer();

d = data[i];

stop = timer();

latency[j++] = stop - start;

}

(2) for (i=0; i<size1; i+=stride1){

d = data[i];

}

j = 0;

for (i=0; i<size2; i+=stride2){

start = timer();

d = data[i];

stop = timer();

latency[j++] = stop - start;

}</pre>

```

The cache hierarchy has two levels. L1 is a 4kB set associative cache.

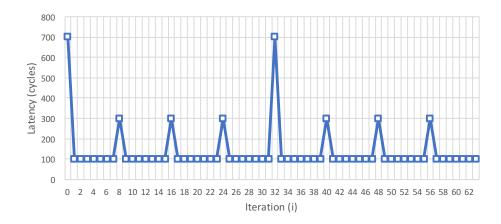

(a) When we run code (1), we obtain the latency values in the following chart for the first 64 reads to the array data (in the first 64 iterations of the loop) with stride equal to 1. What are the cache block sizes in L1 and L2?

| (b) | Using code (2) with stride1 = stride2 = 32, size1 = 1056, and size2 = 1024, we observe latency[0] = 300 cycles. However, if size1 = 1024, latency[0] = 100 cycles. What is the maximum number of ways in L1? (Note: The replacement policy can be either FIFO or LRU).                                                                                                                                                                                                         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (c) | We want to find out the exact replacement policy, assuming that the associativity is the maximum obtained in part (b). We first run code (2) with stride1 = 32, size1 = 1024, stride2 = 64, and size2 = 1056. Then (after resetting j), we run code (1) with stride = 32 and size = 1024. We observe latency[1] = 100 cycles. What is the replacement policy? Explain. (Hint: The replacement policy can be either FIFO or LRU. You need to find the correct one and explain). |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

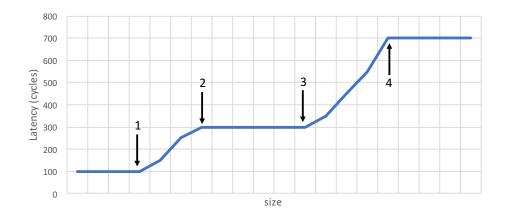

(d) Now we carry out two consecutive runs of code (1) for different values of size. In the first run, stride is equal to 1. In the second run, stride is equal to 16. We ignore the latency results of the first run, and average the latency results of the second run. We obtain the following graph. What do the four parts shown with the arrows represent?

| Before arrow 1:              |

|------------------------------|

|                              |

|                              |

|                              |

|                              |

|                              |

| Between arrow 1 and arrow 2: |

|                              |

|                              |

|                              |

|                              |

|                              |

| Between arrow 2 and arrow 3: |

|                              |

|                              |

|                              |

|                              |

|                              |

| Between arrow 3 and arrow 4: |

|                              |

|                              |

|                              |

|                              |

| After arrow 4:           |               |  |  |  |

|--------------------------|---------------|--|--|--|

|                          |               |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

| Explain as needed (if yo | u need more): |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

|                          |               |  |  |  |

#### 8 Memory Hierarchy

An enterprising computer architect is building a new machine for high-frequency stock trading and needs to choose a CPU. She will need to optimize her setup for *memory access latency* in order to gain a competitive edge in the market. She is considering two different prototype enthusiast CPUs that advertise high memory performance:

- (A) Dragonfire-980 Hyper-Z

- (B) Peregrine G-Class XTreme

She needs to characterize these CPUs to select the best one, and she knows from Prof. Mutlu's course that she is capable of reverse-engineering everything she needs to know. Unfortunately, these CPUs are not yet publicly available, and their exact specifications are unavailable. Luckily, important documents were recently leaked, claiming that all three CPUs have:

- Exactly 1 high-performance core

- LRU replacement policies (for any set-associative caches)

- Inclusive caching (i.e., data in a given cache level is present upward throughout the memory hierarchy. For example, if a cache line is present in L1, the cache line is also present in L2 and L3 if available.)

- Constant-latency memory structures (i.e., an access to any part of a given memory structure takes the same amount of time)

- Cache line, size, and associativity are all size aligned to powers of two

Being an ingenious engineer, she devises the following simple application in order to extract all of the information she needs to know. The application uses a high-resolution timer to measure the amount of time it takes to read data from memory with a specific pattern parameterized by STRIDE and MAX\_ADDRESS:

Assume 1) this code runs for a long time, so all memory structures are fully warmed up, i.e., repeatedly accessed data is already cached, and 2) N is large enough such that the timer captures **only** steady-state information.

By sweeping *STRIDE* and *MAX\_ADDRESS*, the computer architect can glean information about the various memory structures in each CPU.

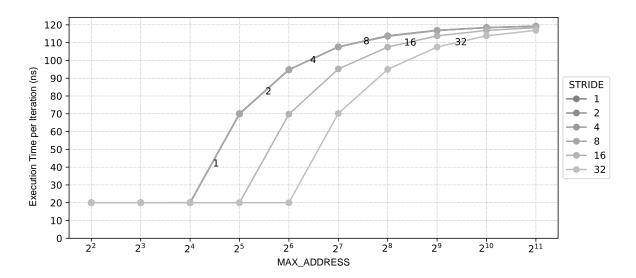

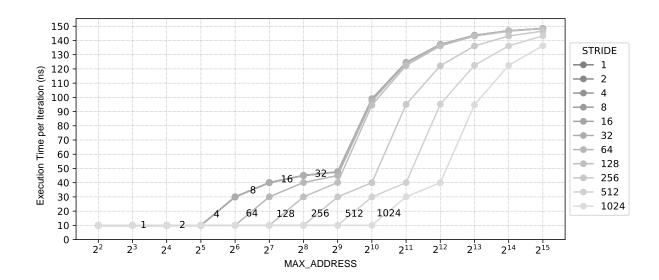

She produces Figure 1 for CPU A and Figure 2 for CPU B.

**Your task:** Using the data from the graphs, reverse-engineer the following system parameters. If the parameter does not make sense (e.g., L3 cache in a 2-cache system), mark the box with an "X". If the graphs provide insufficient information to ascertain a desired parameter, simply mark it as "N/A".

#### (a) Fill in the blanks for Dragonfire-980 Hyper-Z.

Figure 1: Execution time of the test code on CPU A for various values of *STRIDE* and *MAX\_ADDRESS*. *STRIDE* values are labeled on curves themselves for clarity. Note that the curves for strides 1, 2, 4, and 8 overlap in the figure.

Table 1: Fill in the following table for CPU A (Dragonfire-980 Hyper-Z)

| System Parameter                 | CPU A: Dragonfire-980 Hyper-Z |    |    |      |

|----------------------------------|-------------------------------|----|----|------|

|                                  | L1                            | L2 | L3 | DRAM |

| Cache Line Size (B)              |                               |    |    |      |

| Cache Associativity              |                               |    |    |      |

| Total Cache Size (B)             |                               |    |    |      |

| Access Latency (ns) <sup>1</sup> |                               |    |    |      |

<sup>&</sup>lt;sup>1</sup> e.g., DRAM access latency means the latency of fetching the data from DRAM to L3, *not* the latency of bringing the data from the DRAM all the way down to the CPU. Similarly, L3 access latency means the latency of fetching the data from L3 to L2. L1 access latency is the latency to bring the data to the CPU from the L1 cache.

#### (b) Fill in the blanks for Peregrine G-Class XTreme.

Figure 2: Execution time of the test code on CPU B for various values of *STRIDE* and *MAX\_ADDRESS*. *STRIDE* values are labeled on curves themselves for clarity. Note that the curves for strides 1, 2, 4, 8, 16, and 32 overlap in the figure.

Table 2: Fill in the following table for CPU B (Peregrine G-Class XTreme)

| System Parameter                 | CPU B: Peregrine G-Class XTreme |    |    |      |

|----------------------------------|---------------------------------|----|----|------|

|                                  | L1                              | L2 | L3 | DRAM |

| Cache Line Size (B)              |                                 |    |    |      |

| Cache Associativity              |                                 |    |    |      |

| Total Cache Size (B)             |                                 |    |    |      |

| Access Latency (ns) <sup>1</sup> |                                 |    |    |      |

<sup>&</sup>lt;sup>1</sup> e.g., DRAM access latency means the latency of fetching the data from DRAM to L3, *not* the latency of bringing the data from the DRAM all the way down to the CPU. Similarly, L3 access latency means the latency of fetching the data from L3 to L2. L1 access latency is the latency to bring the data to the CPU from the L1 cache.

### 9 Virtual Memory

An ISA supports an 8-bit, byte-addressable virtual address space. The corresponding physical memory has only 128 bytes. Each page contains 16 bytes. A simple, one-level translation scheme is used and the page table resides in physical memory. The initial contents of the frames of physical memory are shown below.

| Frame Number | Frame Contents |

|--------------|----------------|

| 0            | Empty          |

| 1            | Page 13        |

| 2            | Page 5         |

| 3            | Page 2         |

| 4            | Empty          |

| 5            | Page 0         |

| 6            | Empty          |

| 7            | Page Table     |

A three-entry translation lookaside buffer that uses Least Recently-Used (LRU) replacement is added to this system. Initially, this TLB contains the entries for pages 0, 2, and 13. For the following sequence of references, put a circle around those that generate a TLB hit and put a rectangle around those that generate a page fault. What is the hit rate of the TLB for this sequence of references? (Note: LRU policy is used to select pages for replacement in physical memory.)

| Ref | Ferences (to pages): 0, 13, 5, 2, 14, 14, 13, 6, 6, 13, 15, 14, 15, 13, 4, 3. |

|-----|-------------------------------------------------------------------------------|

|     |                                                                               |

|     |                                                                               |

|     |                                                                               |

| (a) | At the end of this sequence, what three entries are contained in the TLB?     |

|     |                                                                               |

|     |                                                                               |

|     |                                                                               |

| (b) | What are the contents of the 8 physical frames?                               |

|     |                                                                               |

|     |                                                                               |

|     |                                                                               |

# 10 Virtual Memory and Caching I

A 2-way set associative write back cache with perfect LRU replacement requires  $15 \times 2^9$  bits of storage to implement its tag store (including bits for valid, dirty and LRU). The cache is virtually indexed, physically tagged. The virtual address space is 1 MB, page size is 2 KB, cache block size is 8 bytes.

| (a) | What is the size of the data store of the cache in bytes?             |

|-----|-----------------------------------------------------------------------|

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

| (b) | How many bits of the virtual index come from the virtual page number? |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

| (c) | What is the physical address space of this memory system?             |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

## 11 Virtual Memory and Caching II

A four-way set-associative writeback cache has a  $2^{11}$  \* 89-bit tag store. The cache uses a custom replacement policy that requires 9 bits per set. The cache block size is 64 bytes. The cache is virtually-indexed and physically-tagged. Data from a given physical address can be present in up to eight different sets in the cache. The system uses hierarchical page tables with two levels. Each level of the page table contains 1024 entries. A page table may be larger or smaller than one page. The TLB contains 64 entries.

| (a) | How many bits of the virtual address are used to choose a set in the cache?                                                                                                                                                          |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                                                                      |

| (b) | What is the size of the cache data store?                                                                                                                                                                                            |

|     |                                                                                                                                                                                                                                      |

| (c) | How many bits in the Physical Frame Number must overlap with the set index bits in the virtual address?                                                                                                                              |

|     |                                                                                                                                                                                                                                      |

| (d) | On the following blank figure representing a virtual address, draw in bitfields and label bit positions for cache block offset and set number. Be complete, showing the beginning and ending bits of each field. Virtual Address:    |

|     |                                                                                                                                                                                                                                      |

| (e) | On the following blank figure representing a physical address, draw in bitfields and label bit positions for <i>physical frame number</i> and <i>page offset</i> . Be complete, showing the beginning and ending bits of each field. |

|     | Physical Address:                                                                                                                                                                                                                    |

|     |                                                                                                                                                                                                                                      |

| (f) | What is the page size?                                                                                                                                                                                                               |

|     |                                                                                                                                                                                                                                      |

| (g) | What is the size of the virtual address space? |

|-----|------------------------------------------------|

|     |                                                |

|     |                                                |

| (h) | What is the size of the physical address space |

|     |                                                |