## Final Exam

# Digital Design and Computer Architecture (252-0028-00L) ETH Zürich, Spring 2022

Prof. Onur Mutlu

| Problem 1 (40 Points):              | Boolean Logic Circuits    |  |

|-------------------------------------|---------------------------|--|

| Problem 2 (50 Points):              | Finite State Machines     |  |

| Problem 3 (30 Points):              | ISA vs. Microarchitecture |  |

| Problem 4 (60 Points):              | Verilog                   |  |

| Problem 5 (30 Points):              | Memory Potpourri          |  |

| Problem 6 (70 Points):              | Performance Evaluation    |  |

| Problem 7 (70 Points):              | Pipelining                |  |

| Problem 8 (60 Points):              | Tomasulo's Algorithm      |  |

| Problem 9 (45 Points):              | GPUs and SIMD             |  |

| Problem 10 (70 Points):             | Branch Prediction         |  |

| Problem 11 (BONUS: 50 Points):      | Prefetching               |  |

| Problem 12 (BONUS: 70 Points):      | Caches                    |  |

| Total (645 (525+120 bonus) Points): |                           |  |

## **Examination Rules:**

- 1. Written exam, 180 minutes in total.

- 2. No books, no calculators, no computers or communication devices. 3 double-sided (or 6 one-sided) A4 sheets of handwritten notes are allowed.

- 3. Write all your answers on this document; space is reserved for your answers after each question.

- 4. You are provided with scratchpad sheets. Do not answer questions on them. We will not collect them.

- 5. Clearly indicate your final answer for each problem. Answers will only be evaluated if they are readable.

- 6. Put your Student ID card visible on the desk during the exam.

- 7. If you feel disturbed, immediately call an assistant.

- 8. Write with a black or blue pen (no pencil, no green, red or any other color).

- 9. Show all your work. For some questions, you may get partial credit even if the end result is wrong due to a calculation mistake. If you make assumptions, state your assumptions clearly and precisely.

- 10. Please write your initials at the top of every page.

### Tips:

- Be cognizant of time. Do not spend too much time on one question.

- Be concise. You may be penalized for verbosity.

- Show work when needed. You will receive partial credit at the instructors' discretion.

- Write legibly. Show your final answer.

This page intentionally left blank

Final Exam Page 1 of 26

#### Boolean Logic Circuits [40 points] 1

During your job interview, you are asked to design a combinational circuit with a four-bit input,  $\{A, B, C, D\}$  (A is the most significant bit and D is the least significant bit), and two 1-bit outputs, Factorial and Div4. The value of each output is determined as follows:

- The output Factorial is 1 only when the input 4-bit number is a product of ALL positive integers that are less than or equal to the input number.

- The output Div4 is 1 only when the input 4-bit number is divisible by 4.

- Otherwise, the corresponding outputs are zero.

Please answer the following four questions.

(a) [10 points] Fill in the missing entries in the truth table below for the combinational circuit you are designing.

|   | Inp | ${ m uts}$ | Outputs |           |      |  |  |

|---|-----|------------|---------|-----------|------|--|--|

| A | В   | C          | D       | Factorial | Div4 |  |  |

| 0 | 0   | 0          | 0       | 1         | 1    |  |  |

| 0 | 0   | 0          | 1       |           |      |  |  |

| 0 | 0   | 1          | 0       |           |      |  |  |

| 0 | 0   | 1          | 1       | 0         | 0    |  |  |

| 0 | 1   | 0          | 0       |           |      |  |  |

| 0 | 1   | 0          | 1       |           |      |  |  |

| 0 | 1   | 1          | 0       |           |      |  |  |

| 0 | 1   | 1          | 1       | 0         | 0    |  |  |

| 1 | 0   | 0          | 0       |           |      |  |  |

| 1 | 0   | 0          | 1       | 0         | 0    |  |  |

| 1 | 0   | 1          | 0       |           |      |  |  |

| 1 | 0   | 1          | 1       |           |      |  |  |

| 1 | 1   | 0          | 0       |           |      |  |  |

| 1 | 1   | 0          | 1       | 0         | 0    |  |  |

| 1 | 1   | 1          | 0       |           |      |  |  |

| 1 | 1   | 1          | 1       |           |      |  |  |

Final Exam Page 2 of 26

| work step-               |                    |                       |           |          |           |          |        |          |      |     |   |

|--------------------------|--------------------|-----------------------|-----------|----------|-----------|----------|--------|----------|------|-----|---|

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

|                          |                    |                       |           |          |           |          |        |          |      |     |   |

| [20 points]              | Find the           | simplest              | represent | ation of | the $Fac$ | torial   | output | bv using | onlu | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial c | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial c | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | 8 |

| [20 points]<br>Show your | Find the work step | simplest<br>-by-step. | represent | ation of | the Fac   | torial o | output | by using | only | NOR | g |

Final Exam Page 3 of 26

## 2 Finite State Machines [50 points]

The Polybahn from Central to Polyterasse has broken down! To fix it you need to design a finite state machine that controls the Polybahn's two doors A and B.

The Polybahn should operate as follows:

- Initially the Polybahn is empty and idle, and passengers can enter through door A.

- The Polybahn is full when it carries 2 passengers.

- When it is full and idle, the Polybahn goes into transit to the other station with both doors closed.

- After reaching the station, the Polybahn will **unload** all passengers through door B, while door A is still closed.

- After the last passenger has exited the Polybahn, door B closes and the Polybahn becomes idle.

- Should (1) a passenger fall out of the Polybahn during **transit**, or (2) the Polybahn become overfull (≥ 3 passengers) at any point, it stops in **emergency** mode, where it opens all doors and remains (unless reset to the initial **idle** state).

The FSM receives two input bits, with the following meaning:

| Input | Meaning                           |

|-------|-----------------------------------|

| 00    | no change                         |

| 01    | exactly one passenger left        |

| 10    | exactly one passenger entered     |

| 11    | the Polybahn arrived in a station |

The FSM produces two output bits: The first bit, A, holds door A open when it is 1. The second bit, B, holds door B open when it is 1.

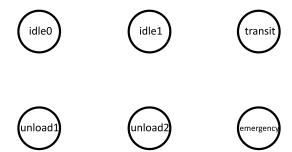

(a) [25 points] Complete the Moore-type FSM below by (1) drawing the transition edges between the states (including reset), (2) specifying the edges' respective input bits, and (3) specifying the output bits of each state. Any input for which no outgoing edge is specified is assumed as a self loop. The 6 given states are sufficient, do not draw additional states.

**Note:** Passengers sometimes slip in or out through incorrect doors, or even through closed doors. Your FSM must correctly handle such cases.

Final Exam Page 4 of 26

Complete the Mealy-type FSM below by (1) drawing the transition edges between the states (including reset), and (2) specifying the edges' respective input and output bits. Label edges in the following format: [input0][input1]/[bell], e.g., 10/0 = passenger entered, bell off. Any input for which no outgoing edge is specified is assumed as a self loop with output 0.

Final Exam Page 5 of 26

# 3 ISA vs. Microarchitecture [30 points]

Note: we will subtract 1 point for each incorrect answer and award 0 points for unanswered questions.

- 1. [2 points] Two-level global branch prediction.

- 1. ISA

- 2. Microarchitecture

- 2. [2 points] Location of the bits that identify the destination register in an ADD instruction.

- 1. ISA

- 2. Microarchitecture

- 3. [2 points] Number of instructions fetched per cycle.

- 1. ISA

- 2. Microarchitecture

- 4. [2 points] Ratio of the number of floating-point to integer general-purpose registers.

- 1. ISA

- 2. Microarchitecture

- 5. [2 points] Number of integer arithmetic and logic units (ALUs).

- 1. ISA

- 2. Microarchitecture

- 6. [2 points] Instruction issue width of the processor core's pipeline.

- 1. ISA

- 2. Microarchitecture

- 7. [2 points] SIMD support.

- 1. ISA

- 2. Microarchitecture

- 8. [2 points] L3 cache replacement policy.

- 1. ISA

- 2. Microarchitecture

- 9. [2 points] Width of the data bus to memory.

- 1. ISA

- 2. Microarchitecture

- 10. [2 points] The size of the addressable memory by programs.

- 1. ISA

- 2. Microarchitecture

- 11. [2 points] Number of cycles it takes to execute an ADD instruction.

- 1. ISA

- 2. Microarchitecture

- 12. [2 points] Ability to choose a specific cache replacement policy using operating system code.

- 1. ISA

- 2. Microarchitecture

- 13. [2 points] Number of read/write ports in the physical register file.

- 1. ISA

- 2. Microarchitecture

- 14. [2 points] Function of each bit in a programmable prefetcher's configuration register.

- 1. ISA

- 2. Microarchitecture

- 15. [2 points] Number of L3 cache banks.

- $1. \ \mathsf{ISA}$

- 2. Microarchitecture

Final Exam Page 6 of 26

#### $\overline{ ext{Verilog}}$ [60 points] 4

#### What Does This Code Do? [30 points] 4.1

Analyze the following Verilog module and answer the question.

```

module mystery_module (clk, en, in1, in2, out);

2

input clk, en;

3

input[63:0] in1;

input[7:0] in2;

5

output reg[10:0] out = 0;

6

reg[2:0] var1 = 0;

always @(posedge clk) begin

10

out <= out;

11

if (en & (var1 == 0)) begin

^{12}

var1 <= var1 + 1'b1;</pre>

13

14

if (in2[var1])

15

out <= 11'd0 + in1[var1*8 +: 8];

16

else

17

out <= 11'd0 - in1[var1*8 +: 8];

18

19

20

21

if (var1 != 0) begin

22

var1 <= var1 + 1'b1;</pre>

23

24

if (in2[var1])

out <= out + in1[var1*8 +: 8];

25

else

26

out <= out - in1[var1*8 +: 8];

27

end

28

end

29

30

31

endmodule

```

Assume that the inputs in1 and in2 always have the following values:

```

in1 = 64'h0807060504030201

in2 = 8'b10111011

```

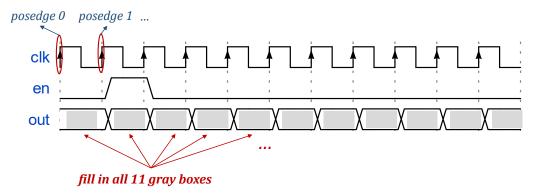

What unsigned decimal values does the out signal get in the following waveform diagram? Fill in the gray boxes with an out value for each clk cycle. Briefly explain your answer.

Final Exam Page 7 of 26

| Initials:             | Digital Design and Computer Architecture | August 11th, 2022 |

|-----------------------|------------------------------------------|-------------------|

| Brief explanation (to | help us award you partial credit):       |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

|                       |                                          |                   |

Final Exam Page 8 of 26

## Complete the Verilog code [30 points]

For each numbered blank (1)-(5) in the following Verilog code, mark the choice below (i.e., one of options A, B, C, D) that makes the Verilog module operate as described in the comments. The resulting code must have correct syntax.

```

module my_module (input clk, input rst,

input[1:0] data, (1) result);

2

3

(2) state = 2'b00; // defining a 2-bit signal with an initial value of 0

4

always @(posedge clk) begin

case (state)

2'b00:

state <= state + (3); // set the next 'state' to 2'b11

2'b01:

10

state <= 2'b00;

11

2'b10: begin

12

state <= 2'b11;

13

14

if ((4)data)

// set the next 'state' to 2'b01 if

15

state <= 2'b01; // all bits of 'data' are 1

end

17

2'b11:

18

state <= 2'b10;

19

endcase

20

21

end

22

23

assign result = (5)state; // assign 1'b1 to 'result' if 'state' has any bit set to 1

^{24}

// otherwise assign 1'b0

25

endmodule

26

```

Provide your choice for each blank (1)-(5) below. Circle only one of A, B, C, D for each blank.

A. output B. output reg C. output reg[0:0] D. input reg

A. reg[1:0] B. regC. wire D. wire[1:0]

A. 1'b3 B. 3'b2 C. 2'd11 D. 3

C. ! D. 1 A. | | B. &

C. && D. ^ A. | B. &

Final Exam Page 9 of 26

#### Memory Potpourri [30 points] 5

Read the following statements about memory organization & technology. Circle "True" if the statement is true and "False" otherwise. Note: we will subtract 1 point for each incorrect answer and award 0 points for unanswered questions.

1. [2 points] A main memory access typically consumes less energy than a register file access. 2. False 1. True 2. [2 points] Building a larger memory array by increasing the length of the array's wordlines and bitlines increases the cost (\$) but does not increase the access time of the array. 1. True 2. False 3. [2 points] Activating a DRAM cell temporarily destroys the value stored in the DRAM cell. 1. True 2. False 4. [2 points] DRAM cost (\$) per bit is much higher than that of SRAM. 1. True 2. False 5. [2 points] The memory hierarchy of a typical computer system comprises different memory technologies. 1. True 2. False 6. 2 points Recently accessed data should be kept at the bottom-level in the memory hierarchy (e.g., main memory or disk) and not at the top-level (e.g., caches) in the hierarchy. 1. True 7. [2 points] A program with no branches has high temporal locality in its instruction memory references. 1. True 2. False 8. 2 points A cache that has a block size equal to word size of memory access instructions cannot exploit spatial locality. 1. True 2. False 9. [2 points] Memory banking enables concurrent access to the memory structure. 1. True 2. False 10. [2 points] In DRAM, accesses to different rows in one bank can be serviced faster compared to accesses to the same row in one bank. 1. True 2. False 11. [2 points] PCM is non-volatile, which means PCM retains stored data even when it is powered off. 1. True 2. False 12. [2 points] If a hypothetical system is not constrained by chip area, memory cost (\$), and energy consumption, DRAM would be the best memory technology to use in that system. 1. True

1. True 2. False

14. [2 points] Virtual-to-physical address translation is on the critical path of a memory access.

2. False 1. True

15. [2 points] Virtual memory makes programmer's and microarchitect's tasks easier.

13. 2 points The entire page table is typically stored in physical memory.

1. True 2. False

Final Exam Page 10 of 26

## 6 Performance Evaluation [70 points]

Some fellow students are working on a project called *AwesomeMEM*, where their goal is to optimize the memory hierarchy (caches and DRAM) to enhance the performance of a multi-core system.

They evaluate two system configurations. First, the *Baseline* configuration constitutes a system with two processors, a last-level cache (LLC), and DRAM as main memory. Second, the *AwesomeMEM* configuration builds on top of the *Baseline* configuration by employing optimizations to the memory hierarchy.

The students evaluate the performance benefits of AwesomeMEM in simulation as follows:

- 1. First, they collect performance metrics of four single-threaded applications  $(App_1, App_2, App_3, App_4)$  running in isolation in the *Baseline* configuration.

- 2. Second, they create two-application mixes to perform a multi-program simulation, where two applications run concurrently in the *Baseline* configuration, each in a dedicated processor. They evaluate two application mixes:  $Mix_1$  (consisting of  $App_1$  and  $App_2$ ); and  $Mix_2$  (consisting of  $App_3$  and  $App_4$ ).

- 3. Third, they use the same two-application mixes as in the second step to perform a multi-program simulation, where two applications run *concurrently* in the *AwesomeMEM* configuration, each in a dedicated processor.

Table 1 summarizes the performance metrics the students collected for each step.

| Execution  | Application | Configuration | Application | Executed     | Executed                | LLC           | Branch                 | DRAM Bank         |  |

|------------|-------------|---------------|-------------|--------------|-------------------------|---------------|------------------------|-------------------|--|

| Mode       | Mix         | Configuration | Application | Instructions | $\operatorname{Cycles}$ | Miss Rate (%) | Misprediction Rate (%) | Conflict Rate (%) |  |

|            |             |               | $App_1$     | 100,000      | 40,000                  | 26%           | 1%                     | 42%               |  |

| Single-    | N/A         | Baseline      | $App_2$     | 100,000      | 800,000                 | 99%           | 1%                     | 94%               |  |

| threaded   | N/A         | Daseille      | $App_3$     | 100,000      | 500,000                 | 52%           | 1%                     | 89%               |  |

|            |             |               | $App_4$     | 100,000      | 20,000                  | 10%           | 1%                     | 14%               |  |

|            | $Mix_1$     | Baseline      | $App_1$     | 100,000      | 200,000                 | 99%           | 1%                     | 97%               |  |

|            |             |               | $App_2$     | 100,000      | 900,000                 | 9970          | 170                    | 3170              |  |

|            |             | AwesomeMEM    | $App_1$     | 80,000       | 100,000                 | 65%           | 1%                     | 55%               |  |

| Multi-     |             | Awesomemin    | $App_2$     | 80,000       | 400,000                 | 0070          | 170                    | 9970              |  |

| programmed |             | Baseline      | $App_3$     | 100,000      | 600,000                 | 60%           | 1%                     | 90%               |  |

|            | $Mix_2$     | Dascinic      | $App_4$     | 100,000      | 20,000                  | 5570          | 170                    | 9 9 7 0           |  |

|            | 1.1 0.02    | AwesomeMEM    | $App_3$     | 80,000       | 400,000                 | 50%           | 1%                     | 45%               |  |

|            |             | 11comenium    | $App_4$     | 100,000      | 20,000                  | 5570          | 170                    | 4970              |  |

(a) [20 points] What is the Instructions Per Cycle (IPC) of each of the four applications when the

Table 1: Performance metrics the students collected.

Answer the following questions based on the performance metrics the students collected.

| application is executed in isolation in the Baseline configuration? Show your work. |

|-------------------------------------------------------------------------------------|

| $App_1$ :                                                                           |

|                                                                                     |

| $App_2$ :                                                                           |

|                                                                                     |

| $App_3$ :                                                                           |

|                                                                                     |

| $App_4$ :                                                                           |

|                                                                                     |

|                                                                                     |

Final Exam Page 11 of 26

(c) [10 points] What is the weighted speedup of each of the two application mixes when it is executed in the Baseline configuration? Show your work.

$Mix_1$ :

Final Exam Page 12 of 26

| Initia | als:                     | Digital Design and Computer Architecture                                                                                               | August 11th, 2022         |

|--------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|        | $Mix_2$ :                |                                                                                                                                        |                           |

|        |                          |                                                                                                                                        |                           |

| (d)    | -                        | the $weighted\ speedup$ of each of the two application in $M$ configuration? Show your work.                                           | nixes when it is executed |

|        | $Mix_1$ :                |                                                                                                                                        |                           |

|        |                          |                                                                                                                                        |                           |

|        | $Mix_2$ :                |                                                                                                                                        |                           |

|        |                          |                                                                                                                                        |                           |

| provi  | ided the following list  | at to reveal the primary technique behind Awesome of architectural techniques and told you that some of system throughput improvement: |                           |

| (i)    | AwesomeMEM incre         | eases the LLC capacity by $2 \times$ that of the <i>Baseline</i> .                                                                     |                           |

| (ii)   | Awe some MEM rand        | domizes main memory requests to reduce DRAM ban                                                                                        | k conflicts.              |

| (iii)  | Awe some MEM  emprectly. | ploys a perfect branch predictor that always predicts                                                                                  | a branch's direction cor- |

| (iv)   | Awe some MEM  emp        | oloys an efficient hardware prefetcher.                                                                                                |                           |

| (e)    |                          | of the above explanations ${\bf cannot}$ possible be a real over the ${\it Baseline}$ ? Explain your reasoning based on                |                           |

|        |                          |                                                                                                                                        |                           |

|        |                          |                                                                                                                                        |                           |

|        |                          |                                                                                                                                        |                           |

|        |                          |                                                                                                                                        |                           |

|        |                          |                                                                                                                                        |                           |

|        |                          |                                                                                                                                        |                           |

Final Exam Page 13 of 26

#### Pipelining [70 points] 7

The following piece of code runs on an in-order pipelined processor as shown in the table (F: Fetch, D: Decode, E: Execute, M: Memory, W: Write back). Instructions are in the form "Instruction Destination, Source2/Immediate." For example, "ADD A, B, C" means A  $\leftarrow$  B + C.

|   | Cycles         | 1 | 2  | 3  | 4  | 5  | 6  | 7  | 8            | 9  | 10 | 11 | 12 | 13           | 14 | 15 | 16           |

|---|----------------|---|----|----|----|----|----|----|--------------|----|----|----|----|--------------|----|----|--------------|

| 1 | MUL R5, R6, R7 | F | D1 | D2 | E1 | E2 | E3 | M  | W            |    |    |    |    |              |    |    |              |

| 2 | ADDI R4, R6, 5 |   | F  | -  | D1 | E1 | _  | -  | $\mathbf{M}$ | W  |    |    |    |              |    |    |              |

| 3 | MUL R4, R7, R8 |   |    |    | F  | D1 | D2 | E1 | E2           | E3 | Μ  | W  |    |              |    |    |              |

| 4 | ADD R5, R5, R6 |   |    |    |    | F  | -  | D1 | E1           | -  | _  | Μ  | W  |              |    |    |              |

| 5 | ADD R6, R7, R5 |   |    |    |    |    |    | F  | D1           | -  | _  | -  | E1 | $\mathbf{M}$ | W  |    | İ            |

| 6 | ADD R7, R1, R4 |   |    |    |    |    |    |    | F            | -  | _  | -  | D1 | D2           | E1 | Μ  | $\mathbf{w}$ |

Use this information to reverse engineer the microarchitecture of this processor to answer the following questions. Answer the questions as precisely as possible with the provided information. If the provided information is not sufficient to answer a question, answer "Unknown" and explain your reasoning clearly.

| ( | a) | [10 points] | What is the ALU's latency | y for an addition and | d for a multiplication | . respectively? |

|---|----|-------------|---------------------------|-----------------------|------------------------|-----------------|

| (4) |                                                                 | o me o marcine, | Tor air addresor. | and for a marriphoe |                   |         |

|-----|-----------------------------------------------------------------|-----------------|-------------------|---------------------|-------------------|---------|

|     | Addition:                                                       |                 |                   |                     |                   |         |

|     | Multiplication:                                                 |                 |                   |                     |                   |         |

| (b) | ) [10 points] Does this p<br>Explain your reasonin              |                 | ment data forwar  | eding? If so, betwe | en which pipeline | stages? |

|     |                                                                 |                 |                   |                     |                   |         |

|     |                                                                 |                 |                   |                     |                   |         |

| (c) | ) [10 points] The numb<br>Explain why this mig<br>decode stage. |                 |                   |                     |                   |         |

|     |                                                                 |                 |                   |                     |                   |         |

|     |                                                                 |                 |                   |                     |                   |         |

Final Exam Page 14 of 26

(f) [15 points] Is it possible to run this code faster by adding more data forwarding paths to the original pipeline? If it is, explain how and calculate the speedup with respect to the original pipeline assuming the changes do not impact clock frequency. Otherwise, explain why it is not

Final Exam Page 15 of 26

#### Tomasulo's Algorithm [60 points] 8

Consider an in-order fetch, out-of-order dispatch, and in-order retirement execution engine that employs Tomasulo's algorithm. This engine has the following characteristics:

- The engine has four main pipeline stages: Fetch (F), Decode (D), Execute (E), and Write-back (W).

- The engine can fetch one instruction per cycle, decode one instruction per cycle, and write back the result of one instruction per cycle.

- The engine has two execution units: 1) an adder to execute ADD instructions and 2) a multiplier to execute MUL instructions.

- The execution units are fully pipelined. The adder has two stages (E1-E2), and the multiplier has four stages (E1-E2-E3-E4). Execution of each stage takes one cycle.

- The adder has a two-entry reservation station, and the multiplier has a three-entry reservation station.

- An instruction always allocates the first available entry of the reservation station (in top-to-bottom order) of the corresponding execution unit.

- Full data forwarding is available, i.e., during the last cycle of the E stage, the tags and data are broadcast to the reservation station and the Register Alias Table (RAT). For example, an ADD instruction updates the reservation station entries of the dependent instructions in the E2 stage. So, the updated value can be read from the reservation station entry in the next cycle. Therefore, a dependent instruction can potentially begin its execution in the next cycle (after E2).

- The multiplier and adder have separate output data buses, which allow both the adder and the multiplier to update the reservation station and the RAT in the same cycle.

- An instruction continues to occupy a reservation station slot until it finishes the Write-back (W) stage. The reservation station entry is deallocated after the Write-back (W) stage.

#### 8.1 **Problem Definition**

The processor is to fetch and execute five instructions. Assume the reservation stations (RS) are all initially empty, and the initial state of the register alias table (RAT) is given below in Figure (a). Instructions are fetched, decoded, and executed as discussed in class. At some point during the execution of the five instructions, a snapshot of the state of the RS and the RAT is taken. Figures (b) and (c) show the state of the RS and the RAT at the snapshot time. A dash (-) indicates that a value has been cleared. A question mark (?) indicates that a value is unknown to you.

Value

256

28

50

| Reg | Valid | Tag | Value |

|-----|-------|-----|-------|

| R0  | 1     | -   | 256   |

| R1  | 1     | -   | 28    |

| R2  | 1     | _   | 1     |

| R3  | 1     | -   | 3     |

| R4  | 1     | _   | 30    |

| R5  | 1     | _   | 5     |

| R6  | 1     | _   | 23    |

| R7  | 1     | _   | 20    |

| R8  | 1     | _   | 61    |

| R9  | 1     | _   | 4     |

|                                   | K4 | 1 | 1 | 30 |  |

|-----------------------------------|----|---|---|----|--|

|                                   | R5 | 0 | X | ?  |  |

|                                   | R6 | 1 | ? | 23 |  |

|                                   | R7 | 0 | Y | ?  |  |

|                                   | R8 | 0 | Z | ?  |  |

|                                   | R9 | 0 | Т | ?  |  |

| (b) State of the RAT at the snap- |    |   |   |    |  |

Valid

1

1

Tag

Reg

R0

R1

R2

R3

(a) Initial state of the RAT

shot time

| ID | V   | Tag | Value | V | Tag | Value |  |

|----|-----|-----|-------|---|-----|-------|--|

| -  | - 1 | -   | -     | - | -   | -     |  |

| Z  | 1   | ?   | 28    | 1 | ?   | 1     |  |

| +  |     |     |       |   |     |       |  |

| ID | V | Tag | Value         | V | Tag | Value |

|----|---|-----|---------------|---|-----|-------|

| X  | 1 | ?   | 50            | 1 | ?   | 1     |

| Y  | 0 | X   | ?             | 1 | ?   | 20    |

| T  | 1 | ?   | 23            | 1 | ?   | 50    |

|    |   |     | $\overline{}$ |   | ,   |       |

|    |   | \   | X             |   |     |       |

(c) State of the RS at the snapshot time

Final Exam Page 16 of 26

## 8.2 Questions

## 8.2.1 Dataflow Graph [40 points]

Based on the information provided above, identify the instructions and provide the dataflow graph below for the instructions that have been fetched. Please appropriately connect the nodes using edges and specify the direction of each edge. Label each edge with the destination architectural register and the corresponding Tag.

# 8.2.2 Program Instructions [20 points]

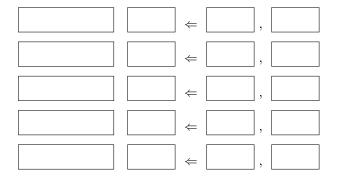

Fill in the blanks below with the five-instruction sequence in program order. There can be more than one correct ordering. Please provide *only one* correct ordering. When referring to registers, please use their architectural names (R0 through R9). Place the register with the smaller architectural name on the left source register box.

For example, ADD R8  $\Leftarrow$  R1, R5.

Final Exam Page 17 of 26

#### 9 GPUs and SIMD [45 points]

We define the SIMD utilization of a program that runs on a GPU as the fraction of SIMD lanes that are kept busy with active threads during the run of a program. As we saw in lecture and practice exercises, the SIMD utilization of a program is computed across the complete run of the program.

The following code segment is run on a GPU. A warp in the GPU consists of 32 threads, and there are 32 SIMD lanes in the GPU. Each thread executes a single iteration of the shown loop. Assume that the data values of the arrays A, B and C are already in vector registers so there are no loads and stores in this program. Both B and C are arrays of integers and each integer in these arrays has an absolute value of less than 10 (i.e., |B[i]| < 10 and |C[i]| < 10, for all i).

```

for (i = 0; i < 1024; i++) {

A[i] = B[i] * C[i];

// instruction 1

if (/* Condition */) { // instruction 2

// instruction 3

// instruction 4

// instruction k + 2

C[i] = C[i] - 1; // instruction k + 3

```

Please answer the following four questions.

| , 1 , 1 | any warps does it | F - 8 |  |

|---------|-------------------|-------|--|

|         |                   |       |  |

|         |                   |       |  |

|         |                   |       |  |

|         |                   |       |  |

|         |                   |       |  |

(b) [20 points] Assume that the condition for the if statement is (i % 16 == 0). What is the number of instructions (k) in the body of the conditional block given a SIMD utilization of  $\frac{11}{22}$ ? Assume that there are **no** control flow instructions in the body of the if statement. Show your work.

Final Exam Page 18 of 26

| (c) | [20 points] Assume that the condition for the if statement is (i % 16 == 0 && i < 512) What is the number of instructions (k) in the body of the conditional block given a SIMD utilization of $\frac{5}{8}$ ? Assume that there are <b>no</b> control flow instructions in the body of the if statement. Show your work. |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                                                                                                                                                                                                                                                           |

Final Exam Page 19 of 26

## 10 Branch Prediction [70 points]

A processor implements an *in-order* pipeline with multiple stages. Each stage completes in a single cycle. The pipeline stalls after fetching a *conditional branch instruction* and resumes execution once the condition of the branch is evaluated. There is no other case in which the pipeline stalls.

## 10.1 Part I: Microbenchmarking [30 points]

You create a microbenchmark as follows to reverse-engineer the pipeline characteristics:

```

LOOP1:

SUB R1, R1, #1 // R1 = R1 - 1

BGT R1, LOOP1 // Branch to LOOP1 if R1 > 0

LOOP2:

B LOOP2 // Branch to LOOP2

// Repeats until program is killed

```

The microbenchmark takes one input value R1 and runs until it is killed (e.g., via an external interrupt).

You carefully run the microbenchmark using different input values (R1) as summarized in Table 2. You terminate the microbenchmark using an external interrupt such that each run is guaranteed to execute exactly 50 dynamic instructions (i.e., the instructions actually executed by the processor, in contrast to static instructions, which is the number of instructions the microbenchmark has).

| Initial R1 Value | Number of Cycles Taken |

|------------------|------------------------|

| 2                | 71                     |

| 4                | 83                     |

| 8                | 107                    |

| 16               | 155                    |

Table 2: Microbenchmark results.

Using this information, you need to determine the following two system characteristics. Clearly show all work to receive full points!

- 1. How many stages are in the pipeline?

- 2. For how many cycles does a conditional branch instruction cause a stall?

Final Exam Page 20 of 26

#### Part II: Performance Enhancement [40 points] 10.2

To improve performance, the designers add a *mystery* branch prediction mechanism to the processor. All we know about this mystery branch prediction is that it does not stall the piepline at all if the prediction is correct. They keep the rest of the design exactly the same as before. You re-run the same microbenchmark with R1 = 4 for the same number of total dynamic instructions with the new design, and you find that the microbenchmark executes in 77 cycles.

| and you mid that the mici  | obenchinark executes in 77 cycles.                                                                                                                                                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| be the $mystery$ branch pr | nation, determine which of the following branch prediction mechanisms could edictor implemented in the new version of the processor. For each branch by, you should circle the configuration parameters that makes it match the y branch predictor. |

| (a) [10 points] Static B   | ranch Predictor                                                                                                                                                                                                                                     |

| Could this be the my       | stery branch predictor: YES NO                                                                                                                                                                                                                      |

| If YES, for which cor      | nfiguration below is the answer YES?                                                                                                                                                                                                                |

| (I) Static Predictio       | n Direction                                                                                                                                                                                                                                         |

| Always taker               | n Always not taken                                                                                                                                                                                                                                  |

| Explain:                   |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

| (b) [10 points] Last Tin   | ne Branch Predictor                                                                                                                                                                                                                                 |

| Could this be the my       | stery branch predictor?                                                                                                                                                                                                                             |

| YES                        | NO                                                                                                                                                                                                                                                  |

| If YES, for which con      | figuration is the answer $\it YES$ ? Pick an option for each configuration parameter.                                                                                                                                                               |

| (I) Initial Predictio      | n Direction                                                                                                                                                                                                                                         |

| Taken                      | Not taken                                                                                                                                                                                                                                           |

| (II) Local for each b      | branch instruction (PC-based) or global (shared among all branches) history?                                                                                                                                                                        |

| Local                      | Global                                                                                                                                                                                                                                              |

|                            |                                                                                                                                                                                                                                                     |

| Explain:                   |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                     |

Final Exam Page 21 of 26

| Initials: |                                             | Digital Design and Computer Architecture | August 11th, 2022 |  |  |  |  |  |  |

|-----------|---------------------------------------------|------------------------------------------|-------------------|--|--|--|--|--|--|

| (c)       | [10 points] Backwa                          | ard taken, Forward not taken (BTFN)      |                   |  |  |  |  |  |  |

|           | Could this be the mystery branch predictor? |                                          |                   |  |  |  |  |  |  |

|           | YES                                         | NO                                       |                   |  |  |  |  |  |  |

|           | Explain:                                    |                                          |                   |  |  |  |  |  |  |

|           |                                             |                                          |                   |  |  |  |  |  |  |

|           |                                             |                                          |                   |  |  |  |  |  |  |

|           |                                             |                                          |                   |  |  |  |  |  |  |

|           |                                             |                                          |                   |  |  |  |  |  |  |

| (d)       | [10 points] Forwar                          | d taken, Backward not taken (FTBN)       |                   |  |  |  |  |  |  |

|           | Could this be the n                         | nystery branch predictor?                |                   |  |  |  |  |  |  |

|           | YES                                         | NO                                       |                   |  |  |  |  |  |  |

|           | Explain:                                    |                                          |                   |  |  |  |  |  |  |

|           |                                             |                                          |                   |  |  |  |  |  |  |

|           |                                             |                                          |                   |  |  |  |  |  |  |

Final Exam Page 22 of 26

# 11 BONUS: Data Prefetching [50 points]

You and your colleague are tasked with designing the prefetcher of a machine your company is designing. The machine has a single processor attached to a main memory (DRAM) system.

You need to examine different prefetcher designs and analyze the trade-offs involved. For all parts of this question, you need to compute the *coverage* or *overhead* of the prefetcher in its **steady state**.

You run an application that has the following memory access pattern (note that these are cache block addresses). Assume this memory access pattern repeats for a long time.

$A, A+1, A+9, A+10, A+18, A+19, A+27, A+28, A+36, A+37, \dots$

(a) [10 points] You first design a stride prefetcher  $Pref_X$  that observes the last three cache block requests. If there is a constant stride S between the last three requests,  $Pref_X$  issues a prefetch to the next cache block using the stride S. In absence of a constant stride,  $Pref_X$  refrains from prefetching. What is the coverage of  $Pref_X$  for the application? Show your work. Please recall, prefetcher coverage is defined as:

$\frac{Total\ number\ of\ prefetch\ requests\ used\ by\ the\ program}{Total\ number\ of\ main\ memory\ requests\ without\ the\ prefetcher}$

| cacheline of $Pref_Y$ |

|-----------------------|

|                       |

|                       |

|                       |

|                       |

Final Exam Page 23 of 26

Final Exam Page 24 of 26

# 12 BONUS: Cache Reverse Engineering [70 points]

You are trying to reverse-engineer the cache associativity in a newly-released system. You already know that the cache has a FIFO replacement policy and 8 blocks with a block size of 4 B. Starting with an empty cache, an application accesses five byte addresses in the following order

$$2 \quad \rightarrow \quad 9 \quad \rightarrow \quad 16 \quad \rightarrow \quad 25 \quad \rightarrow \quad 33$$

Assume you can access three addresses after the above sequence and observe the cache hit rate across these three accesses.

| 1. | [30 points] Which three addresses should you access in order to identify the set-associativity of the |

|----|-------------------------------------------------------------------------------------------------------|

|    | cache (1-, 2-, 4- or 8-way)? There may be multiple solutions; please give the lowest possible         |

|    | addresses that can enable the identification of the set-associativity. Please explain every           |

|    | step in detail to get full points.                                                                    |

Final Exam Page 25 of 26

2. [20 points] What is the associativity of the cache if the cache hit rate observed over the 3 extra addresses accessed in Part (1) were:

| Hit rate | Associativity |

|----------|---------------|

| 0        |               |

| 1/3      |               |

| 2/3      |               |

| 1        |               |

3. [20 points] When you accessed the three addresses you determined in Part (1), you observed a 100% hit rate across these three accesses. Now, your friend asks you to access four more addresses in the following order:

$$32 \rightarrow 0 \rightarrow 8 \rightarrow 28$$

Which of the above four addresses would result in a cache miss?

| 1   |  |

|-----|--|

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| ı   |  |

| - 1 |  |

Final Exam Page 26 of 26