# Digital Design & Computer Arch. Lecture 27: Epilogue

Prof. Onur Mutlu

ETH Zürich Spring 2022 9 June 2022

# No Required Readings (for this lecture)

### Recall: Major High-Level Goals of This Course

- In Digital Circuits & Computer Architecture

- Understand the basics

- Understand the principles (of design)

- Understand the precedents

- Based on such understanding:

- learn how a modern computer works underneath

- evaluate tradeoffs of different designs and ideas

- implement a principled design (a simple microprocessor)

- learn to systematically debug increasingly complex systems

- Hopefully enable you to develop novel, out-of-the-box designs

- The focus is on basics, principles, precedents, and how to use them to create/implement good designs

## Recall: Why These Goals?

- Because you are here for a Computer Science degree

- Regardless of your future direction, learning the principles of digital design & computer architecture will be useful to

- design better hardware

- design better software

- design better systems

- make better tradeoffs in design

- understand why computers behave the way they do

- solve problems better

- think "in parallel"

- think critically

# We Have Come A Long Way

- Started from Transistor as the Building Block

- Logic Design (Combinational, Sequential, Timing)

- Execution Model, ISA and Microarchitecture

- Many Key Processing Paradigms

- The Memory System and the Memory Hierarchy

- Built up to Virtual Memory & System Software Mechanisms

- Takeaway 1: All we covered is real and used in real systems

→ and, it is increasingly important

- Takeaway 2: Principles we covered apply broadly

- Takeaway 3: Tradeoff analysis and critical thinking that you are exposed to apply even more broadly

### Recall: We Are **Done** With This...

- Single-cycle Microarchitectures

- Multi-cycle and Microprogrammed Microarchitectures

- Pipelining

- Issues in Pipelining: Control & Data Dependence Handling, State Maintenance and Recovery, ...

- Out-of-Order Execution

- Other Execution Paradigms

### Approaches to (Instruction-Level) Concurrency

- Pipelining

- Fine-Grained Multithreading

- Out-of-order Execution

- Dataflow (at the ISA level)

- Superscalar Execution

- VLIW

- Systolic Arrays

- Decoupled Access Execute

- SIMD Processing (Vector and Array processors, GPUs)

Now you are very familiar with many processing paradigms

### Approaches to (Instruction-Level) Concurrency

- Pipelining

- Fine-Grained Multithreading

- Out-of-order Execution

- Dataflow (at the ISA level)

- Superscalar Execution

- VLIW

- Systolic Arrays

- Decoupled Access Execute

- SIMD Processing (Vector and Array processors, GPUs)

#### Food for thought: tradeoffs of these different processing paradigms

### We Are Also Done With This...

- Memory Organization & Technology

- Memory Hierarchy & Caches

- Advanced Caches

- Prefetching

- Virtual Memory

Now you are very familiar with memory systems

## We Are Also Done With This...

- Memory Organization & Technology

- Memory Hierarchy & Caches

- Advanced Caches

- Prefetching

- Virtual Memory

Food for thought: tradeoffs of many different memory system designs & ideas

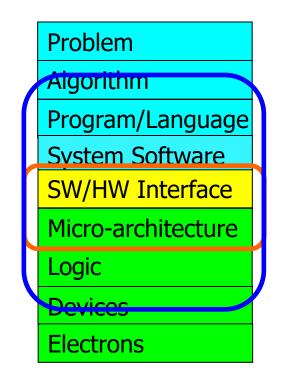

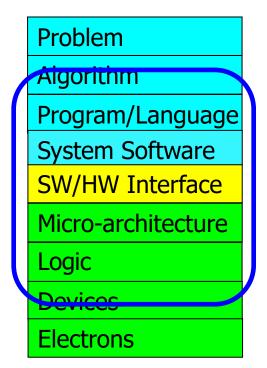

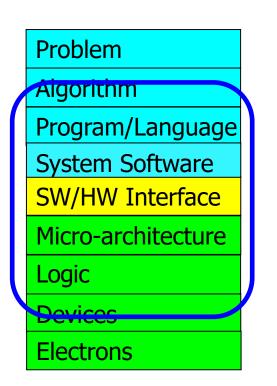

## The Transformation Hierarchy

Computer Architecture (expanded view)

Computer Architecture (narrow view)

#### Food for thought: how do tradeoffs span and affect the hierarchy

#### SAFARI

# The Best Way to Approach This Course

- Take it as a learning and growth experience... all of it

- What we saw changed the world & endured the test of time...

- And, it will be more important...

- You may not all be future architects, but...

- your development and thinking can greatly benefit from the concepts, tradeoffs, principles, critical thinking...

#### **Focus on understanding, learning, critical analysis**

- $\rightarrow$  these are the agents for your growth

- $\rightarrow$  the course is designed to activate these agents (lifelong)

# What We Did Not Cover

# Computer Architecture is Very Rich

- Many ideas, much creativity, many tradeoffs and problems

- As scaling, performance, energy, reliability, security issues become worse in circuits and in software, computer architecture will be more and more important

- Already obvious in

- AI/ML accelerators

- Hardware security issues

- Novel execution paradigms: Processing in memory

• ...

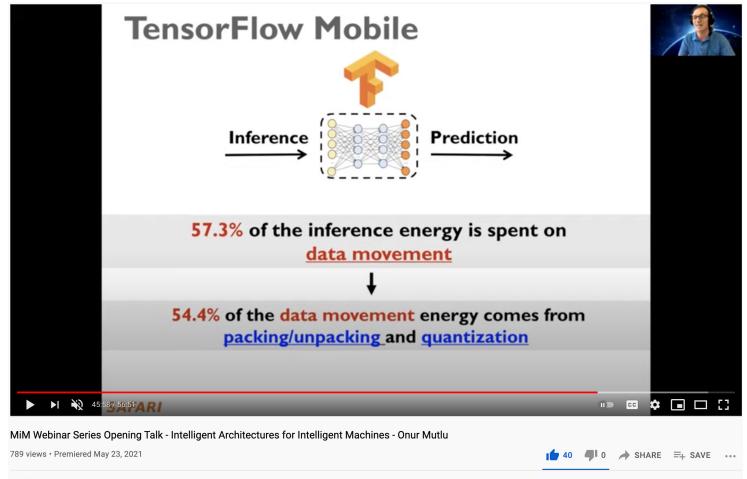

See lecture: Intelligent Architectures for Intelligent Machines

https://www.youtube.com/watch?v=5YKvtNM6XzY

### Intelligent Architectures for Intelligent Machines

Onur Mutlu,

"Intelligent Architectures for Intelligent Machines"

Opening Talk at <u>TU Vienna Mondays in Memory Webinar Series</u> (MiM), Virtual, 3 May 2021.

[Slides (pptx) (pdf)] [Talk Video (57 minutes)]

Onur Mutlu Lectures 16.7K subscribers

https://www.youtube.com/watch?v=5YKvtNM6XzY

ANALYTICS

EDIT VIDEO

### Extra Assignment: Lecture Video Review

- Intelligent Architectures for Intelligent Machines

- Watch this recent lecture and analyze it critically

- https://www.youtube.com/watch?v=5YKvtNM6XzY (May 2021)

#### Optional Assignment – for 1% extra credit

- Write a 1-page summary of your analysis

- What are your key takeaways?

- What did you learn?

- What did you like or dislike?

- Use past review guidelines

- Submit your summary to <u>Moodle</u> Deadline: June 20

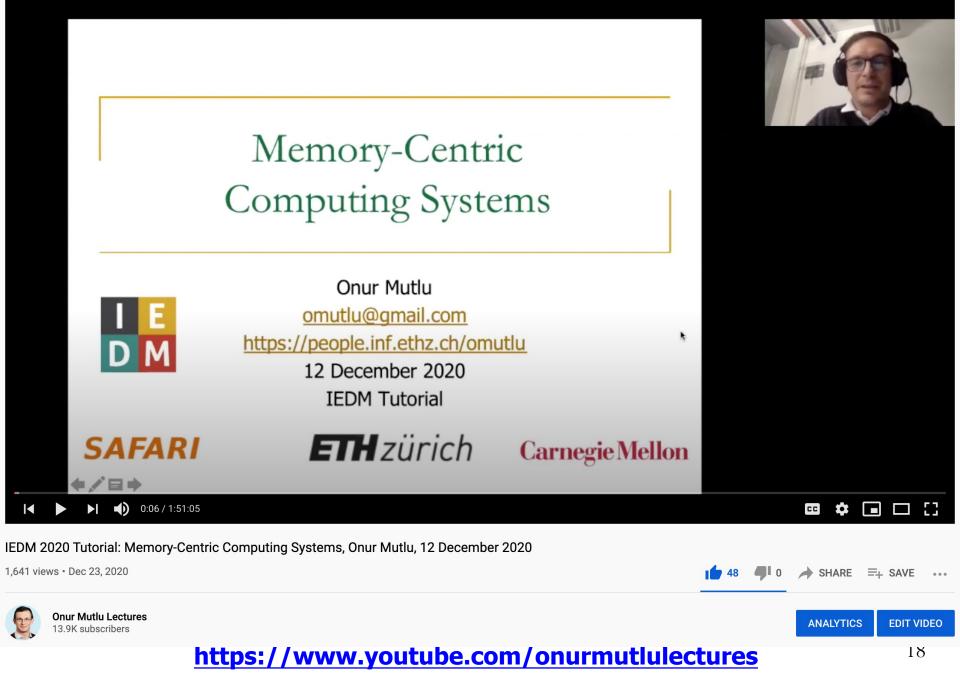

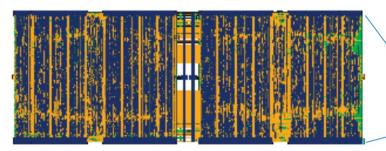

# A Tutorial on Memory-Centric Systems

Onur Mutlu, <u>"Memory-Centric Computing Systems"</u> Invited Tutorial at 66th International Electron Devices *Meeting (IEDM)*, Virtual, 12 December 2020. [Slides (pptx) (pdf)] [Executive Summary Slides (pptx) (pdf)] [Tutorial Video (1 hour 51 minutes)] [Executive Summary Video (2 minutes)] Abstract and Bio [Related Keynote Paper from VLSI-DAT 2020] [Related Review Paper on Processing in Memory]

https://www.youtube.com/watch?v=H3sEaINPBOE

https://www.youtube.com/onurmutlulectures

### Architectures for Intelligent Machines

# **Data-centric**

# **Data-driven**

# **Data-aware**

#### **SAFARI**

Source: http://spectrum.ieee.org/image/MjYzMzAyMg.jpeg

# Recall: Takeaways

- It is an exciting time to be understanding and designing computing architectures

- Many challenging and exciting problems in platform design

- That no one has tackled (or thought about) before

- That can have huge impact on the world's future

- Driven by huge hunger for data (Big Data), new applications (ML/AI, graph analytics, genomics), ever-greater realism, ...

We can easily collect more data than we can analyze/understand

- Driven by significant difficulties in keeping up with that hunger at the technology layer

- □ Five walls: Energy, reliability, complexity, security, scalability

### State of the Art

- This is a great time to be a computer architect

- Circuits strained

- Applications ever more demanding

- Multiple possible emerging technologies

- Many requirements, many systems

- Many, many security, reliability issues

- Many big problems waiting to be solved

All across the hierarchy

#### Many big innovations require computer architecture

Many Interesting Things Are Happening Today in Computer Architecture

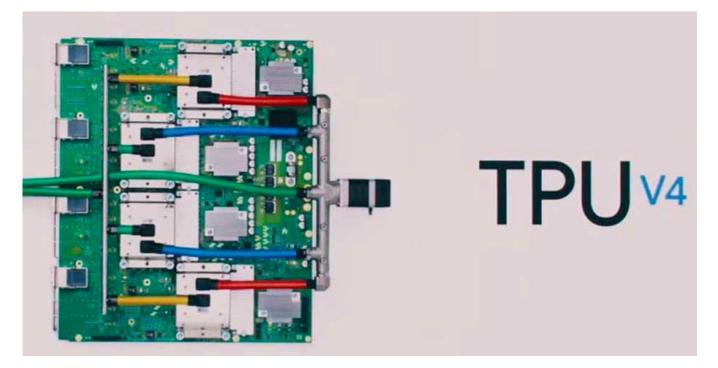

### New Generation of Google TPU v4 (2021)

#### New ML applications (vs TPU3):

- Computer vision

- Natural Language Processing (NLP)

- Recommender system

- Reinforcement learning that plays Go

250 TFLOPS per chip vs 90 TFLOPS in TPU3

https://spectrum.ieee.org/tech-talk/computing/hardware/heres-how-googles-tpu-v4-ai-chip-stacked-up-in-training-tests

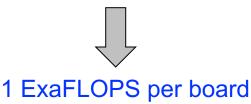

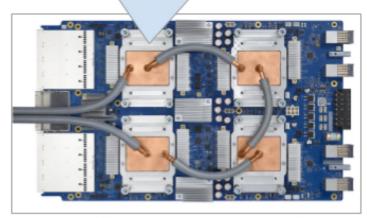

# An Example Modern Systolic Array: TPU3

TPU v2 - 4 chips, 2 cores per chip

TPU v3 - 4 chips, 2 cores per chip

#### 32GB HBM per chip vs 16GB HBM in TPU2

#### 4 Matrix Units per chip 90 TFLOPS per chip vs 2 Matrix Units in TPU2

vs 45 TFLOPS in TPU2

# An Example Modern Systolic Array: TPU2

https://www.nextplatform.com/2017/05/17/first-depth-look-googles-new-second-generation-tpu/

#### 4 TPU chips vs 1 chip in TPU1

High Bandwidth Memory vs DDR3

# Floating point operations vs FP16

45 TFLOPS per chip vs 23 TOPS

Designed for training and inference vs only inference

## An Example Modern Systolic Array: TPU (I)

Control

**Figure 3.** TPU Printed Circuit Board. It can be inserted in the slot for an SATA disk in a server, but the card uses PCIe Gen3 x16.

**Figure 4.** Systolic data flow of the Matrix Multiply Unit. Software has the illusion that each 256B input is read at once, and they instantly update one location of each of 256 accumulator RAMs.

#### Jouppi et al., "In-Datacenter Performance Analysis of a Tensor Processing Unit", ISCA 2017.

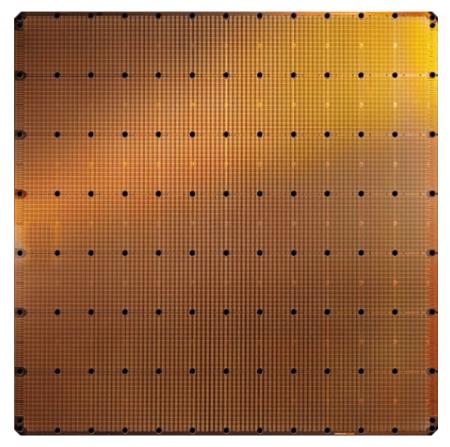

# Cerebras's Wafer Scale Engine-2 (2021)

- The largest ML accelerator chip

- 850,000 cores

- 40 GB of on-chip memory

- 20 PB/s memory bandwidth

Largest GPU 54.2 Billion transistors 826 mm<sup>2</sup> NVIDIA Ampere GA100

Cerebras WSE-2 2.6 Trillion transistors 46,225 mm<sup>2</sup>

https://cerebras.net/product/#overview

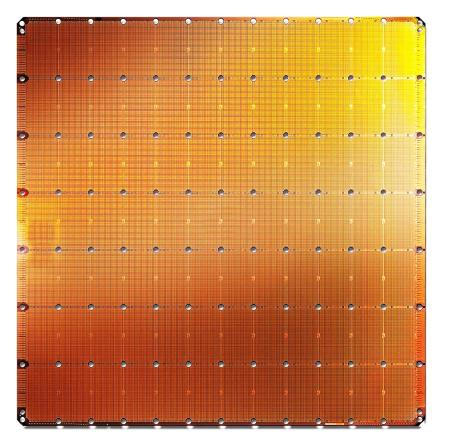

# Cerebras's Wafer Scale Engine (2019)

- The largest ML accelerator chip

- 400,000 cores

- 18 GB of on-chip memory

- 9 PB/s memory bandwidth

Cerebras WSE 1.2 Trillion transistors 46,225 mm<sup>2</sup> Largest GPU 21.1 Billion transistors 815 mm<sup>2</sup>

https://www.anandtech.com/show/14758/hot-chips-31-live-blogs-cerebras-wafer-scale-deep-learning

https://www.cerebras.net/cerebras-wafer-scale-engine-why-we-need-big-chips-for-deep-learning?

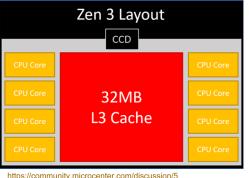

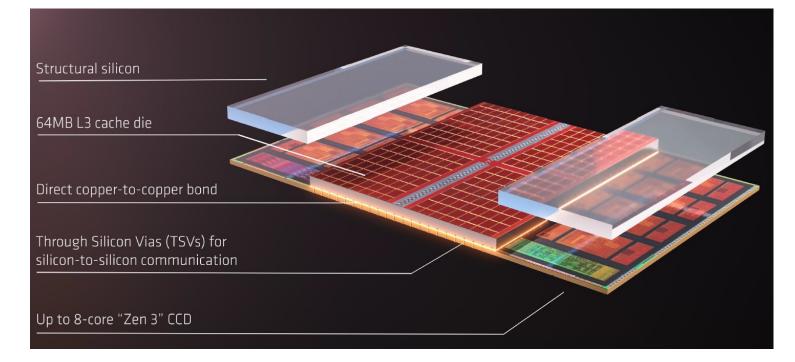

# AMD's 3D Last Level Cache (2021)

https://community.microcenter.com/disc 134/comparing-zen-3-to-zen-2 AMD increases the L3 size of their 8-core Zen 3 processors from 32 MB to 96 MB

Additional 64 MB L3 cache die stacked on top of the processor die

- Connected using Through Silicon Vias (TSVs)

- Total of 96 MB L3 cache

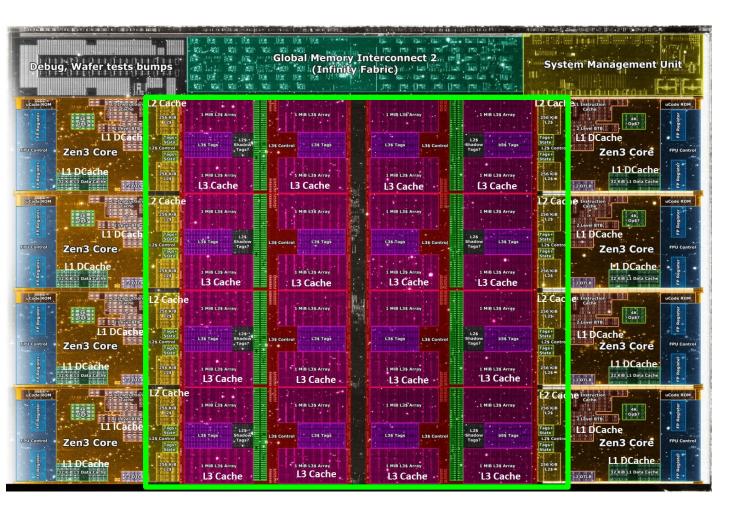

# Recall: Deeper and Larger Cache Hierarchies

Core Count: 8 cores/16 threads

L1 Caches: 32 KB per core

L2 Caches: 512 KB per core

L3 Cache: 32 MB shared

#### AMD Ryzen 5000, 2020

# Many Other Ideas and Topics

- Advanced memory systems

- Self-optimizing architectures (using machine learning principles)

- Processing-in-memory systems

- Emerging memory technologies

- Solid state disks and storage, I/O

- Interconnection networks, communication networks

- Many issues in multiprocessing and multithreading

- Distributed architectures

- Heterogeneous systems: Heterogeneous CPU-GPU-FPGA-HWAcc architectures

- QoS and predictable performance

- Reliable and secure architectures

- Programmability, portability

- Better HW/SW interfaces

- Reconfigurable computing

- Specialized and domain-specific architectures genomics, medicine, health, AI/ML

- Unconventional architectures nature-inspired, quantum, molecular, ...

### Oculus, New York City

Source: https://www.dezeen.com/2016/08/29/santiago-calatrava-oculus-world-trade-center-transportation-hub-new-york-photographs-hufton-crow/

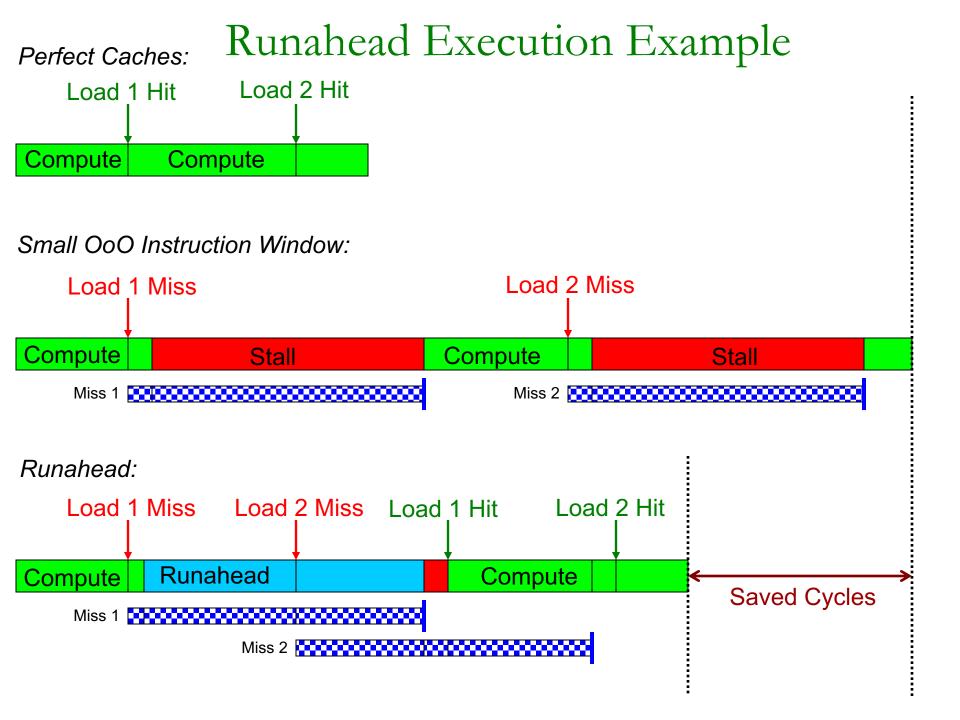

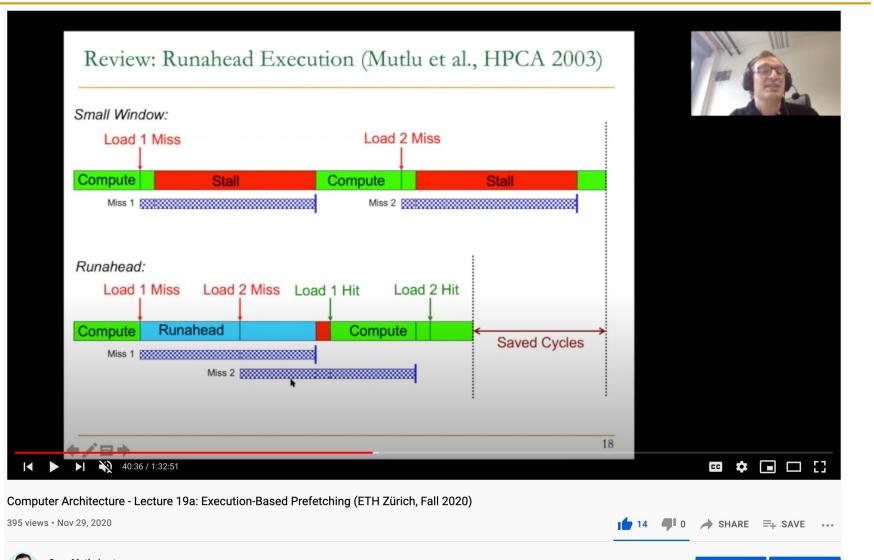

# Recall: Runahead Execution

### Effect of Runahead Prefetching in Sun ROCK

Shailender Chaudhry talk, Aug 2008.

Effective prefetching can both improve performance and reduce hardware cost

## More on Runahead Execution

Onur Mutlu, Jared Stark, Chris Wilkerson, and Yale N. Patt, <u>"Runahead Execution: An Alternative to Very Large Instruction Windows</u> <u>for Out-of-order Processors"</u>

Proceedings of the <u>9th International Symposium on High-Performance Computer</u> <u>Architecture</u> (**HPCA**), pages 129-140, Anaheim, CA, February 2003. <u>Slides (pdf)</u>

One of the 15 computer arch. papers of 2003 selected as Top Picks by IEEE Micro. HPCA Test of Time Award (awarded in 2021).

[Lecture Slides (pptx) (pdf)] [Lecture Video (1 hr 54 mins)] [Retrospective HPCA Test of Time Award Talk Slides (pptx) (pdf)] [Retrospective HPCA Test of Time Award Talk Video (14 minutes)]

#### **Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors**

Onur Mutlu § Jared Stark † Chris Wilkerson ‡ Yale N. Patt §

§ECE Department The University of Texas at Austin {onur,patt}@ece.utexas.edu †Microprocessor Research Intel Labs jared.w.stark@intel.com

‡Desktop Platforms Group Intel Corporation chris.wilkerson@intel.com

#### More on Runahead in Sun ROCK

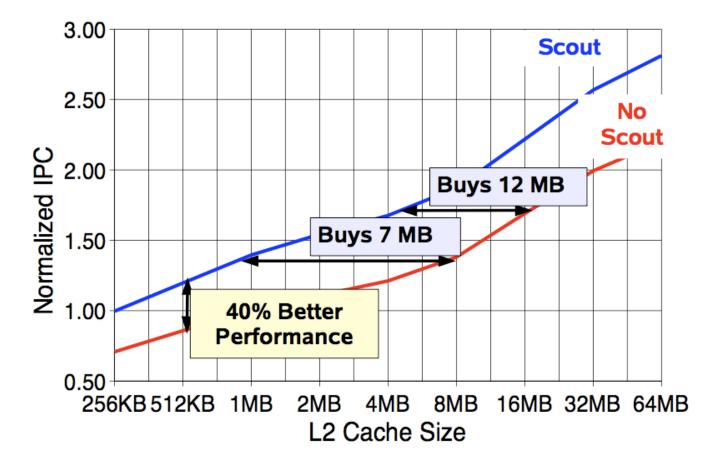

# HIGH-PERFORMANCE THROUGHPUT COMPUTING

THROUGHPUT COMPUTING, ACHIEVED THROUGH MULTITHREADING AND MULTICORE TECHNOLOGY, CAN LEAD TO PERFORMANCE IMPROVEMENTS THAT ARE 10 TO 30× THOSE OF CONVENTIONAL PROCESSORS AND SYSTEMS. HOWEVER, SUCH SYSTEMS SHOULD ALSO OFFER GOOD SINGLE-THREAD PERFORMANCE. HERE, THE AUTHORS SHOW THAT HARDWARE SCOUTING INCREASES THE PERFORMANCE OF AN ALREADY ROBUST CORE BY UP TO 40 PERCENT FOR COMMERCIAL BENCHMARKS.

#### Simultaneous Speculative Threading: A Novel Pipeline Architecture Implemented in Sun's ROCK Processor

Shailender Chaudhry, Robert Cypher, Magnus Ekman, Martin Karlsson, Anders Landin, Sherman Yip, Håkan Zeffer, and Marc Tremblay Sun Microsystems, Inc. 4180 Network Circle, Mailstop SCA18-211 Santa Clara, CA 95054, USA {shailender.chaudhry, robert.cypher, magnus.ekman, martin.karlsson, anders.landin, sherman.yip, haakan.zeffer, marc.tremblay}@sun.com

#### Runahead Execution in IBM POWER6

#### Runahead Execution vs. Conventional Data Prefetching in the IBM POWER6 Microprocessor

Harold W. Cain Priya Nagpurkar

IBM T.J. Watson Research Center Yorktown Heights, NY {tcain, pnagpurkar}@us.ibm.com

Cain+, "Runahead Execution vs. Conventional Data Prefetching in the IBM POWER6 Microprocessor," ISPASS 2010.

#### Runahead Execution in IBM POWER6

#### Abstract

After many years of prefetching research, most commercially available systems support only two types of prefetching: software-directed prefetching and hardware-based prefetchers using simple sequential or stride-based prefetching algorithms. More sophisticated prefetching proposals, despite promises of improved performance, have not been adopted by industry. In this paper, we explore the efficacy of both hardware and software prefetching in the context of an IBM *POWER6* commercial server. Using a variety of applications that have been compiled with an aggressively optimizing compiler to use software prefetching when appropriate, we perform the first study of a new runahead prefetching feature adopted by the POWER6 design, evaluating it in isolation and in conjunction with a conventional hardware-based sequential stream prefetcher and compiler-inserted software prefetching.

We find that the POWER6 implementation of runahead prefetching is quite effective on many of the memory intensive applications studied; in isolation it improves performance as much as 36% and on average 10%. However, it outperforms the hardware-based stream prefetcher on only two of the benchmarks studied, and in those by a small margin. When used in conjunction with the conventional prefetching mechanisms, the runahead feature adds an additional 6% on average, and 39% in the best case (GemsFDTD).

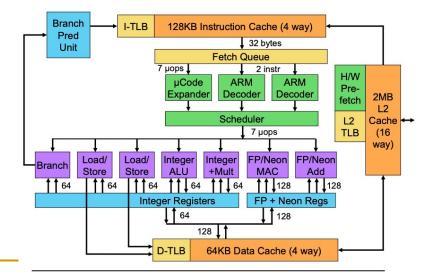

#### Runahead Execution in NVIDIA Denver

# DENVER: NVIDIA'S FIRST 64-BIT ARM Processor

NVIDIA'S FIRST 64-BIT ARM PROCESSOR, CODE-NAMED DENVER, LEVERAGES A HOST OF NEW TECHNOLOGIES, SUCH AS DYNAMIC CODE OPTIMIZATION, TO ENABLE HIGH-PERFORMANCE MOBILE COMPUTING. IMPLEMENTED IN A 28-NM PROCESS, THE DENVER CPU CAN ATTAIN CLOCK SPEEDS OF UP TO 2.5 GHZ. THIS ARTICLE OUTLINES THE DENVER ARCHITECTURE, DESCRIBES ITS TECHNOLOGICAL INNOVATIONS, AND PROVIDES RELEVANT COMPARISONS AGAINST COMPETING MOBILE PROCESSORS.

Boggs+, "Denver: NVIDIA's First 64-Bit ARM Processor," IEEE Micro 2015.

#### Runahead Execution in NVIDIA Denver

Reducing the effects of long cache-miss penalties has been a major focus of the microarchitecture, using techniques like prefetching and run-ahead. An aggressive hardware prefetcher implementation detects L2 cache requests and tracks up to 32 streams, each with complex stride patterns.

Run-ahead uses the idle time that a CPU spends waiting on a long latency operation to discover cache and DTLB misses further down the instruction stream and generates prefetch requests for these misses.<sup>1</sup> These prefetch requests warm up the data cache and DTLB well before the actual execution of the instructions that require the data. Runahead complements the hardware prefetcher because it's better at prefetching nonstrided streams, and it trains the hardware prefetcher faster than normal execution to yield a combined benefit of 13 percent on SPECint2000 and up to 60 percent on SPECfp2000.

Boggs+, "Denver: NVIDIA's First 64-Bit ARM Processor," IEEE Micro 2015.

Gwennap, "NVIDIA's First CPU is a Winner," MPR 2014.

The core includes a hardware prefetch unit that Boggs describes as "aggressive" in preloading the data cache but less aggressive in preloading the instruction cache. It also implements a "run-ahead" feature that continues to execute microcode speculatively after a data-cache miss; this execution can trigger additional cache misses that resolve in the shadow of the first miss. Once the data from the original miss returns, the results of this speculative execution are discarded and execution restarts with the bundle containing the original miss, but run-ahead can preload subsequent data into the cache, thus avoiding a string of time-wasting cache misses. These and other features help Denver outscore Cortex-A15 by more than 2.6x on a memory-read test even when both use the same SoC framework (Tegra K1).

Figure 3. Denver CPU microarchitecture. This design combines a fairly

## Runahead Readings

- Required

- Mutlu et al., "Runahead Execution", HPCA 2003, Top Picks 2003.

#### Recommended

- Mutlu et al., "Efficient Runahead Execution: Power-Efficient Memory Latency Tolerance," ISCA 2005, IEEE Micro Top Picks 2006.

- Mutlu et al., "Address-Value Delta (AVD) Prediction," MICRO 2005.

- Armstrong et al., "Wrong Path Events," MICRO 2004.

#### More on Runahead Execution

- Lecture video from Fall 2020, Computer Architecture:

<u>https://www.youtube.com/watch?v=zPewo6IaJ\_8</u>

- Lecture video from Fall 2017, Computer Architecture:

- https://www.youtube.com/watch?v=Kj3relihGF4

Onur Mutlu, <u>"Efficient Runahead Execution Processors"</u> Ph.D. Dissertation, HPS Technical Report, TR-HPS-2006-007, July 2006. <u>Slides (ppt)</u> *Nominated for the ACM Doctoral Dissertation Award by the University of Texas at Austin.*

## More on Runahead Execution (I)

#### https://www.youtube.com/watch?v=zPewo6laJ\_8&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN&index=34

EDIT VIDEO

ANALYTICS

## More on Runahead Execution (II)

#### Runahead Execution in NVIDIA Denver

Reducing the effects of long cache-miss penalties has been a major focus of the microarchitecture, using techniques like prefetching and run-ahead. An aggressive hardware prefetcher implementation detects L2 cache requests and tracks up to 32 streams, each with complex stride patterns.

Run-ahead uses the idle time that a CPU spends waiting on a long latency operation to discover cache and DTLB misses further down the instruction stream and generates prefetch requests for these misses.<sup>1</sup> These prefetch requests warm up the data cache and DTLB well before the actual execution of the instructions that require the data. Runahead complements the hardware prefetcher because it's better at prefetching nonstrided streams, and it trains the hardware prefetcher faster than normal execution to yield a combined benefit of 13 percent on SPECint2000 and up to 60 percent on SPECfp2000.

Boggs+, "Denver: NVIDIA's First 64-Bit ARM Processor,"

Gwennap, "NVIDIA's First CPU is a Winner," MPR 2014.

The core includes a hardware prefetch unit that Boggs describes as "aggressive" in preloading the data cache but less aggressive in preloading the instruction cache. It also implements a "run-ahead" feature that continues to execute microcode speculatively after a data-cache miss; this execution can trigger additional cache misses that resolve in the shadow of the first miss. Once the data from the original miss returns, the results of this speculative execution are discarded and execution restarts with the bundle containing the original miss, but run-ahead can preload subsequent data into the cache, thus avoiding a string of time-wasting cache misses. These and other features help Denver outscore Cortex-A15 by more than 2.6x on a memory-read test even when both use the same SoC framework (Tegra K1).

IEEE Micro 2015.

Onur Mutlu Lectures 16.5K subscribers

▶ 💦 6:18 / 14:27

📼 🦑 🔳 🖂 🕄

EDIT VIDEO

A SHARE =+ SAVE

ANALYTICS

50

# My Suggestions to You

Suggestion to Researchers: Principle: Passion

# Follow Your Passion (Do not get derailed by naysayers)

#### Principle: Build Infrastructure

# Build Infrastructure to Enable Your Passion

# Work Hard to Enable Your Passion

Suggestion to Researchers: Principle: Resilience

# **Be Resilient**

#### Principle: Learning and Scholarship

# Focus on learning and scholarship

#### Principle: Learning and Scholarship

# The quality of your work defines your impact

#### Principle: Good Mindset, Goals & Focus

# You can make a good impact on the world

#### Recall: This

#### Recall: That

## Recall: A Key Question

- How was Calavatra able to design especially his key buildings?

- Can have many guesses

- (Very) hard work, perseverance, dedication (over decades)

- Experience

- Creativity, Out-of-the-box thinking

- A good understanding of past designs

- Good judgment and intuition

- Strong skill combination (math, architecture, art, engineering, ...)

- Funding (\$\$\$, luck, initiative, entrepreneurialism

- Strong understanding of and commitment to fundamentals

- Principled design

- **.**..

- You will be exposed to and hopefully develop/enhance many of these skills in this course

# Processing in Memory

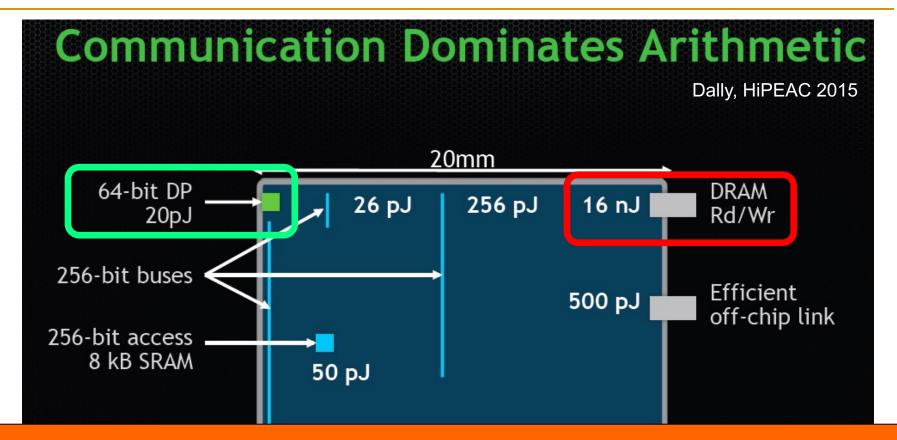

Data access is the major performance and energy bottleneck

# Our current design principles cause great energy waste (and great performance loss)

# Processing of data is performed far away from the data

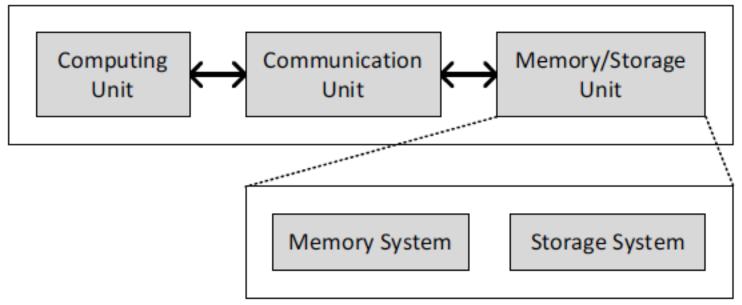

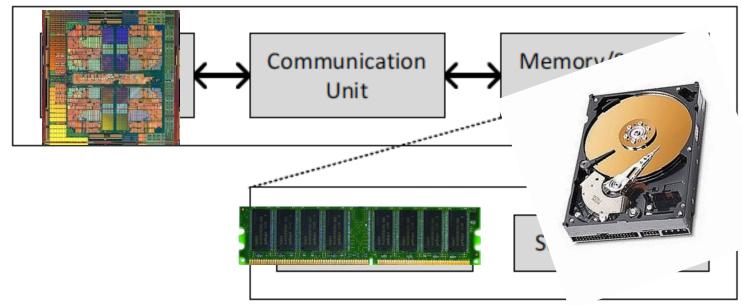

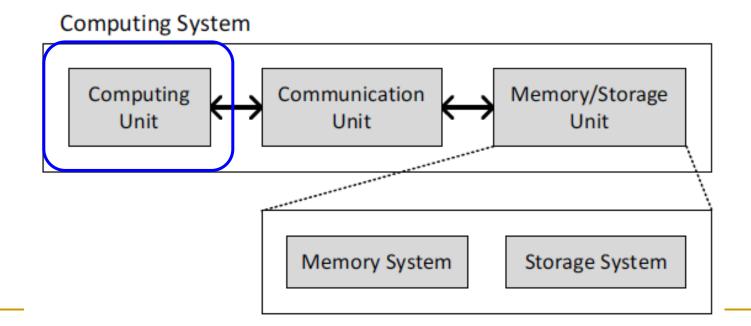

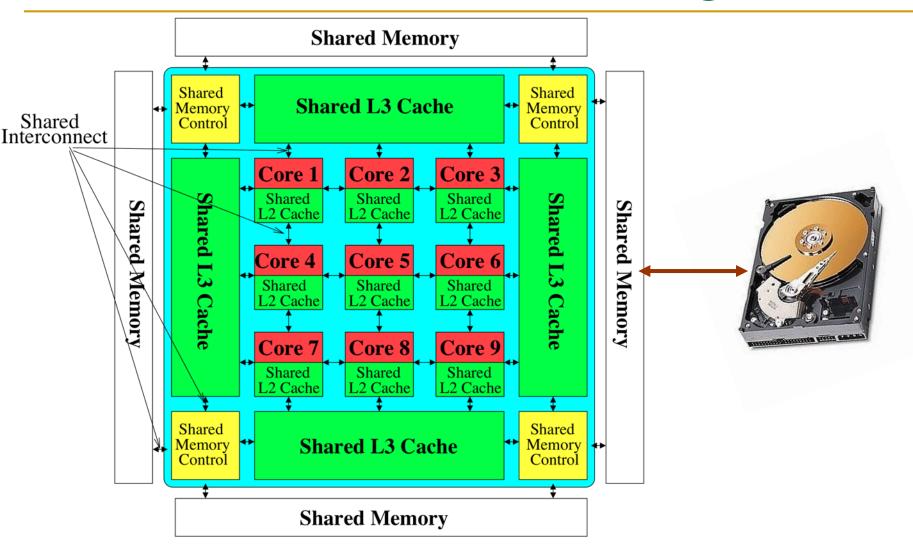

## A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### **Computing System**

Image source: https://lbsitbytes2010.wordpress.com/2013/03/29/john-von-neumann-roll-no-15/

## A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### **Computing System**

Image source: https://lbsitbytes2010.wordpress.com/2013/03/29/john-von-neumann-roll-no-15/

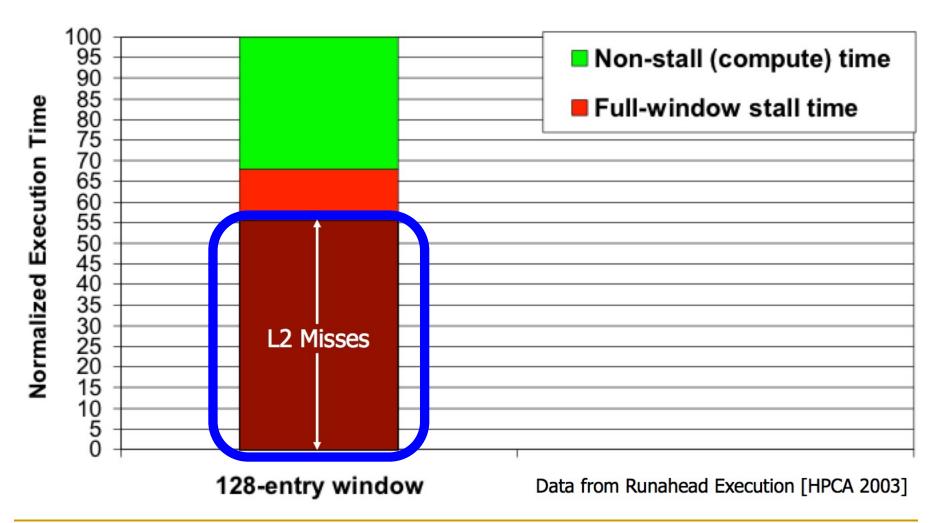

## Today's Computing Systems

- Are overwhelmingly processor centric

- All data processed in the processor  $\rightarrow$  at great system cost

- Processor is heavily optimized and is considered the master

- Data storage units are dumb and are largely unoptimized (except for some that are on the processor die)

I expect that over the coming decade memory subsystem design will be the *only* important design issue for microprocessors.

#### "It's the Memory, Stupid!" (Richard Sites, MPR, 1996)

Mutlu+, "Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-Order Processors," HPCA 2003.

## The Performance Perspective

Onur Mutlu, Jared Stark, Chris Wilkerson, and Yale N. Patt,

"Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors"

Proceedings of the <u>9th International Symposium on High-Performance Computer</u> <u>Architecture</u> (HPCA), pages 129-140, Anaheim, CA, February 2003. <u>Slides (pdf)</u>

One of the 15 computer arch. papers of 2003 selected as Top Picks by IEEE Micro. HPCA Test of Time Award (awarded in 2021).

#### **Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors**

Onur Mutlu § Jared Stark † Chris Wilkerson ‡ Yale N. Patt §

§ECE Department The University of Texas at Austin {onur,patt}@ece.utexas.edu †Microprocessor Research Intel Labs jared.w.stark@intel.com

‡Desktop Platforms Group Intel Corporation chris.wilkerson@intel.com

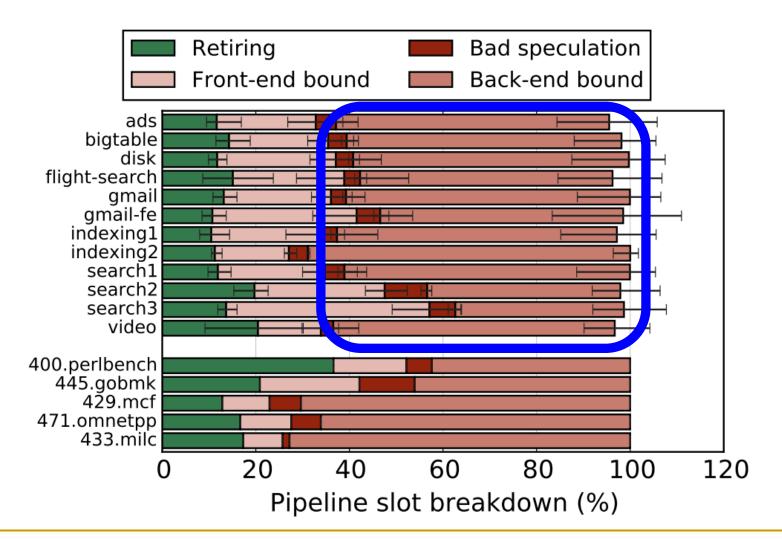

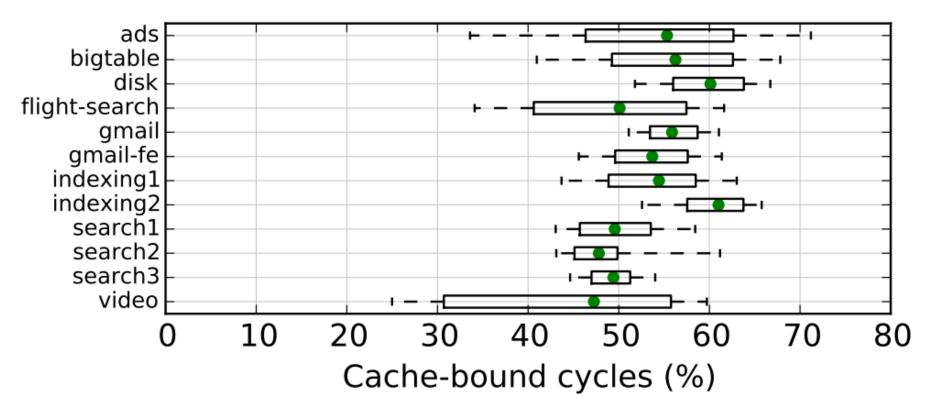

## The Performance Perspective (Today)

All of Google's Data Center Workloads (2015):

Kanev+, "Profiling a Warehouse-Scale Computer," ISCA 2015.

#### The Performance Perspective (Today)

All of Google's Data Center Workloads (2015):

#### Figure 11: Half of cycles are spent stalled on caches.

## Perils of Processor-Centric Design

#### Grossly-imbalanced systems

- Processing done only in **one place**

- Everything else just stores and moves data: data moves a lot

- $\rightarrow$  Energy inefficient

- $\rightarrow$  Low performance

- $\rightarrow$  Complex

- Overly complex and bloated processor (and accelerators)

- To tolerate data access from memory

- Complex hierarchies and mechanisms

- $\rightarrow$  Energy inefficient

- $\rightarrow$  Low performance

- $\rightarrow$  Complex

## Perils of Processor-Centric Design

#### Most of the system is dedicated to storing and moving data

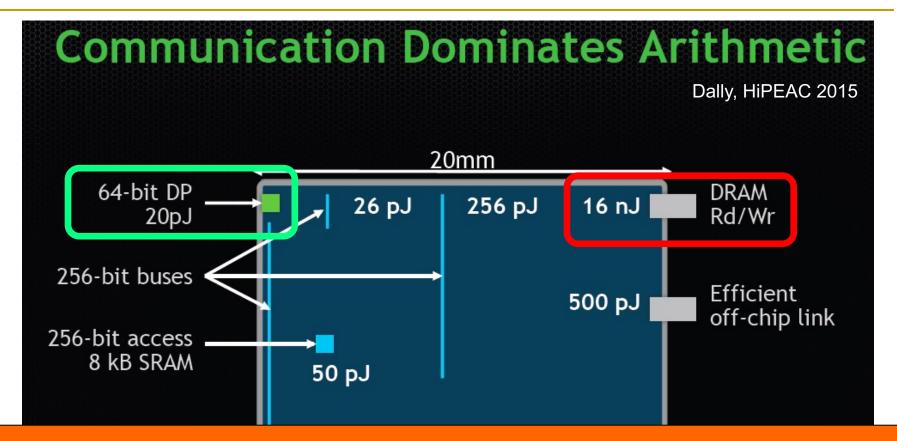

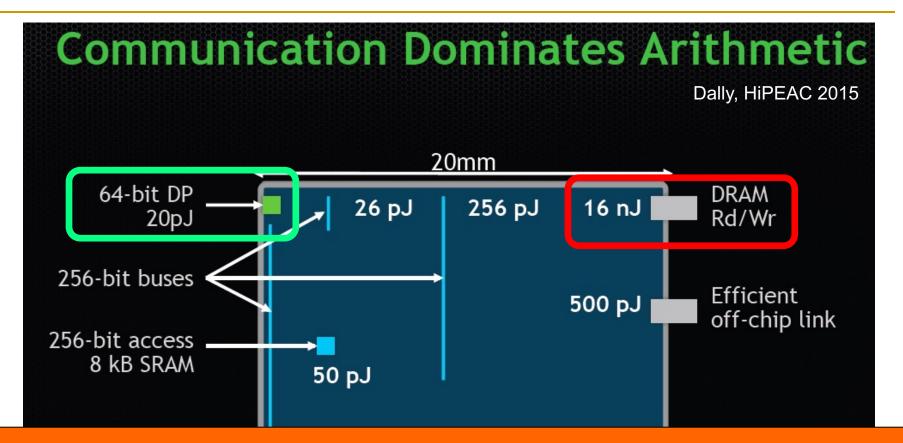

## Data Movement vs. Computation Energy

## A memory access consumes ~100-1000X the energy of a complex addition

#### Energy Waste in Mobile Devices

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the <u>23rd International Conference on Architectural Support for Programming</u> <u>Languages and Operating Systems</u> (ASPLOS), Williamsburg, VA, USA, March 2018.

# 62.7% of the total system energy is spent on data movement

#### Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup>Saugata Ghose<sup>1</sup>Youngsok Kim<sup>2</sup>Rachata Ausavarungnirun<sup>1</sup>Eric Shiu<sup>3</sup>Rahul Thakur<sup>3</sup>Daehyun Kim<sup>4,3</sup>Aki Kuusela<sup>3</sup>Allan Knies<sup>3</sup>Parthasarathy Ranganathan<sup>3</sup>Onur Mutlu<sup>5,1</sup>72

## We Do Not Want to Move Data!

## A memory access consumes ~100-1000X the energy of a complex addition

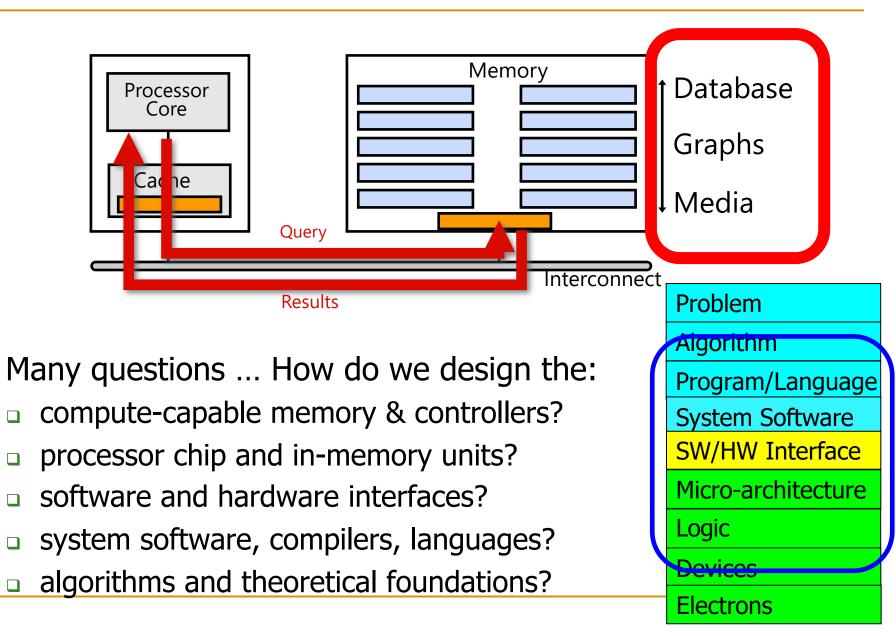

## We Need A Paradigm Shift To ...

Enable computation with minimal data movement

Compute where it makes sense (where data resides)

Make computing architectures more data-centric

## Goal: Processing Inside Memory

## Processing in Memory: Two Approaches

Processing using Memory

Processing near Memory

## Memory as an Active Accelerator

#### Memory similar to a "conventional" accelerator

## In-Memory Bulk Bitwise Operations

- We can support in-DRAM COPY, ZERO, AND, OR, NOT, MAJ

- At low cost

- Using analog computation capability of DRAM

- Idea: activating multiple rows performs computation

#### 30-74X performance and energy improvement

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology," MICRO 2017.

New memory technologies enable even more opportunities

## Ambit [MICRO'17]

Vivek Seshadri et al., "<u>Ambit: In-Memory Accelerator</u> for Bulk Bitwise Operations Using Commodity DRAM <u>Technology</u>," MICRO 2017.

#### Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology

Vivek Seshadri<sup>1,5</sup> Donghyuk Lee<sup>2,5</sup> Thomas Mullins<sup>3,5</sup> Hasan Hassan<sup>4</sup> Amirali Boroumand<sup>5</sup> Jeremie Kim<sup>4,5</sup> Michael A. Kozuch<sup>3</sup> Onur Mutlu<sup>4,5</sup> Phillip B. Gibbons<sup>5</sup> Todd C. Mowry<sup>5</sup>

<sup>1</sup>Microsoft Research India <sup>2</sup>NVIDIA Research <sup>3</sup>Intel <sup>4</sup>ETH Zürich <sup>5</sup>Carnegie Mellon University

## In-DRAM Bulk Bitwise Execution

Vivek Seshadri and Onur Mutlu,

"In-DRAM Bulk Bitwise Execution Engine" Invited Book Chapter in Advances in Computers, to appear in 2020.

[Preliminary arXiv version]

## In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu ETH Zürich onur.mutlu@inf.ethz.ch

## SIMDRAM Framework

Nastaran Hajinazar, Geraldo F. Oliveira, Sven Gregorio, Joao Dinis Ferreira, Nika Mansouri Ghiasi, Minesh Patel, Mohammed Alser, Saugata Ghose, Juan Gomez-Luna, and Onur Mutlu, "SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Computing in DRAM" Proceedings of the 26th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Virtual, March-April 2021.

[2-page Extended Abstract]

[Short Talk Slides (pptx) (pdf)]

[Talk Slides (pptx) (pdf)]

[Short Talk Video (5 mins)]

[Full Talk Video (27 mins)]

#### SIMDRAM: A Framework for Bit-Serial SIMD Processing using DRAM

\*Nastaran Hajinazar<sup>1,2</sup> Nika Mansouri Ghiasi<sup>1</sup> Juan Gómez-Luna<sup>1</sup> Sven Gregorio<sup>1</sup> Mohammed Alser<sup>1</sup> Onur Mutlu<sup>1</sup> João Dinis Ferreira<sup>1</sup> Saugata Ghose<sup>3</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>Simon Fraser University

<sup>3</sup>University of Illinois at Urbana–Champaign

## In-DRAM Physical Unclonable Functions

Jeremie S. Kim, Minesh Patel, Hasan Hassan, and Onur Mutlu, "The DRAM Latency PUF: Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern DRAM <u>Devices"</u> Proceedings of the <u>24th International Symposium on High-Performance Computer</u> <u>Architecture</u> (HPCA), Vienna, Austria, February 2018.

[Lightning Talk Video]

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

[Full Talk Lecture Video (28 minutes)]

#### The DRAM Latency PUF:

Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern Commodity DRAM Devices

> Jeremie S. Kim<sup>†§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§†</sup> <sup>†</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

## In-DRAM True Random Number Generation

Jeremie S. Kim, Minesh Patel, Hasan Hassan, Lois Orosa, and Onur Mutlu, "D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput" Proceedings of the <u>25th International Symposium on High-Performance Computer</u> Architecture (HPCA), Washington, DC, USA, February 2019. [Slides (pptx) (pdf)] [Full Talk Video (21 minutes)] [Full Talk Lecture Video (27 minutes)] Top Picks Honorable Mention by IEEE Micro.

### D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

Jeremie S. Kim<sup>‡§</sup>

Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§‡</sup> <sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

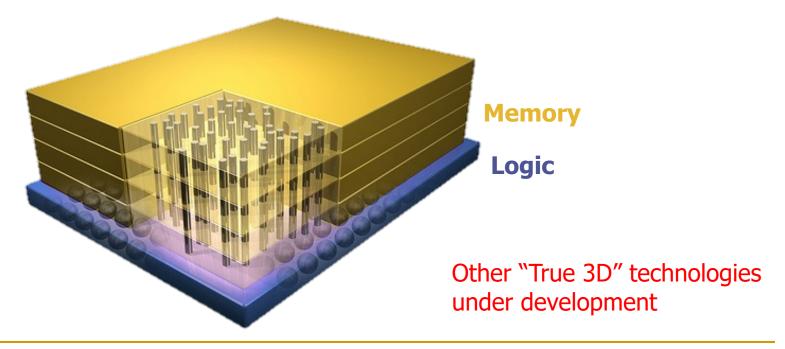

## Opportunity: 3D-Stacked Logic+Memory

# Hybrid Memory Cube

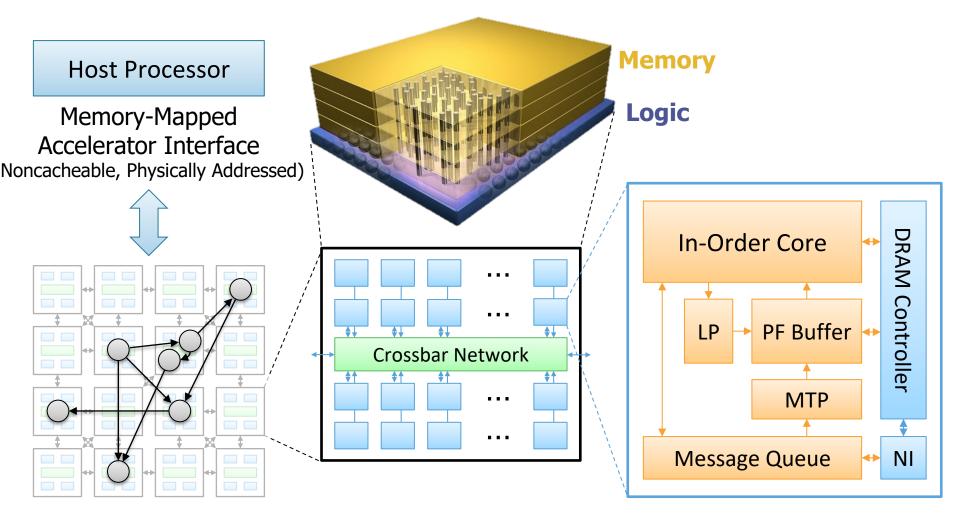

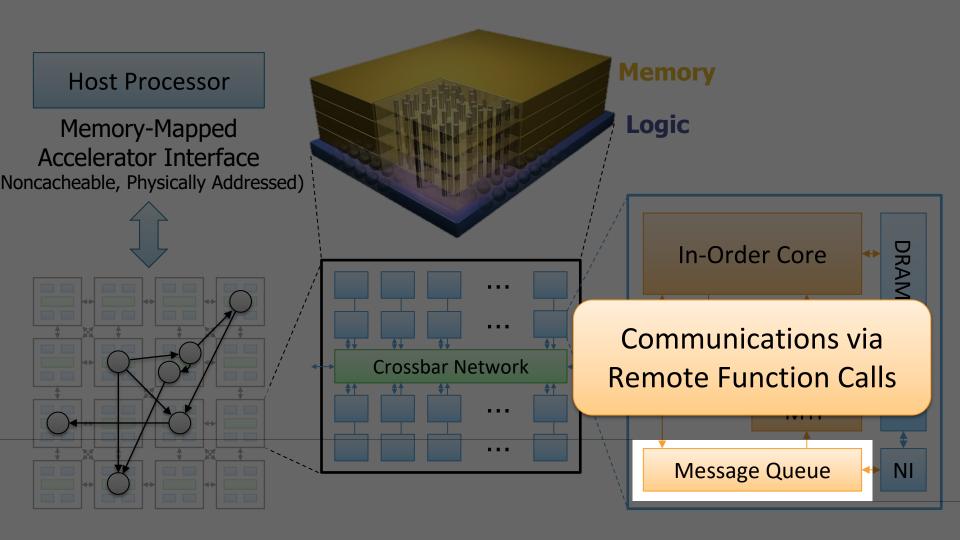

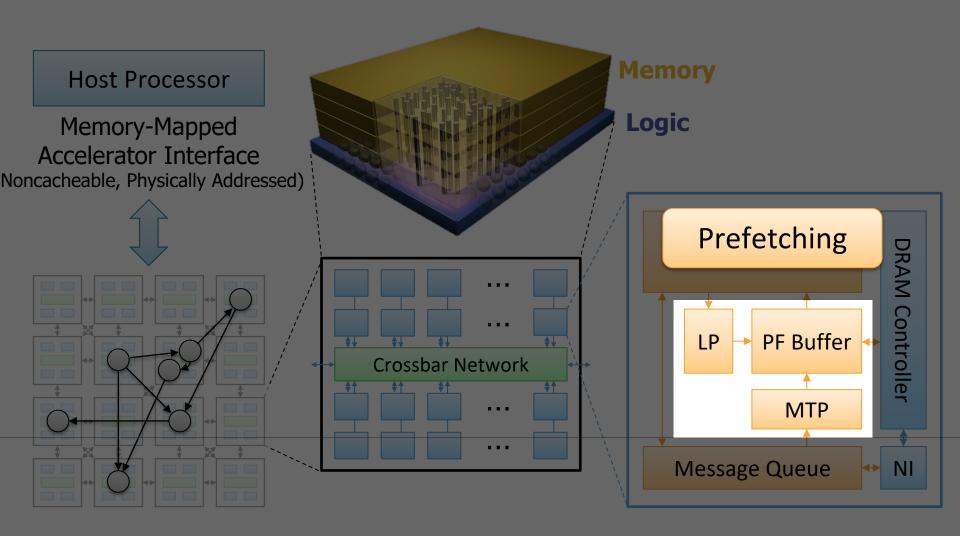

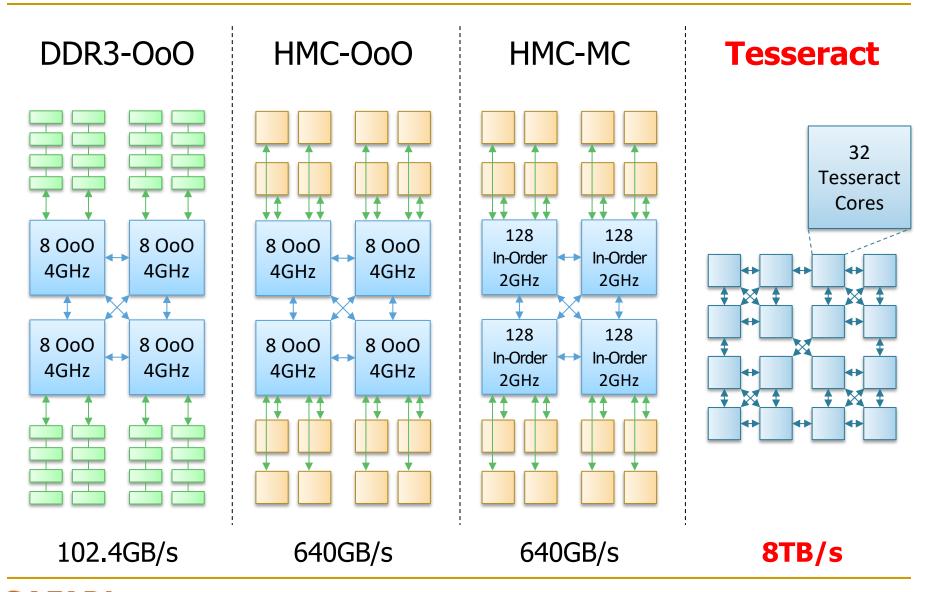

## Tesseract System for Graph Processing

Interconnected set of 3D-stacked memory+logic chips with simple cores

**SAFARI** Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing" ISCA 2015.

## Tesseract System for Graph Processing

## Tesseract System for Graph Processing

## **Evaluated Systems**

**SAFARI** Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing" ISCA 2015.

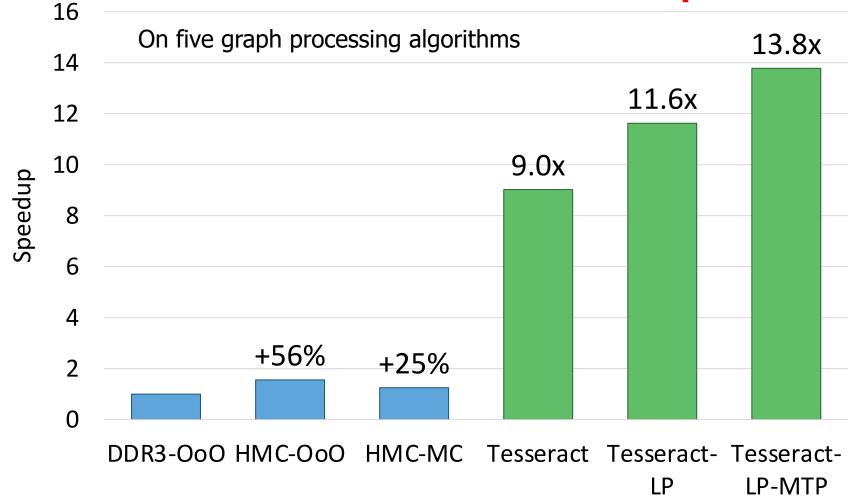

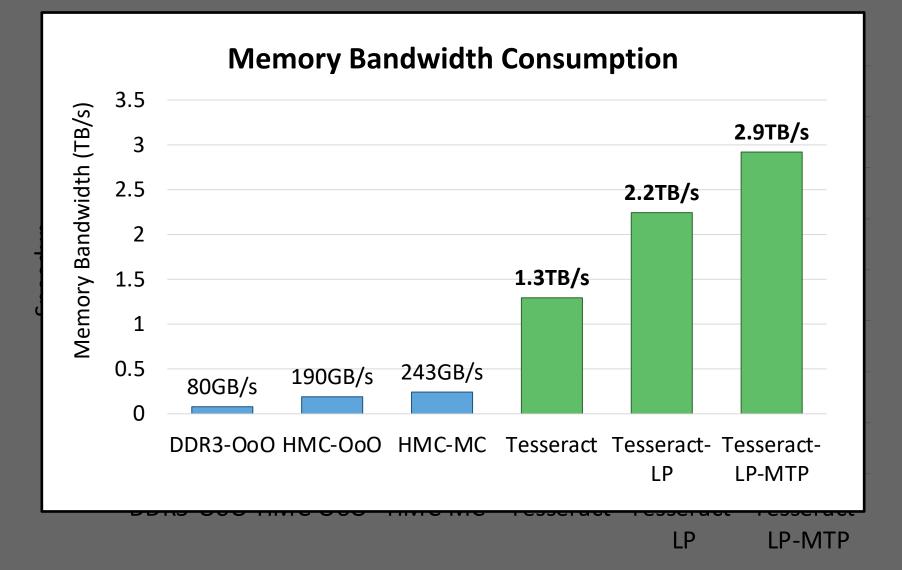

## Tesseract Graph Processing Performance

#### >13X Performance Improvement

**SAFARI** Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing" ISCA 2015.

## Tesseract Graph Processing Performance

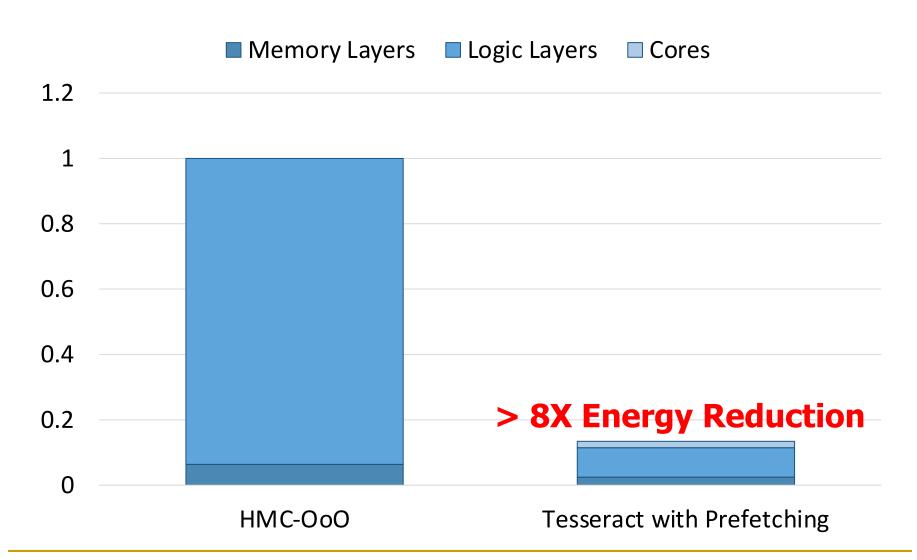

## Tesseract Graph Processing System Energy

**SAFARI** Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing" ISCA 2015.

## More on Tesseract

Junwhan Ahn, Sungpack Hong, Sungjoo Yoo, Onur Mutlu, and Kiyoung Choi,

"A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing"

Proceedings of the <u>42nd International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2015.

[Slides (pdf)] [Lightning Session Slides (pdf)]

#### A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing

Junwhan Ahn Sungpack Hong<sup>§</sup> Sungjoo Yoo Onur Mutlu<sup>†</sup> Kiyoung Choi junwhan@snu.ac.kr, sungpack.hong@oracle.com, sungjoo.yoo@gmail.com, onur@cmu.edu, kchoi@snu.ac.kr Seoul National University <sup>§</sup>Oracle Labs <sup>†</sup>Carnegie Mellon University

## Eliminating the Adoption Barriers

# How to Enable Adoption of Processing in Memory

## Barriers to Adoption of PIM

1. Functionality of and applications & software for PIM

- 2. Ease of programming (interfaces and compiler/HW support)

- 3. System support: coherence & virtual memory

4. Runtime and compilation systems for adaptive scheduling, data mapping, access/sharing control

5. Infrastructures to assess benefits and feasibility

#### All can be solved with change of mindset

## We Need to Revisit the Entire Stack

|  | Problem            | , |

|--|--------------------|---|

|  | Aigorithm          |   |

|  | Program/Language   |   |

|  | System Software    |   |

|  | SW/HW Interface    |   |

|  | Micro-architecture |   |

|  | Logic              |   |

|  | Devices            |   |

|  | Electrons          |   |

#### We can get there step by step

Challenge and Opportunity for Future

# Computing Architectures with

## Minimal Data Movement

Challenge and Opportunity for Future

Fundamentally **Energy-Efficient** (Data-Centric) **Computing Architectures**  Challenge and Opportunity for Future

Fundamentally **High-Performance** (Data-Centric) **Computing Architectures**

## PIM Review and Open Problems

## A Modern Primer on Processing in Memory

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b,c</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>d</sup>

SAFARI Research Group

<sup>a</sup>ETH Zürich <sup>b</sup>Carnegie Mellon University <sup>c</sup>University of Illinois at Urbana-Champaign <sup>d</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "A Modern Primer on Processing in Memory" *Invited Book Chapter in <u>Emerging Computing: From Devices to Systems -</u> <i>Looking Beyond Moore and Von Neumann*, Springer, to be published in 2021.

## PIM Review and Open Problems (II)

#### A Workload and Programming Ease Driven Perspective of Processing-in-Memory

Saugata Ghose†Amirali Boroumand†Jeremie S. Kim†§Juan Gómez-Luna§Onur Mutlu§††Carnegie Mellon University§ETH Zürich

Saugata Ghose, Amirali Boroumand, Jeremie S. Kim, Juan Gomez-Luna, and Onur Mutlu, "Processing-in-Memory: A Workload-Driven Perspective" *Invited Article in <u>IBM Journal of Research & Development</u>, Special Issue on Hardware for Artificial Intelligence*, to appear in November 2019. [Preliminary arXiv version]

#### SAFARI

https://arxiv.org/pdf/1907.12947.pdf

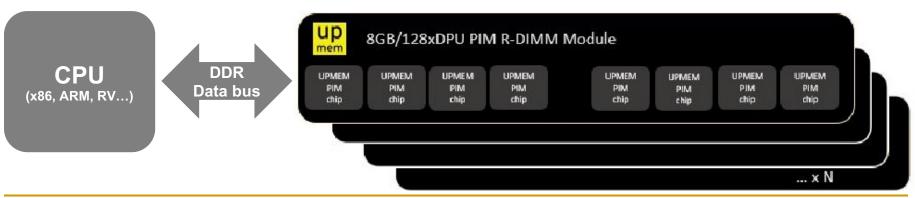

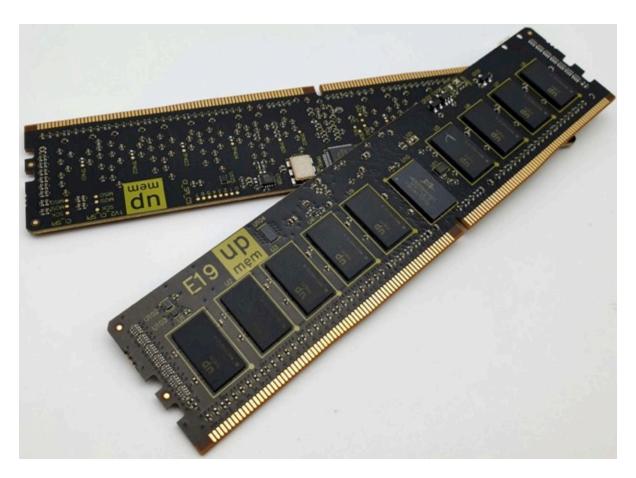

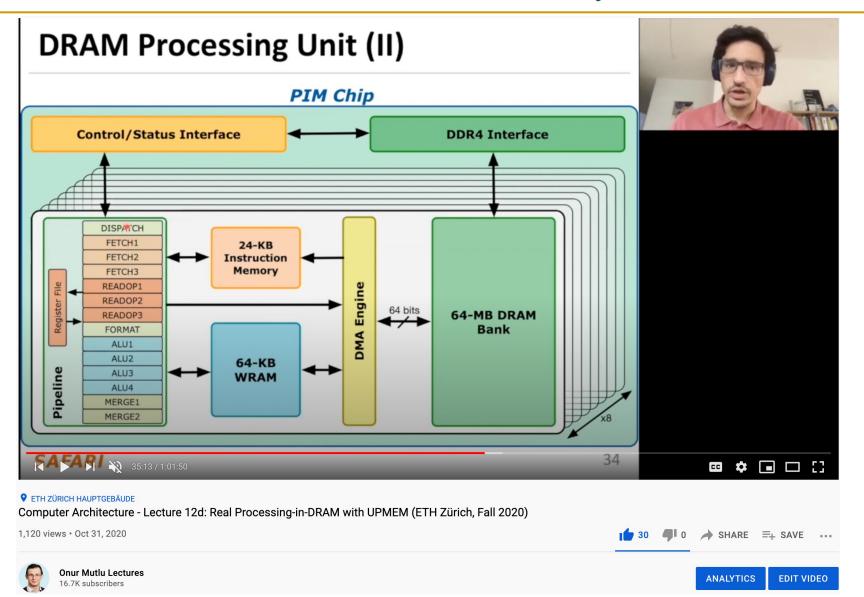

## UPMEM Processing-in-DRAM Engine (2019)

#### Processing in DRAM Engine

Includes standard DIMM modules, with a large number of DPU processors combined with DRAM chips.

#### Replaces standard DIMMs

- DDR4 R-DIMM modules

- 8GB+128 DPUs (16 PIM chips)

- Standard 2x-nm DRAM process

Large amounts of compute & memory bandwidth

https://www.anandtech.com/show/14750/hot-chips-31-analysis-inmemory-processing-by-upmem https://www.upmem.com/video-upmem-presenting-its-true-processing-in-memory-solution-hot-chips-2019/

## **UPMEM Memory Modules**

- E19: 8 chips DIMM (1 rank). DPUs @ 267 MHz

- P21: 16 chips DIMM (2 ranks). DPUs @ 350 MHz

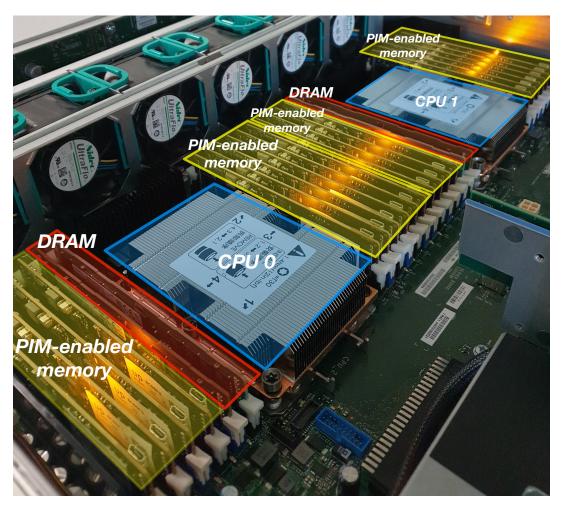

## **PIM System Organization**

• UPMEM-based PIM system with 20 UPMEM memory modules of 16 chips each (40 ranks) → 2560 DPUs

## More on the UPMEM PIM System

https://www.youtube.com/watch?v=Sscy1Wrr22A&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN&index=26

#### Experimental Analysis of the UPMEM PIM Engine

### Benchmarking a New Paradigm: An Experimental Analysis of a Real Processing-in-Memory Architecture

JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland IZZAT EL HAJJ, American University of Beirut, Lebanon IVAN FERNANDEZ, ETH Zürich, Switzerland and University of Malaga, Spain CHRISTINA GIANNOULA, ETH Zürich, Switzerland and NTUA, Greece GERALDO F. OLIVEIRA, ETH Zürich, Switzerland ONUR MUTLU, ETH Zürich, Switzerland

Many modern workloads, such as neural networks, databases, and graph processing, are fundamentally memory-bound. For such workloads, the data movement between main memory and CPU cores imposes a significant overhead in terms of both latency and energy. A major reason is that this communication happens through a narrow bus with high latency and limited bandwidth, and the low data reuse in memory-bound workloads is insufficient to amortize the cost of main memory access. Fundamentally addressing this *data movement bottleneck* requires a paradigm where the memory system assumes an active role in computing by integrating processing capabilities. This paradigm is known as *processing-in-memory (PIM*).

Recent research explores different forms of PIM architectures, motivated by the emergence of new 3Dstacked memory technologies that integrate memory with a logic layer where processing elements can be easily placed. Past works evaluate these architectures in simulation or, at best, with simplified hardware prototypes. In contrast, the UPMEM company has designed and manufactured the first publicly-available real-world PIM architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called *DRAM Processing Units* (*DPUs*), integrated in the same chip.

This paper provides the first comprehensive analysis of the first publicly-available real-world PIM architecture. We make two key contributions. First, we conduct an experimental characterization of the UPMEM-based PIM system using microbenchmarks to assess various architecture limits such as compute throughput and memory bandwidth, yielding new insights. Second, we present *PrIM* (*Processing-In-Memory benchmarks*), a benchmark suite of 16 workloads from different application domains (e.g., dense/sparse linear algebra, databases, data analytics, graph processing, neural networks, bioinformatics, image processing), which we identify as memory-bound. We evaluate the performance and scaling characteristics of PrIM benchmarks on the UPMEM PIM architecture, and compare their performance and energy consumption to their stateof-the-art CPU and GPU counterparts. Our extensive evaluation conducted on two real UPMEM-based PIM systems with 640 and 2,556 DPUs provides new insights about suitability of different workloads to the PIM system, programming recommendations for software designers, and suggestions and hints for hardware and architecture designers of future PIM systems.

#### https://arxiv.org/pdf/2105.03814.pdf

#### DAMOV Methodology & Workloads

#### DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

GERALDO F. OLIVEIRA, ETH Zürich, Switzerland JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland LOIS OROSA, ETH Zürich, Switzerland SAUGATA GHOSE, University of Illinois at Urbana–Champaign, USA NANDITA VIJAYKUMAR, University of Toronto, Canada IVAN FERNANDEZ, University of Malaga, Spain & ETH Zürich, Switzerland MOHAMMAD SADROSADATI, Institute for Research in Fundamental Sciences (IPM), Iran & ETH Zürich, Switzerland ONUR MUTLU, ETH Zürich, Switzerland

Data movement between the CPU and main memory is a first-order obstacle against improving performance, scalability, and energy efficiency in modern systems. Computer systems employ a range of techniques to reduce overheads tied to data movement, spanning from traditional mechanisms (e.g., deep multi-level cache hierarchies, aggressive hardware prefetchers) to emerging techniques such as Near-Data Processing (NDP), where some computation is moved close to memory. Prior NDP works investigate the root causes of data movement bottlenecks using different profiling methodologies and tools. However, there is still a lack of understanding about the key metrics that can identify different data movement bottlenecks and their relation to traditional and emerging data movement mitigation mechanisms. Our goal is to memory-centric data movement mitigation techniques (e.g., caching and prefetching) to more memory-centric techniques (e.g., NDP), thereby developing a rigorous understanding of the best techniques to mitigate each source of data movement.

With this goal in mind, we perform the first large-scale characterization of a wide variety of applications, across a wide range of application domains, to identify fundamental program properties that lead to data movement to/from main memory. We develop the first systematic methodology to classify applications based on the sources contributing to data movement bottlenecks. From our large-scale characterization of 77K functions across 345 applications, we select 144 functions to form the first open-source benchmark suite (DAMOV) for main memory data movement studies. We select a diverse range of functions that (1) represent different types of data movement bottlenecks, and (2) come from a wide range of application domains. Using NDP as a case study, we identify new insights about the different data movement bottlenecks and use these insights to determine the most suitable data movement mitigation mechanism for a particular application. We open-source DAMOV and the complete source code for our new characterization methodology at https://github.com/CMU-SAFARI/DAMOV.

#### SAFARI

#### https://arxiv.org/pdf/2105.03725.pdf

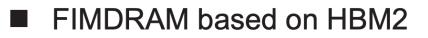

## Samsung Function-in-Memory DRAM (2021)

Samsung Newsroom

CORPORATE | PRODUCTS | PRESS RESOURCES | VIEWS | ABOUT US

Audio

Share ( 🔊

#### Samsung Develops Industry's First High Bandwidth Memory with AI Processing Power

Korea on February 17, 2021

#### The new architecture will deliver over twice the system performance and reduce energy consumption by more than 70%

Samsung Electronics, the world leader in advanced memory technology, today announced that it has developed the industry's first High Bandwidth Memory (HBM) integrated with artificial intelligence (AI) processing power – the HBM-PIM The new processing-in-memory (PIM) architecture brings powerful AI computing capabilities inside high-performance memory, to accelerate large-scale processing in data centers, high performance computing (HPC) systems and AI-enabled mobile applications.

Kwangil Park, senior vice president of Memory Product Planning at Samsung Electronics stated, "Our groundbreaking HBM-PIM is the industry's first programmable PIM solution tailored for diverse AI-driven workloads such as HPC, training and inference. We plan to build upon this breakthrough by further collaborating with AI solution providers for even more advanced PIM-powered applications."

## Samsung Function-in-Memory DRAM (2021)

#### [3D Chip Structure of HBM with FIMDRAM]

ISSCC 2021 / SESSION 25 / DRAM / 25.4

25.4 A 20nm 6GB Function-In-Memory DRAM, Based on HBM2 with a 1.2TFLOPS Programmable Computing Unit Using Bank-Level Parallelism, for Machine Learning Applications

Young-Cheon Kwon', Suk Han Lee', Jaehoon Lee', Sang-Hyuk Kwon', Je Min Ryu', Jong-Pil Son', Seongil O', Hak-Soo Yu', Haesuk Lee', Soo Young Kim', Youngmin Cho', Jin Guk Kim', Jongyoon Cho'i, Hyun-Sung Shin', Jin Kim', BengSeng Phuah', HyoungMin Kim', Myeong Jun Song', Ahn Choi', Daeho Kim', SooYoung Kim', Eun-Bong Kim', David Wang', Shinhaeng Kang', Yuhwan Ro<sup>3</sup>, Seungwoo Seo<sup>3</sup>, JoonHo Song<sup>3</sup>, Jaeyoun Youn', Kyomin Sohn', Nam Sung Kim'

<sup>1</sup>Samsung Electronics, Hwaseong, Korea <sup>2</sup>Samsung Electronics, San Jose, CA <sup>3</sup>Samsung Electronics, Suwon, Korea

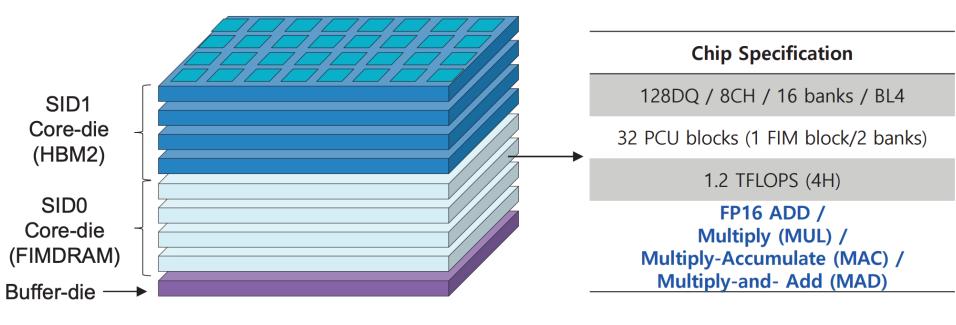

### Samsung Function-in-Memory DRAM (2021)

### **Chip Implementation**

- Mixed design methodology to implement FIMDRAM

- Full-custom + Digital RTL

[Digital RTL design for PCU block]

#### ISSCC 2021 / SESSION 25 / DRAM / 25.4

25.4 A 20nm 6GB Function-In-Memory DRAM, Based on HBM2 with a 1.2TFLOPS Programmable Computing Unit Using Bank-Level Parallelism, for Machine Learning Applications

Young-Cheon Kwon', Suk Han Lee', Jaehoon Lee', Sang-Hyuk Kwon', Je Min Ryu', Jong-Pil Son', Seongil O', Hak-Soo Yu', Haesuk Lee', Soo Young Kim', Youngmin Lho', Jin Guk Kim', Jongyoon Chol', Hyun-Sung Shin', Jin Kim', BengSeng Phuah', HyoungMin Kim', Myeong Jun Soong', Ann Chol', Daeho Kim', Sooryoung Kim', Euro-Bong Kim', David Wang', Shinhaeng Kang', Yuhwan Ro', Seungwoo Seo', JoonHo Song', Jaeyoun Youn', Koyonin Sohn', Nam Sung Kim'

<sup>1</sup>Samsung Electronics, Hwaseong, Korea <sup>2</sup>Samsung Electronics, San Jose, CA <sup>3</sup>Samsung Electronics, Suwon, Korea

| Cell array<br>for bank0                             | Cell array<br>for bank4                              | Cell array<br>for bank0                             | Cell array<br>for bank4                              | Pseudo       | Pseudo    |

|-----------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|--------------|-----------|

| PCU block<br>for bank0 & 1                          | PCU block<br>for bank4 & 5                           | PCU block<br>for bank0 & 1                          | PCU block<br>for bank4 & 5                           | channel-0    | channel-1 |

| Cell array<br>for bank1<br>Cell array<br>for bank2  | Cell array<br>for bank5<br>Cell array<br>for bank6   | Cell array<br>for bank1<br>Cell array<br>for bank2  | Cell array<br>for bank5<br>Cell array<br>for bank6   |              |           |

| PCU block<br>for bank2 & 3                          | PCU block<br>for bank6 & 7                           | PCU block<br>for bank2 & 3                          | PCU block<br>for bank6 & 7                           |              |           |

| Cell array<br>for bank3                             | Cell array<br>for bank7                              | Cell array<br>for bank3                             | Cell array<br>for bank7                              |              |           |

|                                                     |                                                      |                                                     |                                                      |              |           |

|                                                     |                                                      | TSV &                                               | Peri C                                               | ontrol Block |           |

| Cell array<br>for bank11                            | Cell array<br>for bank15                             | Cell array<br>for bank11                            | Cell array<br>for bank15                             |              |           |

| PCU block<br>for bank10 & 1                         | PCU block<br>1 for bank14 & 15                       | PCU block<br>for bank10 & 11                        | PCU block<br>for bank14 & 15                         |              |           |

| Cell array<br>for bank10<br>Cell array<br>for bank9 | Cell array<br>for bank14<br>Cell array<br>for bank13 | Cell array<br>for bank10<br>Cell array<br>for bank9 | Cell array<br>for bank14<br>Cell array<br>for bank13 |              |           |

| PCU block<br>for bank8 & 9                          | PCU block<br>for bank12 & 13                         | PCU block<br>for bank8 & 9                          | PCU block<br>for bank12 & 13                         | Pseudo       | Pseudo    |

| Cell array<br>for bank8                             | Cell array<br>for bank12                             | Cell array<br>for bank8                             | Cell array<br>for bank12                             | channel-0    | channel-1 |

### Detailed Lectures on PIM (I)

- Computer Architecture, Fall 2020, Lecture 6

- **Computation in Memory** (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=oGcZAGwfEUE&list=PL5Q2soXY2Zi9xidyIgBxUz 7xRPS-wisBN&index=12

- Computer Architecture, Fall 2020, Lecture 7

- **Near-Data Processing** (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=j2GIigqn1Qw&list=PL5Q2soXY2Zi9xidyIgBxUz7 xRPS-wisBN&index=13

- Computer Architecture, Fall 2020, Lecture 11a

- Memory Controllers (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=TeG773OgiMQ&list=PL5Q2soXY2Zi9xidyIgBxUz 7xRPS-wisBN&index=20

- Computer Architecture, Fall 2020, Lecture 12d

- Real Processing-in-DRAM with UPMEM (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=Sscy1Wrr22A&list=PL5Q2soXY2Zi9xidyIgBxUz7 xRPS-wisBN&index=25

SAFARI

### Detailed Lectures on PIM (II)

- Computer Architecture, Fall 2020, Lecture 15

- **Emerging Memory Technologies** (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=AlE1rD9G\_YU&list=PL5Q2soXY2Zi9xidyIgBxUz 7xRPS-wisBN&index=28

- Computer Architecture, Fall 2020, Lecture 16a

- Opportunities & Challenges of Emerging Memory Technologies (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=pmLszWGmMGQ&list=PL5Q2soXY2Zi9xidyIgBx Uz7xRPS-wisBN&index=29

- Computer Architecture, Fall 2020, Guest Lecture

- In-Memory Computing: Memory Devices & Applications (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=wNmqQHiEZNk&list=PL5Q2soXY2Zi9xidyIgBxU z7xRPS-wisBN&index=41

SAFARI

### A Tutorial on Processing in Memory

Onur Mutlu, <u>"Memory-Centric Computing Systems"</u> Invited Tutorial at 66th International Electron Devices *Meeting (IEDM)*, Virtual, 12 December 2020. [Slides (pptx) (pdf)] [Executive Summary Slides (pptx) (pdf)] [Tutorial Video (1 hour 51 minutes)] [Executive Summary Video (2 minutes)] Abstract and Bio [Related Keynote Paper from VLSI-DAT 2020] [Related Review Paper on Processing in Memory]

https://www.youtube.com/watch?v=H3sEaINPBOE

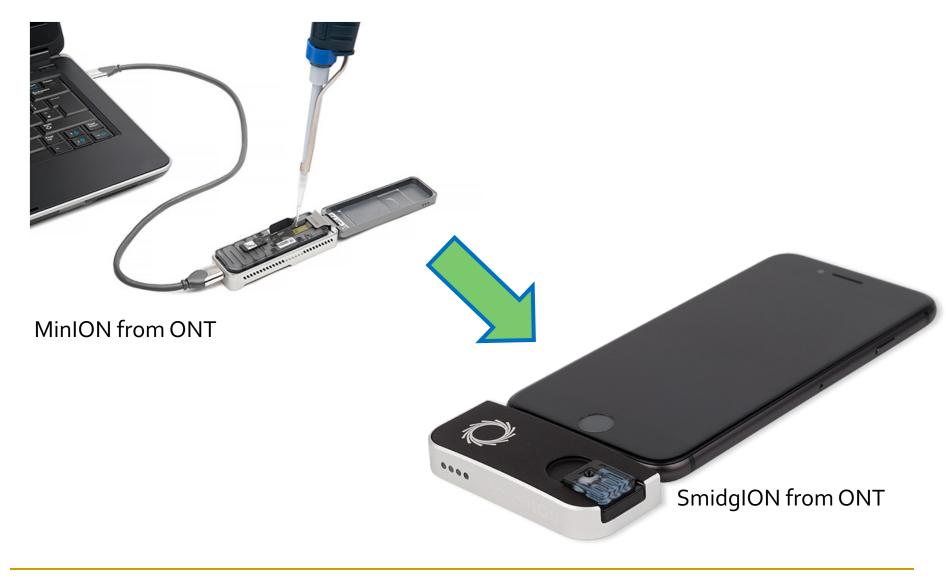

### PIM Can Enable New Medical Platforms

#### Nanopore sequencing technology and tools for genome assembly: computational analysis of the current state, bottlenecks and future directions

Damla Senol Cali 🖾, Jeremie S Kim, Saugata Ghose, Can Alkan, Onur Mutlu

Briefings in Bioinformatics, bby017, https://doi.org/10.1093/bib/bby017 Published: 02 April 2018 Article history ▼

Oxford Nanopore MinION

Senol Cali+, "Nanopore Sequencing Technology and Tools for Genome Assembly: Computational Analysis of the Current State, Bottlenecks and Future Directions," Briefings in Bioinformatics, 2018. [Preliminary arxiv.org version]

#### SAFARI

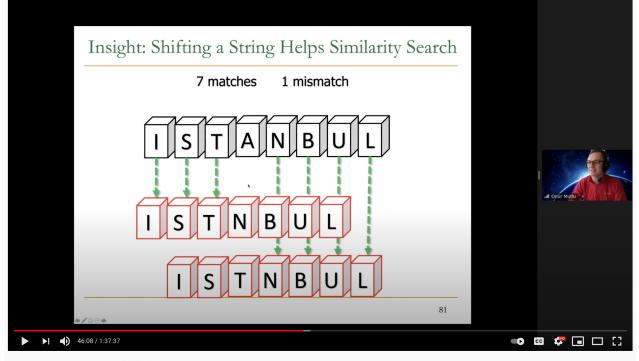

### Future of Genome Sequencing & Analysis

#### SAFARI

### Accelerating Genome Analysis: Overview

Mohammed Alser, Zulal Bingol, Damla Senol Cali, Jeremie Kim, Saugata Ghose, Can Alkan, and Onur Mutlu,

"Accelerating Genome Analysis: A Primer on an Ongoing Journey" IEEE Micro (IEEE MICRO), Vol. 40, No. 5, pages 65-75, September/October 2020.

[Slides (pptx)(pdf)]

[Talk Video (1 hour 2 minutes)]

### Accelerating Genome Analysis: A Primer on an Ongoing Journey

Mohammed Alser ETH Zürich

Zülal Bingöl Bilkent University

Damla Senol Cali Carnegie Mellon University

Jeremie Kim ETH Zurich and Carnegie Mellon University Saugata Ghose University of Illinois at Urbana–Champaign and Carnegie Mellon University

Can Alkan Bilkent University

**Onur Mutlu** ETH Zurich, Carnegie Mellon University, and Bilkent University

#### More on Fast Genome Analysis ...

```

Onur Mutlu,

<u>"Accelerating Genome Analysis: A Primer on an Ongoing Journey"</u>

Invited Lecture at <u>Technion</u>, Virtual, 26 January 2021.

[<u>Slides (pptx) (pdf)</u>]

[<u>Talk Video (1 hour 37 minutes, including Q&A)</u>]

[Polated Invited Paper (at IEEE Micro. 2020)]

```

[Related Invited Paper (at IEEE Micro, 2020)]

Onur Mutlu - Invited Lecture @Technion: Accelerating Genome Analysis: A Primer on an Ongoing Journey

566 views · Premiered Feb 6, 2021

### Detailed Lectures on Genome Analysis

- Computer Architecture, Fall 2020, Lecture 3a

- Introduction to Genome Sequence Analysis (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=CrRb32v7SJc&list=PL5Q2soXY2Zi9xidyIgBxUz7 xRPS-wisBN&index=5

- Computer Architecture, Fall 2020, Lecture 8

- **Intelligent Genome Analysis** (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=ygmQpdDTL7o&list=PL5Q2soXY2Zi9xidyIgBxU z7xRPS-wisBN&index=14

- Computer Architecture, Fall 2020, Lecture 9a

SAFARI

- **GenASM: Approx. String Matching Accelerator** (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=XoLpzmN-Pas&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN&index=15

- Accelerating Genomics Project Course, Fall 2020, Lecture 1

- Accelerating Genomics (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=rgjl8ZyLsAg&list=PL5Q2soXY2Zi9E2bBVAgCqL gwiDRQDTyId

### If You Want More of This...

### Multiple Future Options

- Take the Bachelor's Seminar in Computer Architecture

- Offered every Fall and Spring

- <u>https://safari.ethz.ch/architecture\_seminar</u>

- Take the Master's-level Computer Architecture course

- Offered every Fall

- <u>https://safari.ethz.ch/architecture</u>

- Take our P&S Courses in Computer Architecture

- Offered every Fall and Spring

- <u>https://safari.ethz.ch/projects\_and\_seminars</u>

#### Do research with me and my SAFARI research group

- Bachelor's/Master's theses, semester projects, internships

- Opportunity to be a part of a vibrant, cutting-edge group

- <u>https://safari.ethz.ch/</u>

#### SAFARI Research Group

# SAFARI Research Group safari.ethz.ch

https://safari.ethz.ch

#### Onur Mutlu's SAFARI Research Group

#### Computer architecture, HW/SW, systems, bioinformatics, security, memory

https://safari.ethz.ch/safari-newsletter-january-2021/

### SAFARI Newsletter April 2020 Edition

#### <u>https://safari.ethz.ch/safari-newsletter-april-2020/</u>

View in your browser

Think Big, Aim High

Dear SAFARI friends,

### SAFARI Newsletter January 2021 Edition

#### <u>https://safari.ethz.ch/safari-newsletter-january-2021/</u>

in 🖸 🖌 f

Think Big, Aim High, and Have a Wonderful 2021! Newsletter January 2021

Dear SAFARI friends,

Happy New Year! We are excited to share our group highlights with you in this second edition of the SAFARI newsletter (You can find the first edition from April 2020 here). 2020 has

#### Bachelor's Seminar in Computer Architecture

- Fall 2021

- 2 credit units

- Rigorous seminar on fundamental and cutting-edge topics in computer architecture

- Critical presentation, review, and discussion of major works in computer architecture

- We will cover many ideas & issues, analyze their tradeoffs, perform critical thinking, discussion and brainstorming

- Participation, presentation, synthesis report

- You can register for the course online

- <u>https://safari.ethz.ch/architecture\_seminar</u>

#### Computer Architecture Course

- Fall 2021

- 8 credit units

#### Labs

Lab 1: Caching (Due: Friday, October 9 at midnight)

Image: Handout

Image: Code (Zip)

Moodle Submission Page

Lab 2: Memory Hierarchy (Due: Sun. 25.10)

- Handout

- Code (Zip)

- Submission

Lab 3: Memory Scheduling (Due: Tue. 17.11)

- Handout

- Code (Zip)

- Submission

Lab 4: Prefetching (Due: Mon. 21.12)

Image: Image:

Lab 5: Multicore and Cache Coherence (BONUS) (Due: Fri. 29.1)

- Image: Image and the second sec

- Covers many cutting-edge topics in memory systems, interconnects, multiprocessors, heterogeneous systems, PIM, and more...

Many topics we could not cover in this course

- Exam, lab assignments, homeworks

- You can register for the course online

- https://safari.ethz.ch/architecture/fall2020/doku.php?id=schedule

### Projects & Seminars (P&S) Courses

Fall 2021

#### P&S Courses in Computer Architecture

- Offered every Fall and Spring

- Short lectures + Hands-on project

- Lightweight but deep courses on specific topics you can choose from

- Memory

- Understanding and Improving Modern DRAM Performance, Reliability, and Security with Hands-On Experiments

- Designing and Evaluating Memory Systems and Modern Software Workloads with Ramulator

- Storage

- Understanding and Designing Modern NAND Flash-Based Solid-State Drives (SSDs) by Building a Practical SSD Simulator

- Heterogenous Computing: GPU, FPGA, PIM

- Hands-on Acceleration on Heterogeneous Computing Systems

- Exploring the **Processing-in-Memory** Paradigm for Future Computing Systems

- Applications: Bioinformatics & Machine Learning

- Accelerating Genome Analysis with FPGAs, GPUs, and New Execution Paradigms

- Genome Sequencing on Mobile Devices

- <u>https://safari.ethz.ch/projects\_and\_seminars</u>

### Doing Research with Us

- If you are interested in learning more and doing research in Computer Architecture, three suggestions:

- Email me with your interest (CC: Juan)

- □ Take the seminar course or the "Computer Architecture" course

- Do readings and assignments on your own

- There are many exciting projects and research positions, e.g.:

- Memory systems

- Hardware security

- □ GPUs, FPGAs, heterogeneous systems, ...

- New execution paradigms (e.g., in-memory computing)

- Security-architecture-reliability-energy-performance interactions

- Architectures for medical/health/genomics

- <u>A limited list is here: https://safari.ethz.ch/theses/</u>

#### How To Do Projects with SAFARI?

- Be excited about topics we work on

- Get in touch with me & my students/postdocs

- Browse projects here (not all projects are listed)

<u>https://safari.ethz.ch/theses/</u>

- Take our courses and enjoy them ☺

SAFAR

- Read our papers and get in touch with authors

- <u>https://people.inf.ethz.ch/omutlu/projects.htm</u>

- Email us & apply here: <u>https://safari.ethz.ch/work-with-us/</u>

### Food for Thought: Two Quotes

The reasonable man adapts himself to the world; The unreasonable one persists in trying adapt the world to himself.

Therefore, all progress depends on the unreasonable man.

#### **George Bernard Shaw**

Progress is impossible without change, and those who cannot change their minds cannot change anything.

# Digital Design & Computer Arch. Lecture 27: Epilogue

Prof. Onur Mutlu

ETH Zürich Spring 2022 9 June 2022

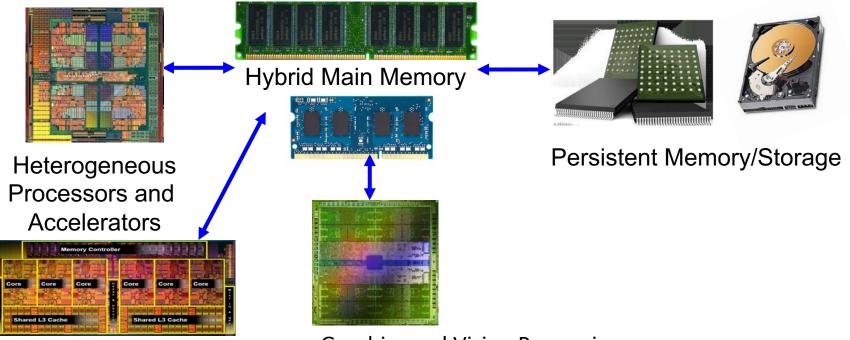

## Research in Computer Architecture

#### Current Research Mission

Computer architecture, HW/SW, systems, bioinformatics, security

**Graphics and Vision Processing**

#### **Build fundamentally better architectures**

#### SAFARI

#### Four Key Current Directions

Fundamentally Secure/Reliable/Safe Architectures

Fundamentally Energy-Efficient Architectures

Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency and Predictable Architectures

Architectures for AI/ML, Genomics, Medicine, Health

### Current Research Mission & Major Topics

#### **Build fundamentally better architectures**

Broad research spanning apps, systems, logic with architecture at the center

- Data-centric arch. for low energy & high perf.

Proc. in Mem/DRAM, NVM, unified mem/storage

- Low-latency & predictable architectures

- □ Low-latency, low-energy yet low-cost memory

- QoS-aware and predictable memory systems

- Fundamentally secure/reliable/safe arch.

Tolerating all bit flips; patchable HW; secure mem

- Architectures for ML/AI/Genomics/Health/Med

Algorithm/arch./logic co-design; full heterogeneity

- Data-driven and data-aware architectures

- ML/AI-driven architectural controllers and design

- Expressive memory and expressive systems

#### **SAFARI**

#### Research & Teaching: Some Overview Talks

- Future Computing Architectures

- https://www.youtube.com/watch?v=kgiZISOcGFM&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJI&index=1

- Enabling In-Memory Computation

- https://www.youtube.com/watch?v=njX 14584Jw&list=PL5Q2soXY2Zi8D 5MGV6EnXEJHnV2YFBJl&index=16

- Accelerating Genome Analysis

- https://www.youtube.com/watch?v=r7sn41IH-4A&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=41

- Rethinking Memory System Design

- https://www.youtube.com/watch?v=F7xZLNMIY1E&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=3

- Intelligent Architectures for Intelligent Machines

- https://www.youtube.com/watch?v=c6\_LgzuNdkw&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJI&index=25

- The Story of RowHammer

- https://www.youtube.com/watch?v=sgd7PHQQ1AI&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=39

#### An Interview on Research and Education

- Computing Research and Education (@ ISCA 2019)

- https://www.youtube.com/watch?v=8ffSEKZhmvo&list=PL5Q2 soXY2Zi\_4oP9LdL3cc8G6NIjD2Ydz

- Maurice Wilkes Award Speech (10 minutes)

- https://www.youtube.com/watch?v=tcQ3zZ3JpuA&list=PL5Q2 soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=15

### More Thoughts and Suggestions

Onur Mutlu,

<u>"Some Reflections (on DRAM)"</u>

Award Speech for <u>ACM SIGARCH Maurice Wilkes Award</u>, at the **ISCA** Awards

Ceremony, Phoenix, AZ, USA, 25 June 2019.

[Slides (pptx) (pdf)]

[Video of Award Acceptance Speech (Youtube; 10 minutes) (Youku; 13 minutes)]

[Video of Interview after Award Acceptance (Youtube; 1 hour 6 minutes) (Youku; 1 hour 6 minutes)]

[News Article on "ACM SIGARCH Maurice Wilkes Award goes to Prof. Onur Mutlu"]

Onur Mutlu,

<u>"How to Build an Impactful Research Group"</u>

<u>57th Design Automation Conference Early Career Workshop (DAC</u>), Virtual,

19 July 2020.

[Slides (pptx) (pdf)]

#### SAFARI

### Referenced Papers, Talks, Artifacts

All are available at

https://people.inf.ethz.ch/omutlu/projects.htm

http://scholar.google.com/citations?user=7XyGUGkAAAAJ&hl=en

https://www.youtube.com/onurmutlulectures

https://github.com/CMU-SAFARI/

# Some Basics of Research

### How To Do Research & Advanced Dev.

- We will talk a lot about this in this course

- Learning by example

Reading and evaluating strong and seminal papers & designs

- Learning by doing

- Semester-long research/design projects, masters' projects, PhD thesis

- Learning by open, critical discussions

- Paper reading groups, frequent brainstorming and discussions

- Design sessions

- Collaborations

#### What Is The Goal of Research?

- To generate new insight

- that can enable what previously did not exist

Research is a hunt for insight that can eventually impact the world

### Some Basic Advice for Good Research

- Choose great problems to solve: Have great taste

- Difficult

- Important

- High impact

- Read heavily and critically

- Think big (out of the box)

- Do not restrain yourself to tweaks or constraints of today

- Yet, think about adoption issues

#### Aim high

#### Write and present extremely well

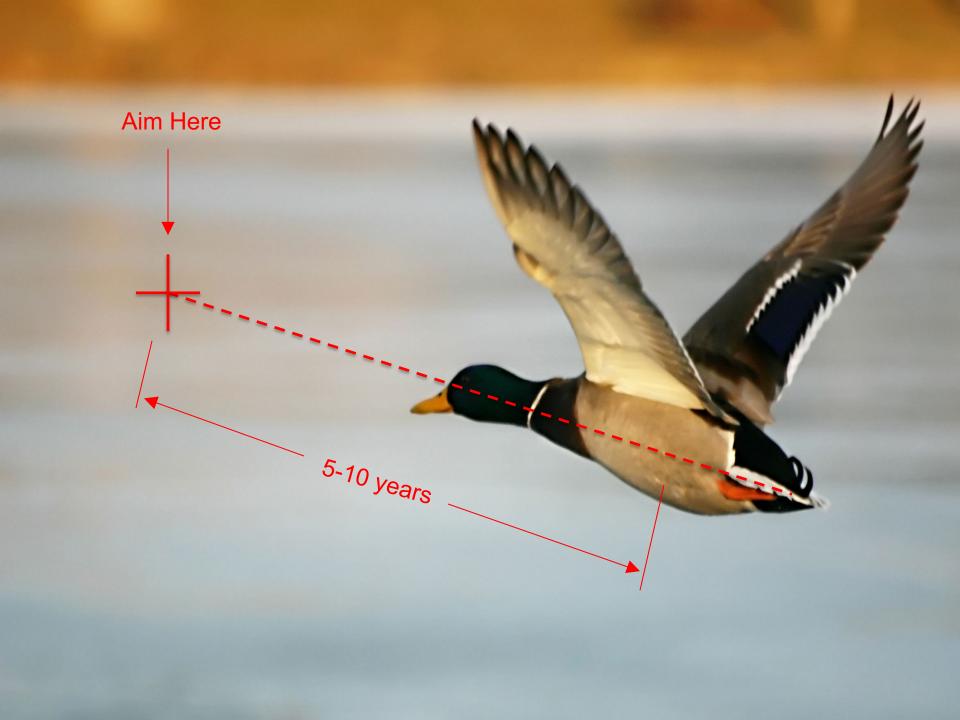

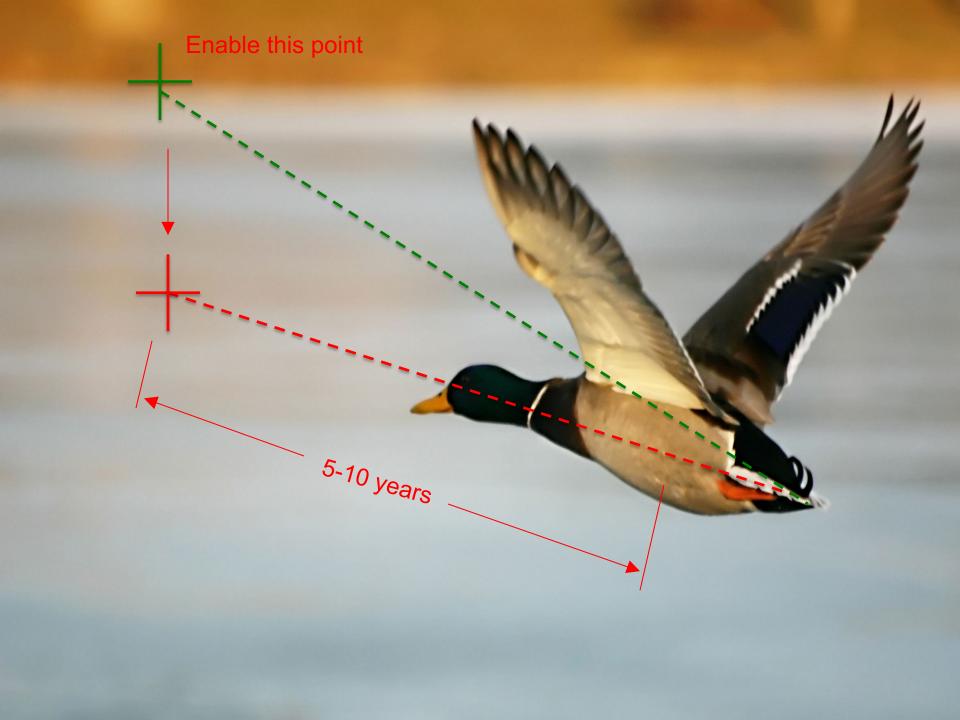

#### Looking here for lost keys

### Lost keys here

### Looking here

\*

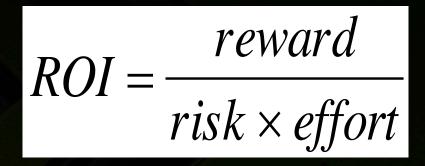

### **The Research Formula**

### Reward

## If you are wildly successful, what difference will it make?

reward ROI =risk × effort

### Effort

## Learn as much as possible with as little work as possible

reward ROI =risk × effort

### Effort

### Do the minimum analysis and experimentation necessary to make a point

reward ROI =risk × effort

Research is a *hunt for insight*

Need to get off the beaten path to find new insights

### Recommended Talk

- Bill Dally, <u>Moving the needle: Effective Computer</u> <u>Architecture Research in Academy and Industry</u> ISCA 2010 Keynote Talk.

- Acknowledgment: Past few slides are from this talk

What transfers is *insight* Not academic design Not performance numbers

### More Good Advice

### "The purpose of computing is insight, not numbers" *Richard Hamming*

## Some Personal Examples

- Onur Mutlu

- □ Full Professor @ ETH Zurich ITET (INFK), since September 2015

- Strecker Professor @ Carnegie Mellon University ECE/CS, 2009-2016, 2016-...

- □ PhD from UT-Austin, worked at Google, VMware, Microsoft Research, Intel, AMD

- https://people.inf.ethz.ch/omutlu/

- omutlu@gmail.com (Best way to reach me)

- https://people.inf.ethz.ch/omutlu/projects.htm

- Research and Teaching in:

- Computer architecture, computer systems, hardware security, bioinformatics

- Memory and storage systems

- Hardware security, safety, predictability

- Fault tolerance, robust systems

- Hardware/software cooperation

- Architectures for bioinformatics, health, medicine, intelligent decision making

• ...

### Onur Mutlu's SAFARI Research Group

### Computer architecture, HW/SW, systems, bioinformatics, security, memory

https://safari.ethz.ch/safari-newsletter-april-2020/

### SAFARI Newsletter January 2021 Edition

### <u>https://safari.ethz.ch/safari-newsletter-january-2021/</u>

in 🖸 🖌 f

Think Big, Aim High, and Have a Wonderful 2021! Newsletter January 2021

Dear SAFARI friends,

Happy New Year! We are excited to share our group highlights with you in this second edition of the SAFARI newsletter (You can find the first edition from April 2020 here). 2020 has

### Principle: Teaching and Research

## Teaching drives Research Research drives Teaching

## Focus on Insight Encourage New Ideas

### Principle: Learning and Scholarship

## Focus on learning and scholarship

### Principle: Environment of Freedom

## Create an environment that values free exploration, openness, collaboration, hard work, creativity

### Principle: Learning and Scholarship

# The quality of your work defines your impact

### Research & Teaching: Some Overview Talks

https://www.youtube.com/onurmutlulectures

- Future Computing Architectures

- https://www.youtube.com/watch?v=kgiZISOcGFM&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJI&index=1

- Enabling In-Memory Computation

- https://www.youtube.com/watch?v=njX 14584Jw&list=PL5Q2soXY2Zi8D 5MGV6EnXEJHnV2YFBJl&index=16

- Accelerating Genome Analysis

- https://www.youtube.com/watch?v=r7sn41lH-4A&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=41

- Rethinking Memory System Design

- https://www.youtube.com/watch?v=F7xZLNMIY1E&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=3

- Intelligent Architectures for Intelligent Machines

- https://www.youtube.com/watch?v=c6\_LgzuNdkw&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=25

- The Story of RowHammer

- https://www.youtube.com/watch?v=sgd7PHQQ1AI&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=39

### An Interview on Research and Education

- Computing Research and Education (@ ISCA 2019)

- https://www.youtube.com/watch?v=8ffSEKZhmvo&list=PL5Q2 soXY2Zi\_4oP9LdL3cc8G6NIjD2Ydz

- Maurice Wilkes Award Speech (10 minutes)

- https://www.youtube.com/watch?v=tcQ3zZ3JpuA&list=PL5Q2 soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=15

### More Thoughts and Suggestions

Onur Mutlu,

<u>"Some Reflections (on DRAM)"</u>

Award Speech for <u>ACM SIGARCH Maurice Wilkes Award</u>, at the **ISCA** Awards

Ceremony, Phoenix, AZ, USA, 25 June 2019.

[Slides (pptx) (pdf)]

[Video of Award Acceptance Speech (Youtube; 10 minutes) (Youku; 13 minutes)]

[Video of Interview after Award Acceptance (Youtube; 1 hour 6 minutes) (Youku; 1 hour 6 minutes)]

[News Article on "ACM SIGARCH Maurice Wilkes Award goes to Prof. Onur Mutlu"]

Onur Mutlu,

<u>"How to Build an Impactful Research Group"</u>

<u>57th Design Automation Conference Early Career Workshop (DAC</u>), Virtual,

19 July 2020.

[Slides (pptx) (pdf)]

### SAFARI

### Data Movement vs. Computation Energy

### A memory access consumes ~100-1000X the energy of a complex addition