# Memory Systems and Memory-Centric Computing Systems Part 3: Computation in Memory

Prof. Onur Mutlu omutlu@gmail.com https://people.inf.ethz.ch/omutlu

7 July 2019 SAMOS Tutorial

**ETH** zürich

## Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Minimally Changing Memory Chips

- Exploiting 3D-Stacked Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

### 1. Data access is a major bottleneck

Applications are increasingly data hungry

### 2. Energy consumption is a key limiter

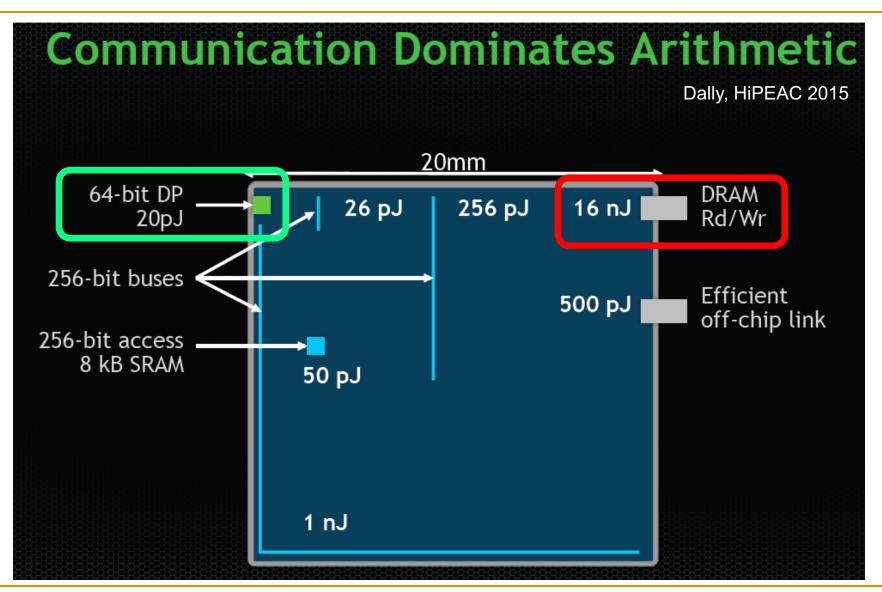

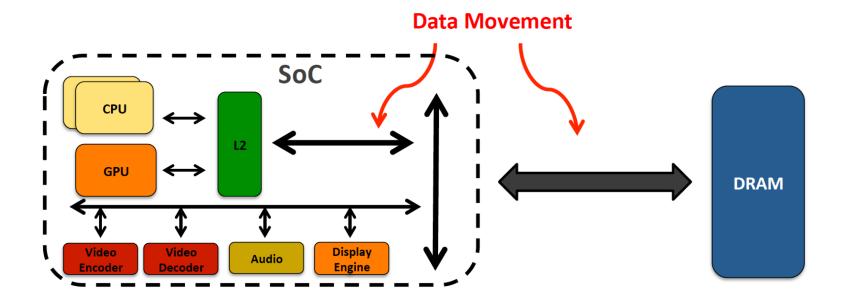

# 3. Data movement energy dominates compute

Especially true for off-chip to on-chip movement

# Observation and Opportunity

#### High latency and high energy caused by data movement

- Long, energy-hungry interconnects

- Energy-hungry electrical interfaces

- Movement of large amounts of data

- Opportunity: Minimize data movement by performing computation directly (near) where the data resides

- Processing in memory (PIM)

- In-memory computation/processing

- Near-data processing (NDP)

- General concept applicable to any data storage & movement unit (caches, SSDs, main memory, network, controllers)

### Four Key Issues in Future Platforms

Fundamentally Secure/Reliable/Safe Architectures

Fundamentally Energy-Efficient Architectures

Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency Architectures

Architectures for Genomics, Medicine, Health

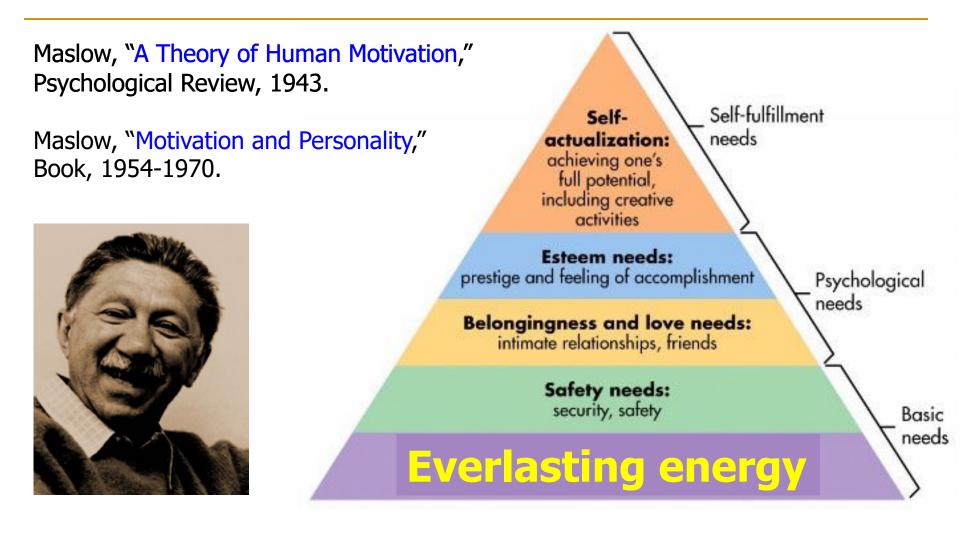

### Maslow's (Human) Hierarchy of Needs, Revisited

### Do We Want This?

SAFARI Source

Source: V. Milutinovic

### Or This?

I expect that over the coming decade memory subsys-Challenge and Opp(tem design will be the *only* important design issue for micro-

# High Performance, Energy Efficient, Sustainable

Data access is the major performance and energy bottleneck

# Our current design principles cause great energy waste (and great performance loss)

# Processing of data is performed far away from the data

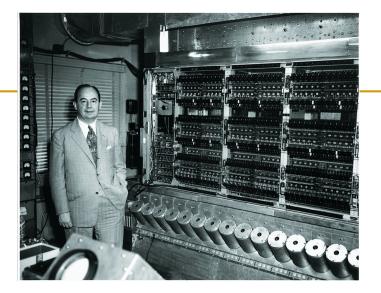

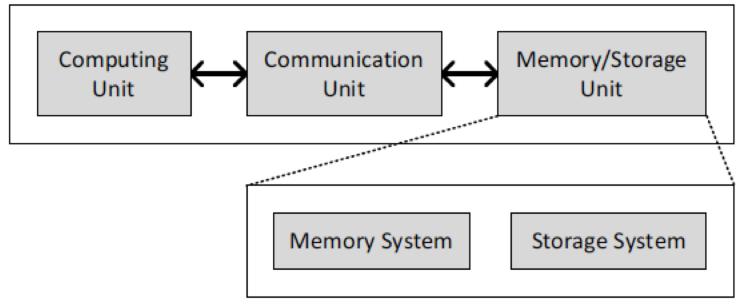

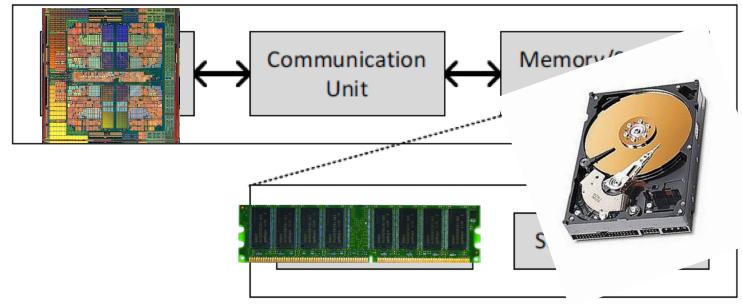

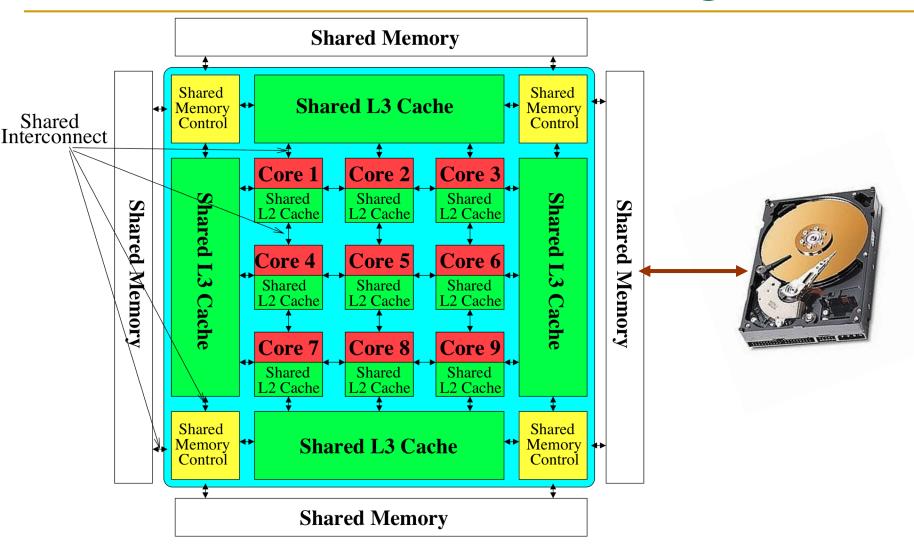

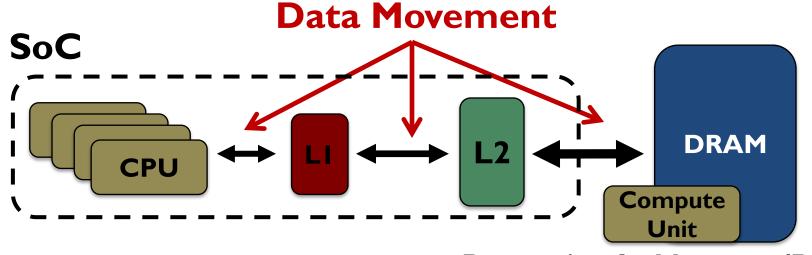

# A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

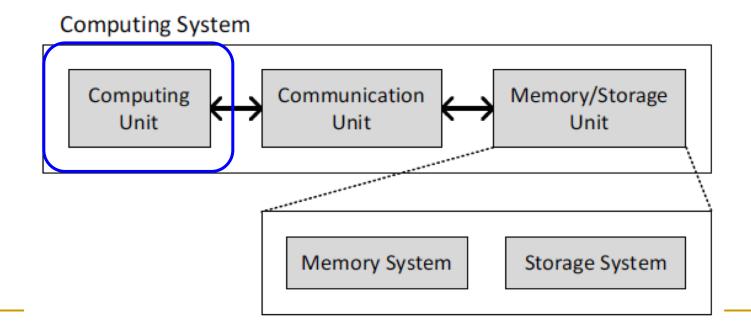

#### **Computing System**

Image source: https://lbsitbytes2010.wordpress.com/2013/03/29/john-von-neumann-roll-no-15/

# A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### **Computing System**

Image source: https://lbsitbytes2010.wordpress.com/2013/03/29/john-von-neumann-roll-no-15/

### Today's Computing Systems

- Are overwhelmingly processor centric

- All data processed in the processor  $\rightarrow$  at great system cost

- Processor is heavily optimized and is considered the master

- Data storage units are dumb and are largely unoptimized (except for some that are on the processor die)

I expect that over the coming decade memory subsystem design will be the *only* important design issue for microprocessors.

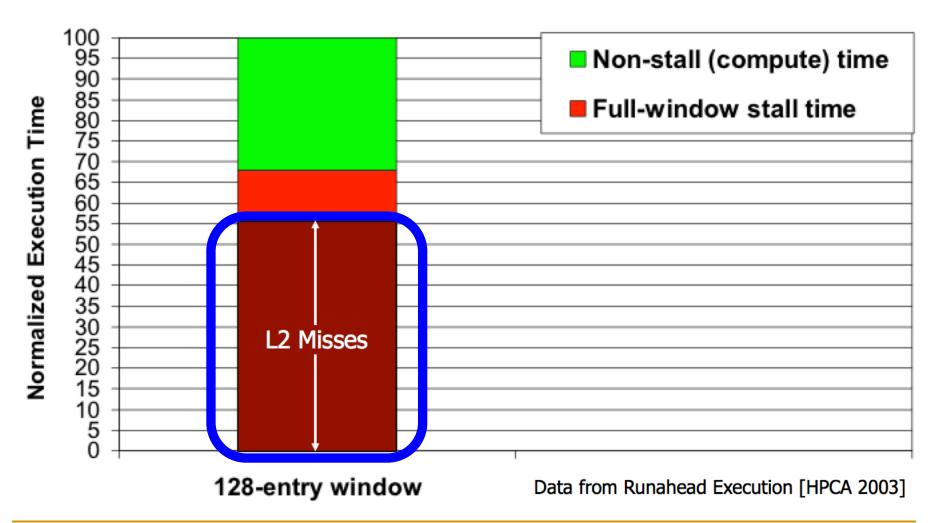

### "It's the Memory, Stupid!" (Richard Sites, MPR, 1996)

Mutlu+, "Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-Order Processors," HPCA 2003.

# The Performance Perspective

Onur Mutlu, Jared Stark, Chris Wilkerson, and Yale N. Patt, "Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors" Proceedings of the <u>9th International Symposium on High-Performance</u> <u>Computer Architecture</u> (HPCA), pages 129-140, Anaheim, CA, February 2003. <u>Slides (pdf)</u>

#### **Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors**

Onur Mutlu § Jared Stark † Chris Wilkerson ‡ Yale N. Patt §

§ECE Department The University of Texas at Austin {onur,patt}@ece.utexas.edu †Microprocessor Research Intel Labs jared.w.stark@intel.com

Desktop Platforms Group Intel Corporation chris.wilkerson@intel.com

## The Performance Perspective (Today)

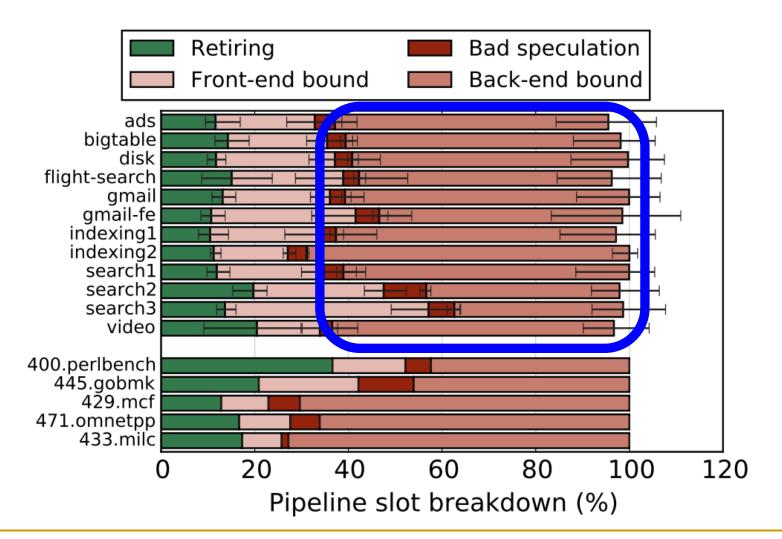

All of Google's Data Center Workloads (2015):

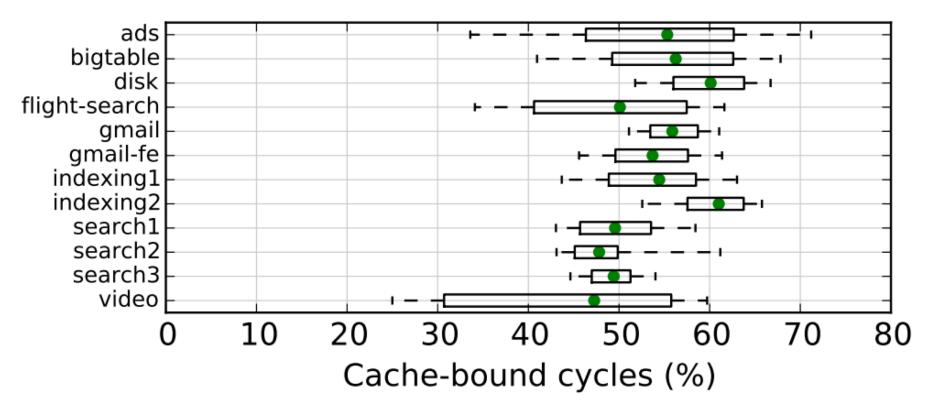

### The Performance Perspective (Today)

All of Google's Data Center Workloads (2015):

#### Figure 11: Half of cycles are spent stalled on caches.

## Perils of Processor-Centric Design

#### Grossly-imbalanced systems

- Processing done only in **one place**

- Everything else just stores and moves data: data moves a lot

- $\rightarrow$  Energy inefficient

- $\rightarrow$  Low performance

- $\rightarrow$  Complex

- Overly complex and bloated processor (and accelerators)

- To tolerate data access from memory

- Complex hierarchies and mechanisms

- $\rightarrow$  Energy inefficient

- $\rightarrow$  Low performance

- $\rightarrow$  Complex

### Perils of Processor-Centric Design

#### Most of the system is dedicated to storing and moving data

# The Energy Perspective

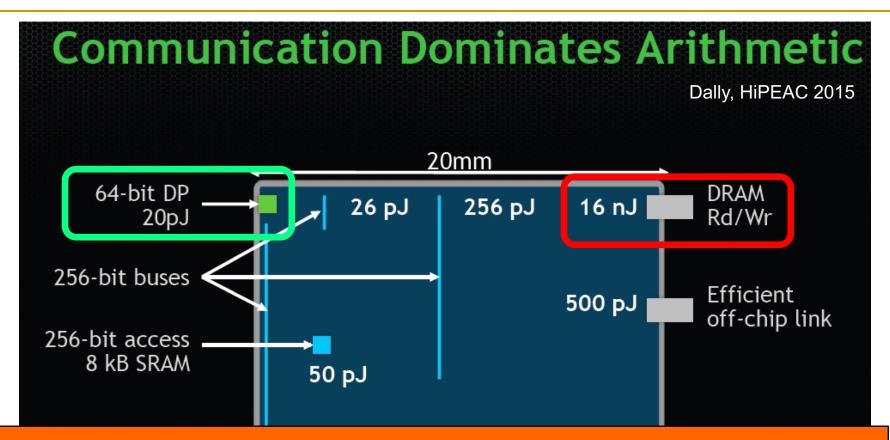

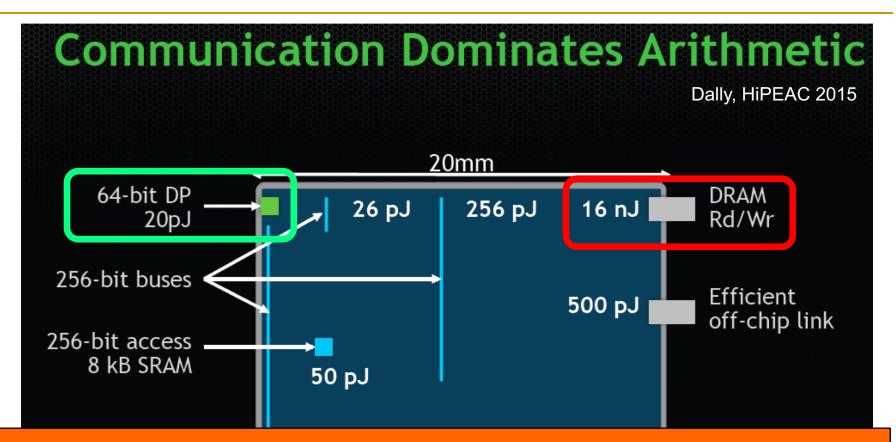

# Data Movement vs. Computation Energy

# A memory access consumes ~1000X the energy of a complex addition

## Data Movement vs. Computation Energy

Data movement is a major system energy bottleneck

- Comprises 41% of mobile system energy during web browsing [2]

- Costs ~115 times as much energy as an ADD operation [1, 2]

[1]: Reducing data Movement Energy via Online Data Clustering and Encoding (MICRO'16)

[2]: Quantifying the energy cost of data movement for emerging smart phone workloads on mobile platforms (IISWC'14)

### Energy Waste in Mobile Devices

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the <u>23rd International Conference on Architectural Support for Programming</u> <u>Languages and Operating Systems</u> (ASPLOS), Williamsburg, VA, USA, March 2018.

### 62.7% of the total system energy is spent on data movement

### Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup>Saugata Ghose<sup>1</sup>Youngsok Kim<sup>2</sup>Rachata Ausavarungnirun<sup>1</sup>Eric Shiu<sup>3</sup>Rahul Thakur<sup>3</sup>Daehyun Kim<sup>4,3</sup>Aki Kuusela<sup>3</sup>Allan Knies<sup>3</sup>Parthasarathy Ranganathan<sup>3</sup>Onur Mutlu<sup>5,1</sup>24

### We Do Not Want to Move Data!

# A memory access consumes ~1000X the energy of a complex addition

### We Need A Paradigm Shift To ...

Enable computation with minimal data movement

Compute where it makes sense (where data resides)

Make computing architectures more data-centric

## Goal: Processing Inside Memory

## Why In-Memory Computation Today?

- Pull from Systems and Applications

- Data access is a major system and application bottleneck

- Systems are energy limited

- Data movement much more energy-hungry than computation

## Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Minimally Changing Memory Chips

- Exploiting 3D-Stacked Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

# Processing in Memory: Two Approaches

Minimally changing memory chips

Exploiting 3D-stacked memory

# Approach 1: Minimally Changing DRAM

- DRAM has great capability to perform bulk data movement and computation internally with small changes

- Can exploit internal connectivity to move data

- Can exploit analog computation capability

• Examples: RowClone, In-DRAM AND/OR, Gather/Scatter DRAM

- <u>RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data</u> (Seshadri et al., MICRO 2013)

- □ Fast Bulk Bitwise AND and OR in DRAM (Seshadri et al., IEEE CAL 2015)

- <u>Gather-Scatter DRAM: In-DRAM Address Translation to Improve the Spatial</u> <u>Locality of Non-unit Strided Accesses</u> (Seshadri et al., MICRO 2015)

- "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology" (Seshadri et al., MICRO 2017)

#### SAFARI

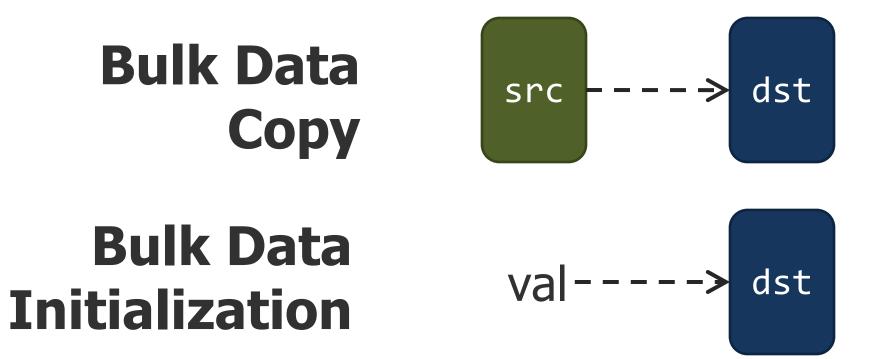

### Starting Simple: Data Copy and Initialization

# Starting Simple: Data Copy and Initialization

memmove & memcpy: 5% cycles in Google's datacenter [Kanev+ ISCA'15]

### VM Cloning Deduplication

---->

Many more

# Page Migration

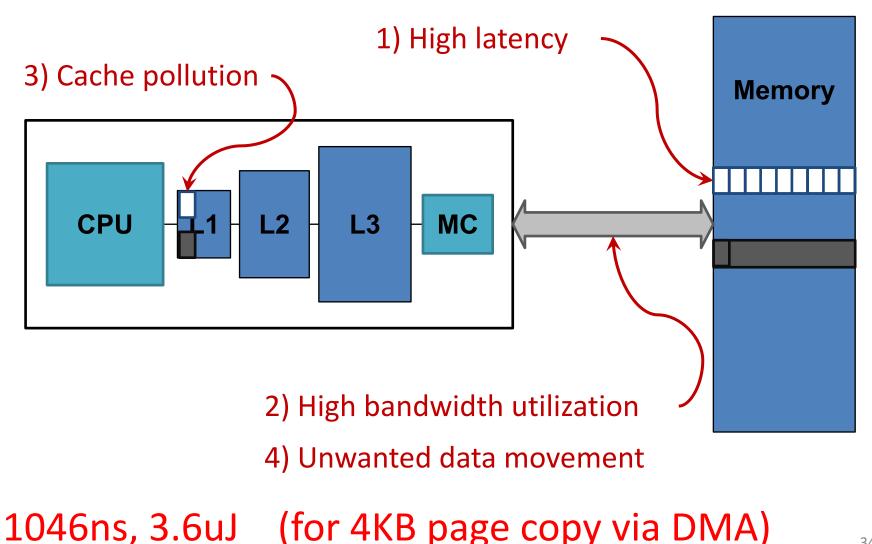

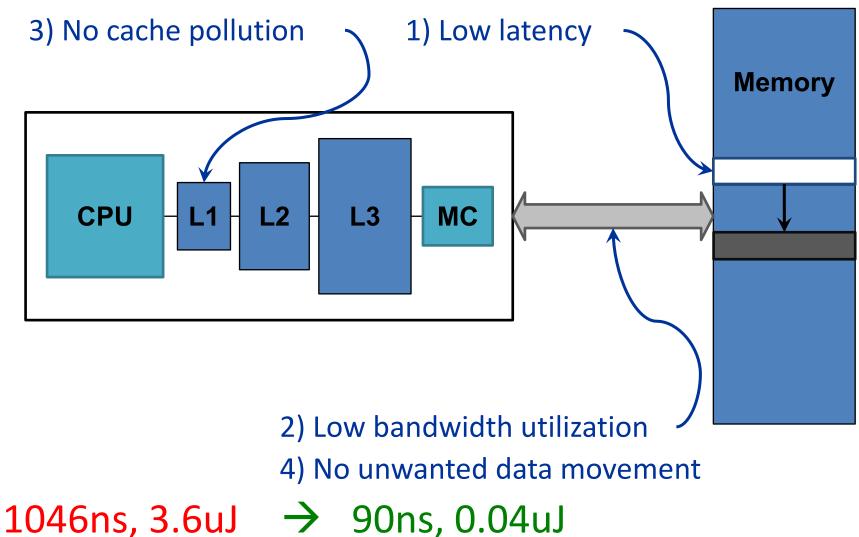

Today's Systems: Bulk Data Copy

Future Systems: In-Memory Copy

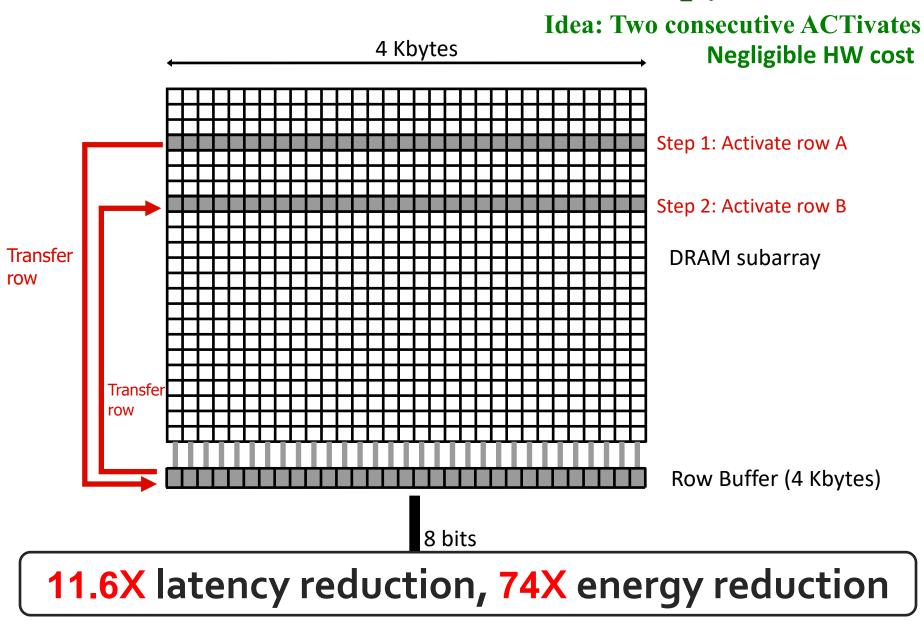

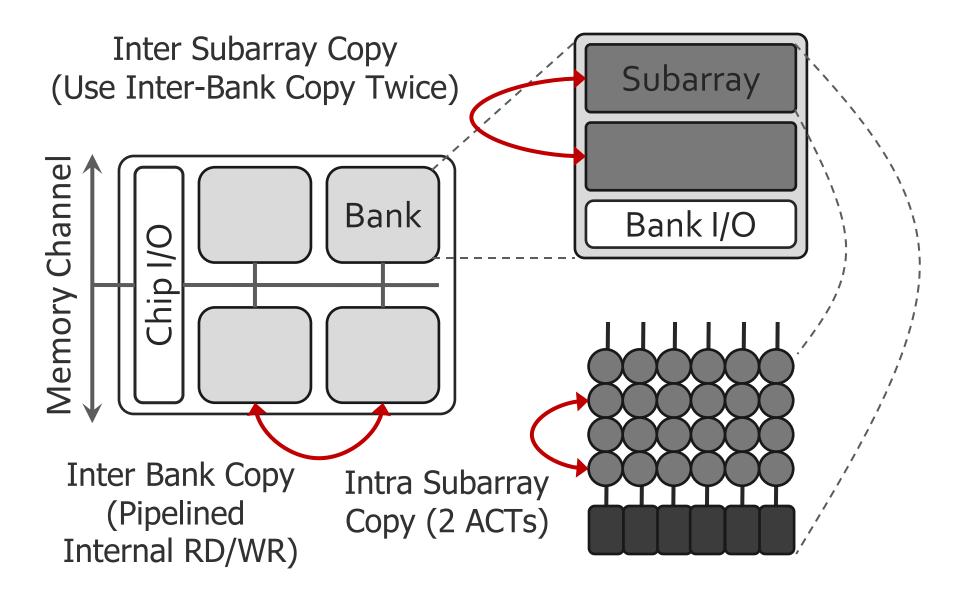

### RowClone: In-DRAM Row Copy

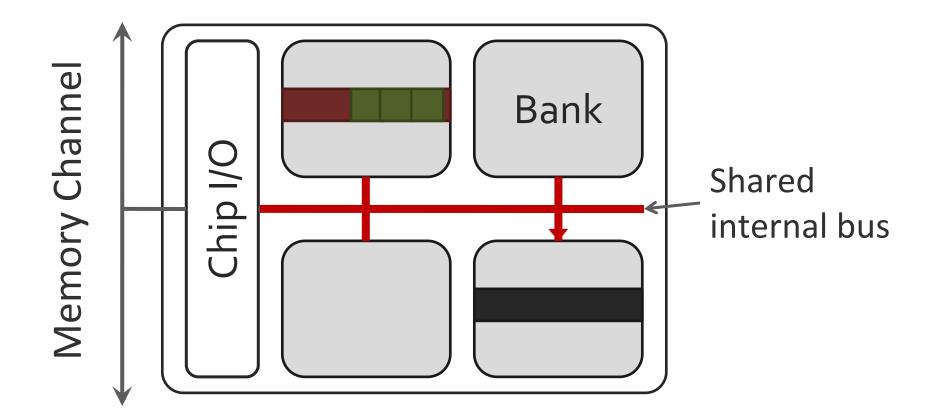

## RowClone: Inter-Bank

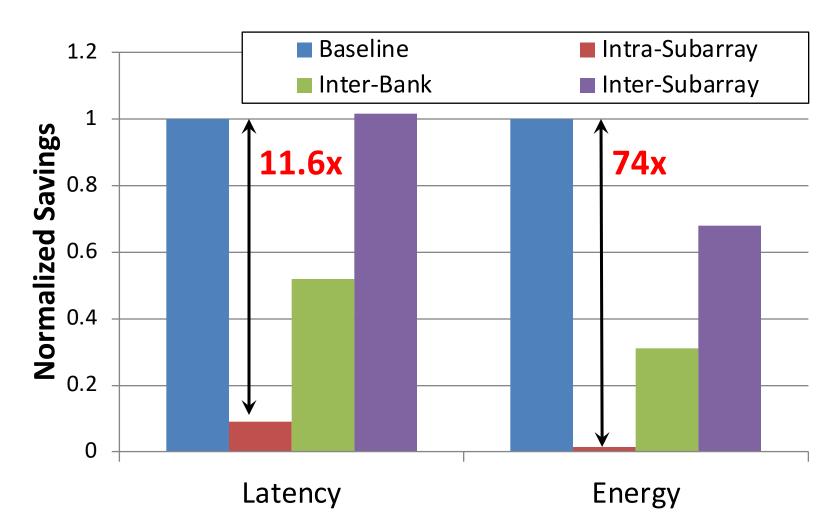

Overlap the latency of the read and the write 1.9X latency reduction, 3.2X energy reduction

### Generalized RowClone

### 0.01% area cost

## RowClone: Latency and Energy Savings

Seshadri et al., "RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data," MICRO 2013.

### More on RowClone

Vivek Seshadri, Yoongu Kim, Chris Fallin, Donghyuk Lee, Rachata Ausavarungnirun, Gennady Pekhimenko, Yixin Luo, Onur Mutlu, Michael A. Kozuch, Phillip B. Gibbons, and Todd C. Mowry,

"RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization" Proceedings of the <u>46th International Symposium on Microarchitecture</u>

(*MICRO*), Davis, CA, December 2013. [<u>Slides (pptx) (pdf)</u>] [<u>Lightning Session</u> <u>Slides (pptx) (pdf)</u>] [<u>Poster (pptx) (pdf)</u>]

### RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization

Vivek Seshadri Yoongu Kim Chris Fallin\* Donghyuk Lee vseshadr@cs.cmu.edu yoongukim@cmu.edu cfallin@c1f.net donghyuk1@cmu.edu Rachata Ausavarungnirun Gennady Pekhimenko Yixin Luo rachata@cmu.edu gpekhime@cs.cmu.edu yixinluo@andrew.cmu.edu Onur Mutlu Phillip B. Gibbons<sup>†</sup> Michael A. Kozuch<sup>†</sup> Todd C. Mowry onur@cmu.edu phillip.b.gibbons@intel.com michael.a.kozuch@intel.com tcm@cs.cmu.edu Carnegie Mellon University <sup>†</sup>Intel Pittsburgh

## In-Memory Bulk Bitwise Operations

- We can support in-DRAM COPY, ZERO, AND, OR, NOT, MAJ

- At low cost

- Using analog computation capability of DRAM

- Idea: activating multiple rows performs computation

- 30-60X performance and energy improvement

- Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology," MICRO 2017.

- New memory technologies enable even more opportunities

- Memristors, resistive RAM, phase change mem, STT-MRAM, ...

- Can operate on data with minimal movement

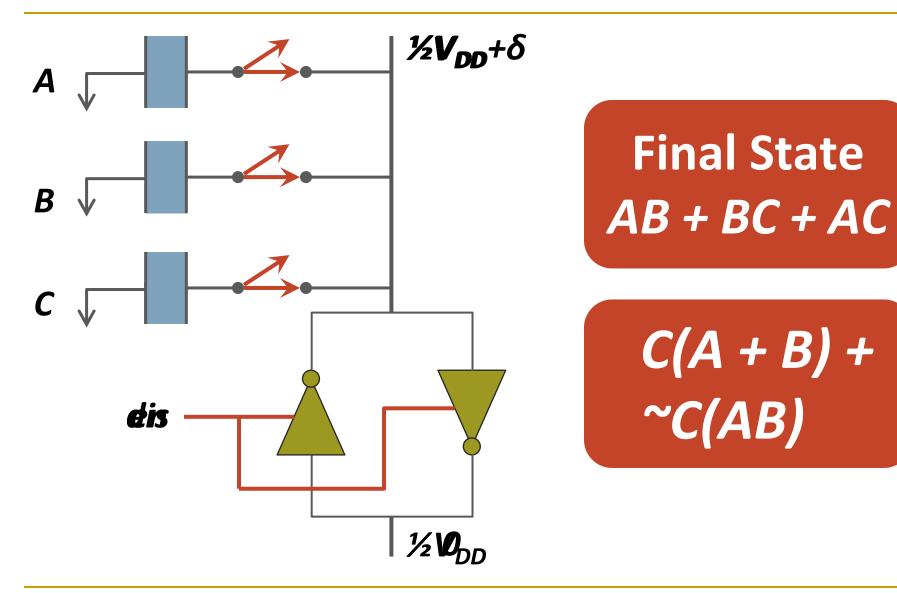

### In-DRAM AND/OR: Triple Row Activation

### In-DRAM Bulk Bitwise AND/OR Operation

- BULKAND A,  $B \rightarrow C$

- Semantics: Perform a bitwise AND of two rows A and B and store the result in row C

- R0 reserved zero row, R1 reserved one row

- D1, D2, D3 Designated rows for triple activation

- 1. RowClone A into D1

- 2. RowClone B into D2

- 3. RowClone R0 into D3

- 4. ACTIVATE D1,D2,D3

- 5. RowClone Result into C

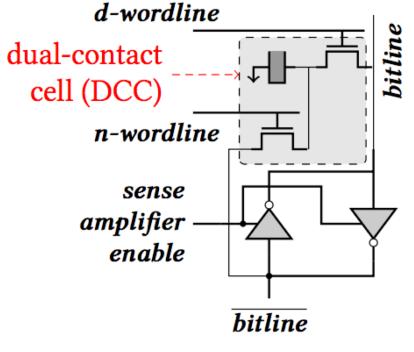

## In-DRAM NOT: Dual Contact Cell

Figure 5: A dual-contact cell connected to both ends of a sense amplifier Idea: Feed the negated value in the sense amplifier into a special row

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

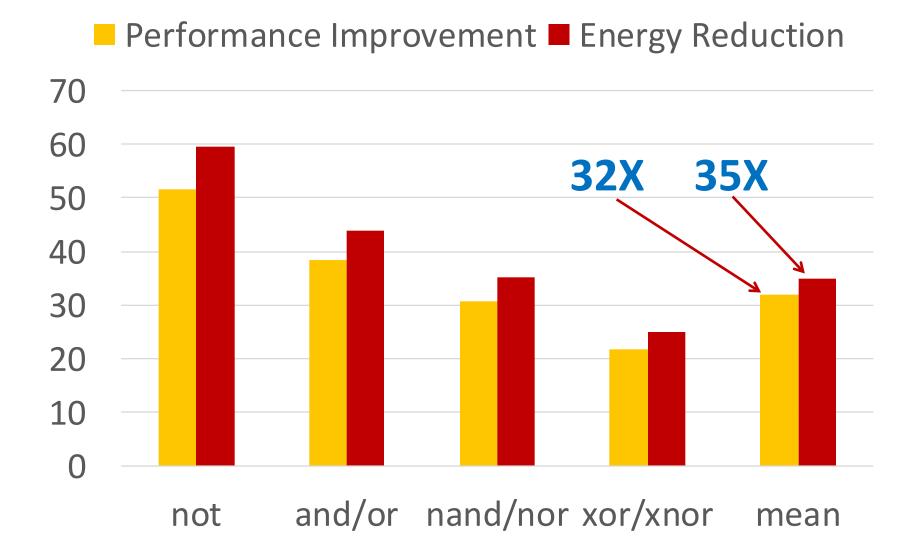

## Performance: In-DRAM Bitwise Operations

Figure 9: Throughput of bitwise operations on various systems.

|                | Design         | not   | and/or | nand/nor | xor/xnor |

|----------------|----------------|-------|--------|----------|----------|

| DRAM &         | DDR3           | 93.7  | 137.9  | 137.9    | 137.9    |

| Channel Energy | Ambit          | 1.6   | 3.2    | 4.0      | 5.5      |

| (nJ/KB)        | $(\downarrow)$ | 59.5X | 43.9X  | 35.1X    | 25.1X    |

Table 3: Energy of bitwise operations. ( $\downarrow$ ) indicates energy reduction of Ambit over the traditional DDR3-based design.

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

### Ambit vs. DDR3: Performance and Energy

47

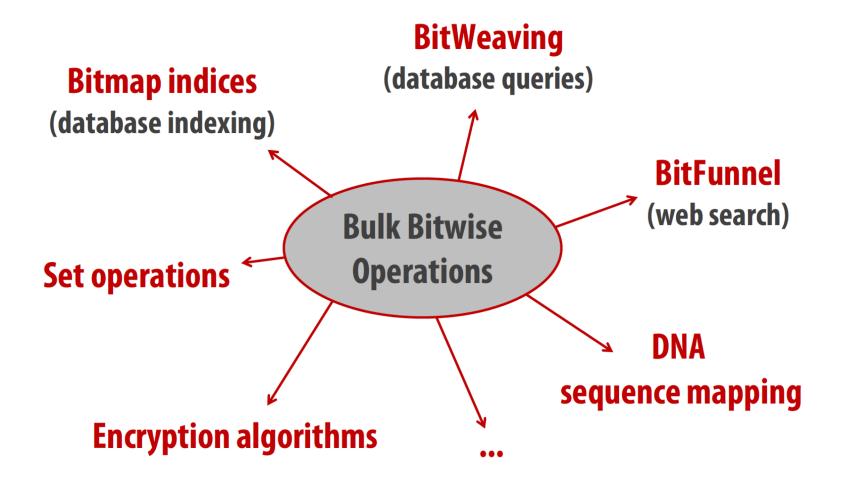

### Bulk Bitwise Operations in Workloads

### SAFARI

[1] Li and Patel, BitWeaving, SIGMOD 2013[2] Goodwin+, BitFunnel, SIGIR 2017

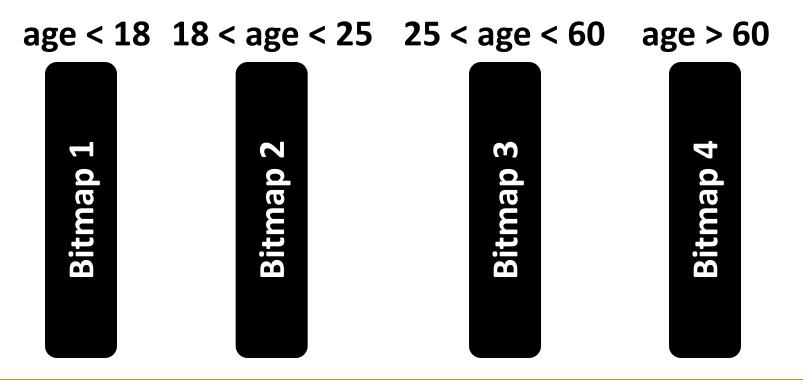

### Example Data Structure: Bitmap Index

- Alternative to B-tree and its variants

- Efficient for performing *range queries* and *joins*

- Many bitwise operations to perform a query

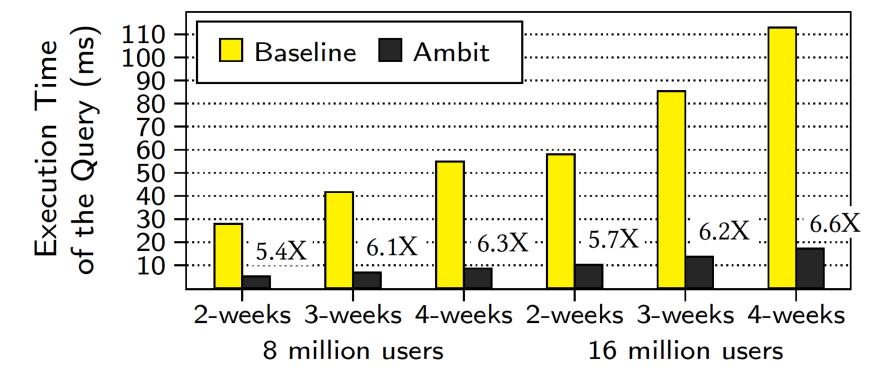

## Performance: Bitmap Index on Ambit

Figure 10: Bitmap index performance. The value above each bar indicates the reduction in execution time due to Ambit.

**>5.4-6.6X Performance Improvement**

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

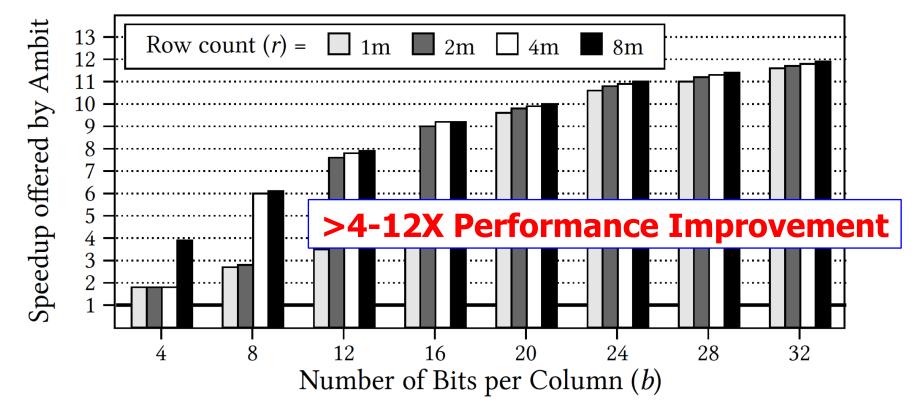

## Performance: BitWeaving on Ambit

#### `select count(\*) from T where c1 <= val <= c2`</pre>

## Figure 11: Speedup offered by Ambit over baseline CPU with SIMD for BitWeaving

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

## More on In-DRAM Bulk AND/OR

Vivek Seshadri, Kevin Hsieh, Amirali Boroumand, Donghyuk Lee, Michael A. Kozuch, Onur Mutlu, Phillip B. Gibbons, and Todd C. Mowry,

<u>"Fast Bulk Bitwise AND and OR in DRAM"</u> <u>IEEE Computer Architecture Letters</u> (CAL), April 2015.

## Fast Bulk Bitwise AND and OR in DRAM

Vivek Seshadri\*, Kevin Hsieh\*, Amirali Boroumand\*, Donghyuk Lee\*, Michael A. Kozuch<sup>†</sup>, Onur Mutlu\*, Phillip B. Gibbons<sup>†</sup>, Todd C. Mowry\* \*Carnegie Mellon University <sup>†</sup>Intel Pittsburgh

## More on In-DRAM Bitwise Operations

Vivek Seshadri et al., "<u>Ambit: In-Memory Accelerator</u> for Bulk Bitwise Operations Using Commodity DRAM <u>Technology</u>," MICRO 2017.

### Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology

Vivek Seshadri<sup>1,5</sup> Donghyuk Lee<sup>2,5</sup> Thomas Mullins<sup>3,5</sup> Hasan Hassan<sup>4</sup> Amirali Boroumand<sup>5</sup> Jeremie Kim<sup>4,5</sup> Michael A. Kozuch<sup>3</sup> Onur Mutlu<sup>4,5</sup> Phillip B. Gibbons<sup>5</sup> Todd C. Mowry<sup>5</sup>

<sup>1</sup>Microsoft Research India <sup>2</sup>NVIDIA Research <sup>3</sup>Intel <sup>4</sup>ETH Zürich <sup>5</sup>Carnegie Mellon University

Challenge: Intelligent Memory Device

# Does memory have to be dumb?

Challenge and Opportunity for Future

# Computing Architectures with

## Minimal Data Movement

## Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Minimally Changing Memory Chips

- Exploiting 3D-Stacked Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

## Processing in Memory: Two Approaches

Minimally changing memory chips

Exploiting 3D-stacked memory

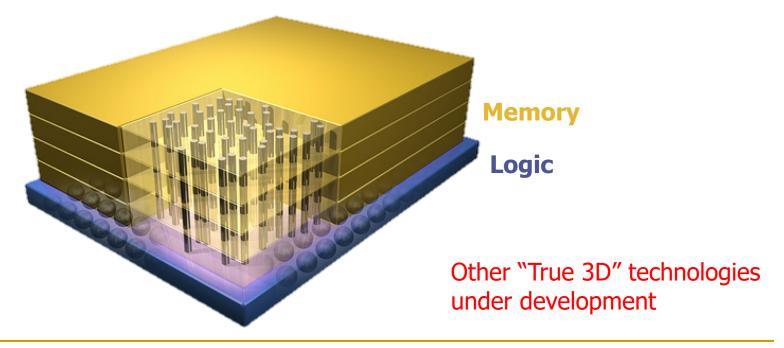

## Opportunity: 3D-Stacked Logic+Memory

## DRAM Landscape (circa 2015)

| Segment     | DRAM Standards & Architectures                                                                                                                                                                                                        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Commodity   | DDR3 (2007) [14]; DDR4 (2012) [18]                                                                                                                                                                                                    |

| Low-Power   | LPDDR3 (2012) [17]; LPDDR4 (2014) [20]                                                                                                                                                                                                |

| Graphics    | GDDR5 (2009) [15]                                                                                                                                                                                                                     |

| Performance | eDRAM [28], [32]; RLDRAM3 (2011) [29]                                                                                                                                                                                                 |

| 3D-Stacked  | WIO (2011) [16]; WIO2 (2014) [21]; MCDRAM (2015) [13];<br>HBM (2013) [19]; HMC1.0 (2013) [10]; HMC1.1 (2014) [11]                                                                                                                     |

| Academic    | SBA/SSA (2010) [38]; Staged Reads (2012) [8]; RAIDR (2012) [27];<br>SALP (2012) [24]; TL-DRAM (2013) [26]; RowClone (2013) [37];<br>Half-DRAM (2014) [39]; Row-Buffer Decoupling (2014) [33];<br>SARP (2014) [6]; AL-DRAM (2015) [25] |

Table 1. Landscape of DRAM-based memory

Kim+, "Ramulator: A Flexible and Extensible DRAM Simulator", IEEE CAL 2015.

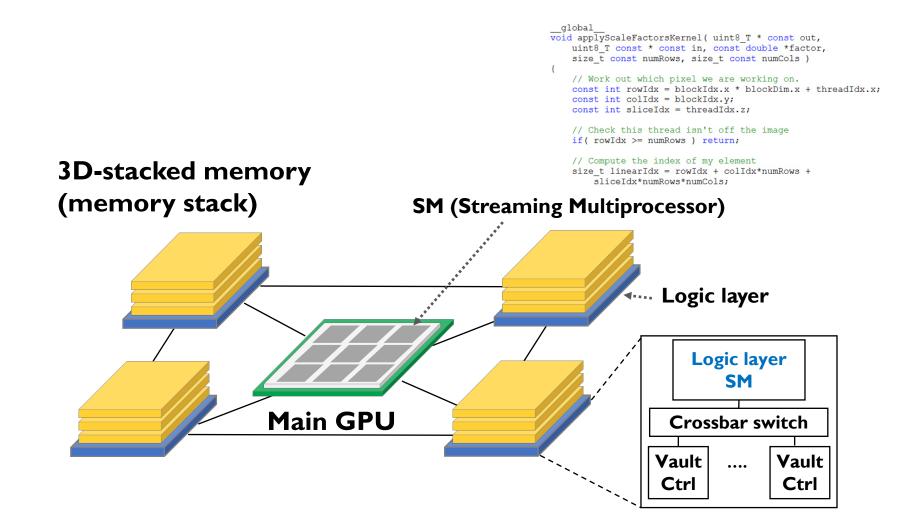

### Several Questions in 3D-Stacked PIM

- What are the performance and energy benefits of using 3D-stacked memory as a coarse-grained accelerator?

- By changing the entire system

- By performing simple function offloading

- What is the minimal processing-in-memory support we can provide?

- With minimal changes to system and programming

### Another Example: In-Memory Graph Processing

Large graphs are everywhere (circa 2015)

Scalable large-scale graph processing is challenging

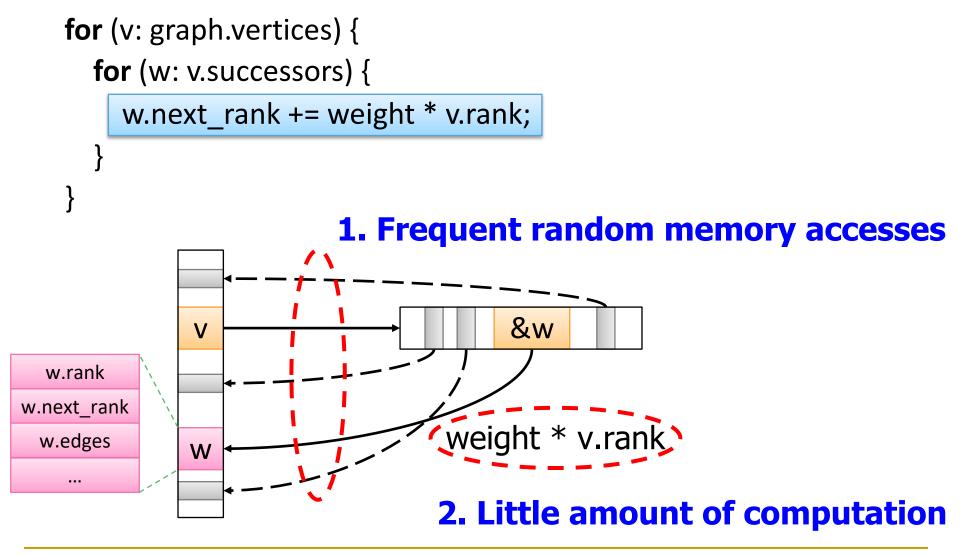

## Key Bottlenecks in Graph Processing

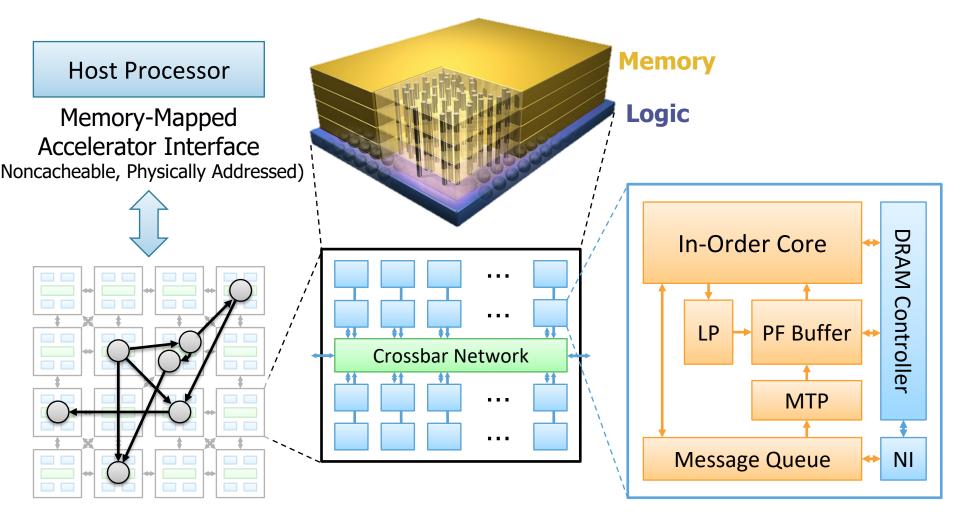

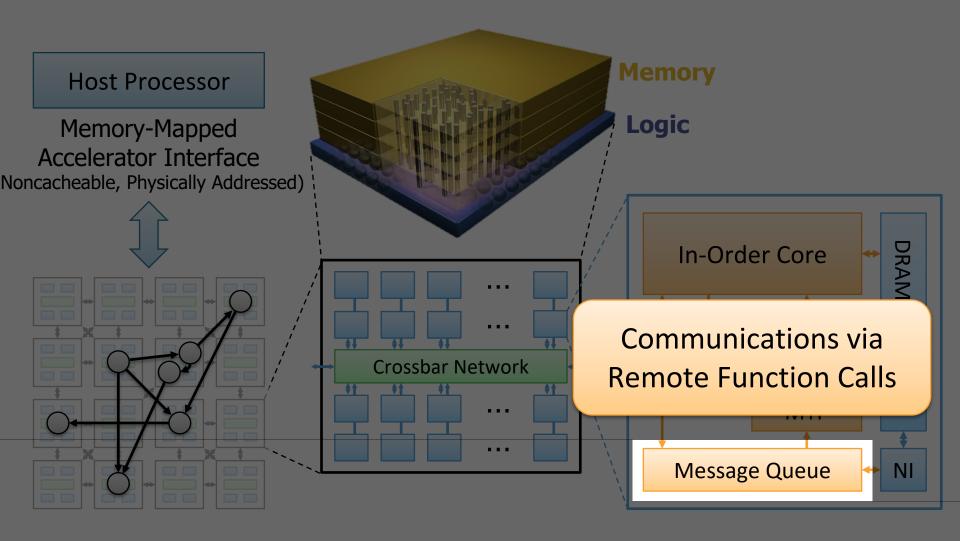

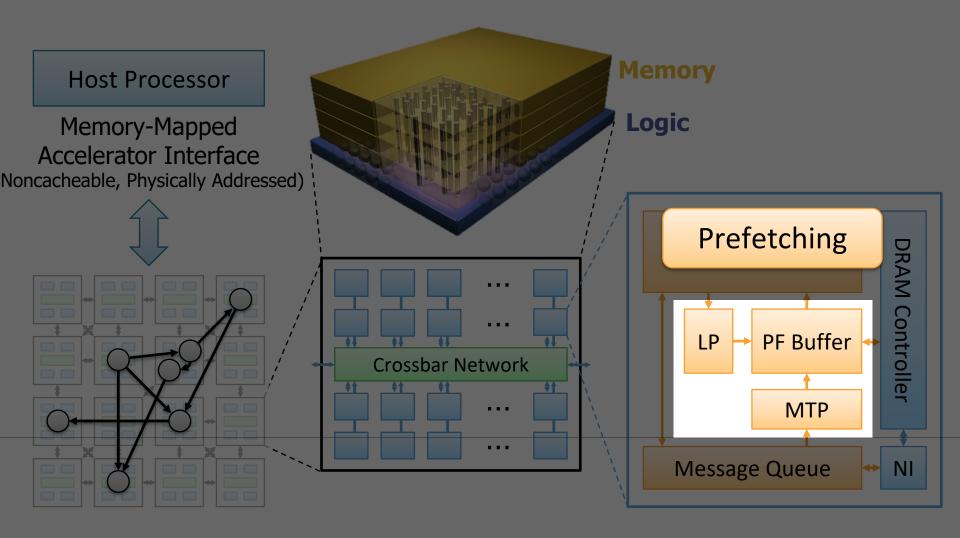

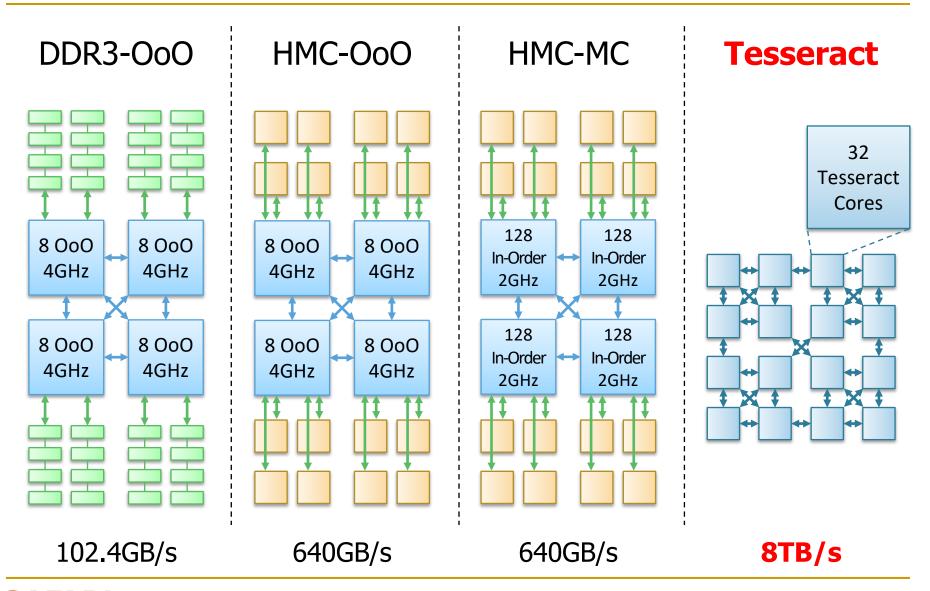

## Tesseract System for Graph Processing

Interconnected set of 3D-stacked memory+logic chips with simple cores

**SAFARI** Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing" ISCA 2015.

## Tesseract System for Graph Processing

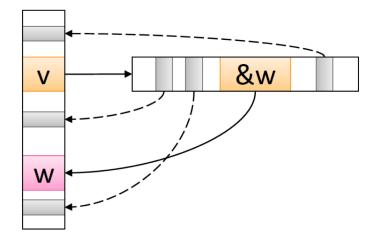

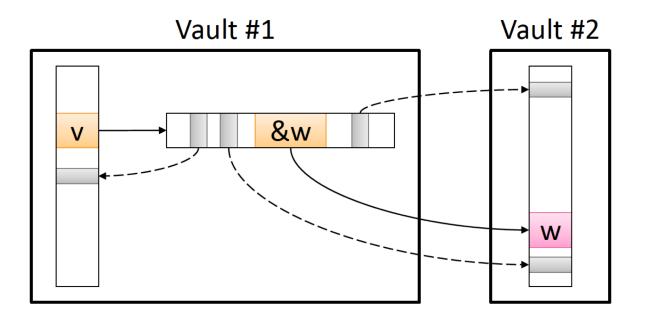

### Communications In Tesseract (I)

```

for (v: graph.vertices) {

```

for (w: v.successors) {

w.next\_rank += weight \* v.rank;

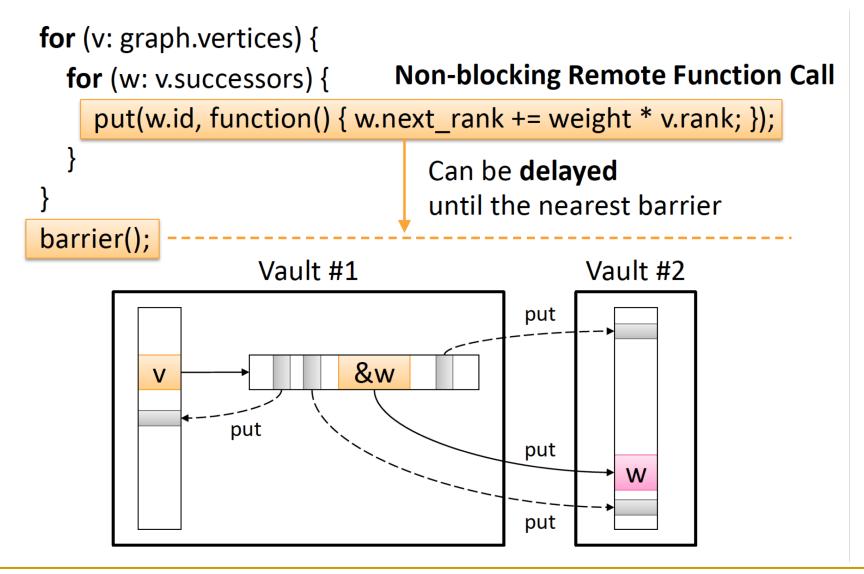

### Communications In Tesseract (II)

```

for (v: graph.vertices) {

```

for (w: v.successors) {

w.next\_rank += weight \* v.rank;

### Communications In Tesseract (III)

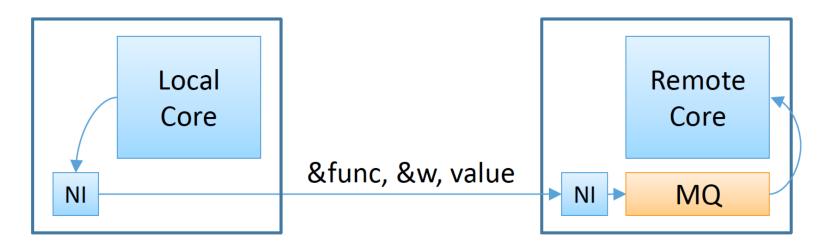

## Remote Function Call (Non-Blocking)

- 1. Send function address & args to the remote core

- 2. Store the incoming message to the message queue

- 3. Flush the message queue when it is full or a synchronization barrier is reached

put(w.id, function() { w.next\_rank += value; })

## Tesseract System for Graph Processing

### **Evaluated Systems**

**SAFARI** Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing" ISCA 2015.

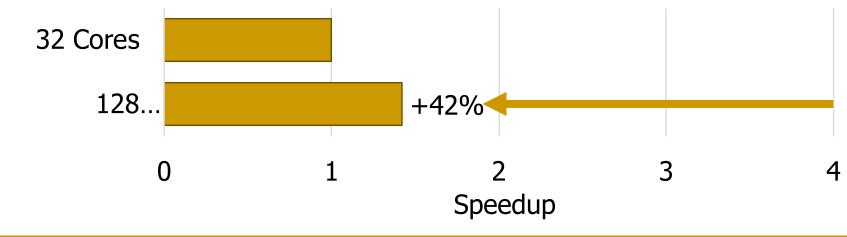

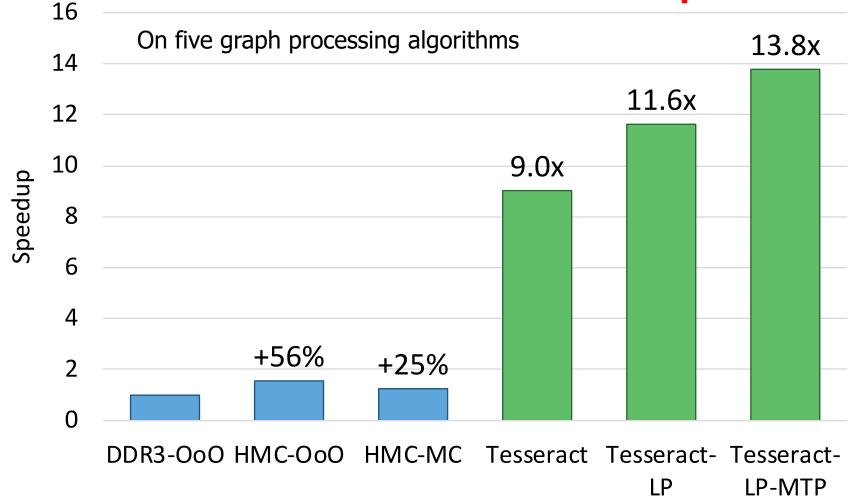

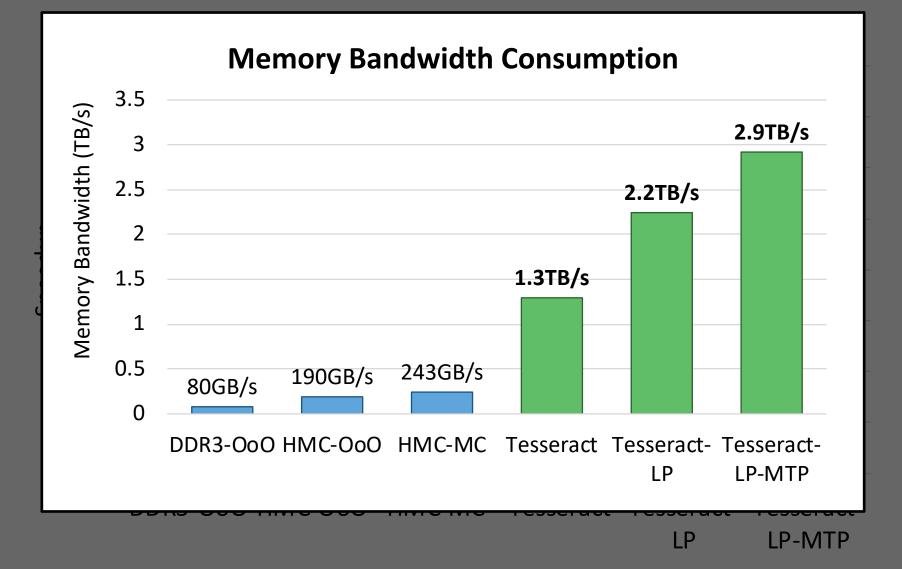

## Tesseract Graph Processing Performance

### >13X Performance Improvement

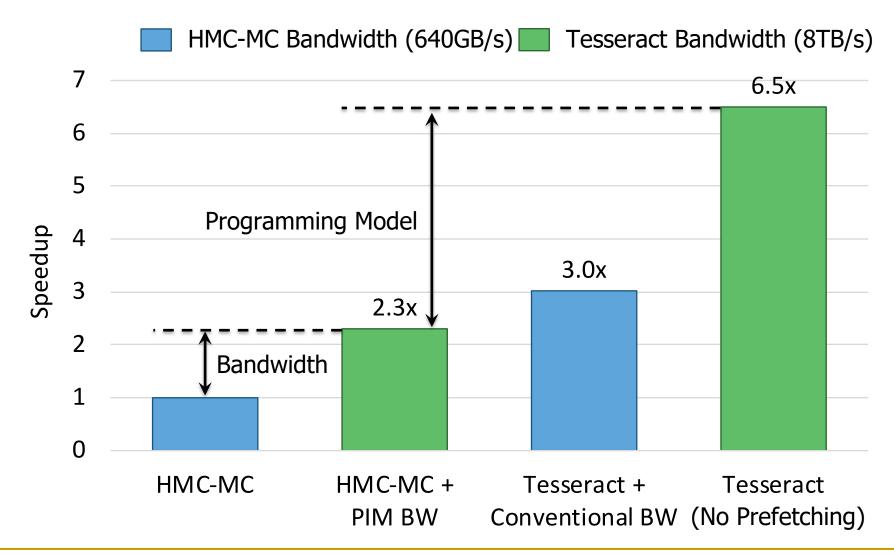

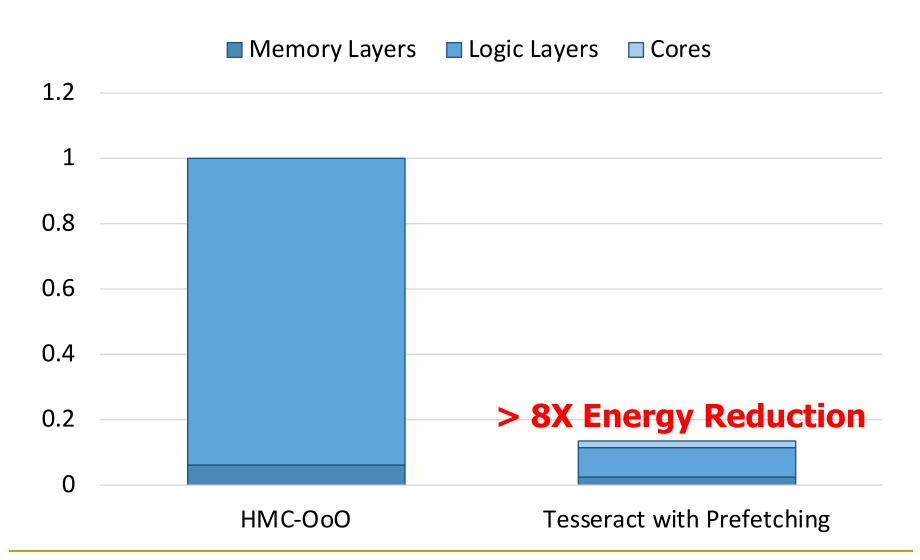

**SAFARI** Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing" ISCA 2015.

## Tesseract Graph Processing Performance

#### Effect of Bandwidth & Programming Model

### Tesseract Graph Processing System Energy

**SAFARI** Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing" ISCA 2015.

#### More on Tesseract

Junwhan Ahn, Sungpack Hong, Sungjoo Yoo, Onur Mutlu, and Kiyoung Choi,

"A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing"

Proceedings of the <u>42nd International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2015.

[Slides (pdf)] [Lightning Session Slides (pdf)]

#### A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing

Junwhan Ahn Sungpack Hong<sup>§</sup> Sungjoo Yoo Onur Mutlu<sup>†</sup> Kiyoung Choi junwhan@snu.ac.kr, sungpack.hong@oracle.com, sungjoo.yoo@gmail.com, onur@cmu.edu, kchoi@snu.ac.kr Seoul National University <sup>§</sup>Oracle Labs <sup>†</sup>Carnegie Mellon University

### Several Questions in 3D-Stacked PIM

- What are the performance and energy benefits of using 3D-stacked memory as a coarse-grained accelerator?

- By changing the entire system

- By performing simple function offloading

- What is the minimal processing-in-memory support we can provide?

- With minimal changes to system and programming

### 3D-Stacked PIM on Mobile Devices

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks"

Proceedings of the <u>23rd International Conference on Architectural</u> <u>Support for Programming Languages and Operating</u> <u>Systems</u> (**ASPLOS**), Williamsburg, VA, USA, March 2018.

#### Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand1Saugata Ghose1Youngsok Kim2Rachata Ausavarungnirun1Eric Shiu3Rahul Thakur3Daehyun Kim4,3Aki Kuusela3Allan Knies3Parthasarathy Ranganathan3Onur Mutlu<sup>5,1</sup>

# Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

#### **Amirali Boroumand**

Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, Onur Mutlu

SEOUL NATIONAL UNIVERSITY

# **Consumer Devices**

#### **Consumer devices are everywhere!**

### Energy consumption is a first-class concern in consumer devices

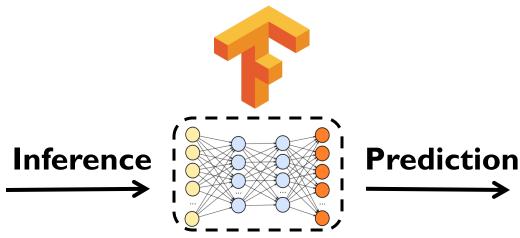

# Popular Google Consumer Workloads

Chrome

**Google's web browser**

#### **TensorFlow Mobile**

Google's machine learning framework

**Google's video codec**

# **Energy Cost of Data Movement**

#### I<sup>st</sup> key observation: 62.7% of the total system energy is spent on data movement

**Processing-In-Memory (PIM)**

**Potential solution: move computation close to data**

Challenge: limited area and energy budget

# Using PIM to Reduce Data Movement

2<sup>nd</sup> key observation: a significant fraction of the data movement often comes from simple functions

We can design lightweight logic to implement these <u>simple functions</u> in <u>memory</u>

Small embedded low-power core

> PIM Core

Small fixed-function accelerators

Offloading to PIM logic reduces energy and improves performance, on average, by 55.4% and 54.2%

# Goals

Understand the data movement related bottlenecks in modern consumer workloads

2 Analyze opportunities to mitigate data movement by using processing-in-memory (PIM)

**3** Design PIM logic that can maximize energy efficiency given the limited area and energy budget in consumer devices

# **Workload Analysis**

Chrome

**Google's web browser**

#### **TensorFlow Mobile**

Google's machine learning framework

**Google's video codec**

# **TensorFlow Mobile**

# 57.3% of the inference energy is spent on data movement

54.4% of the data movement energy comes from packing/unpacking\_and quantization

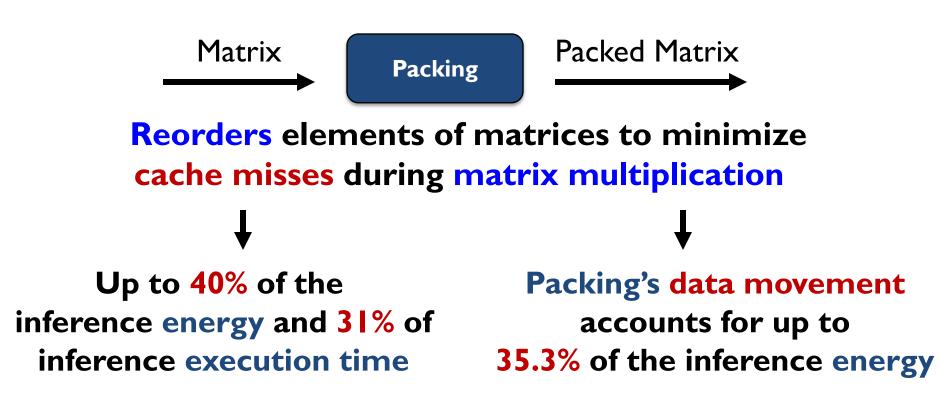

# Packing

A simple data reorganization process that requires simple arithmetic

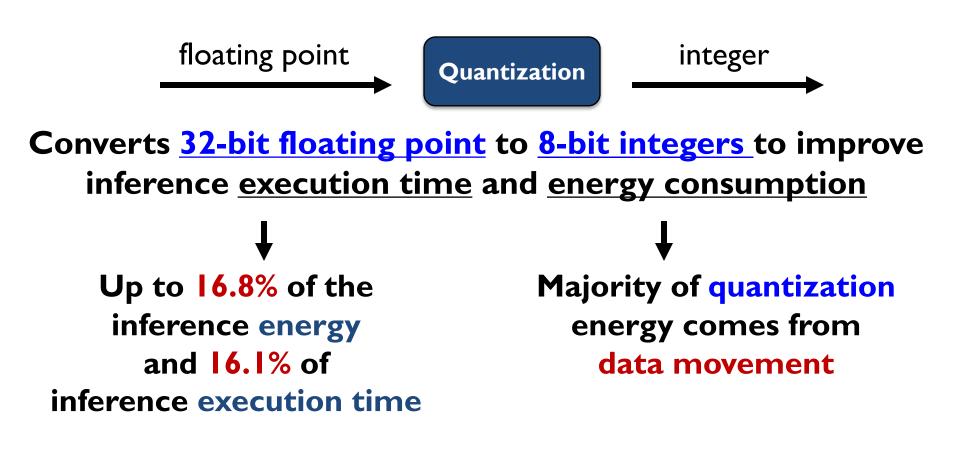

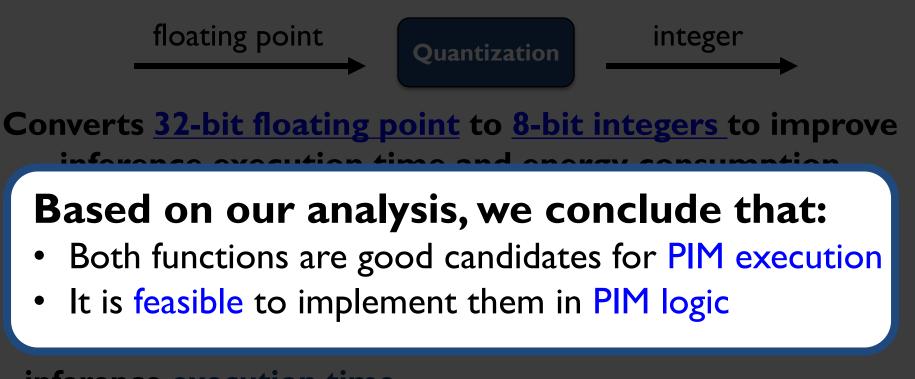

# Quantization

A simple data conversion operation that requires shift, addition, and multiplication operations

inference execution time

A simple data conversion operation that requires shift, addition, and multiplication operations

# **Evaluation Methodology**

- System Configuration (gem5 Simulator)

- SoC: 4 OoO cores, 8-wide issue, 64 kB Ll cache, 2MB L2 cache

- **PIM Core:** I core per vault, I-wide issue, 4-wide SIMD, 32kBLI cache

- **3D-Stacked Memory: 2GB cube**, 16 vaults per cube

- Internal Bandwidth: 256GB/S

- Off-Chip Channel Bandwidth: 32 GB/s

- Baseline Memory: LPDDR3, 2GB, FR-FCFS scheduler

- We study each target in isolation and emulate each separately and run them in our simulator 40 SAFARI

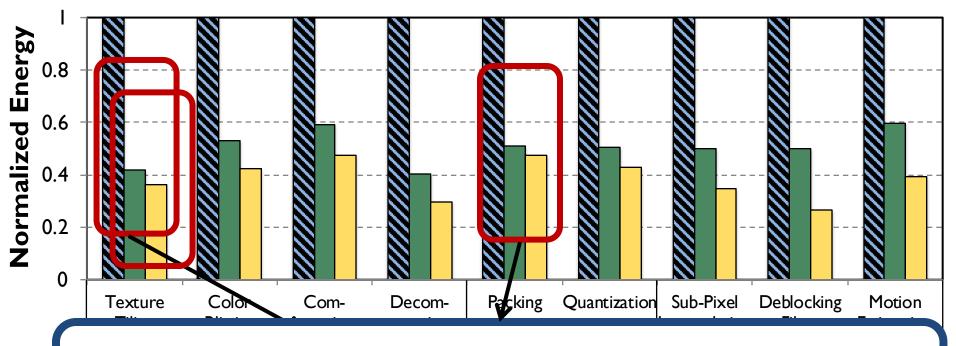

# **Normalized Energy**

77.7% and 82.6% of energy reduction for texture tiling and packing comes from eliminating data movement

PIM core and PIM accelerator reduces energy consumption on average by 49.1% and 55.4% SAFARI

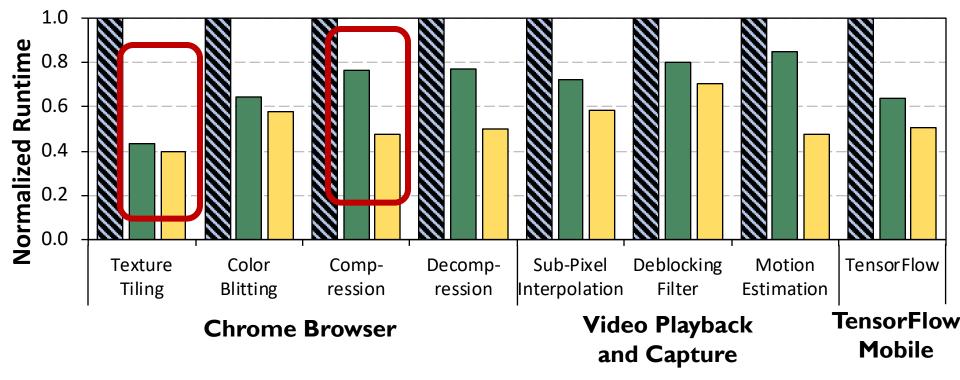

# **Normalized Runtime**

#### S CPU-Only ■ PIM-Core ■ PIM-Acc

Offloading these kernels to PIM core and PIM accelerator improves performance on average by 44.6% and 54.2%

# Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

#### **Amirali Boroumand**

Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, Onur Mutlu

### **ASPLOS 2018**

**Carnegie Mellon**

SEOUL NATIONAL UNIVERSITY

Google

### More on PIM for Mobile Devices

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the <u>23rd International Conference on Architectural Support for Programming</u> <u>Languages and Operating Systems</u> (ASPLOS), Williamsburg, VA, USA, March 2018.

# 62.7% of the total system energy is spent on data movement

#### Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup>Saugata Ghose<sup>1</sup>Youngsok Kim<sup>2</sup>Rachata Ausavarungnirun<sup>1</sup>Eric Shiu<sup>3</sup>Rahul Thakur<sup>3</sup>Daehyun Kim<sup>4,3</sup>Aki Kuusela<sup>3</sup>Allan Knies<sup>3</sup>Parthasarathy Ranganathan<sup>3</sup>Onur Mutlu<sup>5,1</sup>93

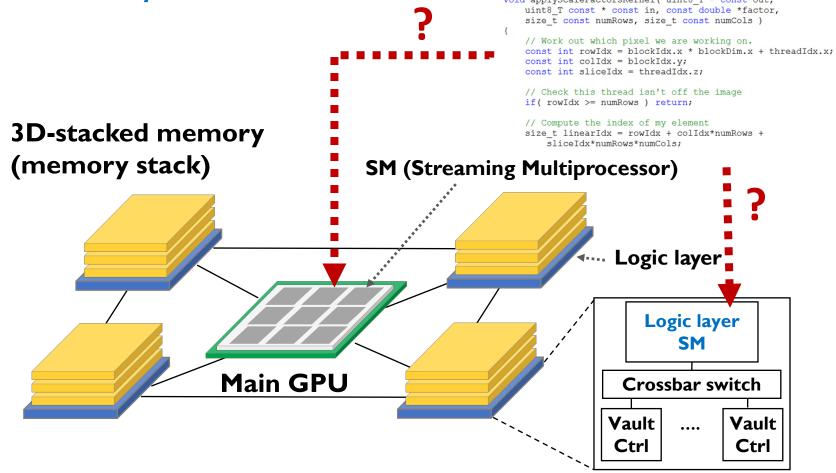

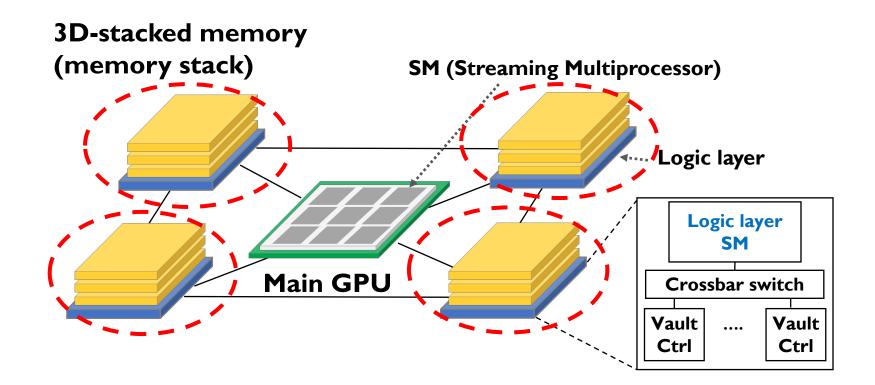

#### **Truly Distributed GPU Processing with PIM?**

# Accelerating GPU Execution with PIM (I)

Kevin Hsieh, Eiman Ebrahimi, Gwangsun Kim, Niladrish Chatterjee, Mike O'Connor, Nandita Vijaykumar, Onur Mutlu, and Stephen W. Keckler, "Transparent Offloading and Mapping (TOM): Enabling Programmer-Transparent Near-Data Processing in GPU Systems" Proceedings of the <u>43rd International Symposium on Computer</u>

Architecture (ISCA), Seoul, South Korea, June 2016.

[Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

#### Transparent Offloading and Mapping (TOM): Enabling Programmer-Transparent Near-Data Processing in GPU Systems

Kevin Hsieh<sup>‡</sup> Eiman Ebrahimi<sup>†</sup> Gwangsun Kim<sup>\*</sup> Niladrish Chatterjee<sup>†</sup> Mike O'Connor<sup>†</sup> Nandita Vijaykumar<sup>‡</sup> Onur Mutlu<sup>§‡</sup> Stephen W. Keckler<sup>†</sup> <sup>‡</sup>Carnegie Mellon University <sup>†</sup>NVIDIA <sup>\*</sup>KAIST <sup>§</sup>ETH Zürich

# Accelerating GPU Execution with PIM (II)

Ashutosh Pattnaik, Xulong Tang, Adwait Jog, Onur Kayiran, Asit K. Mishra, Mahmut T. Kandemir, <u>Onur Mutlu</u>, and Chita R. Das, <u>"Scheduling Techniques for GPU Architectures with Processing-</u> <u>In-Memory Capabilities"</u>

Proceedings of the <u>25th International Conference on Parallel</u> <u>Architectures and Compilation Techniques</u> (**PACT**), Haifa, Israel, September 2016.

#### Scheduling Techniques for GPU Architectures with Processing-In-Memory Capabilities

Ashutosh Pattnaik<sup>1</sup> Xulong Tang<sup>1</sup> Adwait Jog<sup>2</sup> Onur Kayıran<sup>3</sup> Asit K. Mishra<sup>4</sup> Mahmut T. Kandemir<sup>1</sup> Onur Mutlu<sup>5,6</sup> Chita R. Das<sup>1</sup> <sup>1</sup>Pennsylvania State University <sup>2</sup>College of William and Mary <sup>3</sup>Advanced Micro Devices, Inc. <sup>4</sup>Intel Labs <sup>5</sup>ETH Zürich <sup>6</sup>Carnegie Mellon University

### Accelerating Linked Data Structures

Kevin Hsieh, Samira Khan, Nandita Vijaykumar, Kevin K. Chang, Amirali Boroumand, Saugata Ghose, and Onur Mutlu, <u>"Accelerating Pointer Chasing in 3D-Stacked Memory:</u> <u>Challenges, Mechanisms, Evaluation"</u> *Proceedings of the <u>34th IEEE International Conference on Computer</u> <u>Design</u> (ICCD), Phoenix, AZ, USA, October 2016.*

#### Accelerating Pointer Chasing in 3D-Stacked Memory: Challenges, Mechanisms, Evaluation

Kevin Hsieh<sup>†</sup> Samira Khan<sup>‡</sup> Nandita Vijaykumar<sup>†</sup> Kevin K. Chang<sup>†</sup> Amirali Boroumand<sup>†</sup> Saugata Ghose<sup>†</sup> Onur Mutlu<sup>§†</sup> <sup>†</sup>Carnegie Mellon University <sup>‡</sup>University of Virginia <sup>§</sup>ETH Zürich

### Accelerating Dependent Cache Misses

Milad Hashemi, Khubaib, Eiman Ebrahimi, Onur Mutlu, and Yale N. Patt, "Accelerating Dependent Cache Misses with an Enhanced <u>Memory Controller"</u> *Proceedings of the <u>43rd International Symposium on Computer</u> <i>Architecture (ISCA)*, Seoul, South Korea, June 2016. [Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

### Accelerating Dependent Cache Misses with an Enhanced Memory Controller

Milad Hashemi<sup>\*</sup>, Khubaib<sup>†</sup>, Eiman Ebrahimi<sup>‡</sup>, Onur Mutlu<sup>§</sup>, Yale N. Patt<sup>\*</sup>

\* The University of Texas at Austin <sup>†</sup>Apple <sup>‡</sup>NVIDIA <sup>§</sup>ETH Zürich & Carnegie Mellon University

### Several Questions in 3D-Stacked PIM

- What are the performance and energy benefits of using 3D-stacked memory as a coarse-grained accelerator?

- By changing the entire system

- By performing simple function offloading

What is the minimal processing-in-memory support we can provide?

With minimal changes to system and programming

### PIM-Enabled Instructions

Junwhan Ahn, Sungjoo Yoo, Onur Mutlu, and Kiyoung Choi, "PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture" Proceedings of the <u>42nd International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2015. [Slides (pdf)] [Lightning Session Slides (pdf)]

#### PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture

Junwhan Ahn Sungjoo Yoo Onur Mutlu<sup>†</sup> Kiyoung Choi junwhan@snu.ac.kr, sungjoo.yoo@gmail.com, onur@cmu.edu, kchoi@snu.ac.kr Seoul National University <sup>†</sup>Carnegie Mellon University

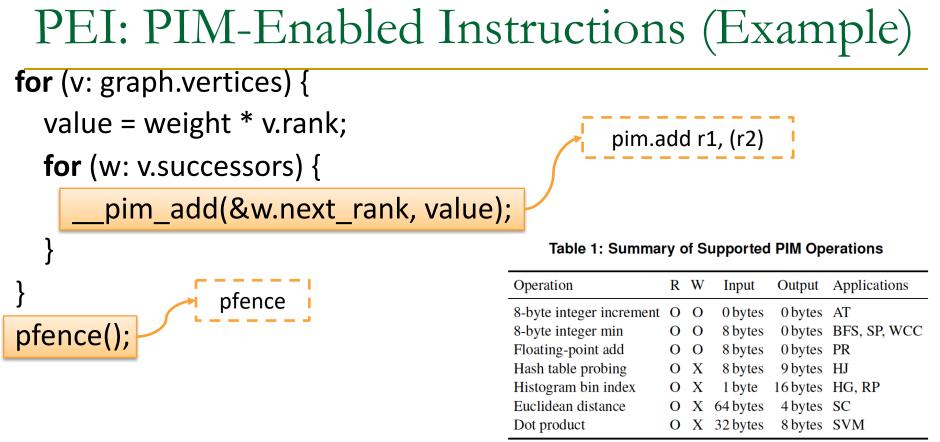

# PEI: PIM-Enabled Instructions (Ideas)

- Goal: Develop mechanisms to get the most out of near-data processing with minimal cost, minimal changes to the system, no changes to the programming model

- Key Idea 1: Expose each PIM operation as a cache-coherent, virtually-addressed host processor instruction (called PEI) that operates on only a single cache block

- e.g., \_\_pim\_add(&w.next\_rank, value)  $\rightarrow$  pim.add r1, (r2)

- No changes sequential execution/programming model

- No changes to virtual memory

- Minimal changes to cache coherence

- No need for data mapping: Each PEI restricted to a single memory module

- Key Idea 2: Dynamically decide where to execute a PEI (i.e., the host processor or PIM accelerator) based on simple locality characteristics and simple hardware predictors

- Execute each operation at the location that provides the best performance

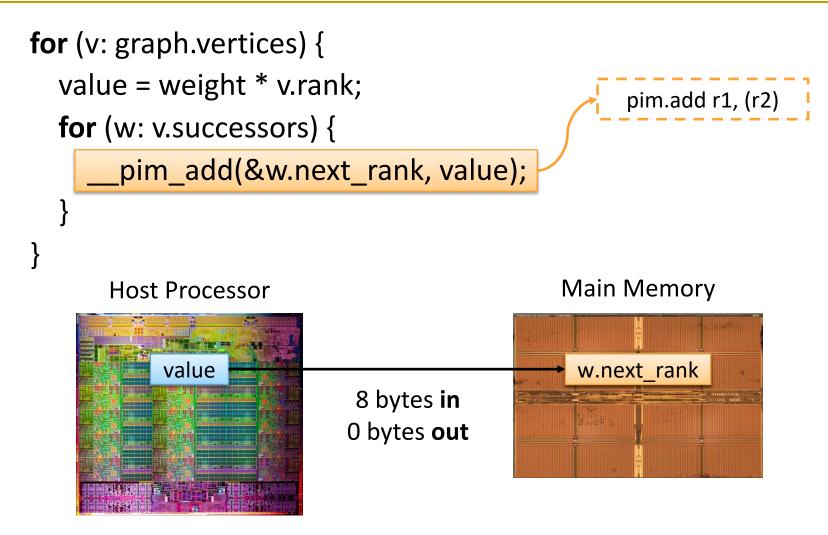

#### Simple PIM Operations as ISA Extensions (II)

```

for (v: graph.vertices) {

value = weight * v.rank;

for (w: v.successors) {

w.next rank += value;

Main Memory

Host Processor

w.next rank

w.next rank

64 bytes in

64 bytes out

```

**Conventional Architecture**

#### Simple PIM Operations as ISA Extensions (III)

**In-Memory Addition**

#### Always Executing in Memory? Not A Good Idea

- Executed either in memory or in the processor: dynamic decision

- Low-cost locality monitoring for a single instruction

- Cache-coherent, virtually-addressed, single cache block only

- Atomic between different PEIs

- Not atomic with normal instructions (use pfence for ordering)

SAFARI

- Key to practicality: single-cache-block restriction

- Each PEI can access *at most one last-level cache block*

- Similar restrictions exist in atomic instructions

- Benefits

- **Localization**: each PEI is bounded to one memory module

- Interoperability: easier support for cache coherence and virtual memory

- Simplified locality monitoring: data locality of PEIs can be identified simply by the cache control logic

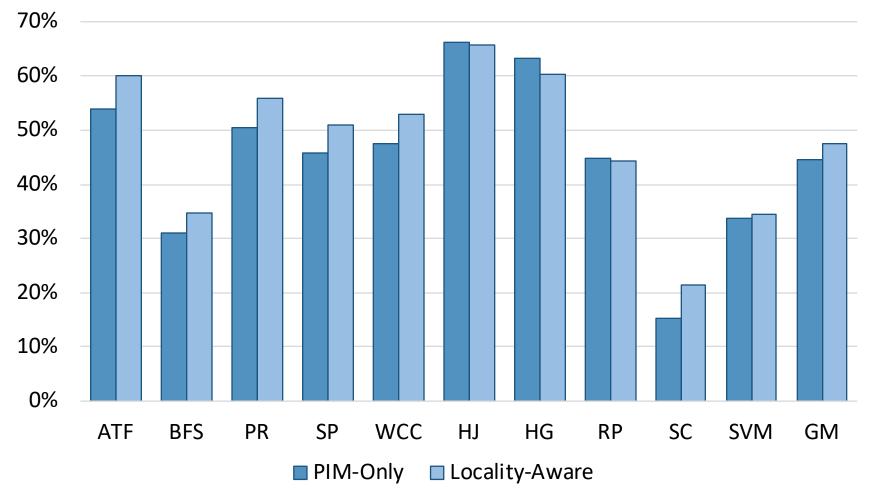

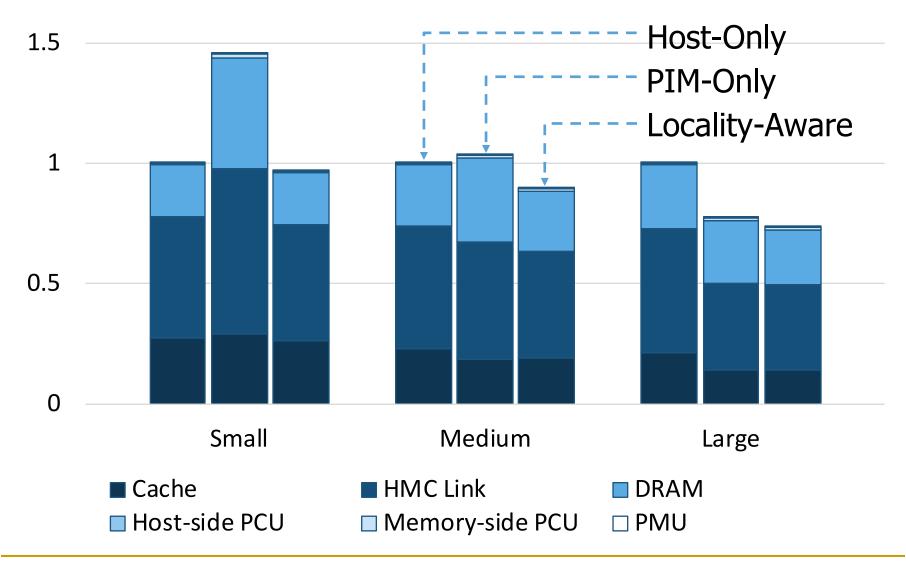

### PEI: Initial Evaluation Results

#### Initial evaluations with 10 emerging data-intensive workloads

- Large-scale graph processing

- In-memory data analytics

- Machine learning and data mining

- Three input sets (small, medium, large) for each workload to analyze the impact of data locality

Table 2: Baseline Simulation Configuration

| Component                          | Configuration                                     |

|------------------------------------|---------------------------------------------------|

| Core                               | 16 out-of-order cores, 4 GHz, 4-issue             |

| L1 I/D-Cache                       | Private, 32 KB, 4/8-way, 64 B blocks, 16 MSHRs    |

| L2 Cache                           | Private, 256 KB, 8-way, 64 B blocks, 16 MSHRs     |

| L3 Cache                           | Shared, 16 MB, 16-way, 64 B blocks, 64 MSHRs      |

| <b>On-Chip Network</b>             | Crossbar, 2 GHz, 144-bit links                    |

| Main Memory                        | 32 GB, 8 HMCs, daisy-chain (80 GB/s full-duplex)  |

| HMC                                | 4 GB, 16 vaults, 256 DRAM banks [20]              |

| – DRAM                             | FR-FCFS, tCL = tRCD = tRP = $13.75$ ns [27]       |

| <ul> <li>Vertical Links</li> </ul> | 64 TSVs per vault with 2 Gb/s signaling rate [23] |

Pin-based cycle-level x86-64 simulation

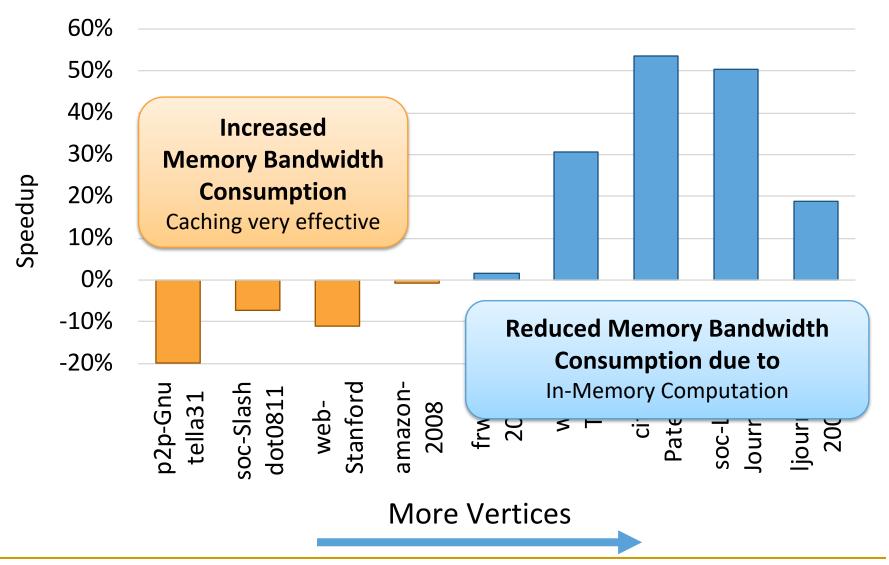

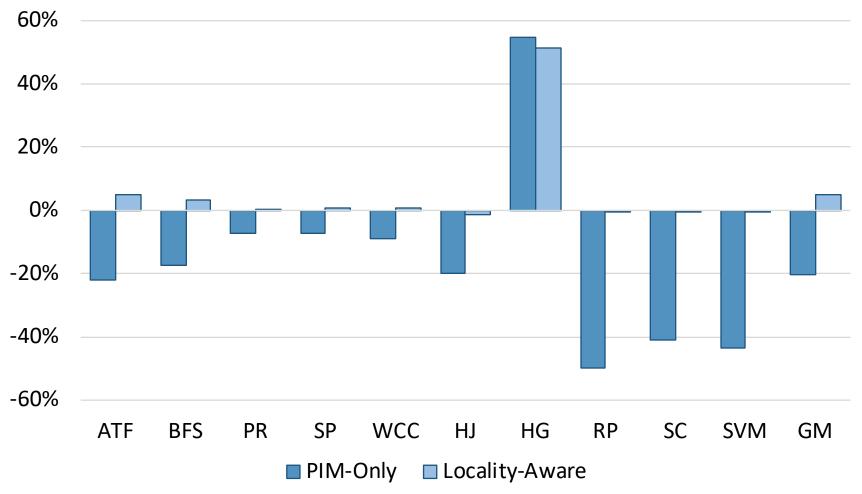

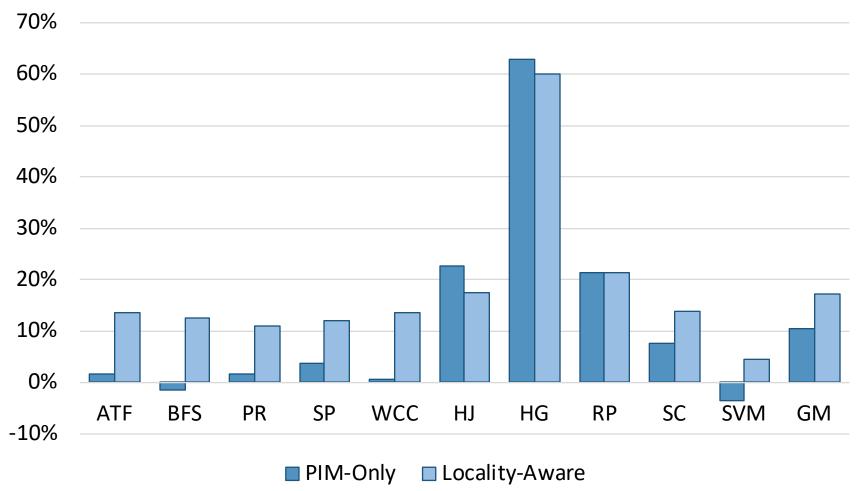

Performance Improvement and Energy Reduction:

- 47% average speedup with large input data sets

- 32% speedup with small input data sets

- 25% avg. energy reduction in a single node with large input data sets

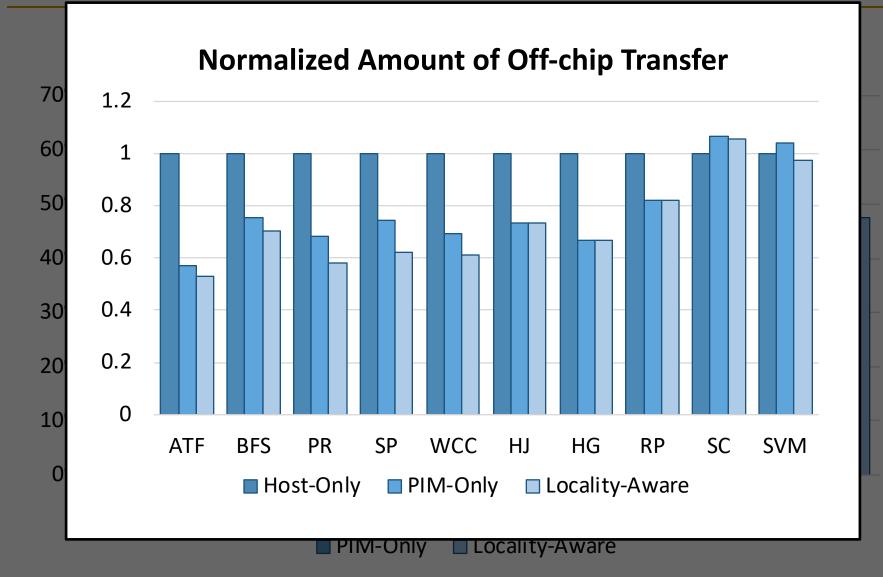

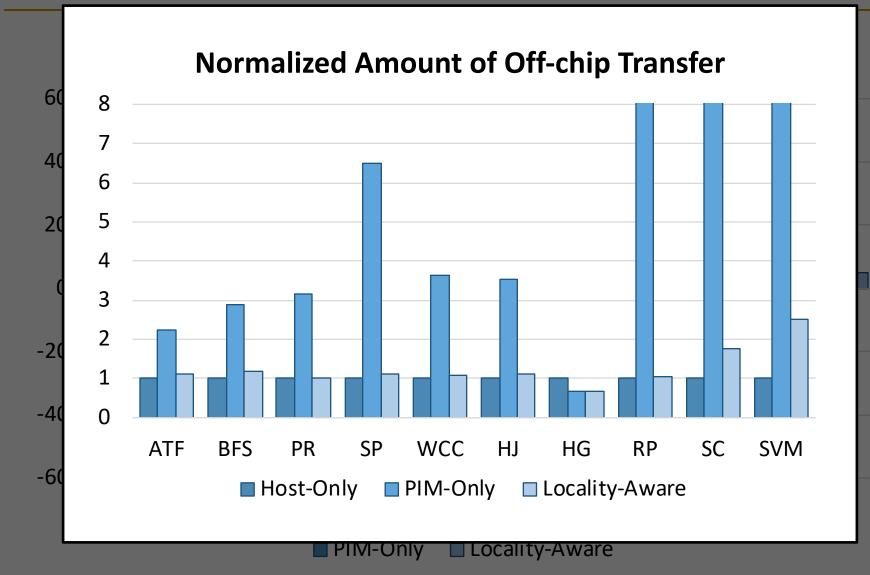

### Evaluated Data-Intensive Applications

- Ten emerging data-intensive workloads

- Large-scale graph processing

- Average teenage follower, BFS, PageRank, single-source shortest path, weakly connected components

- In-memory data analytics

- Hash join, histogram, radix partitioning

- Machine learning and data mining

- Streamcluster, SVM-RFE

- Three input sets (small, medium, large) for each workload to show the impact of data locality

### PEI Performance Delta: Large Data Sets

### PEI Performance: Large Data Sets

### PEI Performance Delta: Small Data Sets

### PEI Performance: Small Data Sets

### PEI Performance Delta: Medium Data Sets

#### (Medium Inputs, Baseline: Host-Only)

### PEI Energy Consumption

### PEI: Advantages & Disadvantages

#### Advantages

- + Simple and low cost approach to PIM

- + No changes to programming model, virtual memory

- + Dynamically decides where to execute an instruction

#### Disadvantages

- Does not take full advantage of PIM potential

- Single cache block restriction is limiting

### Simpler PIM: PIM-Enabled Instructions

Junwhan Ahn, Sungjoo Yoo, Onur Mutlu, and Kiyoung Choi, "PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture" Proceedings of the <u>42nd International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2015. [Slides (pdf)] [Lightning Session Slides (pdf)]

#### PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture

Junwhan Ahn Sungjoo Yoo Onur Mutlu<sup>†</sup> Kiyoung Choi junwhan@snu.ac.kr, sungjoo.yoo@gmail.com, onur@cmu.edu, kchoi@snu.ac.kr Seoul National University <sup>†</sup>Carnegie Mellon University

### Automatic Code and Data Mapping

Kevin Hsieh, Eiman Ebrahimi, Gwangsun Kim, Niladrish Chatterjee, Mike O'Connor, Nandita Vijaykumar, Onur Mutlu, and Stephen W. Keckler, <u>"Transparent Offloading and Mapping (TOM): Enabling</u> <u>Programmer-Transparent Near-Data Processing in GPU</u> <u>Systems"</u> *Proceedings of the <u>43rd International Symposium on Computer</u>*

Architecture (ISCA), Seoul, South Korea, June 2016.

[Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

#### Transparent Offloading and Mapping (TOM): Enabling Programmer-Transparent Near-Data Processing in GPU Systems

Kevin Hsieh<sup>‡</sup> Eiman Ebrahimi<sup>†</sup> Gwangsun Kim<sup>\*</sup> Niladrish Chatterjee<sup>†</sup> Mike O'Connor<sup>†</sup> Nandita Vijaykumar<sup>‡</sup> Onur Mutlu<sup>§‡</sup> Stephen W. Keckler<sup>†</sup> <sup>‡</sup>Carnegie Mellon University <sup>†</sup>NVIDIA <sup>\*</sup>KAIST <sup>§</sup>ETH Zürich

### Automatic Offloading of Critical Code

Milad Hashemi, Khubaib, Eiman Ebrahimi, Onur Mutlu, and Yale N. Patt, "Accelerating Dependent Cache Misses with an Enhanced <u>Memory Controller"</u> *Proceedings of the <u>43rd International Symposium on Computer</u> <i>Architecture (ISCA)*, Seoul, South Korea, June 2016. [Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

### Accelerating Dependent Cache Misses with an Enhanced Memory Controller

Milad Hashemi<sup>\*</sup>, Khubaib<sup>†</sup>, Eiman Ebrahimi<sup>‡</sup>, Onur Mutlu<sup>§</sup>, Yale N. Patt<sup>\*</sup>

\* The University of Texas at Austin <sup>†</sup>Apple <sup>‡</sup>NVIDIA <sup>§</sup>ETH Zürich & Carnegie Mellon University

### Automatic Offloading of Prefetch Mechanisms

Milad Hashemi, Onur Mutlu, and Yale N. Patt, <u>"Continuous Runahead: Transparent Hardware Acceleration for</u> <u>Memory Intensive Workloads"</u> *Proceedings of the <u>49th International Symposium on</u> <u>Microarchitecture</u> (<i>MICRO*), Taipei, Taiwan, October 2016. [Slides (pptx) (pdf)] [Lightning Session Slides (pdf)] [Poster (pptx) (pdf)]

#### Continuous Runahead: Transparent Hardware Acceleration for Memory Intensive Workloads

Milad Hashemi<sup>\*</sup>, Onur Mutlu<sup>§</sup>, Yale N. Patt<sup>\*</sup>

\* The University of Texas at Austin §ETH Zürich

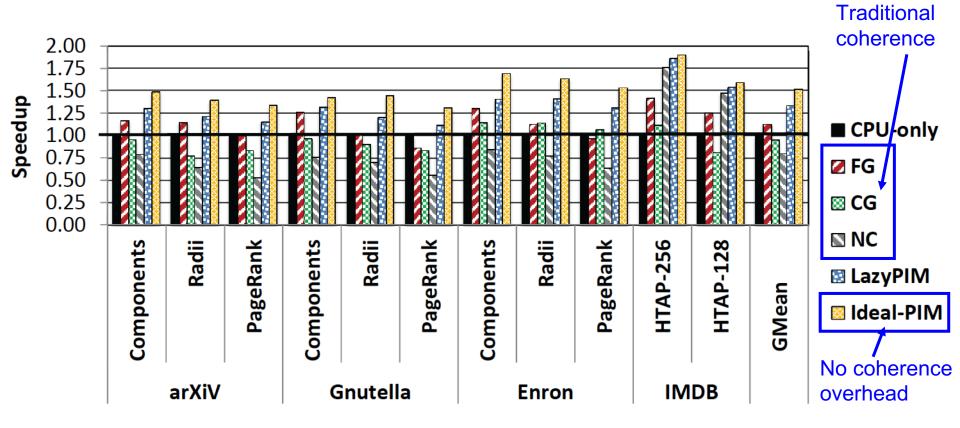

### Efficient Automatic Data Coherence Support

Amirali Boroumand, Saugata Ghose, Minesh Patel, Hasan Hassan, Brandon Lucia, Kevin Hsieh, Krishna T. Malladi, Hongzhong Zheng, and Onur Mutlu,

"LazyPIM: An Efficient Cache Coherence Mechanism for Processing-in-Memory"

*<u>IEEE Computer Architecture Letters</u> (CAL)*, June 2016.

#### LazyPIM: An Efficient Cache Coherence Mechanism for Processing-in-Memory

Amirali Boroumand<sup>†</sup>, Saugata Ghose<sup>†</sup>, Minesh Patel<sup>†</sup>, Hasan Hassan<sup>†§</sup>, Brandon Lucia<sup>†</sup>, Kevin Hsieh<sup>†</sup>, Krishna T. Malladi<sup>\*</sup>, Hongzhong Zheng<sup>\*</sup>, and Onur Mutlu<sup>‡†</sup> <sup>†</sup>Carnegie Mellon University \*Samsung Semiconductor, Inc. <sup>§</sup>TOBB ETÜ <sup>‡</sup>ETH Zürich

### Efficient Automatic Data Coherence Support

Amirali Boroumand, Saugata Ghose, Minesh Patel, Hasan Hassan, Brandon Lucia, Kevin Hsieh, Krishna T. Malladi, Hongzhong Zheng, and <u>Onur Mutlu</u>,

"CoNDA: Efficient Cache Coherence Support for Near-Data Accelerators" Proceedings of the <u>46th International Symposium on Computer</u>

<u>Architecture</u> (**ISCA**), Phoenix, AZ, USA, June 2019.

#### **CoNDA: Efficient Cache Coherence Support** for Near-Data Accelerators

Amirali Boroumand<sup>†</sup> Saugata Ghose<sup>†</sup> Minesh Patel<sup>\*</sup> Hasan Hassan<sup>\*</sup> Brandon Lucia<sup>†</sup> Rachata Ausavarungnirun<sup>†‡</sup> Kevin Hsieh<sup>†</sup> Nastaran Hajinazar<sup>¢†</sup> Krishna T. Malladi<sup>§</sup> Hongzhong Zheng<sup>§</sup> Onur Mutlu<sup>\*†</sup> <sup>†</sup>Carnegie Mellon University <sup>\*</sup>ETH Zürich <sup>‡</sup>KMUTNB

\*Simon Fraser University

\*ETH Zürich <sup>‡</sup>KMUTNB <sup>§</sup>Samsung Semiconductor, Inc.

Challenge and Opportunity for Future

Fundamentally **Energy-Efficient** (Data-Centric) **Computing Architectures**  Challenge and Opportunity for Future

Fundamentally **High-Performance** (Data-Centric) **Computing Architectures**  Challenge and Opportunity for Future

# Computing Architectures with

## Minimal Data Movement

### Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Minimally Changing Memory Chips

- Exploiting 3D-Stacked Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

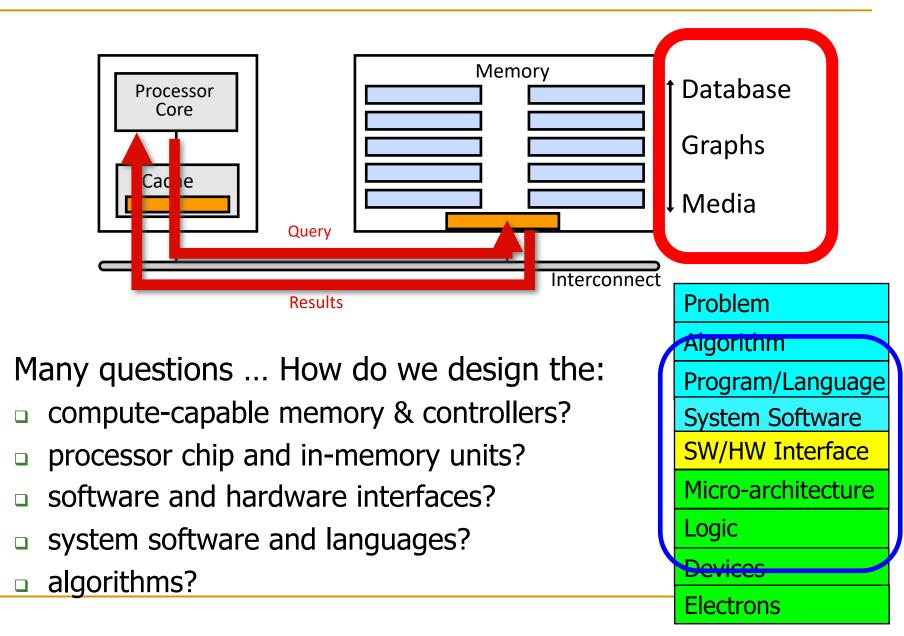

### Eliminating the Adoption Barriers

# How to Enable Adoption of Processing in Memory

### Barriers to Adoption of PIM

1. Functionality of and applications & software for PIM

- 2. Ease of programming (interfaces and compiler/HW support)

- 3. System support: coherence & virtual memory

4. Runtime and compilation systems for adaptive scheduling, data mapping, access/sharing control

5. Infrastructures to assess benefits and feasibility

#### All can be solved with change of mindset

### We Need to Revisit the Entire Stack

| Problem            |  |

|--------------------|--|

| Aigorithm          |  |

| Program/Language   |  |

| System Software    |  |

| SW/HW Interface    |  |

| Micro-architecture |  |

| Logic              |  |

| Devices            |  |

| Electrons          |  |

#### We can get there step by step

### PIM Review and Open Problems

### Processing Data Where It Makes Sense: Enabling In-Memory Computation

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>b,c</sup>

<sup>a</sup>ETH Zürich <sup>b</sup>Carnegie Mellon University <sup>c</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "Processing Data Where It Makes Sense: Enabling In-Memory Computation" Invited paper in Microprocessors and Microsystems (MICPRO), June 2019. [arXiv version]

https://arxiv.org/pdf/1903.03988.pdf

ΔΓΔΠΙ

### Key Challenge 1: Code Mapping

• Challenge 1: Which operations should be executed in memory vs. in CPU?

### Key Challenge 2: Data Mapping

• Challenge 2: How should data be mapped to different 3D memory stacks?

### How to Do the Code and Data Mapping?

Kevin Hsieh, Eiman Ebrahimi, Gwangsun Kim, Niladrish Chatterjee, Mike O'Connor, Nandita Vijaykumar, Onur Mutlu, and Stephen W. Keckler, <u>"Transparent Offloading and Mapping (TOM): Enabling</u> <u>Programmer-Transparent Near-Data Processing in GPU</u> <u>Systems"</u> *Proceedings of the <u>43rd International Symposium on Computer</u>*

Architecture (ISCA), Seoul, South Korea, June 2016.

[Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

#### Transparent Offloading and Mapping (TOM): Enabling Programmer-Transparent Near-Data Processing in GPU Systems

Kevin Hsieh<sup>‡</sup> Eiman Ebrahimi<sup>†</sup> Gwangsun Kim<sup>\*</sup> Niladrish Chatterjee<sup>†</sup> Mike O'Connor<sup>†</sup> Nandita Vijaykumar<sup>‡</sup> Onur Mutlu<sup>§‡</sup> Stephen W. Keckler<sup>†</sup> <sup>‡</sup>Carnegie Mellon University <sup>†</sup>NVIDIA <sup>\*</sup>KAIST <sup>§</sup>ETH Zürich

### How to Schedule Code?

Ashutosh Pattnaik, Xulong Tang, Adwait Jog, Onur Kayiran, Asit K. Mishra, Mahmut T. Kandemir, <u>Onur Mutlu</u>, and Chita R. Das, <u>"Scheduling Techniques for GPU Architectures with Processing-</u> <u>In-Memory Capabilities"</u>

Proceedings of the <u>25th International Conference on Parallel</u> <u>Architectures and Compilation Techniques</u> (**PACT**), Haifa, Israel, September 2016.

### Scheduling Techniques for GPU Architectures with Processing-In-Memory Capabilities

Ashutosh Pattnaik<sup>1</sup> Xulong Tang<sup>1</sup> Adwait Jog<sup>2</sup> Onur Kayıran<sup>3</sup> Asit K. Mishra<sup>4</sup> Mahmut T. Kandemir<sup>1</sup> Onur Mutlu<sup>5,6</sup> Chita R. Das<sup>1</sup> <sup>1</sup>Pennsylvania State University <sup>2</sup>College of William and Mary <sup>3</sup>Advanced Micro Devices, Inc. <sup>4</sup>Intel Labs <sup>5</sup>ETH Zürich <sup>6</sup>Carnegie Mellon University

### Challenge: Coherence for Hybrid CPU-PIM Apps

### How to Maintain Coherence? (I)

Amirali Boroumand, Saugata Ghose, Minesh Patel, Hasan Hassan, Brandon Lucia, Kevin Hsieh, Krishna T. Malladi, Hongzhong Zheng, and Onur Mutlu,

"LazyPIM: An Efficient Cache Coherence Mechanism for Processing-in-Memory" IEEE Computer Architecture Letters (CAL), June 2016.

#### LazyPIM: An Efficient Cache Coherence Mechanism for Processing-in-Memory

Amirali Boroumand<sup>†</sup>, Saugata Ghose<sup>†</sup>, Minesh Patel<sup>†</sup>, Hasan Hassan<sup>†§</sup>, Brandon Lucia<sup>†</sup>, Kevin Hsieh<sup>†</sup>, Krishna T. Malladi<sup>\*</sup>, Hongzhong Zheng<sup>\*</sup>, and Onur Mutlu<sup>‡†</sup> <sup>†</sup>Carnegie Mellon University \*Samsung Semiconductor, Inc. <sup>§</sup>TOBB ETÜ <sup>‡</sup>ETH Zürich

### How to Maintain Coherence? (II)

Amirali Boroumand, Saugata Ghose, Minesh Patel, Hasan Hassan, Brandon Lucia, Kevin Hsieh, Krishna T. Malladi, Hongzhong Zheng, and <u>Onur Mutlu</u>,

"CoNDA: Efficient Cache Coherence Support for Near-Data Accelerators" Proceedings of the <u>46th International Symposium on Computer</u>

<u>Architecture</u> (**ISCA**), Phoenix, AZ, USA, June 2019.

#### **CoNDA: Efficient Cache Coherence Support** for Near-Data Accelerators

Amirali Boroumand<sup>†</sup> Saugata Ghose<sup>†</sup> Minesh Patel<sup>\*</sup> Hasan Hassan<sup>\*</sup> Brandon Lucia<sup>†</sup> Rachata Ausavarungnirun<sup>†‡</sup> Kevin Hsieh<sup>†</sup> Nastaran Hajinazar<sup>°†</sup> Krishna T. Malladi<sup>§</sup> Hongzhong Zheng<sup>§</sup> Onur Mutlu<sup>\*†</sup> <sup>†</sup>Carnegie Mellon University <sup>\*</sup>ETH Zürich <sup>‡</sup>KMUTNB

\*Simon Fraser University

\*ETH Zürich <sup>‡</sup>KMUTNB <sup>§</sup>Samsung Semiconductor, Inc.

### How to Support Virtual Memory?

Kevin Hsieh, Samira Khan, Nandita Vijaykumar, Kevin K. Chang, Amirali Boroumand, Saugata Ghose, and Onur Mutlu, <u>"Accelerating Pointer Chasing in 3D-Stacked Memory:</u> <u>Challenges, Mechanisms, Evaluation"</u> *Proceedings of the <u>34th IEEE International Conference on Computer</u> <u>Design</u> (ICCD), Phoenix, AZ, USA, October 2016.*

### Accelerating Pointer Chasing in 3D-Stacked Memory: Challenges, Mechanisms, Evaluation

Kevin Hsieh<sup>†</sup> Samira Khan<sup>‡</sup> Nandita Vijaykumar<sup>†</sup> Kevin K. Chang<sup>†</sup> Amirali Boroumand<sup>†</sup> Saugata Ghose<sup>†</sup> Onur Mutlu<sup>§†</sup> <sup>†</sup>Carnegie Mellon University <sup>‡</sup>University of Virginia <sup>§</sup>ETH Zürich

### How to Design Data Structures for PIM?

Zhiyu Liu, Irina Calciu, Maurice Herlihy, and Onur Mutlu, "Concurrent Data Structures for Near-Memory Computing" Proceedings of the <u>29th ACM Symposium on Parallelism in Algorithms</u> and Architectures (SPAA), Washington, DC, USA, July 2017. [Slides (pptx) (pdf)]

#### **Concurrent Data Structures for Near-Memory Computing**

Zhiyu Liu Computer Science Department Brown University zhiyu\_liu@brown.edu

Maurice Herlihy Computer Science Department Brown University mph@cs.brown.edu Irina Calciu VMware Research Group icalciu@vmware.com

Onur Mutlu Computer Science Department ETH Zürich onur.mutlu@inf.ethz.ch

### Simulation Infrastructures for PIM

- Ramulator extended for PIM

- Flexible and extensible DRAM simulator

- Can model many different memory standards and proposals

- Kim+, "Ramulator: A Flexible and Extensible DRAM Simulator", IEEE CAL 2015.

- <u>https://github.com/CMU-SAFARI/ramulator</u>

### Ramulator: A Fast and Extensible DRAM Simulator

Yoongu Kim<sup>1</sup> Weikun Yang<sup>1,2</sup> Onur Mutlu<sup>1</sup> <sup>1</sup>Carnegie Mellon University <sup>2</sup>Peking University

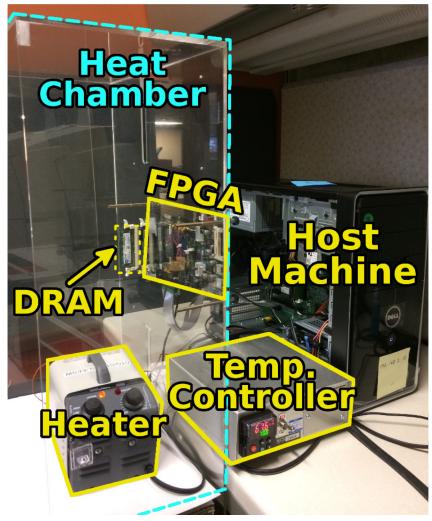

### An FPGA-based Test-bed for PIM?

Hasan Hassan et al., <u>SoftMC: A</u> <u>Flexible and Practical Open-</u> <u>Source Infrastructure for</u> <u>Enabling Experimental DRAM</u> <u>Studies</u> HPCA 2017.

- Flexible

- Easy to Use (C++ API)

- Open-source

github.com/CMU-SAFARI/SoftMC

### Simulation Infrastructures for PIM (in SSDs)

Arash Tavakkol, Juan Gomez-Luna, Mohammad Sadrosadati, Saugata Ghose, and <u>Onur Mutlu</u>,

"MQSim: A Framework for Enabling Realistic Studies of Modern Multi-Queue SSD Devices"

Proceedings of the <u>16th USENIX Conference on File and Storage</u> <u>Technologies</u> (FAST), Oakland, CA, USA, February 2018.

[Slides (pptx) (pdf)]

[Source Code]

#### MQSim: A Framework for Enabling Realistic Studies of Modern Multi-Queue SSD Devices

Arash Tavakkol<sup>†</sup>, Juan Gómez-Luna<sup>†</sup>, Mohammad Sadrosadati<sup>†</sup>, Saugata Ghose<sup>‡</sup>, Onur Mutlu<sup>†‡</sup> <sup>†</sup>*ETH Zürich* <sup>‡</sup>*Carnegie Mellon University*

### New Applications and Use Cases for PIM

Jeremie S. Kim, Damla Senol Cali, Hongyi Xin, Donghyuk Lee, Saugata Ghose, Mohammed Alser, Hasan Hassan, Oguz Ergin, Can Alkan, and Onur Mutlu,

"GRIM-Filter: Fast Seed Location Filtering in DNA Read Mapping Using Processing-in-Memory Technologies"

<u>BMC Genomics</u>, 2018.

Proceedings of the <u>16th Asia Pacific Bioinformatics Conference</u> (**APBC**), Yokohama, Japan, January 2018. <u>arxiv.org Version (pdf)</u>

### GRIM-Filter: Fast seed location filtering in DNA read mapping using processing-in-memory technologies

Jeremie S. Kim<sup>1,6\*</sup>, Damla Senol Cali<sup>1</sup>, Hongyi Xin<sup>2</sup>, Donghyuk Lee<sup>3</sup>, Saugata Ghose<sup>1</sup>, Mohammed Alser<sup>4</sup>, Hasan Hassan<sup>6</sup>, Oguz Ergin<sup>5</sup>, Can Alkan<sup>4\*</sup> and Onur Mutlu<sup>6,1\*</sup>

*From* The Sixteenth Asia Pacific Bioinformatics Conference 2018 Yokohama, Japan. 15-17 January 2018

### Genome Read In-Memory (GRIM) Filter:

Fast Seed Location Filtering in DNA Read Mapping using Processing-in-Memory Technologies

#### Jeremie Kim,

Damla Senol, Hongyi Xin, Donghyuk Lee, Saugata Ghose, Mohammed Alser, Hasan Hassan, Oguz Ergin, Can Alkan, and Onur Mutlu

TOBB UNIVERSITY OF ECONOMICS AND TECHNOLOGY

### Executive Summary

- Genome Read Mapping is a very important problem and is the first step in many types of genomic analysis

Could lead to improved health care, medicine, quality of life

- Could lead to improved health care, medicine, quality of life

- Read mapping is an **approximate string matching** problem

- □ Find the best fit of 100 character strings into a 3 billion character dictionary

- Alignment is currently the best method for determining the similarity between two strings, but is very expensive

- We propose an in-memory processing algorithm GRIM-Filter for accelerating read mapping, by reducing the number of required alignments

- We implement GRIM-Filter using in-memory processing within 3Dstacked memory and show up to 3.7x speedup.

# Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

#### **Amirali Boroumand**

Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, Onur Mutlu

SEOUL NATIONAL UNIVERSITY

## PIM Review and Open Problems

#### Processing Data Where It Makes Sense: Enabling In-Memory Computation

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>b,c</sup>

<sup>a</sup>ETH Zürich <sup>b</sup>Carnegie Mellon University <sup>c</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "Processing Data Where It Makes Sense: Enabling In-Memory Computation" Invited paper in Microprocessors and Microsystems (MICPRO), June 2019. [arXiv version]

https://arxiv.org/pdf/1903.03988.pdf

ΔΓΔΠΙ

Challenge and Opportunity for Future

Fundamentally **Energy-Efficient** (Data-Centric) **Computing Architectures**  Challenge and Opportunity for Future

Fundamentally **High-Performance** (Data-Centric) **Computing Architectures**  Challenge and Opportunity for Future

# Computing Architectures with

# Minimal Data Movement

One Important Takeaway

# Main Memory Needs Intelligent Controllers

# Sub-Agenda: In-Memory Computation

- Major Trends Affecting Main Memory

- The Need for Intelligent Memory Controllers

- Bottom Up: Push from Circuits and Devices

- Top Down: Pull from Systems and Applications

- Processing in Memory: Two Directions

- Minimally Changing Memory Chips

- Exploiting 3D-Stacked Memory

- How to Enable Adoption of Processing in Memory

- Conclusion

# PIM: Concluding Remarks

# Concluding Remarks

- It is time to design principled system architectures to solve the memory problem

- Design complete systems to be balanced, high-performance, and energy-efficient, i.e., data-centric (or memory-centric)

- Enable computation capability inside and close to memory

- This can

- Lead to orders-of-magnitude improvements

- Enable new applications & computing platforms

- **D** Enable better understanding of nature

#### The Future of Processing in Memory is Bright

#### Regardless of challenges

in underlying technology and overlying problems/requirements

Can enable:

- Orders of magnitude improvements

- New applications and computing systems

| Problem            |

|--------------------|

| Aigorithm          |

| Program/Language   |

| System Software    |

| SW/HW Interface    |

| Micro-architecture |

| Logic              |

| Devices            |

| Electrons          |

Yet, we have to

- Think across the stack

- Design enabling systems

### We Need to Revisit the Entire Stack

|  | Problem            |  |

|--|--------------------|--|

|  | Aigorithm          |  |

|  | Program/Language   |  |

|  | System Software    |  |

|  | SW/HW Interface    |  |

|  | Micro-architecture |  |

|  | Logic              |  |

|  | Devices            |  |

|  | Electrons          |  |

#### We can get there step by step

#### SAFARI

### If In Doubt, See Other Doubtful Technologies

- A very "doubtful" emerging technology

- for at least two decades

Proceedings of the IEEE, Sept. 2017

# Error Characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives

This paper reviews the most recent advances in solid-state drive (SSD) error characterization, mitigation, and data recovery techniques to improve both SSD's reliability and lifetime.

By Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu

https://arxiv.org/pdf/1706.08642

## PIM Review and Open Problems

#### Processing Data Where It Makes Sense: Enabling In-Memory Computation

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>b,c</sup>

<sup>a</sup>ETH Zürich <sup>b</sup>Carnegie Mellon University <sup>c</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "Processing Data Where It Makes Sense: Enabling In-Memory Computation" Invited paper in Microprocessors and Microsystems (MICPRO), June 2019. [arXiv version]

https://arxiv.org/pdf/1903.03988.pdf

ΔΓΔΠΙ

# Memory Systems and Memory-Centric Computing Systems Part 3: Computation in Memory

Prof. Onur Mutlu omutlu@gmail.com https://people.inf.ethz.ch/omutlu

7 July 2019 SAMOS Tutorial

**ETH** zürich