## P&S Heterogeneous Systems

#### GPU Performance Considerations

Dr. Juan Gómez Luna

Prof. Onur Mutlu

ETH Zürich

Fall 2022

31 October 2022

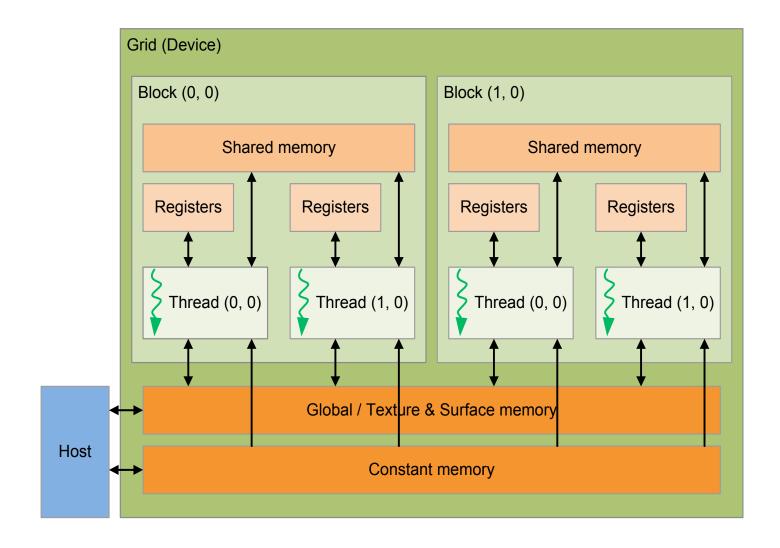

### GPU Memories

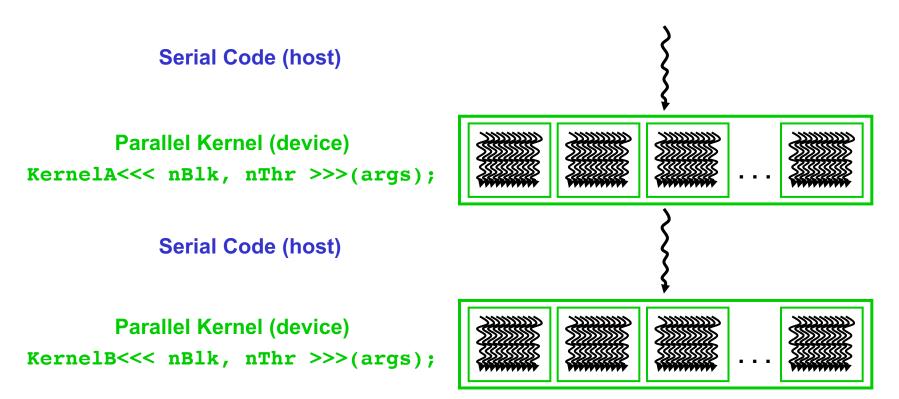

#### Traditional Program Structure

- CPU threads and GPU kernels

- Sequential or modestly parallel sections on CPU

- Massively parallel sections on GPU

## Memory Hierarchy in CUDA Programs

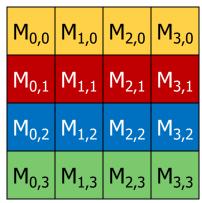

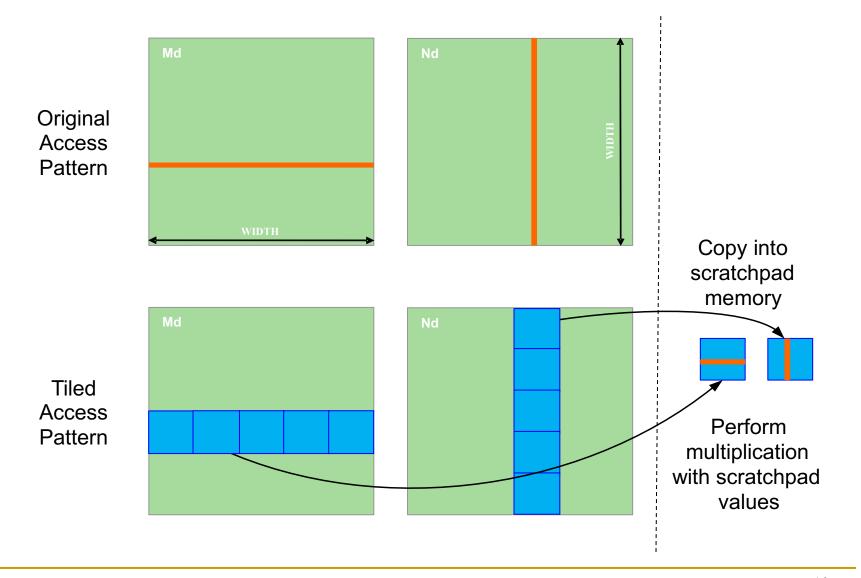

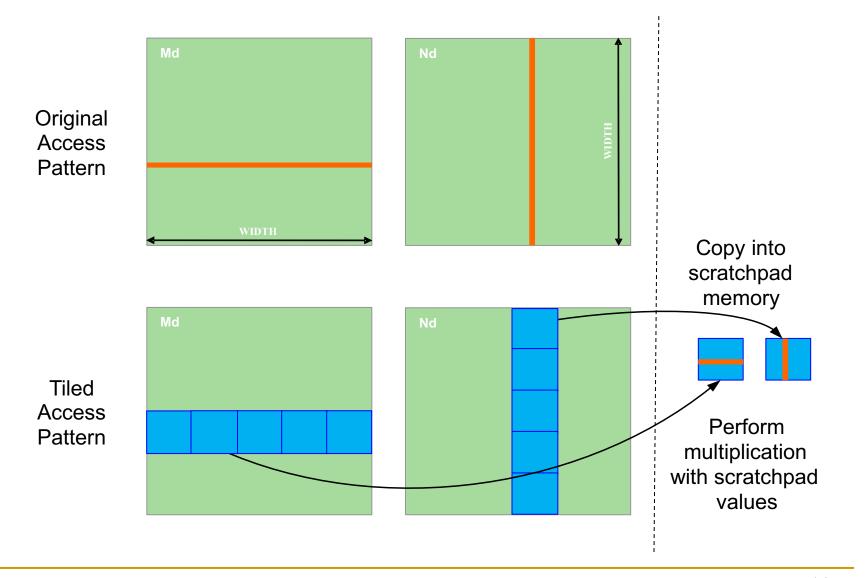

#### Tiled Matrix Multiplication (II)

Tiled implementation operates on submatrices (tiles or blocks) that fit fast memories (cache, scratchpad, RF)

```

\#define A(i,j) matrix A[i * P + j]

\#define B(i,j) matrix B[i * N + j]

\#define C(i,j) matrix C[i * N + j]

for (I = 0; I < M; I += tile dim) {

В

for (J = 0; J < N; J += tile dim) {

Set to zero(&C(I, J)); // Set to zero

for (K = 0; K < P; K += tile dim)

Multiply tiles(\&C(I, J), \&A(I, K), \&B(K, J));

Multiply small submatrices (tiles or

dim

blocks) of size tile dim x tile dim

M

tile dim

```

### Tiled Matrix-Matrix Multiplication (V)

```

__shared__ float A_s[TILE_DIM][TILE_DIM];

Declare arrays in shared memory

__shared__ float B_s[TILE_DIM][TILE_DIM];

unsigned int row = blockIdx.y*blockDim.y + threadIdx.y;

unsigned int col = blockIdx.x*blockDim.x + threadIdx.x;

float sum = 0.0f;

for(unsigned int tile = 0; tile < N/TILE_DIM; ++tile) {</pre>

// Load tile to shared memory

A_s[threadIdx.y][threadIdx.x] = A[row*N + tile*TILE_DIM + threadIdx.x];

B_s[threadIdx.y][threadIdx.x] = B[(tile*TILE_DIM + threadIdx.y)*N + col];

__syncthreads();

Threads wait for each other to finish loading before computing

// Compute with tile

for(unsigned int i = 0; i < TILE_DIM; ++i) {</pre>

sum += A_s[threadIdx.y][i]*B_s[i][threadIdx.x];

__syncthreads();

Threads wait for each other to finish computing before loading

C[row*N + col] = sum;

```

#### Performance Considerations

#### Performance Considerations

- Main bottlenecks

- CPU-GPU data transfers

- Global memory access

- Memory access

- Latency hiding

- Occupancy

- Memory coalescing

- Data reuse

- Shared memory usage

- SIMD (Warp) Utilization: Divergence

- Other considerations

- Atomic operations: Serialization

- Data transfers between CPU and GPU

- Overlap of communication and computation

# Memory Access

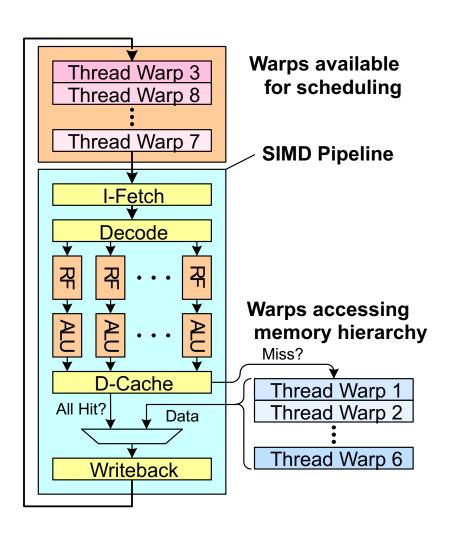

#### Latency Hiding via Warp-Level FGMT

- Warp: A set of threads that execute the same instruction (on different data elements)

- Fine-grained multithreading

- One instruction per thread in pipeline at a time (No interlocking)

- Interleave warp execution to hide latencies

- Register values of all threads stay in register file

- FGMT enables long latency tolerance

- Millions of pixels

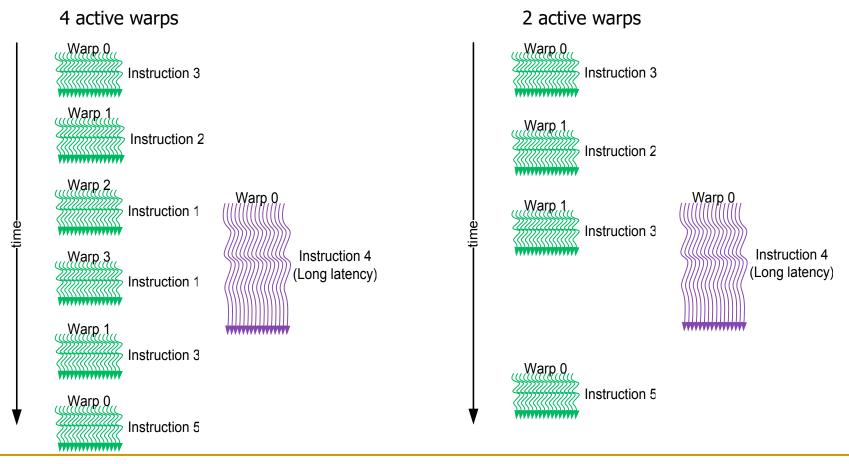

#### Latency Hiding and Occupancy

- FGMT can hide long latency operations (e.g., memory accesses)

- Occupancy: ratio of active warps to the maximum number of warps per GPU core

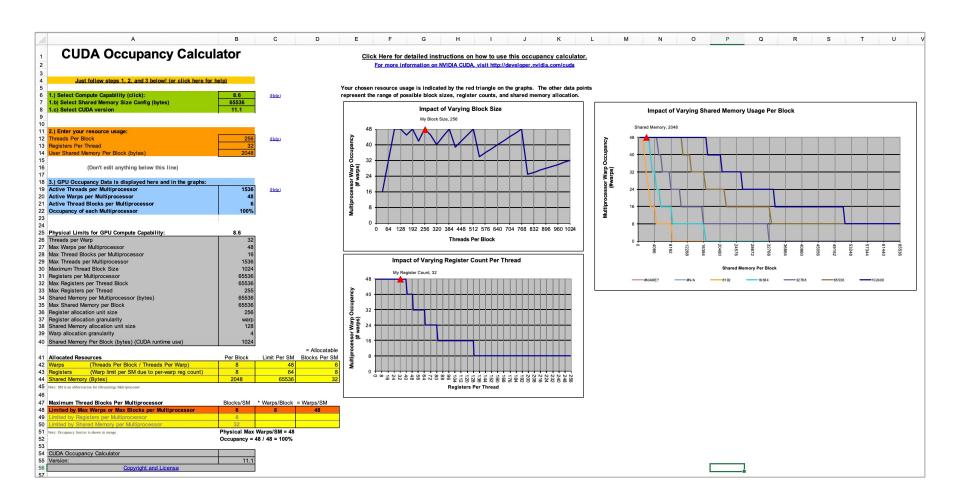

#### Occupancy

- GPU core, a.k.a. SM, resources (typical values)

- Maximum number of warps per SM (64)

- Maximum number of blocks per SM (32)

- Register usage (256KB)

- Shared memory usage (64KB)

- Occupancy calculation

- Number of threads per block (defined by the programmer)

- Registers per thread (known at compile time)

- Shared memory per block (defined by the programmer)

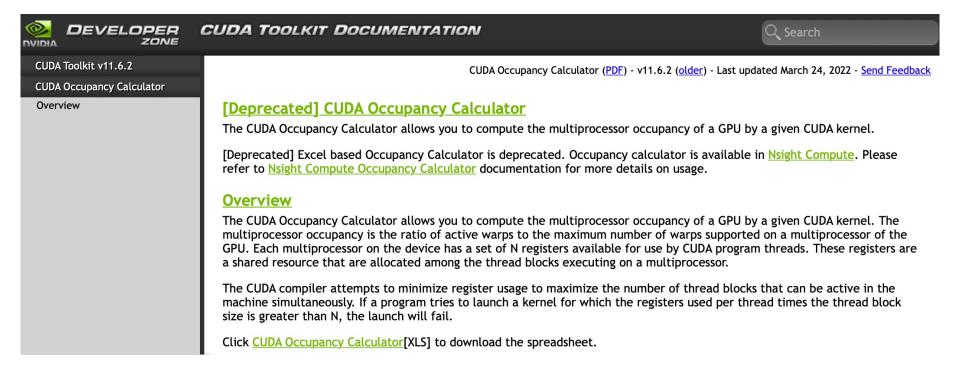

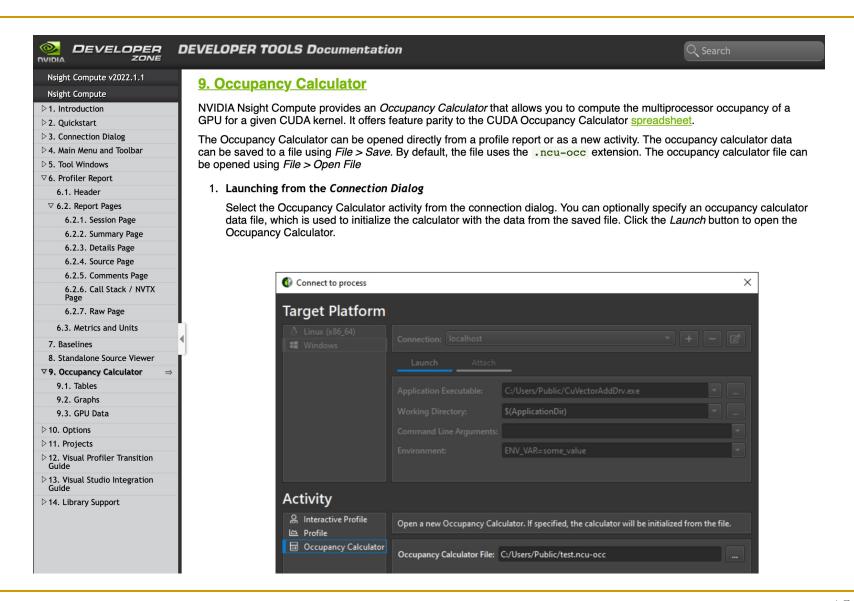

#### CUDA Occupancy Calculator (I)

#### CUDA Occupancy Calculator (II)

#### CUDA Occupancy Calculator (III)

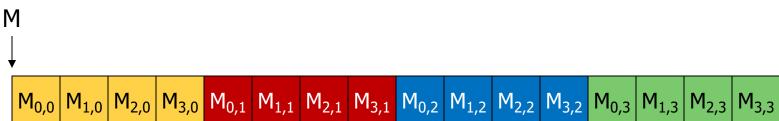

#### Memory Layout of a Matrix in C

Slide credit: Hwu & Kirk

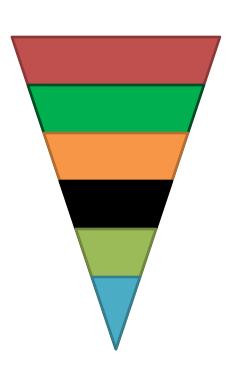

# The DRAM Subsystem The Top-Down View

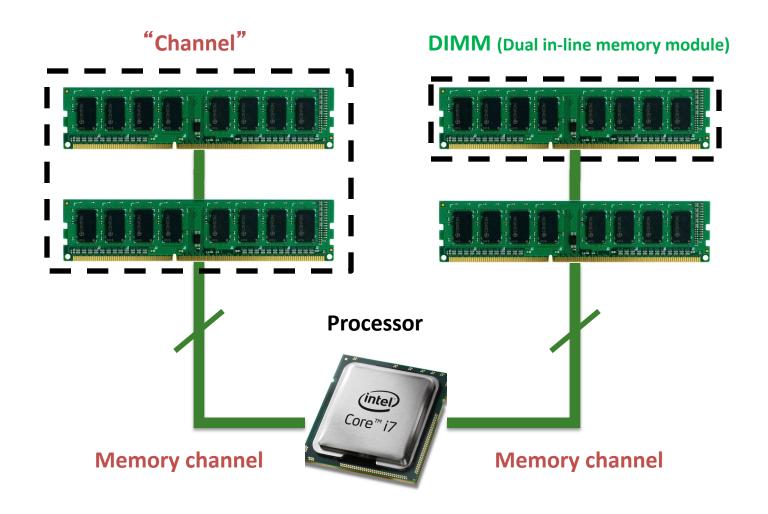

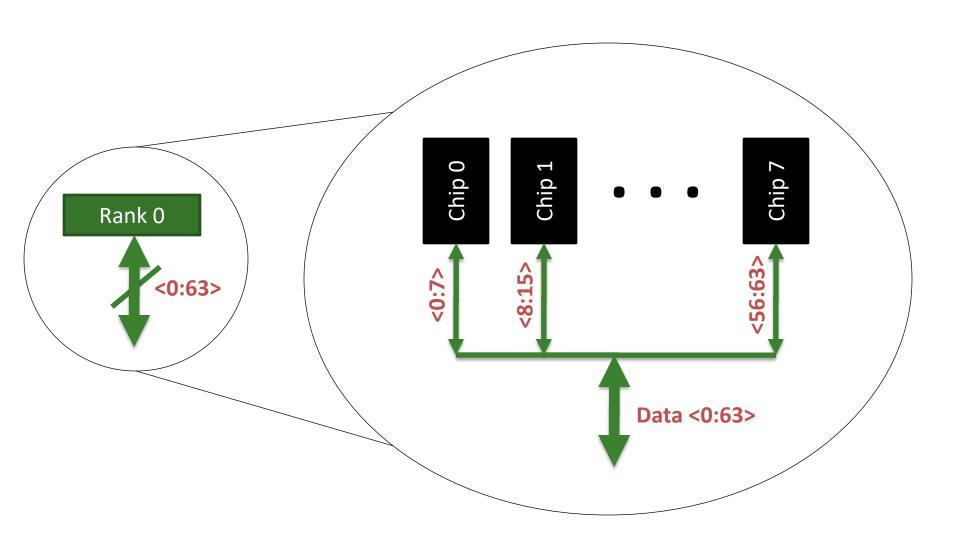

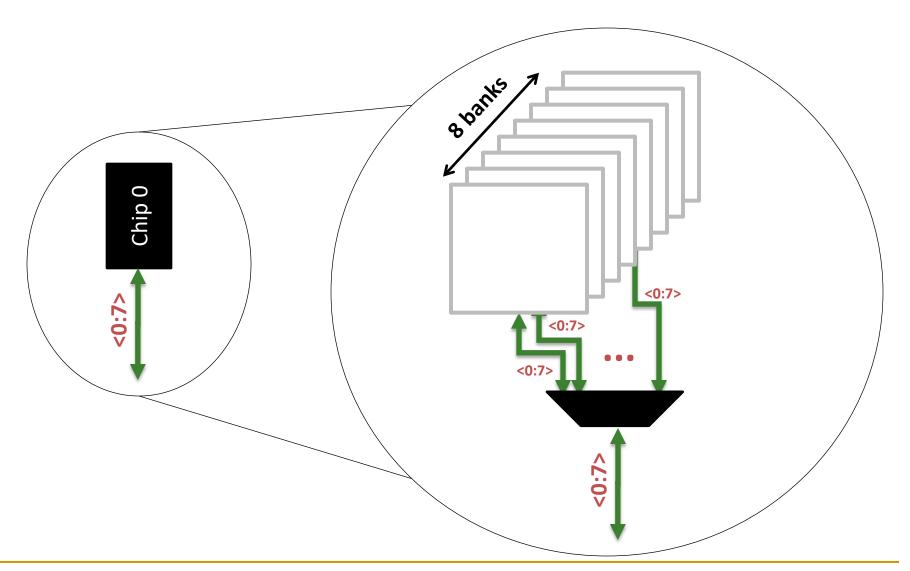

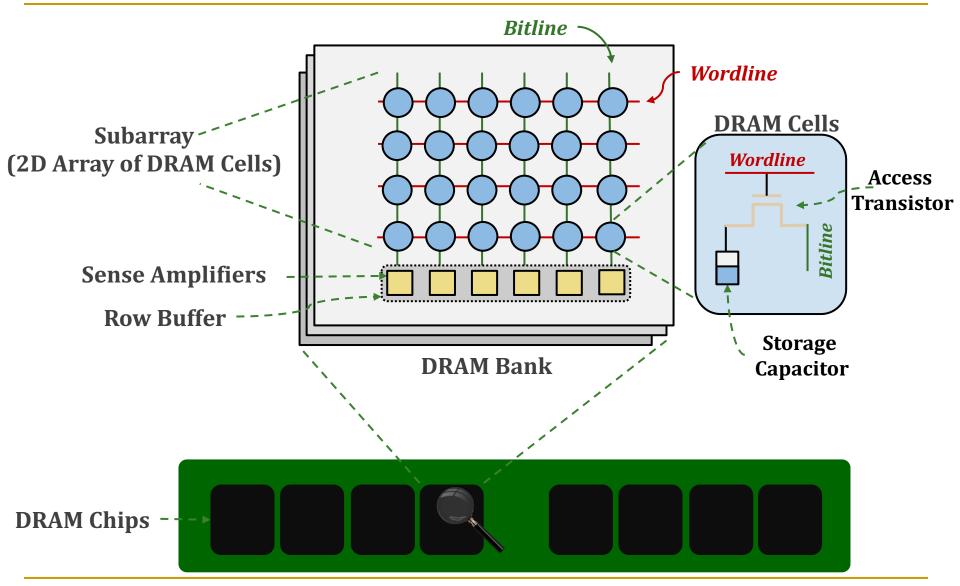

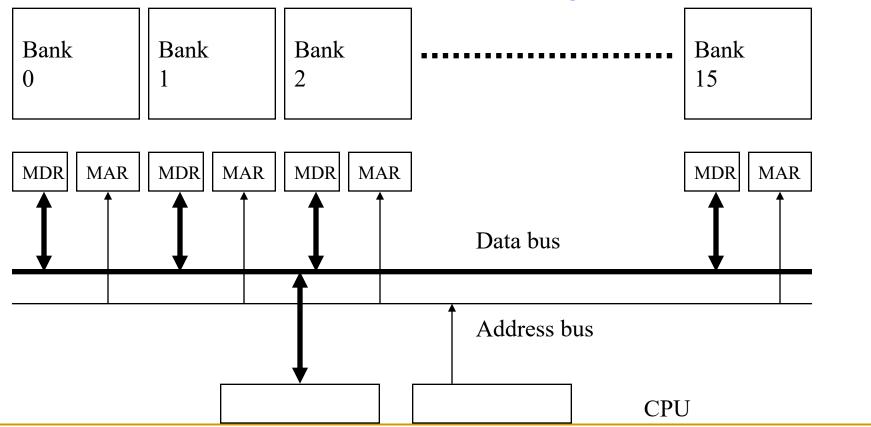

#### DRAM Subsystem Organization

- Channel

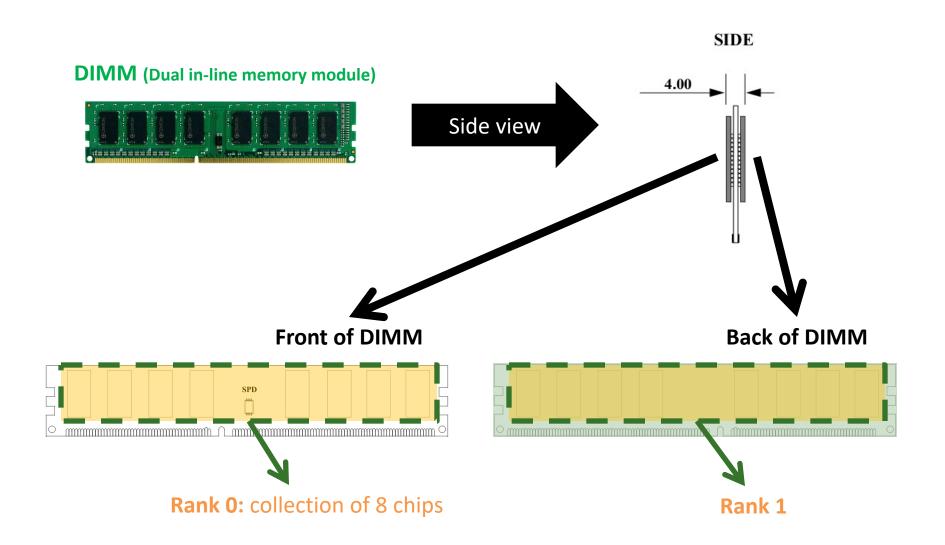

- DIMM

- Rank

- Chip

- Bank

- Row/Column

#### The DRAM Subsystem

#### Breaking down a DIMM (module)

### Breaking down a Rank

## Breaking down a Chip

## Inside a DRAM Chip

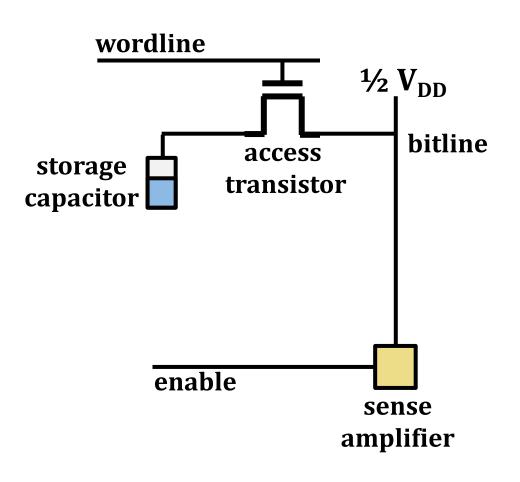

## DRAM Cell Operation

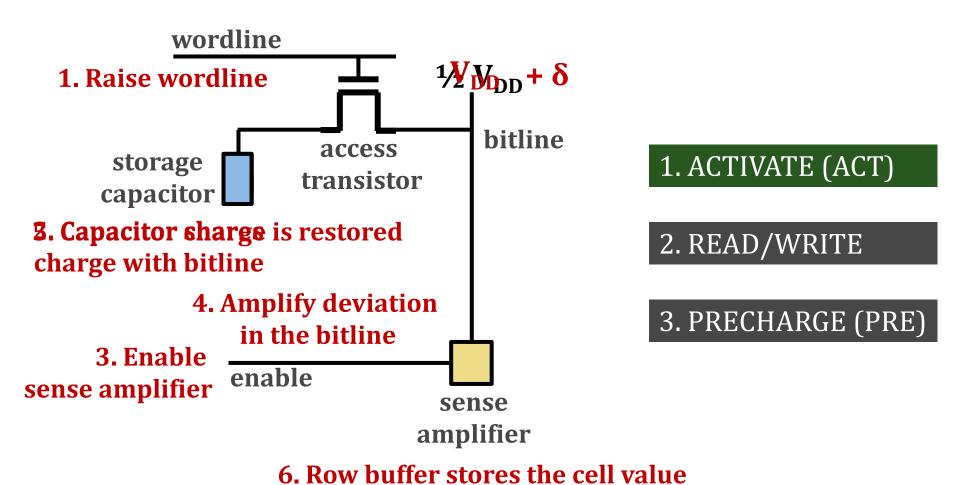

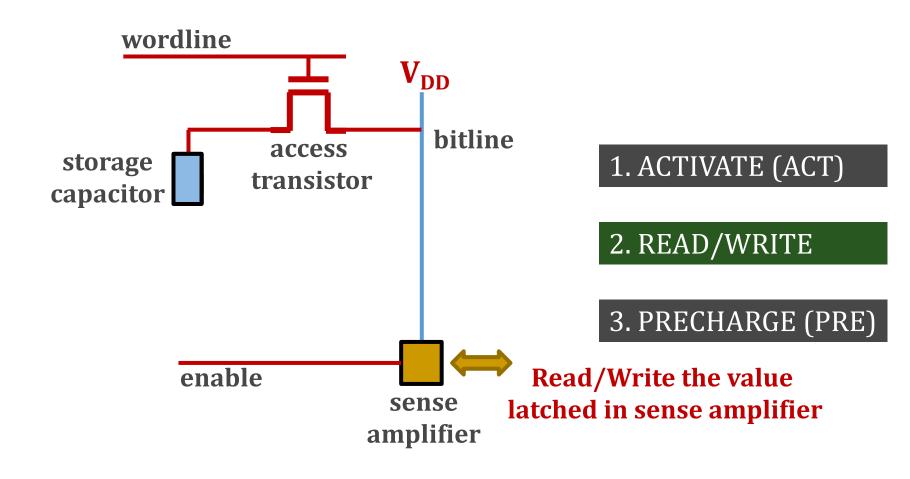

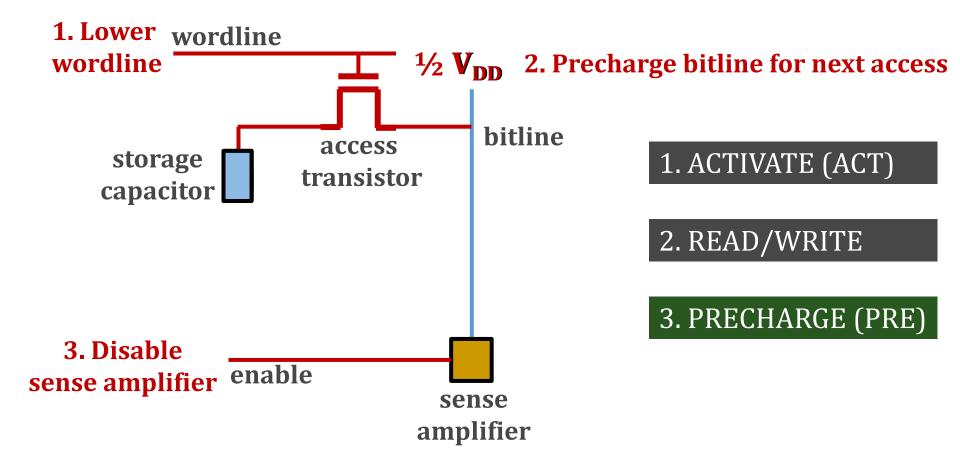

- 1. ACTIVATE (ACT)

- 2. READ/WRITE

- 3. PRECHARGE (PRE)

#### DRAM Cell Operation - ACTIVATE

#### DRAM Cell Operation – READ/WRITE

#### DRAM Cell Operation - PRECHARGE

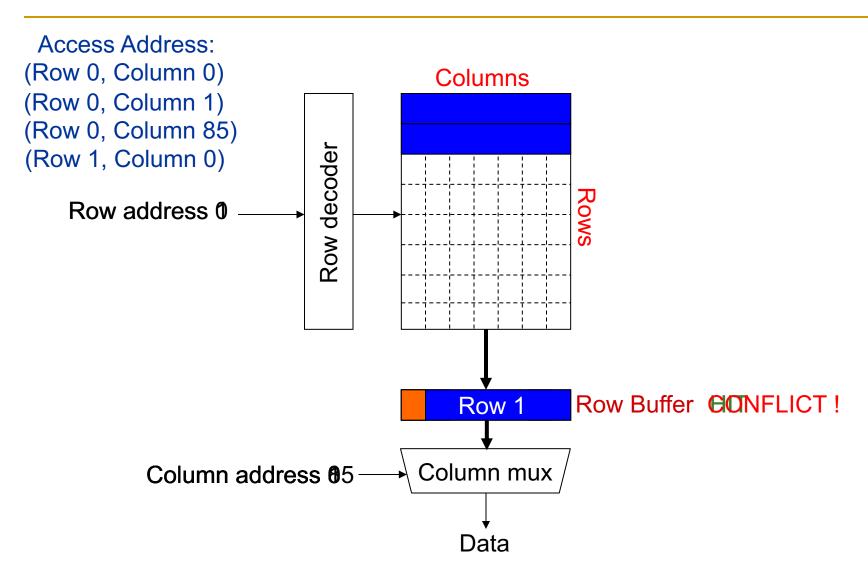

#### DRAM Bank Operation

#### DRAM Burst

- Accessing data in different bursts (rows)

- Need to access the array again

Timeline:

- Accessing data in the same burst (row)

- No need to access the array again, just the multiplexer

Timeline:

Accessing data in the same burst is faster than accessing data in different bursts

#### Recall: Memory Banking

- Memory is divided into banks that can be accessed independently;

banks share address and data buses (to minimize pin cost)

- Can start and complete one bank access per cycle

- Can sustain N concurrent accesses if all N go to different banks

Picture credit: Derek Chiou

#### Multiple Banks (Interleaving) and Channels

- Multiple banks

- Enable concurrent DRAM accesses

- Bits in address determine which bank an address resides in

- Multiple independent channels serve the same purpose

- But they are even better because they have separate data buses

- Increased bus bandwidth

- Enabling more concurrency requires reducing

- Bank conflicts

- Channel conflicts

- How to select/randomize bank/channel indices in address?

- Lower order bits have more entropy

- Randomizing hash functions (XOR of different address bits)

#### Latency Hiding with Multiple Banks

With one bank, time still wasted in between bursts

- Need many threads to simultaneously access memory to keep all banks busy

- Achieved with having high occupancy in GPU cores (SMs)

- Similar idea to hiding pipeline latency in the core

#### Lecture on Memory Organization & Technology

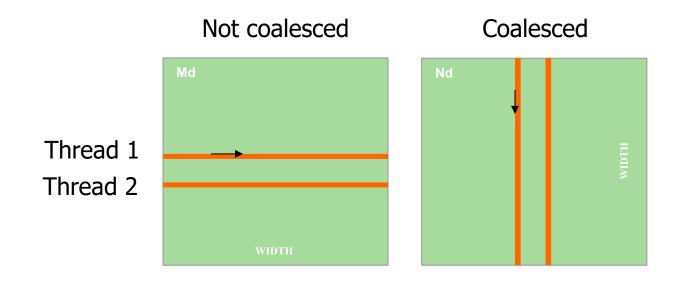

#### Memory Coalescing (I)

- When threads in the same warp access consecutive memory locations in the same burst, the accesses can be combined and served by one burst

- One DRAM transaction is needed

- Known as memory coalescing

- If threads in the same warp access locations not in the same burst, accesses cannot be combined

- Multiple transactions are needed

- Takes longer to service data to the warp

- Sometimes called memory divergence

#### Memory Coalescing (II)

- When accessing global memory, we want to make sure that concurrent threads access nearby memory locations

- Peak bandwidth utilization occurs when all threads in a warp access one cache line (or several consecutive cache lines)

Slide credit: Hwu & Kirk

#### Uncoalesced Memory Accesses

Slide credit: Hwu & Kirk

36

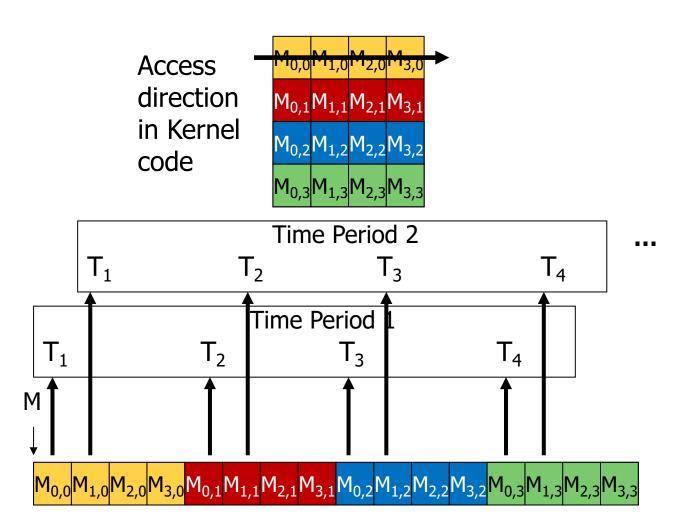

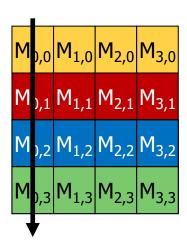

### Coalesced Memory Accesses

Access direction in Kernel code

37

Slide credit: Hwu & Kirk

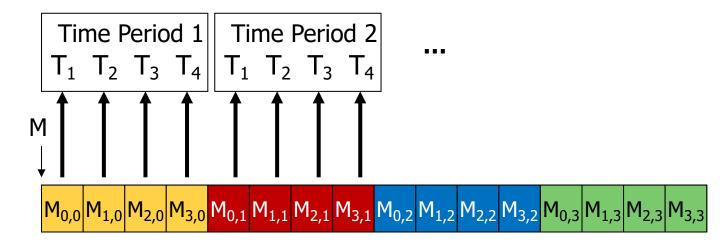

### AoS vs. SoA

### Array of Structures vs. Structure of Arrays

```

struct foo{

float a[8];

Structure of

float b[8];

Arrays

float c[8];

(SoA)

int d[8];

} A;

struct foo{

float a:

Array of

float b:

Structures

float c:

(AoS)

int d:

} A[8];

```

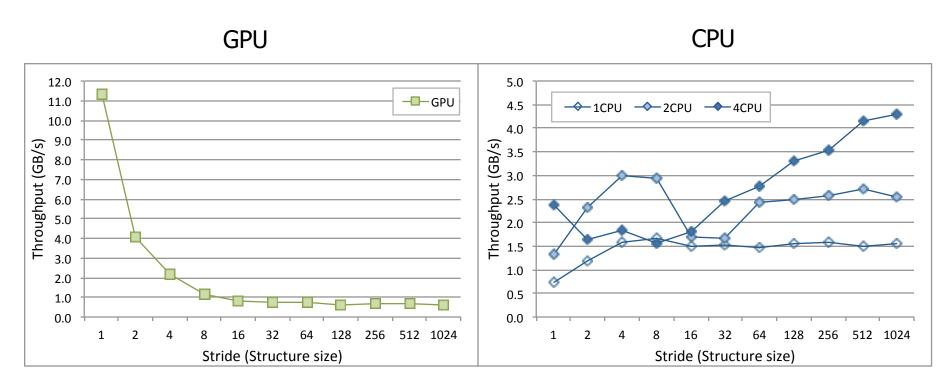

### CPUs Prefer AoS, GPUs Prefer SoA

#### Linear and strided accesses

AMD Kaveri A10-7850K

## Use Shared Memory to Improve Coalescing

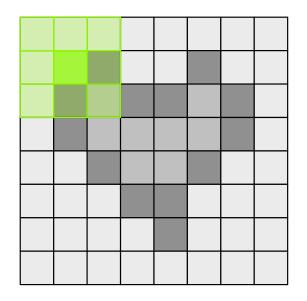

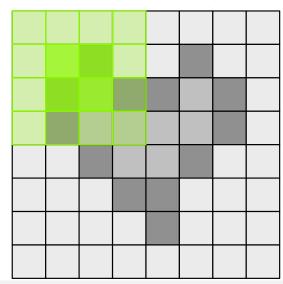

### Data Reuse

Same memory locations accessed by neighboring threads

```

for (int i = 0; i < 3; i++){

for (int j = 0; j < 3; j++){

sum += gauss[i][j] * Image[(i+row-1)*width + (j+col-1)];

}

}</pre>

```

## Data Reuse: Tiling

To take advantage of data reuse, we divide the input into tiles that can be loaded into shared memory

```

__shared__ int l_data[(L_SIZE+2)*(L_SIZE+2)];

...

Load tile into shared memory

__syncthreads();

for (int i = 0; i < 3; i++){

for (int j = 0; j < 3; j++){

sum += gauss[i][j] * l_data[(i+l_row-1)*(L_SIZE+2)+j+l_col-1];

}

}</pre>

```

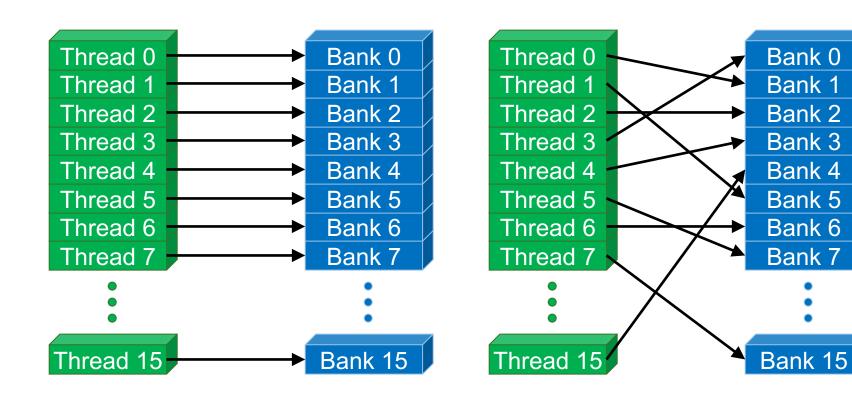

### Shared Memory

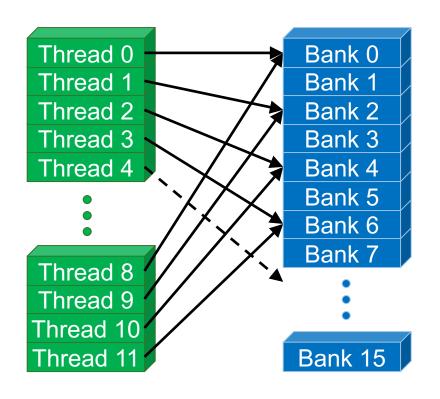

- Shared memory is an interleaved (banked) memory

- Each bank can service one address per cycle

- Typically, 32 banks in NVIDIA GPUs

- Successive 32-bit words are assigned to successive banks

- Bank = Address % 32

- Bank conflicts are only possible within a warp

- No bank conflicts between different warps

## Shared Memory Bank Conflicts (I)

#### Bank conflict free

Linear addressing: stride = 1

Random addressing 1:1

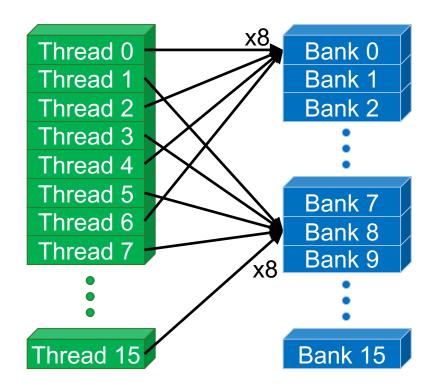

### Shared Memory Bank Conflicts (II)

### N-way bank conflicts

2-way bank conflict: stride = 2

8-way bank conflict: stride = 8

## Use Shared Memory to Improve Coalescing

## Reducing Shared Memory Bank Conflicts

- Bank conflicts are only possible within a warp

- No bank conflicts between different warps

- If strided accesses are needed, some optimization techniques can help

- Padding

- Randomized mapping

- Rau, "Pseudo-randomly interleaved memory," ISCA 1991

- Hash functions

- V.d.Braak+, "Configurable XOR Hash Functions for Banked Scratchpad Memories in GPUs," IEEE TC, 2016

## SIMD Utilization

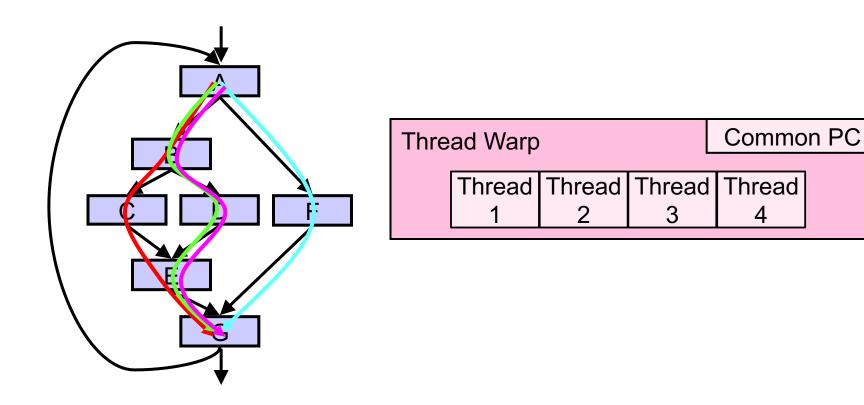

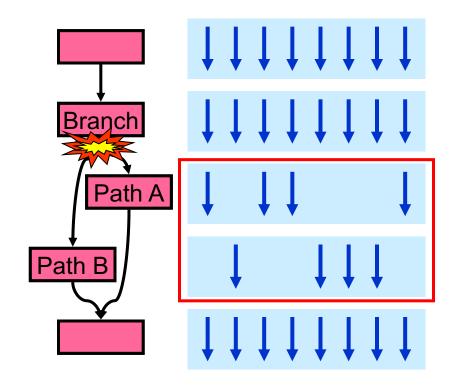

### Threads Can Take Different Paths in Warp-based SIMD

- Each thread can have conditional control flow instructions

- Threads can execute different control flow paths

### Control Flow Problem in GPUs/SIMT

- A GPU uses a SIMD pipeline to save area on control logic

- Groups scalar threads into warps

- Branch divergence occurs when threads inside warps branch to different execution paths

This is the same as conditional/predicated/masked execution. Recall the Vector Mask and Masked Vector Operations?

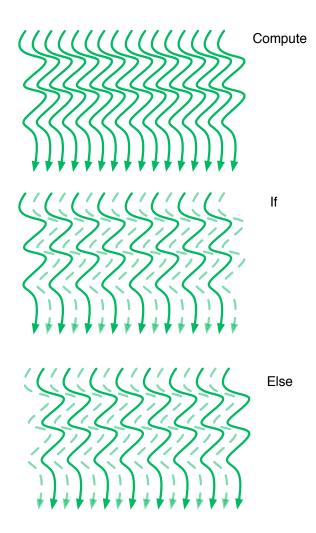

### SIMD Utilization

### Intra-warp divergence

```

Compute(threadIdx.x);

if (threadIdx.x % 2 == 0){

Do_this(threadIdx.x);

}

else{

Do_that(threadIdx.x);

}

```

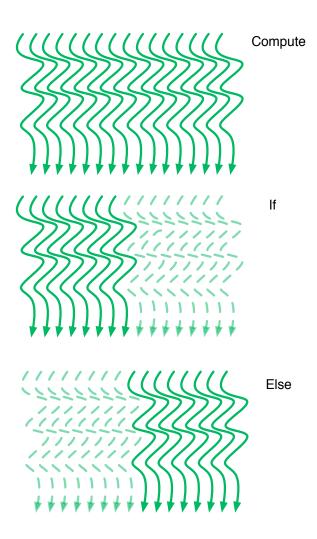

## Increasing SIMD Utilization

### Divergence-free execution

```

Compute(threadIdx.x);

if (threadIdx.x < 32){

Do_this(threadIdx.x * 2);

}

else{

Do_that((threadIdx.x%32)*2+1);

}</pre>

```

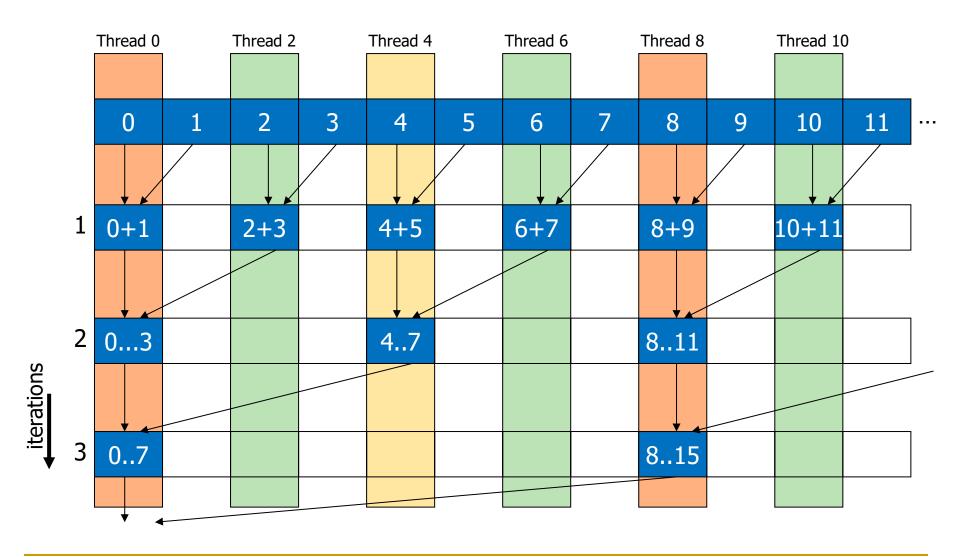

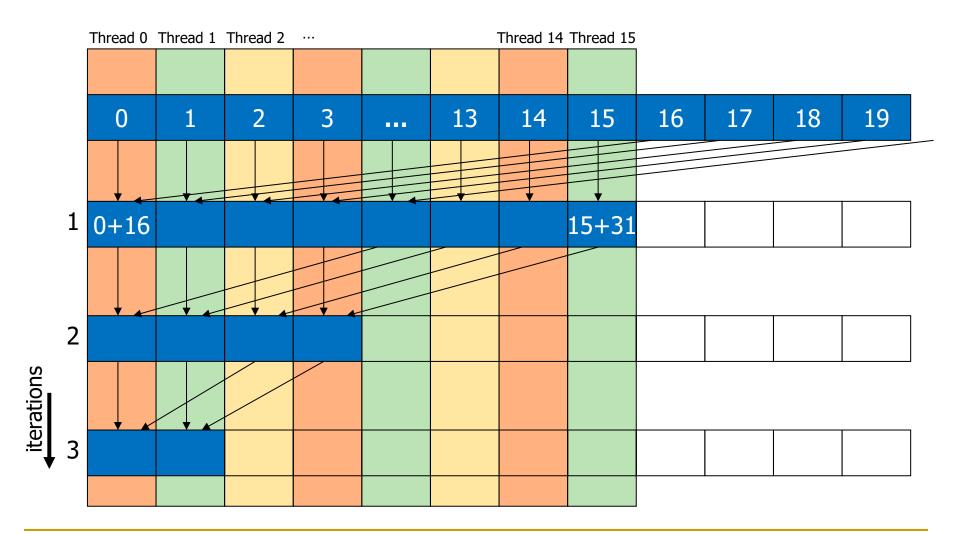

## Vector Reduction: Naïve Mapping (I)

Slide credit: Hwu & Kirk

## Vector Reduction: Naïve Mapping (II)

Program with low SIMD utilization

```

__shared__ float partialSum[]

unsigned int t = threadIdx.x;

for (int stride = 1; stride < blockDim.x; stride *= 2) {

__syncthreads();

if (t % (2*stride) == 0)

partialSum[t] += partialSum[t + stride];

}</pre>

```

## Divergence-Free Mapping (I)

All active threads belong to the same warp

Slide credit: Hwu & Kirk

## Divergence-Free Mapping (II)

Program with high SIMD utilization

```

__shared__ float partialSum[]

unsigned int t = threadIdx.x;

for (int stride = blockDim.x; stride > 0; stride >> 1){

__syncthreads();

if (t < stride)

partialSum[t] += partialSum[t + stride];

}</pre>

```

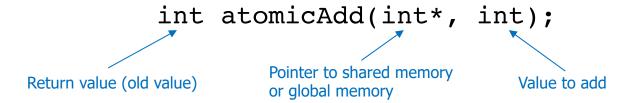

## Atomic Operations

## Atomic Operations (I)

- CUDA provides atomic instructions on shared memory and global memory

- They perform read-modify-write operations atomically

- Arithmetic functions

- Add, sub, max, min, exch, inc, dec, CAS

- Bitwise functions

- And, or, xor

- Datatypes: int, uint, ull, float (half, single, double)\*

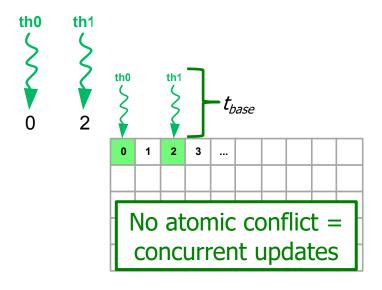

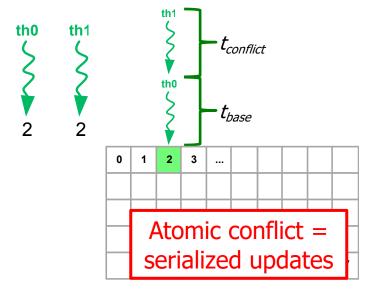

## Atomic Operations (II)

Atomic operations serialize the execution if there are atomic conflicts

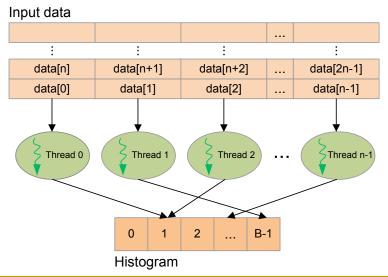

### Uses of Atomic Operations

### Computation

- Atomics on an array that will be the output of the kernel

- Example

- Histogram, reduction

### Synchronization

- Atomics on memory locations that are used for synchronization or coordination

- Example

- Counters, locks, flags...

- Use them to prevent data races when more than one thread need to update the same memory location

## Image Histogram

- Histograms are widely used in image processing

- Some computation before voting in the histogram may be needed

Parallel threads frequently incur atomic conflicts in image histogram computation

### Optimized Parallel Reduction

- 7 versions in CUDA samples: Tree-based reduction in shared memory

- Version 0: No whole warps active

- Version 1: Contiguous threads, but many bank conflicts

- Version 2: No bank conflicts

- Version 3: First level of reduction when reading from global memory

- Version 4: Warp shuffle or unrolling of final warp

- Version 5: Warp shuffle or complete unrolling

- Version 6: Multiple elements per thread sequentially

### Reduction with Atomic Operations

- 3 new versions of reduction based on 3 previous versions

- Version 0: No whole warps active

- Version 3: First level of reduction when reading from global memory

- Version 6: Multiple elements per thread sequentially

- New versions 7, 8, and 9

- Replace the for loop (tree-based reduction) with one shared memory atomic operation per thread

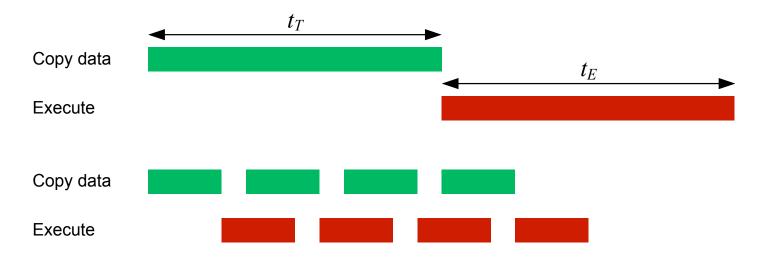

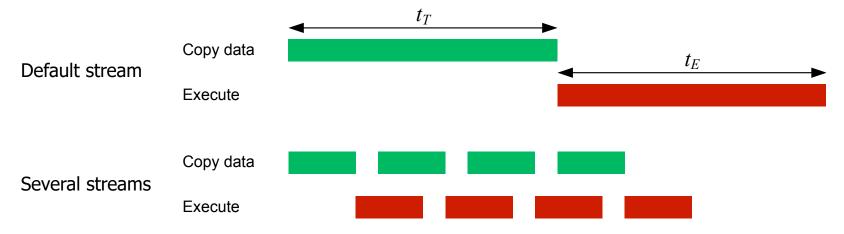

# Asynchronous Data Transfers between CPU and GPU

### CUDA Streams

- CUDA streams (command queues in OpenCL)

- Sequence of operations that are performed in order

- 1. Data transfer CPU-GPU

- 2. Kernel execution

- D input data instances, B blocks

- #Streams: (D / #Streams) data instances, (B / #Streams) blocks

- 3. Data transfer GPU-CPU

### Asynchronous Transfers between CPU & GPU

- Computation divided into #Streams

- D input data instances, B blocks

- #Streams

- D/#Streams data instances

- B/#Streams blocks

Estimates

$$t_E + \frac{t_T}{\#Streams}$$

$$t_E >= t_T \text{(dominant kernel)}$$

$$t_T + \frac{t_E}{\#Streams}$$

$$t_T > t_E \text{ (dominant transfers)}$$

### Overlap of Data Transfers and Kernel Execution

Code for devices that do not support concurrent data transfers

```

// Create streams

int number of streams = 32;

cudaStream t stream[number of streams]; // Stream declaration

for(int i = 0; i < number of streams; ++i)</pre>

cudaStreamCreate(&stream[i]); // Stream creation

// CPU-GPU data transfers

for (int i = 0; i < number of streams; ++i)</pre>

cudaMemcpyAsync(inputDevPtr + i * size, hostPtr + i * size, size,

cudaMemcpyHostToDevice, stream[i]);

// Kernel launches

for (int i = 0; i < number of streams; ++i)</pre>

MyKernel << num blocks / number of streams, num threads, 0, stream[i]>>>

(outputDevPtr + i * size, inputDevPtr + i * size, size);

// GPU-CPU data transfers

for (int i = 0; i < number of streams; ++i)</pre>

cudaMemcpyAsync(hostPtr + i * size, outputDevPtr + i * size, size,

cudaMemcpyDeviceToHost, stream[i]);

cudaDeviceSynchronize(); // Explicit synchronization

// Destroy streams

for (int i = 0; i < number of streams; ++i)</pre>

Check CUDA programming guide

cudaStreamDestroy(stream[i]); // Stream destruction

https://docs.nvidia.com/cuda/cuda-c-programming-

quide/index.html#streams

```

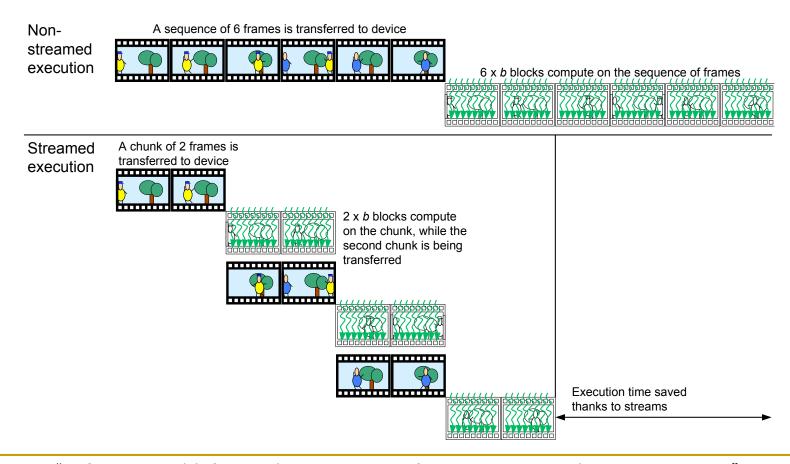

### Use Case: Video Processing

- Applications with independent computation on different data instances can benefit from asynchronous transfers

- For instance, video processing

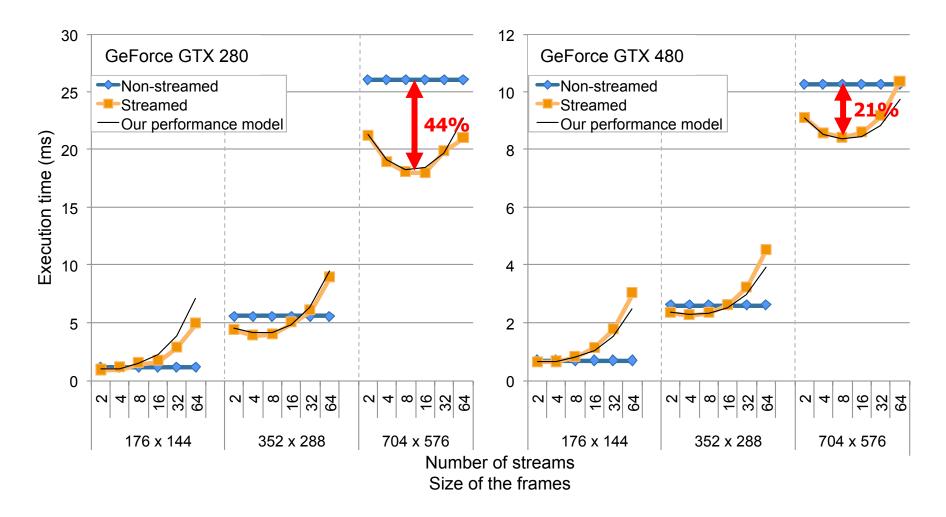

### Video Processing: Performance Results (I)

### 256-bin histogram calculation

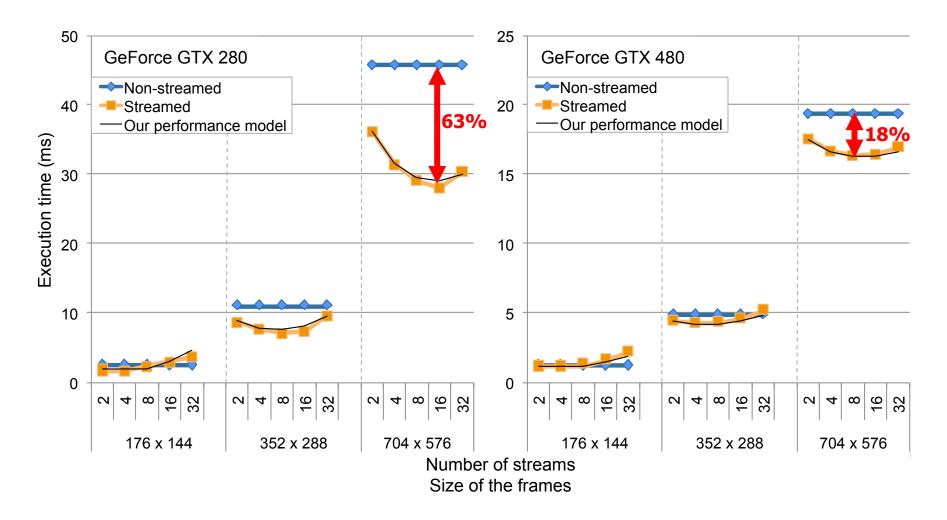

### Video Processing: Performance Results (II)

### RGB-to-grayscale conversion

### Performance Considerations

- Main bottlenecks

- CPU-GPU data transfers

- Global memory access

- Memory access

- Latency hiding

- Occupancy

- Memory coalescing

- Data reuse

- Shared memory usage

- SIMD (Warp) Utilization: Divergence

- Other considerations

- Atomic operations: Serialization

- Data transfers between CPU and GPU

- Overlap of communication and computation

## Recommended Readings (I)

- Hwu and Kirk, "Programming Massively Parallel Processors,"

Third Edition, 2017

- Chapter 5: Performance considerations

- Chapter 18 Programming

a heterogeneous computing cluster,

Section 18.5

## Recommended Readings (II)

- Hwu and Kirk and El Hajj, "Programming Massively Parallel Processors," Fourth Edition, 2022

- Chapter 6 Performance considerations

- Chapter 20 Programming a heterogeneous computing cluster, Section 20.5

## P&S Heterogeneous Systems

### GPU Performance Considerations

Dr. Juan Gómez Luna

Prof. Onur Mutlu

ETH Zürich

Fall 2022

31 October 2022