# **P&S HW/SW Co-design** Introduction & Project Proposals

Konstantinos Kanellopoulos Prof. Onur Mutlu

> ETH Zurich Fall 2022 17 October 2022

### P&S: Hardware/Software Co-design (I)

#### 227-0085-56L Projekte & Seminare: Intelligent Architectures via Hardware/Software Cooperation

| Semester                | Autumn Semester 2022                                                                                     |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| Lecturers               | O. Mutlu                                                                                                 |  |  |  |

| Periodicity             | every semester recurring course                                                                          |  |  |  |

| Language of instruction | English                                                                                                  |  |  |  |

| Comment                 | Only for Electrical Engineering and Information Technology BSc.                                          |  |  |  |

|                         | Course can only be registered for once. A repeatedly registration in a later semester is not chargeable. |  |  |  |

| Courses   | Catalogue data | Performance assessment                                                                                                                                                                                                                                                                                               | Learning materials                                                                                          | Groups                                                      | Restrictions                                                                        | Offered in                                                             | Overview                                                                              |                                                    |  |  |  |

|-----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| Abstract  |                | The category of "Laboratory Courses, Projects, Seminars" includes courses and laboratories in various formats designed to impart practical knowledge and skills. Moreover, these classes encourage independent experimentation and design, allow for explorative learning and teach the methodology of project work. |                                                                                                             |                                                             |                                                                                     |                                                                        |                                                                                       |                                                    |  |  |  |

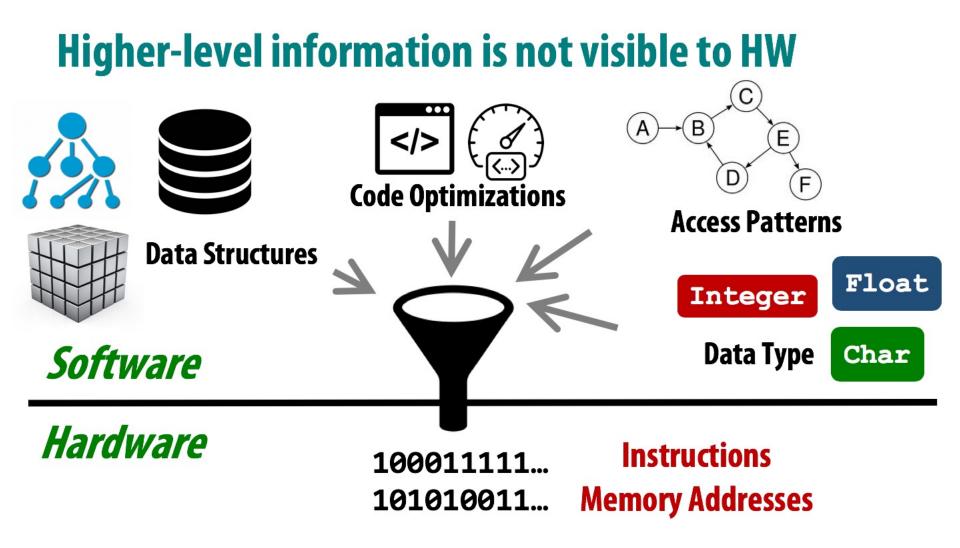

| Objective |                |                                                                                                                                                                                                                                                                                                                      | ational and memory optin<br>any others. As such, the<br>own and such optimizati<br>ardware optimizations ca | mizations, su<br>potential of<br>ons come w<br>annot achiev | uch as prefetching<br>such optimization<br>ith large area, po<br>re their performan | g, cache mana<br>ns is limited du<br>wer and compl<br>nce potential ar | gement policies, i<br>e to the limited inf<br>lexity overheads r<br>nd waste power, c | memory data placement,<br>formation the underlying |  |  |  |

## The Role of This Course

#### P&S Hardware/Software Co-design: Contents

- We will introduce the need for hardware/software codesign in current computing systems, in order to achieve high performance and energy efficiency

- You will get familiar with the current as well as futuristic hardware/software co-operative techniques

- You will learn how to modify software to match the underlying hardware and vice-versa

- You will work hands-on: analyzing workloads, creating new hardware/software interfaces, proposing new software and architectural solutions, etc.

### Key Takeaways

- This P&S aims at improving your

- Knowledge in Computer Architecture and Hardware/Software

Co-Design

- Technical skills in programming and developing architectural simulators

- Critical thinking and analysis

- Interaction with a big group of researchers

- Familiarity with key research directions

- Technical presentation of your project

# (Learn how to) design efficient hardware/software

co-operative techniques

### Prerequisites of the Course

- Digital Design and Computer Architecture (or equivalent course)

- https://safari.ethz.ch/digitaltechnik/spring2021/doku.php?id=schedule

- https://safari.ethz.ch/digitaltechnik/spring2022/doku.php?id=schedule

- Familiarity with C/C++ programming

- Familiarity with Machine Learning frameworks

- Only in specific projects

- Interest in

- computer architectures and computing paradigms

- discovering why things do or do not work and solving problems

- making systems efficient and usable

### Course Info: Who Are We? (I)

#### Onur Mutlu

- Full Professor @ ETH Zurich ITET (INFK), since September 2015

- Strecker Professor @ Carnegie Mellon University ECE/CS, 2009-2016, 2016-...

- PhD from UT-Austin, worked at Google, VMware, Microsoft Research, Intel, AMD

- https://people.inf.ethz.ch/omutlu/

- omutlu@gmail.com (Best way to reach me)

- https://people.inf.ethz.ch/omutlu/projects.htm

#### Research and Teaching in:

- Computer architecture, computer systems, hardware security, bioinformatics

- Memory and storage systems

- Hardware security, safety, predictability

- Fault tolerance

- Hardware/software cooperation

- Architectures for bioinformatics, health, medicine

• ...

#### Course Info: Who Are We? (II)

Get to know our research: <u>https://safari.ethz.ch/safari-group/</u>

### Course Info: Who Are We? (III)

Get to know them and their research: <u>https://safari.ethz.ch/safari-group/10</u>

#### Onur Mutlu's SAFARI Research Group

#### **Computer architecture, HW/SW, systems, bioinformatics, security, memory**

https://safari.ethz.ch/safari-newsletter-january-2021/

#### SAFARI Newsletter December 2021 Edition

#### <u>https://safari.ethz.ch/safari-newsletter-december-2021/</u>

**ETH** zürich

Think Big, Aim High

View in your browser December 2021

#### SAFARI Live Seminars (I)

https://safari.ethz.ch/safari-seminar-series/

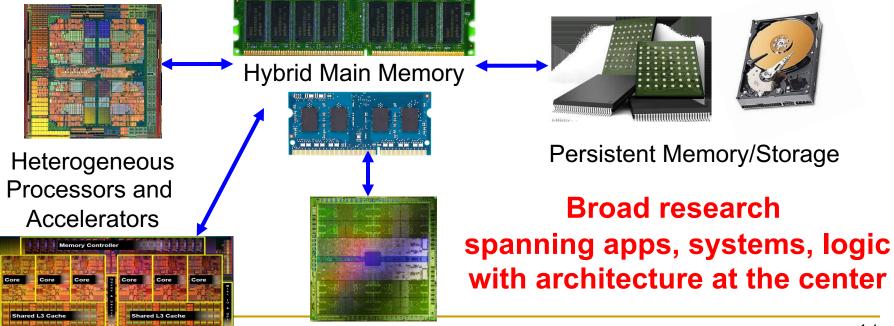

#### Current Research Focus Areas

#### <u>Research Focus:</u> Computer architecture, HW/SW, bioinformatics

- Memory and storage (DRAM, flash, emerging), interconnects

- Heterogeneous & parallel systems, GPUs, systems for data analytics

- System/architecture interaction, new execution models, new interfaces

- Energy efficiency, fault tolerance, hardware security, performance

- Genome sequence analysis & assembly algorithms and architectures

- Biologically inspired systems & system design for bio/medicine

#### Course Requirements and Expectations

- Study the learning materials

- Each student will carry out a hands-on project

- Build, implement, code, and design with close engagement from the supervisors

#### Participation

- Ask questions, contribute thoughts/ideas

- Read relevant papers

- Presentation & GitHub repository

We will help the projects with good progress to get published in good venues!

### Your Responsibilities

- Several Lectures:

- Monday 12:30-1:30 PM

- Working on your project for ~4-5 hours per week

- Meeting your mentors weekly is required to be able to track progress efficiently

- https://safari.ethz.ch/projects\_and\_seminars/fall2022/doku. php?id=hw\_sw\_codesign

- Useful information for the course

- Check your email and Moodle frequently for announcements

- We will also have Moodle for Q&A, announcements, ...

We will give you a chance to select a project

- Then, we will have 1-1 meetings to match your interests, skills, and background with a suitable project

- It is important that you study the learning materials before our next meeting!

- We will assign the projects next week

- Presentation of research papers

- Background on computer architecture topics (e.g. Virtual Memory)

- Tutorial on microarchitectural simulator

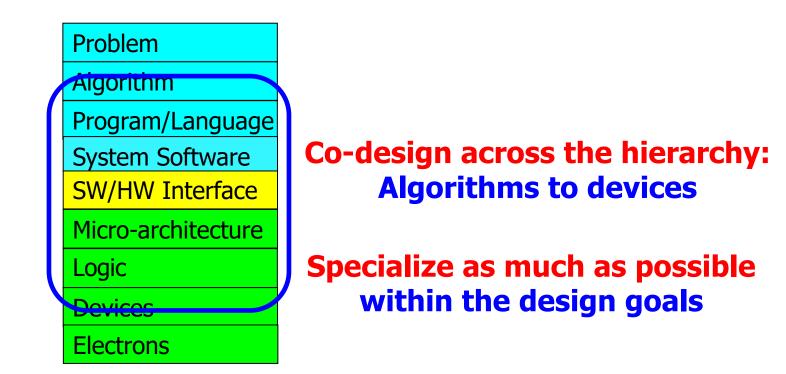

# Hardware/Software Co-design

To achieve the highest energy efficiency and performance:

#### we must take the expanded view

of computer architecture

### Hardware/Software Co-design

- Design application-specific standalone accelerators

- + High performance/energy benefits

- Low Flexibility

- Extend general-purpose processors with application- or task-specific hardware components

- + High performance/energy benefits

- Abrupt changes in the processor

- Revisiting the existing hardware/software interfaces to enhance performance, security, portability

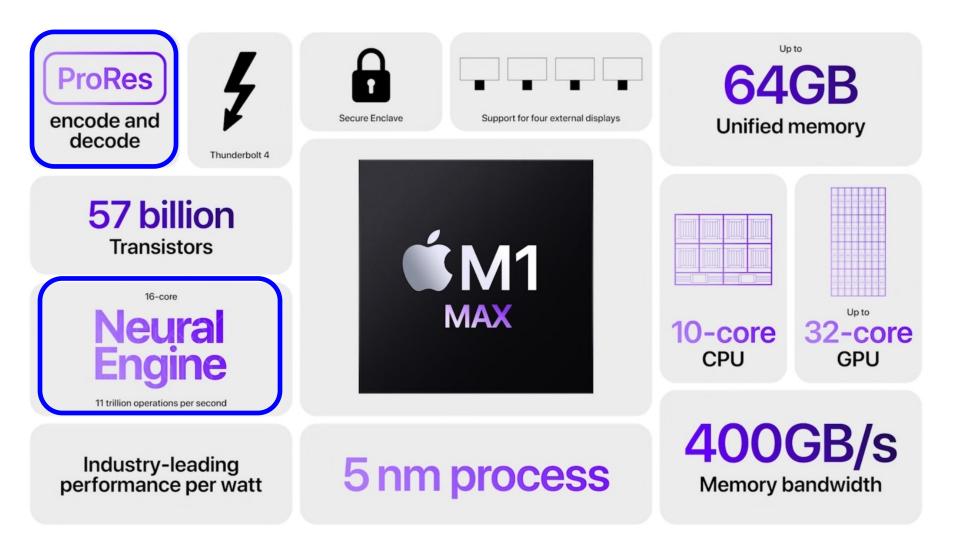

### Apple M1 Max Processor

### Different Platforms, Different Goals

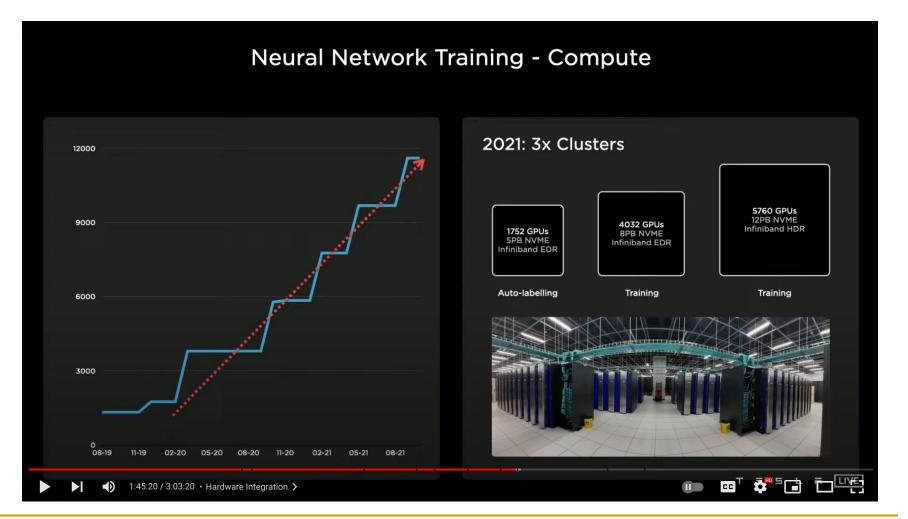

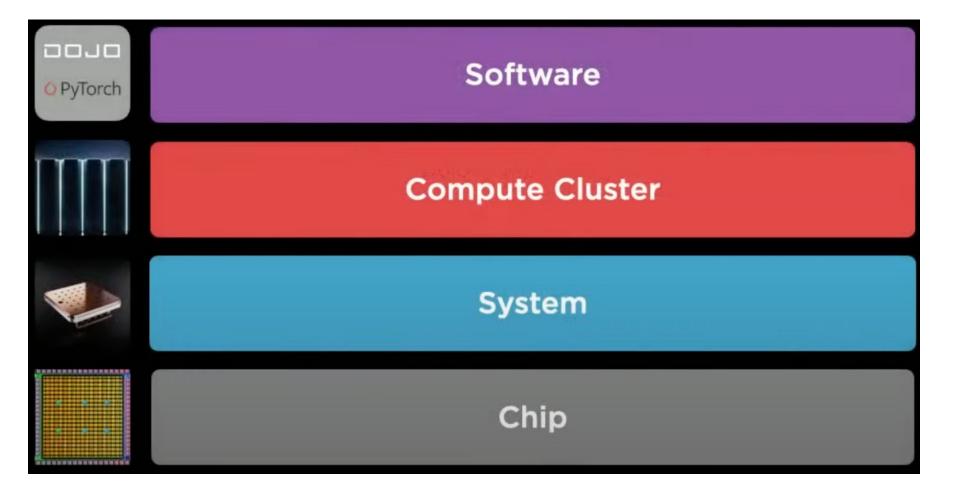

Tesla Dojo Chip & System

D1 Chip

#### 362 TFLOPs BF16/CFP8 22.6 TFLOPs FP32

10TBps/dir. On-Chip Bandwidth 4TBps/edge. Off-Chip Bandwidth

400W TDP

50 Billion Transistors

11+ Miles Of Wires

▶ 1:53:07 / 3:03:20 • Dojo >

https://www.youtube.com/watch?v=j0z4FweCy4M&t=6340s

### Different Platforms, Different Goals

Tesla Dojo Chip & System

#### https://www.youtube.com/watch?v=j0z4FweCy4M&t=6340s

### Different Platforms, Different Goals

Tesla Dojo Chip & System

#### SAFARI Live Seminar

#### https://www.youtube.com/watch?v=x2-qB0J7KHw

SAFARI Live Seminar - Thinking Outside the Die: Architecting the ML Accelerator of the Future

1 waiting • Scheduled for Feb 28, 2022

Onu

💼 7 🖓 DISLIKE 📣 SHARE 🖅 SAVE …

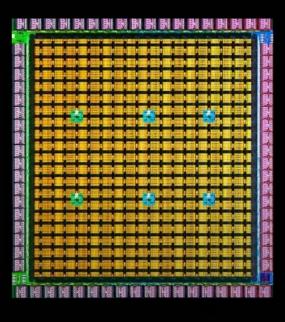

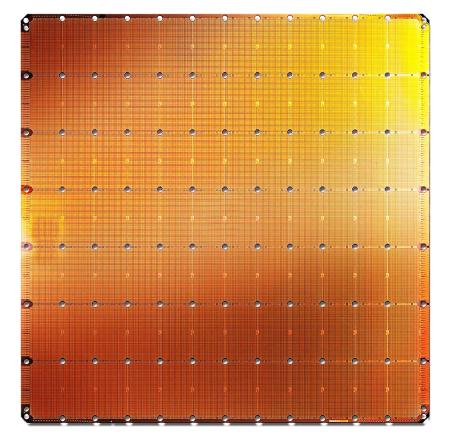

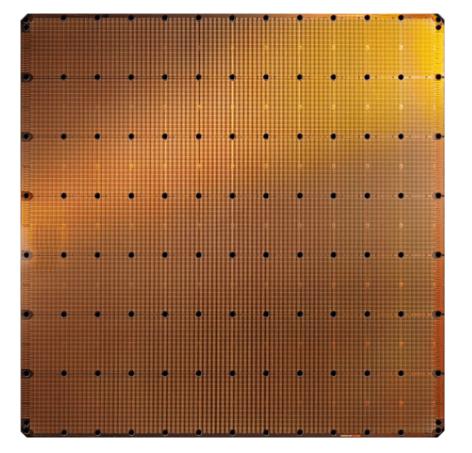

### Cerebras's Wafer Scale Engine (2019)

The largest ML accelerator chip (2019)

400,000 cores

Cerebras WSE 1.2 Trillion transistors 46,225 mm<sup>2</sup> Largest GPU 21.1 Billion transistors 815 mm<sup>2</sup> NVIDIA TITAN V

### Cerebras's Wafer Scale Engine-2 (2021)

The largest ML accelerator chip (2021)

850,000 cores

Cerebras WSE-2 2.6 Trillion transistors 46,225 mm<sup>2</sup> Largest GPU 54.2 Billion transistors 826 mm<sup>2</sup> NVIDIA Ampere GA100

https://www.anandtech.com/show/14758/hot-chips-31-live-blogs-cerebras-wafer-scale-deep-learning https://www.cerebras.net/cerebras-wafer-scale-engine-why-we-need-big-chips-for-deep-learning/

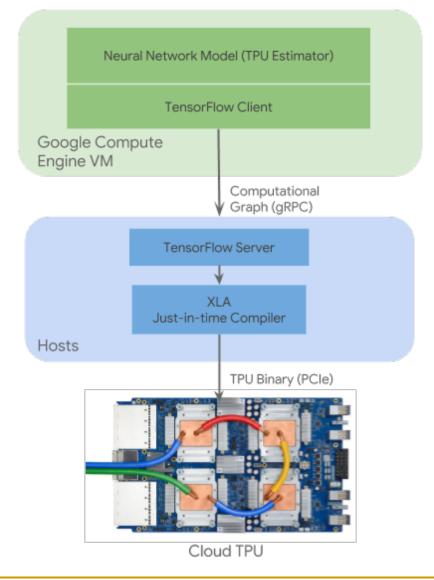

### Google TensorFlow + TPU

#### Google TPU Generation I (~2016)

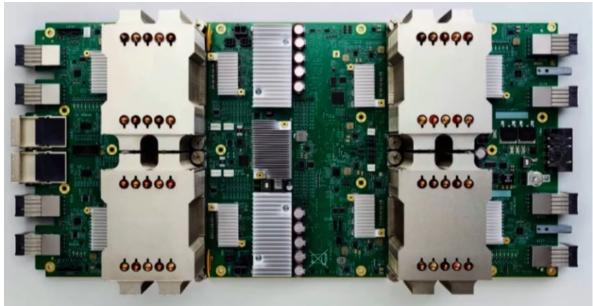

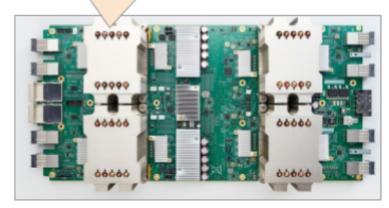

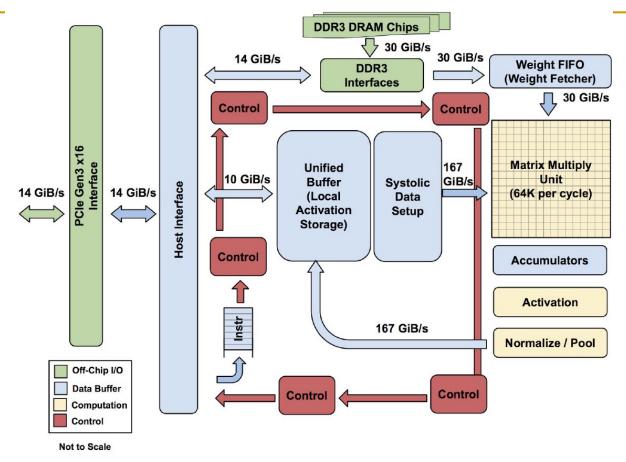

**Figure 3.** TPU Printed Circuit Board. It can be inserted in the slot for an SATA disk in a server, but the card uses PCIe Gen3 x16.

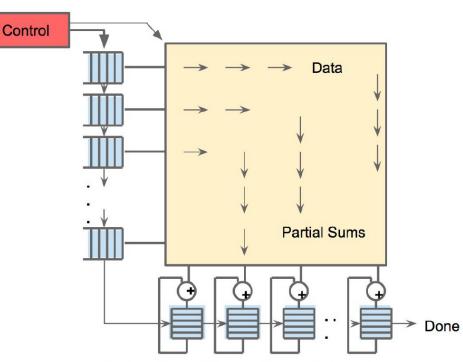

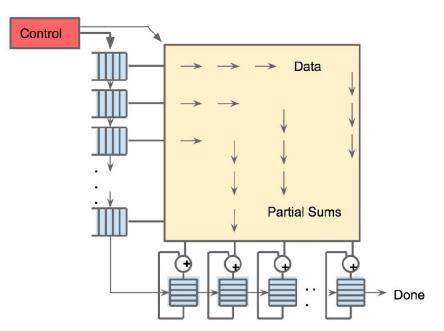

**Figure 4.** Systolic data flow of the Matrix Multiply Unit. Software has the illusion that each 256B input is read at once, and they instantly update one location of each of 256 accumulator RAMs.

#### Jouppi et al., "In-Datacenter Performance Analysis of a Tensor Processing Unit", ISCA 2017.

### Google TPU Generation II (2017)

https://www.nextplatform.com/2017/05/17/first-depth-look-googles-new-second-generation-tpu/

#### 4 TPU chips vs 1 chip in TPU1

### High Bandwidth Memory vs DDR3

### Floating point operations vs FP16

45 TFLOPS per chip vs 23 TOPS

Designed for training and inference vs only inference

### Google TPU Generation III (2019)

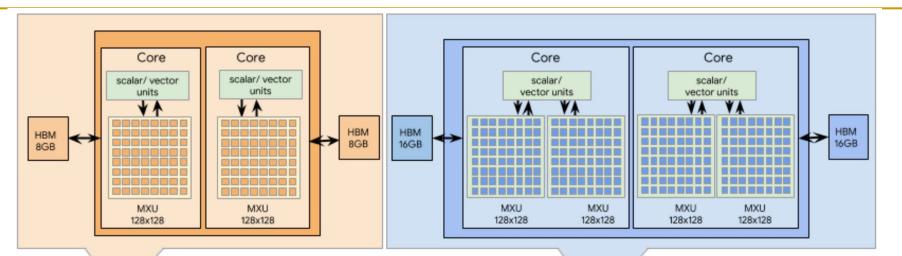

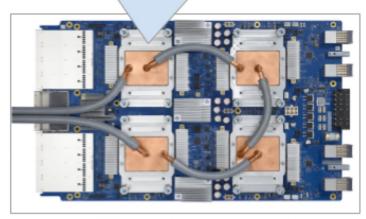

TPU v2 - 4 chips, 2 cores per chip

TPU v3 - 4 chips, 2 cores per chip

#### 32GB HBM per chip vs 16GB HBM in TPU2

#### 4 Matrix Units per chip 90 TFLOPS per chip vs 2 Matrix Units in TPU2 vs 45 TFLOPS in TPU2

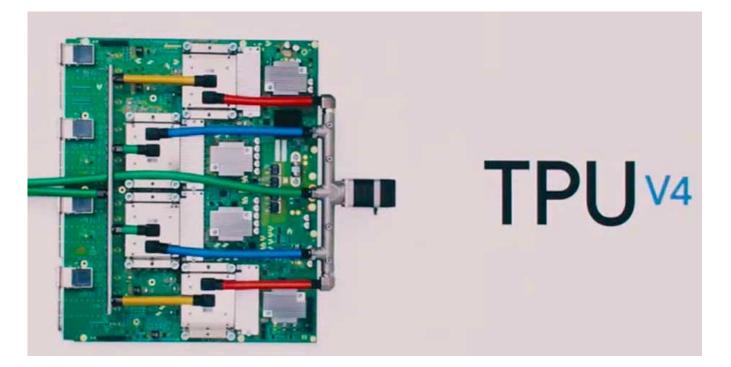

#### Google TPU Generation IV (2019)

#### New ML applications (vs. TPU3):

- Computer vision

- Natural Language Processing (NLP)

- Recommender system

- Reinforcement learning that plays Go

250 TFLOPS per chip in 2021 vs 90 TFLOPS in TPU3

https://spectrum.ieee.org/tech-talk/computing/hardware/heres-how-googles-tpu-v4-ai-chip-stacked-up-in-training-tests

#### An Example Modern Systolic Array: TPU (II)

As reading a large SRAM uses much more power than arithmetic, the matrix unit uses systolic execution to save energy by reducing reads and writes of the Unified Buffer [Kun80][Ram91][Ovt15b]. Figure 4 shows that data flows in from the left, and the weights are loaded from the top. A given 256-element multiply-accumulate operation moves through the matrix as a diagonal wavefront. The weights are preloaded, and take effect with the advancing wave alongside the first data of a new block. Control and data are pipelined to give the illusion that the 256 inputs are read at once, and that they instantly update one location of each of 256 accumulators. From a correctness perspective, software is unaware of the systolic nature of the matrix unit, but for performance, it does worry about the latency of the unit.

Jouppi et al., "In-Datacenter Performance Analysis of a Tensor Processing Unit", ISCA 2017.

#### An Example Modern Systolic Array: TPU (III)

**Figure 1.** TPU Block Diagram. The main computation part is the yellow Matrix Multiply unit in the upper right hand corner. Its inputs are the blue Weight FIFO and the blue Unified Buffer (UB) and its output is the blue Accumulators (Acc). The yellow Activation Unit performs the nonlinear functions on the Acc, which go to the UB.

# System Architecture Design Today

- Human-driven

- Humans design the policies (how to do things)

- Many (too) simple, short-sighted policies all over the system

- No automatic data-driven policy learning

- (Almost) no learning: cannot take lessons from past actions

### Can we design fundamentally intelligent architectures?

## An Intelligent Architecture

- Data-driven

- Machine learns the "best" policies (how to do things)

- Sophisticated, workload-driven, changing, far-sighted policies

- Automatic data-driven policy learning

- All controllers are intelligent data-driven agents

#### How do we start?

### Self-Optimizing DRAM Controllers

Engin Ipek, Onur Mutlu, José F. Martínez, and Rich Caruana, "Self Optimizing Memory Controllers: A Reinforcement Learning <u>Approach</u>" *Proceedings of the <u>35th International Symposium on Computer Architecture</u> (ISCA), pages 39-50, Beijing, China, June 2008.*

#### Self-Optimizing Memory Controllers: A Reinforcement Learning Approach

Engin İpek<sup>1,2</sup> Onur Mutlu<sup>2</sup> José F. Martínez<sup>1</sup> Rich Caruana<sup>1</sup>

<sup>1</sup>Cornell University, Ithaca, NY 14850 USA <sup>2</sup> Microsoft Research, Redmond, WA 98052 USA

# Pythia: RL-Based Prefetching

- Rahul Bera, Konstantinos Kanellopoulos, Anant Nori, Taha Shahroodi, Sreenivas Subramoney, and <u>Onur Mutlu</u>,

"Pythia: A Customizable Hardware Prefetching Framework Using

Online Reinforcement Learning"

Proceedings of the <u>54th International Symposium on</u>

<u>Microarchitecture</u> (MICRO), Virtual, October 2021.

[Slides (pptx) (pdf)] [Short Talk Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)][Talk Video (20 minutes)]

[Lightning Talk Video (1.5 minutes)]

- [Pythia Source Code (Officially Artifact Evaluated with All Badges)]

#### Pythia: A Customizable Hardware Prefetching Framework Using Online Reinforcement Learning

Rahul Bera1Konstantinos Kanellopoulos1Anant V. Nori2Taha Shahroodi3,1Sreenivas Subramoney2Onur Mutlu1

<sup>1</sup>ETH Zürich <sup>2</sup>Processor Architecture Research Labs, Intel Labs <sup>3</sup>TU Delft

### Hermes: Perceptron-Based Off-chip Prediction

Rahul Bera, Konstantinos Kanellopoulos, Shankar Balachandran, David Novo, Ataberk Olgun, Mohammad Sadrosadati, Onur Mutlu "Hermes: Accelerating Long-Latency Load Requests via Perceptron-Based Off-Chip Load Prediction" Proceedings of the <u>55th International Symposium on</u>

<u>Microarchitecture</u> (**MICRO**), Chicago USA, October 2022.

#### Hermes: Accelerating Long-Latency Load Requests via Perceptron-Based Off-Chip Load Prediction

Rahul Bera1Konstantinos Kanellopoulos1Shankar Balachandran2David Novo3Ataberk Olgun1Mohammad Sadrosadati1Onur Mutlu1

<sup>1</sup>ETH Zürich <sup>2</sup>Intel Processor Architecture Research Lab <sup>3</sup>LIRMM, Univ. Montpellier, CNRS

### Data-Aware Architectures

- A data-aware architecture understands what it can do with and to each piece of data

- It makes use of different properties of data to improve performance, efficiency and other metrics

- Compressibility

- Approximability

- Locality

- Sparsity

- Criticality for Computation X

- Access Semantics

• ...

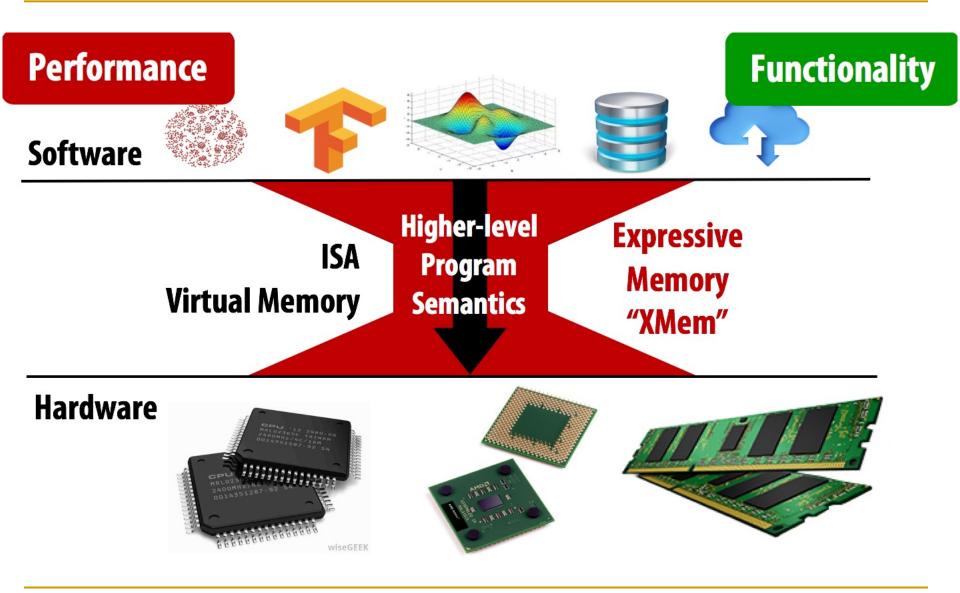

## One Problem: Limited Expressiveness

## A Solution: More Expressive Interfaces

# Expressive (Memory) Interfaces

Nandita Vijaykumar, Abhilasha Jain, Diptesh Majumdar, Kevin Hsieh, Gennady Pekhimenko, Eiman Ebrahimi, Nastaran Hajinazar, Phillip B. Gibbons and Onur Mutlu, "A Case for Richer Cross-layer Abstractions: Bridging the Semantic Gap with Expressive Memory" Proceedings of the <u>45th International Symposium on Computer Architecture</u> (ISCA), Los Angeles, CA, USA, June 2018.

[Slides (pptx) (pdf)] [Lightning Talk Slides (pptx) (pdf)] [Lightning Talk Video]

#### A Case for Richer Cross-layer Abstractions: Bridging the Semantic Gap with Expressive Memory

Nandita Vijaykumar<sup>†</sup>§ Abhilasha Jain<sup>†</sup> Diptesh Majumdar<sup>†</sup> Kevin Hsieh<sup>†</sup> Gennady Pekhimenko<sup>‡</sup> Eiman Ebrahimi<sup>&</sup> Nastaran Hajinazar<sup>∔</sup> Phillip B. Gibbons<sup>†</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>University of Toronto <sup>&</sup>NVIDIA <sup>+</sup>Simon Fraser University <sup>§</sup>ETH Zürich

# Expressive (Memory) Interfaces for GPUs

Nandita Vijaykumar, Eiman Ebrahimi, Kevin Hsieh, Phillip B. Gibbons and Onur Mutlu, "The Locality Descriptor: A Holistic Cross-Layer Abstraction to Express

Data Locality in GPUs"

Proceedings of the <u>45th International Symposium on Computer Architecture</u> (ISCA),

Los Angeles, CA, USA, June 2018.

[Slides (pptx) (pdf)] [Lightning Talk Slides (pptx) (pdf)]

[Lightning Talk Video]

The Locality Descriptor:

#### A Holistic Cross-Layer Abstraction to Express Data Locality in GPUs

Nandita Vijaykumar<sup>†§</sup> Eiman Ebrahimi<sup>‡</sup> Kevin Hsieh<sup>†</sup> Phillip B. Gibbons<sup>†</sup> Onur Mutlu<sup>§†</sup> <sup>†</sup>Carnegie Mellon University <sup>‡</sup>NVIDIA <sup>§</sup>ETH Zürich

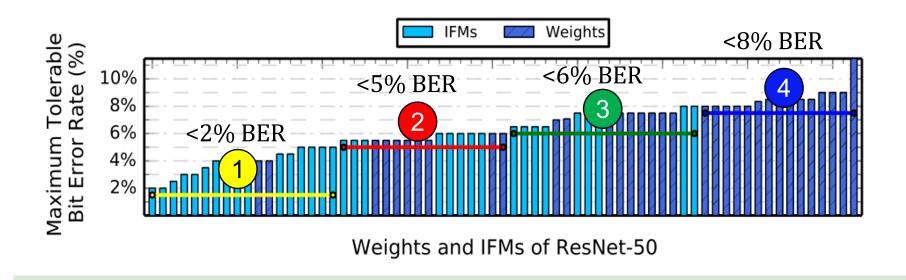

## Another Example: EDEN for DNNs

- Deep Neural Network evaluation is very DRAM-intensive (especially for large networks)

- 1. Some data and layers in DNNs are very tolerant to errors

- 2. Reduce DRAM latency and voltage on such data and layers

3. While still achieving a user-specified DNN accuracy target by making training DRAM-error-aware

#### Data-aware management of DRAM latency and voltage for Deep Neural Network Inference

### **Example DNN Data Type to DRAM Mapping**

#### Mapping example of ResNet-50:

#### Map more error-tolerant DNN layers to DRAM partitions with lower voltage/latency

4 DRAM partitions with different error rates

### EDEN: Data-Aware Efficient DNN Inference

Skanda Koppula, Lois Orosa, A. Giray Yaglikci, Roknoddin Azizi, Taha Shahroodi, Konstantinos Kanellopoulos, and Onur Mutlu, "EDEN: Enabling Energy-Efficient, High-Performance Deep Neural Network Inference Using Approximate DRAM" Proceedings of the 52nd International Symposium on Microarchitecture (MICRO), Columbus, OH, USA, October 2019.

[Lightning Talk Slides (pptx) (pdf)]

[Lightning Talk Video (90 seconds)]

#### EDEN: Enabling Energy-Efficient, High-Performance Deep Neural Network Inference Using Approximate DRAM

Skanda Koppula Lois Orosa A. Giray Yağlıkçı Roknoddin Azizi Taha Shahroodi Konstantinos Kanellopoulos Onur Mutlu ETH Zürich

# SMASH: SW/HW Indexing Acceleration

- Konstantinos Kanellopoulos, Nandita Vijaykumar, Christina Giannoula, Roknoddin Azizi, Skanda Koppula, Nika Mansouri Ghiasi, Taha Shahroodi, Juan Gomez-Luna, and Onur Mutlu,

- "SMASH: Co-designing Software Compression and Hardware-Accelerated Indexing for Efficient Sparse Matrix Operations" Proceedings of the 52nd International Symposium on

- <u>Microarchitecture</u> (**MICRO**), Columbus, OH, USA, October 2019.

- [<u>Slides (pptx) (pdf)</u>] [Lightning Talk Slides (pptx) (pdf)]

- [Poster (pptx) (pdf)]

- [Lightning Talk Video (90 seconds)]

- [Full Talk Lecture (30 minutes)]

#### SMASH: Co-designing Software Compression and Hardware-Accelerated Indexing for Efficient Sparse Matrix Operations

Konstantinos Kanellopoulos<sup>1</sup> Nandita Vijaykumar<sup>2,1</sup> Christina Giannoula<sup>1,3</sup> Roknoddin Azizi<sup>1</sup> Skanda Koppula<sup>1</sup> Nika Mansouri Ghiasi<sup>1</sup> Taha Shahroodi<sup>1</sup> Juan Gomez Luna<sup>1</sup> Onur Mutlu<sup>1,2</sup> <sup>1</sup>ETH Zürich <sup>2</sup>Carnegie Mellon University <sup>3</sup>National Technical University of Athens

## Data-Aware Virtual Memory Framework

Nastaran Hajinazar, Pratyush Patel, Minesh Patel, Konstantinos Kanellopoulos, Saugata Ghose, Rachata Ausavarungnirun, Geraldo Francisco de Oliveira Jr., Jonathan Appavoo, Vivek Seshadri, and Onur Mutlu, "The Virtual Block Interface: A Flexible Alternative to the Conventional Virtual Memory Framework" *Proceedings of the <u>47th International Symposium on Computer Architecture</u> (<i>ISCA*), Virtual, June 2020. [Slides (pptx) (pdf)] [Lightning Talk Slides (pptx) (pdf)] [ARM Research Summit Poster (pptx) (pdf)] [Talk Video (26 minutes)] [Lightning Talk Video (3 minutes)]

#### The Virtual Block Interface: A Flexible Alternative to the Conventional Virtual Memory Framework

Nastaran Hajinazar<sup>\*†</sup> Pratyush Patel<sup>⋈</sup> Minesh Patel<sup>★</sup> Konstantinos Kanellopoulos<sup>★</sup> Saugata Ghose<sup>‡</sup> Rachata Ausavarungnirun<sup>⊙</sup> Geraldo F. Oliveira<sup>★</sup> Jonathan Appavoo<sup>◊</sup> Vivek Seshadri<sup>▽</sup> Onur Mutlu<sup>\*‡</sup>

\*ETH Zürich <sup>†</sup>Simon Fraser University  $\bowtie$  University of Washington <sup>‡</sup>Carnegie Mellon University  $\odot$  King Mongkut's University of Technology North Bangkok  $\diamond$ Boston University  $\bigtriangledown$  Microsoft Research India

# Thank you ☺ Questions?