## **SoftMC Tutorial**

Hasan Hassan

01.10.2020

## Summary

- **SoftMC:** an FPGA-based DRAM testing infrastructure

- Characterize, analyze, and understand DRAM cell behavior

- Flexible and Easy to Use (C++ API)

- Open-source (github.com/CMU-SAFARI/SoftMC)

- SoftMC enables a wide range of studies

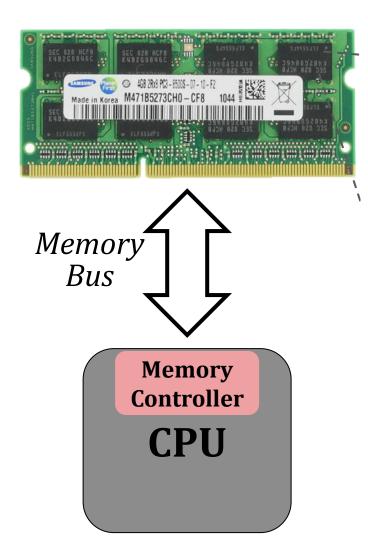

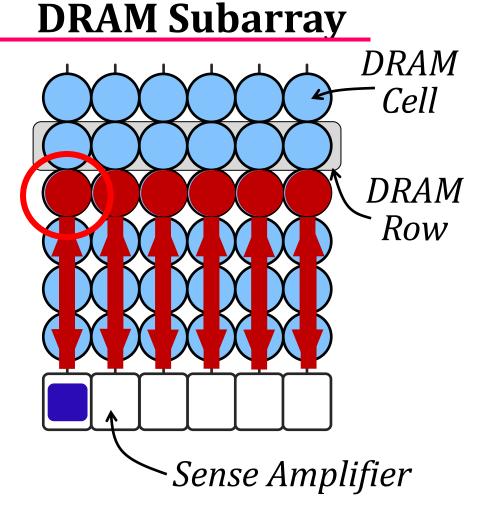

## **DRAM Organization**

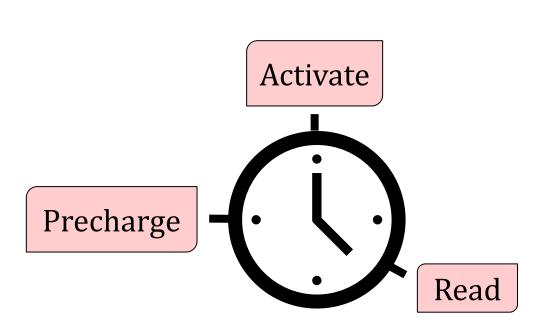

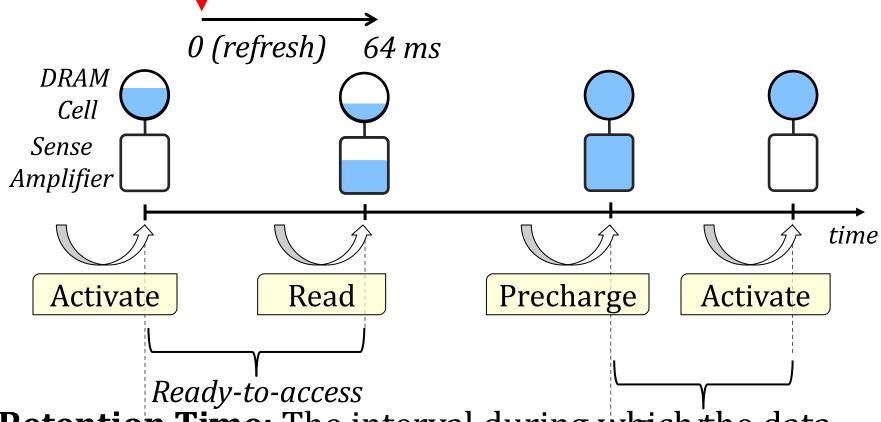

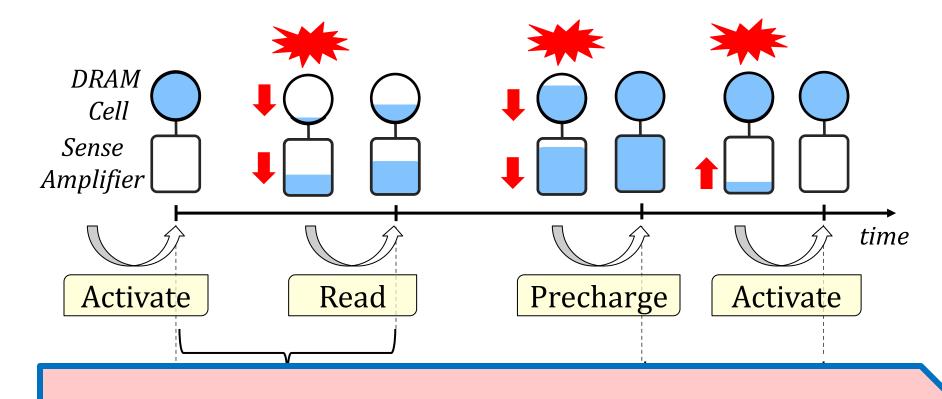

## **Accessing DRAM**

### **DRAM Latency**

Retention Timen The interval during which the data is retained correctly in the DRAM cell with our accessing it

### Latency vs. Reliability

Violating latencies negatively affects DRAM reliability

### Other Factors Affecting Reliability and Latency

- Temperature

- Voltage

- Inter-cell Interference

- Manufacturing Process

- Reten

• ...

To develop new mechanisms improving reliability and latency, we need to better understand the effects of these factors

### **Characterizing DRAM**

Many of the factors affecting DRAM reliability and latency cannot be properly modeled

We need to perform experimental studies of real DRAM chips

## Prior Research Enabled by SoftMC

#### EDEN: Enabling Energy-Efficient, High-Performance Deep Neural Network Inference Using Approximate DRAM

Skanda Koppula Lois Orosa A. Giray Yağlıkçı Roknoddin Azizi Taha Shahroodi Konstantinos Kanellopoulos Onur Mutlu ETH Zürich

### TRRespass: Exploiting the Many Sides of Target Row Refresh

Pietro Frigo\*† Emanuele Vannacci\*† Hasan Hassan§ Victor van der Veen¶

Onur Mutlu§ Cristiano Giuffrida\* Herbert Bos\* Kaveh Razavi\*

\*Vrije Universiteit Amsterdam

§ETH Zürich

¶Qualcomm Technologies Inc.

†Equal contribution joint first authors

#### D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

Jeremie S. Kim<sup>‡§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§‡</sup>

<sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

#### What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study

Saugata Ghose<sup>†</sup> Abdullah Giray Yağlıkçı\*<sup>†</sup> Raghav Gupta<sup>†</sup> Donghyuk Lee<sup>‡</sup>

Kais Kudrolli<sup>†</sup> William X. Liu<sup>†</sup> Hasan Hassan\* Kevin K. Chang<sup>†</sup>

Niladrish Chatterjee<sup>‡</sup> Aditya Agrawal<sup>‡</sup> Mike O'Connor<sup>‡</sup>⋄ Onur Mutlu\*<sup>†</sup>

<sup>†</sup>Carnegie Mellon University \*ETH Zürich <sup>‡</sup>NVIDIA Research °The University of Texas at Austin

#### Understanding Reduced-Voltage Operation in Modern DRAM Chips: Characterization, Analysis, and Mechanisms

Kevin K. Chang $^{\dagger}$  Abdullah Giray Yağlıkçı $^{\dagger}$  Saugata Ghose $^{\dagger}$  Aditya Agrawal $^{\P}$  Niladrish Chatterjee $^{\P}$  Abhijith Kashyap $^{\dagger}$  Donghyuk Lee $^{\P}$  Mike O'Connor $^{\P,\ddagger}$  Hasan Hassan $^{\S}$  Onur Mutlu $^{\S,\dagger}$

<sup>‡</sup>The University of Texas at Austin

#### ComputeDRAM: In-Memory Compute Using Off-the-Shelf DRAMs

<sup>¶</sup>NVIDIA

Fei Gao feig@princeton.edu Department of Electrical Engineering Princeton University

<sup>†</sup>Carnegie Mellon University

Georgios Tziantzioulis georgios.tziantzioulis@princeton.edu Department of Electrical Engineering Princeton University

David Wentzlaff wentzlaf@princeton.edu Department of Electrical Engineering Princeton University

§ETH Zürich

#### Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content

Samira Khan\* Chris Wilkerson<sup>†</sup> Zhe Wang<sup>†</sup> Alaa R. Alameldeen<sup>†</sup> Donghyuk Lee<sup>‡</sup> Onur Mutlu\*

\*University of Virginia <sup>†</sup>Intel Labs <sup>‡</sup>Nvidia Research \*ETH Zürich

#### Understanding Latency Variation in Modern DRAM Chips: Experimental Characterization, Analysis, and Optimization

Kevin K. Chang¹ Abhijith Kashyap¹ Hasan Hassan¹,²

Saugata Ghose¹ Kevin Hsieh¹ Donghyuk Lee¹ Tianshi Li¹,³

Gennady Pekhimenko¹ Samira Khan⁴ Onur Mutlu⁵,¹

¹Carnegie Mellon University ²TOBB ETÜ ³Peking University ⁴University of Virginia ⁵ETH Zürich

### **SoftMC**

- FPGA-based DRAM characterization infrastructure

- Ability to test any DRAM operation

- Ability to test any combination of DRAM operations and custom timing parameters

- Simple programming interface (C++)

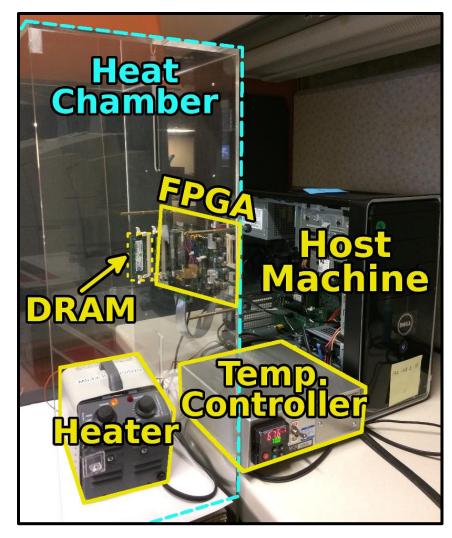

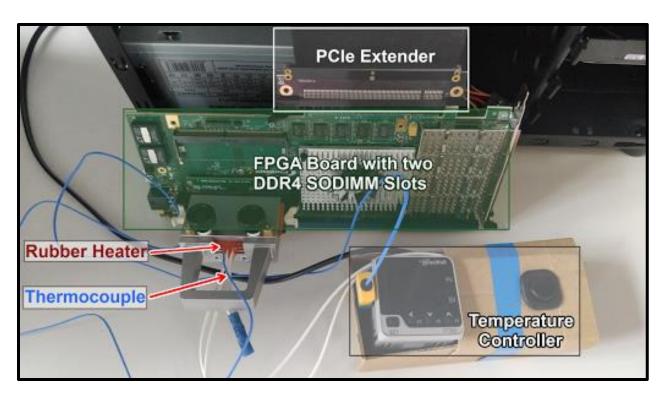

## **Current SoftMC Setups**

DDR4

DDR3

# SoftMC Programming DEMO