# **P&S Processing-in-Memory**

Real-World Processing-in-Memory Architectures: Alibaba Hybrid Bonding PNM Engine

> Dr. Juan Gómez Luna Prof. Onur Mutlu ETH Zürich Spring 2022 12 May 2022

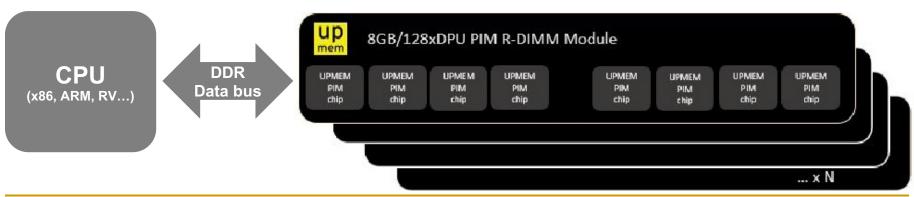

UPMEM Processing-in-DRAM Engine (2019)

### Processing in DRAM Engine

Includes standard DIMM modules, with a large number of DPU processors combined with DRAM chips.

### Replaces standard DIMMs

- DDR4 R-DIMM modules

- 8GB+128 DPUs (16 PIM chips)

- Standard 2x-nm DRAM process

Large amounts of compute & memory bandwidth

https://www.anandtech.com/show/14750/hot-chips-31-analysis-inmemory-processing-by-upmem

https://www.upmem.com/video-upmem-presenting-its-true-processing-in-memory-solution-hot-chips-2019/

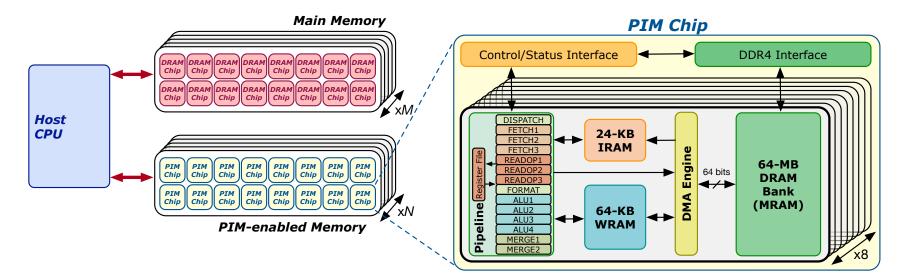

## **UPMEM PIM System Organization**

- A UPMEM DIMM contains 8 or 16 chips

- Thus, 1 or 2 ranks of 8 chips each

- Inside each PIM chip there are:

- 8 64MB banks per chip: Main RAM (MRAM) banks

- 8 DRAM Processing Units (DPUs) in each chip, 64 DPUs per rank

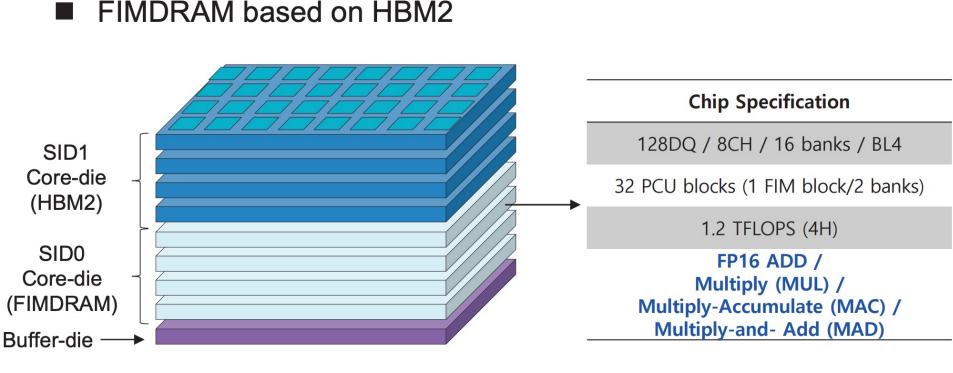

### FIMDRAM: Chip Structure

[3D Chip Structure of HBM with FIMDRAM]

### FIMDRAM: System Organization (III)

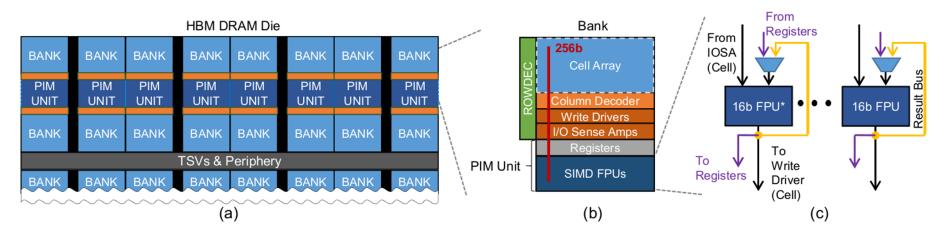

- PIM units respond to standard DRAM column commands (RD or WR)

- Compliant with unmodified JEDEC controllers

- They execute one wide-SIMD operation commanded by a PIM instruction with deterministic latency in a lock-step manner

- A PIM unit can get 16 16-bit operands from IOSAs, a register, and/or the result bus

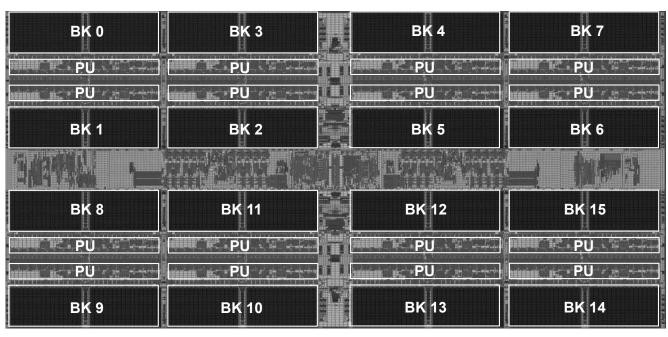

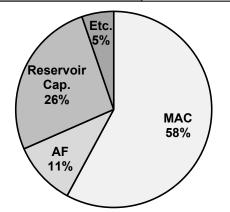

## AiM: Chip Implementation

4 Gb AiM die with 16 processing units (PUs)

#### AiM Die Photograph

#### 1 Process Unit (PU) Area

| Total                    | 0.19mm <sup>2</sup> |

|--------------------------|---------------------|

| MAC                      | 0.11mm <sup>2</sup> |

| Activation Function (AF) | 0.02mm <sup>2</sup> |

| Reservoir Cap.           | 0.05mm <sup>2</sup> |

| Etc.                     | 0.01mm <sup>2</sup> |

Lee et al., A 1ynm 1.25V 8Gb, 16Gb/s/pin GDDR6-based Accelerator-in-Memory supporting 1TFLOPS MAC Operation and Various Activation Functions for Deep-Learning Applications, ISSCC 2022

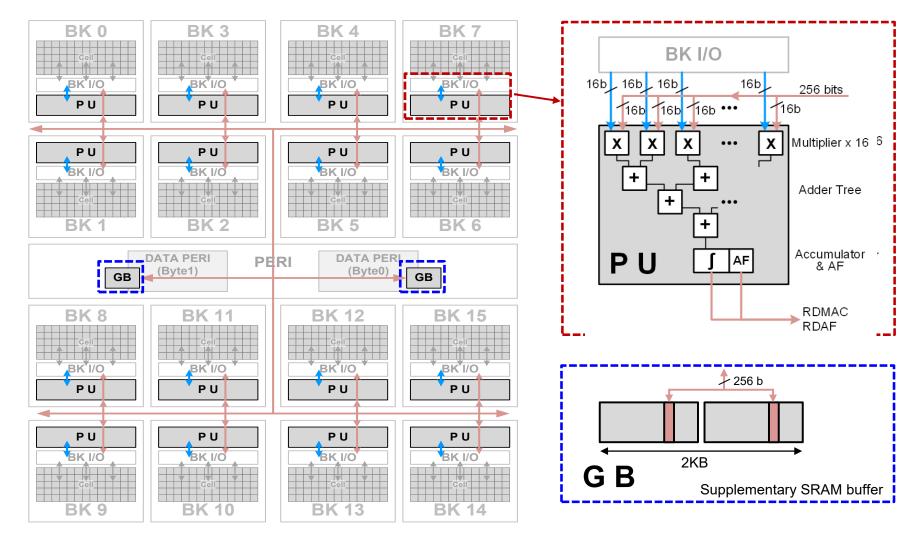

## AiM: System Organization

#### GDDR6-based AiM architecture

Lee et al., A 1ynm 1.25V 8Gb, 16Gb/s/pin GDDR6-based Accelerator-in-Memory supporting 1TFLOPS MAC Operation and Various Activation Functions for Deep-Learning Applications, ISSCC 2022

7

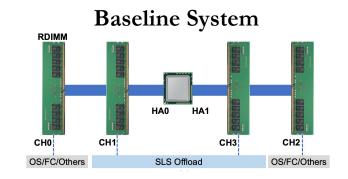

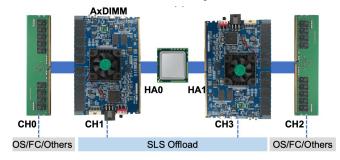

### Samsung AxDIMM (2021)

- DIMM-based PIM

- DLRM recommendation system

AxDIMM System

### AxDIMM Design: Hardw

Ke et al. "Near-Memory Processing<sup>2</sup>i<sup>hit</sup>Action: <sup>Abit</sup>celeratin<sup>1</sup>/<sub>2</sub><sup>pie</sup>rsonali<sup>1</sup>/<sub>2</sub><sup>bit</sup>Recommendation with AxDIMM", IEEE Micro (2021)

Alibaba 3D Logic-to-DRAM Hybrid Bonding with Processing-near-Memory Engine

### **ISSCC 2022 / SESSION 29 / ML CHIPS FOR EMERGING A**

#### 29.1 184QPS/W 64Mb/mm<sup>2</sup> 3D Logic-to-DRAM Hybrid Bonding with Process-Near-Memory Engine for Recommendation System

Dimin Niu<sup>1</sup>, Shuangchen Li<sup>1</sup>, Yuhao Wang<sup>1</sup>, Wei Han<sup>1</sup>, Zhe Zhang<sup>2</sup>, Yijin Guan<sup>2</sup>, Tianchan Guan<sup>3</sup>, Fei Sun<sup>1</sup>, Fei Xue<sup>1</sup>, Lide Duan<sup>1</sup>, Yuanwei Fang<sup>1</sup>, Hongzhong Zheng<sup>1</sup>, Xiping Jiang<sup>4</sup>, Song Wang<sup>4</sup>, Fengguo Zuo<sup>4</sup>, Yubing Wang<sup>4</sup>, Bing Yu<sup>4</sup>, Qiwei Ren<sup>4</sup>, Yuan Xie<sup>1</sup>

<sup>1</sup>Alibaba DAMO Academy, Sunnyvale, CA; <sup>2</sup>Alibaba DAMO Academy, Beijing, China <sup>3</sup>Alibaba DAMO Academy, Shanghai, China; <sup>4</sup>UniIC, Xian, China

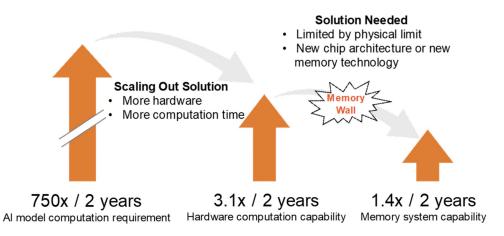

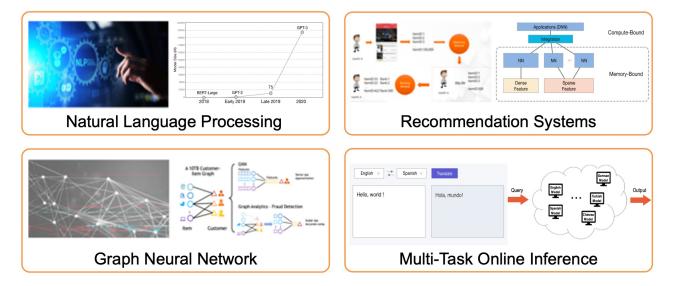

### Processing-in-Memory for Machine Learning

#### Memory bandwidth is not enough for many ML workloads

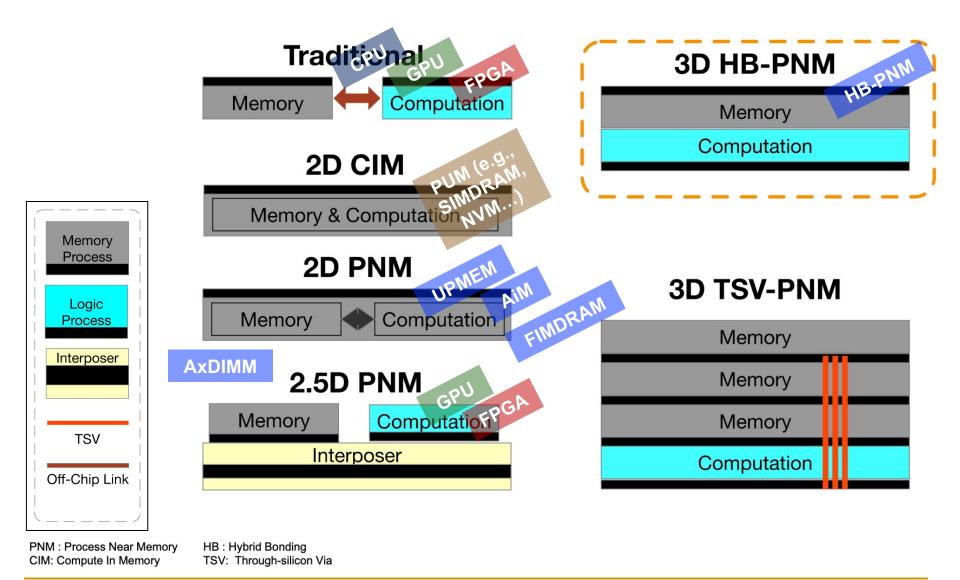

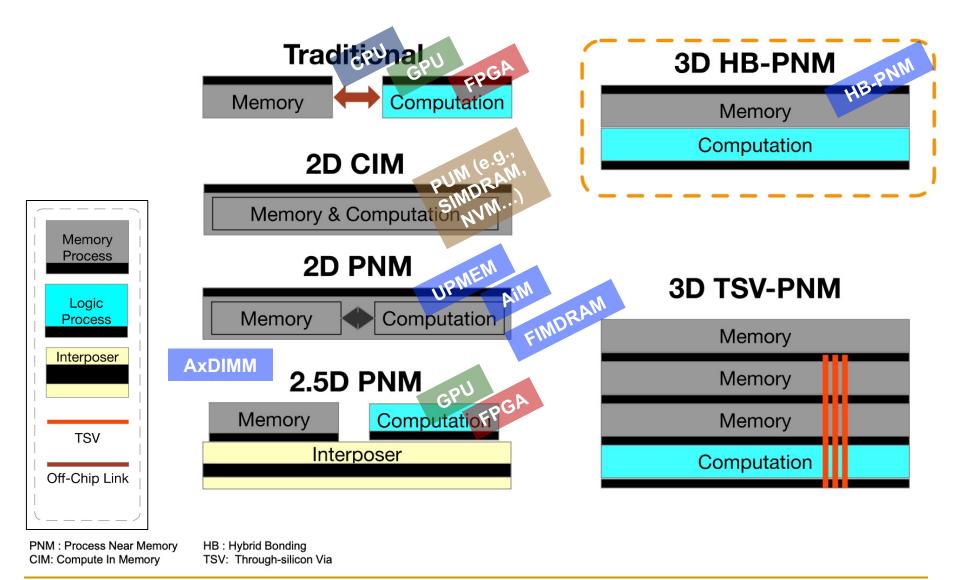

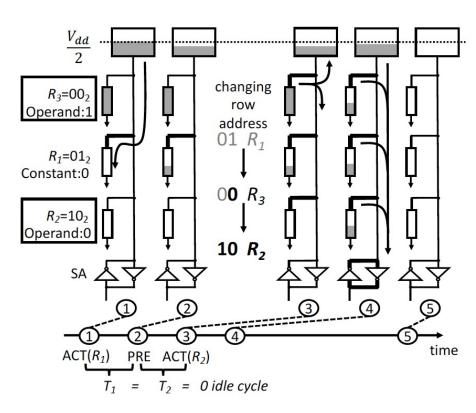

### Processing-in-Memory Classification

Niu et al., 184QPS/W 64Mb/mm2 3D Logic-to-DRAM Hybrid Bonding with Process-Near-Memory Engine for Recommendation System, ISSCC 2022

## Two PIM Approaches

5.2. Two Approaches: Processing Using Memory (PUM) vs. Processing Near Memory (PNM)

Many recent works take advantage of the memory technology innovations that we discuss in Section 5.1 to enable and implement PIM. We find that these works generally take one of two approaches, which are categorized in Table 1: (1) *processing using memory* or (2) *processing near memory*. We briefly describe each approach here. Sections 6 and 7 will provide example approaches and more detail for both.

| Table 1: Summary of enabling technologies for the two approaches to |  |

|---------------------------------------------------------------------|--|

| PIM used by recent works. Adapted from [309].                       |  |

| Approach                | Enabling Technologies                                                                               |

|-------------------------|-----------------------------------------------------------------------------------------------------|

| Processing Using Memory | SRAM<br>DRAM<br>Phase-change memory (PCM)<br>Magnetic RAM (MRAM)<br>Resistive RAM (RRAM)/memristors |

| Processing Near Memory  | Logic layers in 3D-stacked memory<br>Silicon interposers<br>Logic in memory controllers             |

**Processing using memory (PUM)** exploits the existing memory architecture and the operational principles of the memory circuitry to enable operations within main memory with minimal changes. PUM makes use Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "A Modern Primer on Processing in Memory" Invited Book Chapter in <u>Emerging</u> <u>Computing: From Devices to Systems -</u> <u>Looking Beyond Moore and Von Neumann</u>,

Springer, to be published in 2021. [Tutorial Video on "Memory-Centric Computing Systems" (1 hour 51 minutes)]

# A Modern Primer on Processing in Memory

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b,c</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>d</sup>

SAFARI Research Group

<sup>a</sup>ETH Zürich <sup>b</sup>Carnegie Mellon University <sup>c</sup>University of Illinois at Urbana-Champaign <sup>d</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "A Modern Primer on Processing in Memory" *Invited Book Chapter in <u>Emerging Computing: From Devices to Systems -</u> <i>Looking Beyond Moore and Von Neumann*, Springer, to be published in 2021.

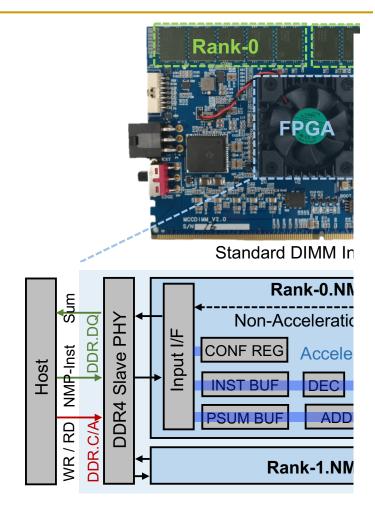

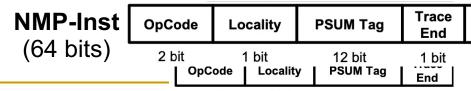

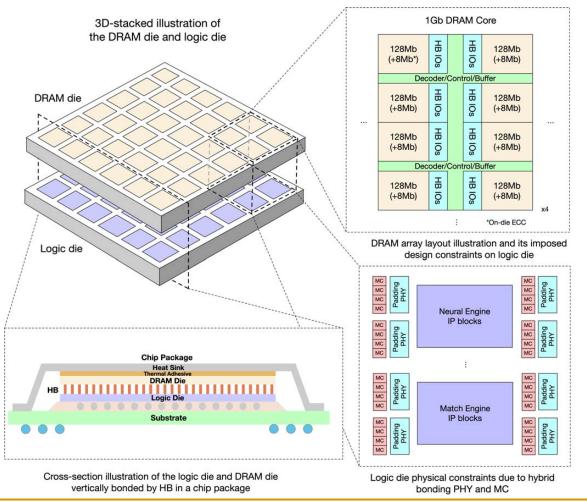

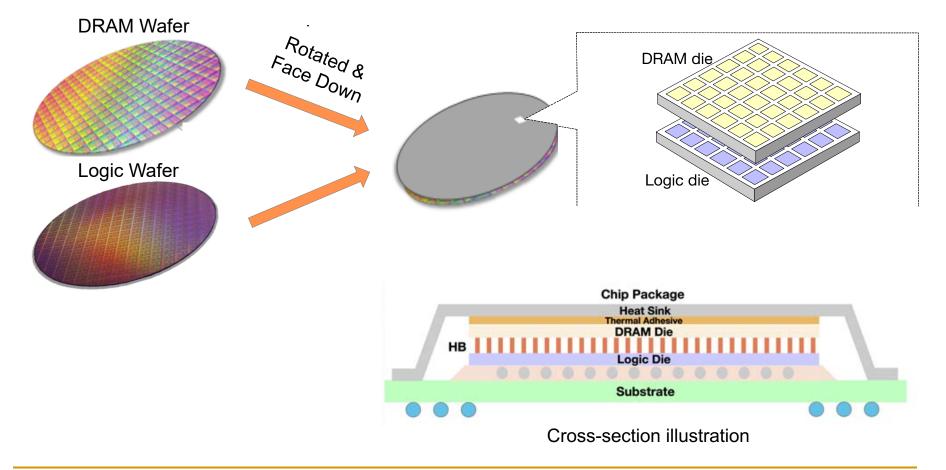

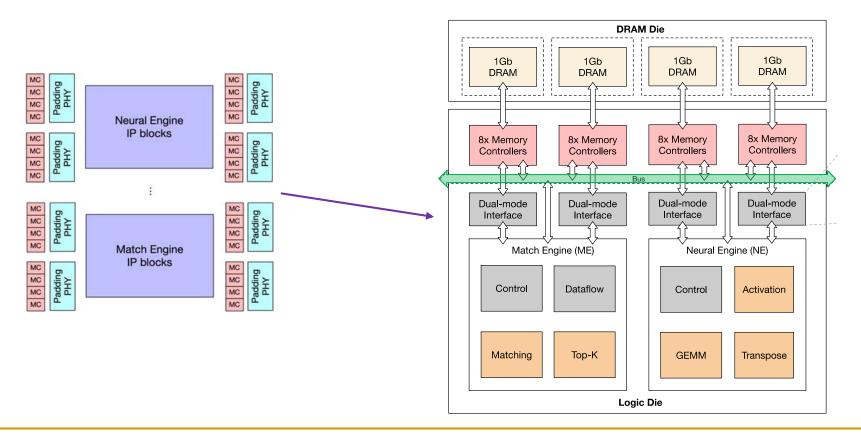

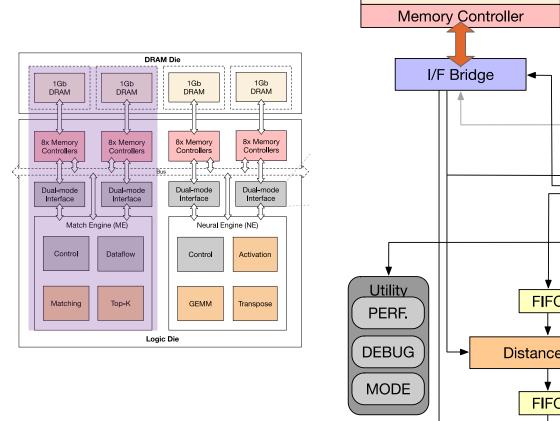

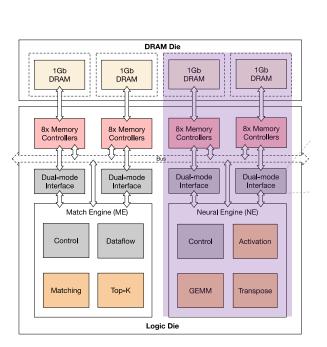

### HB-PNM: Overall Architecture (I)

3D-stacked logic die and DRAM die vertically bonded by hybrid bonding (HB)

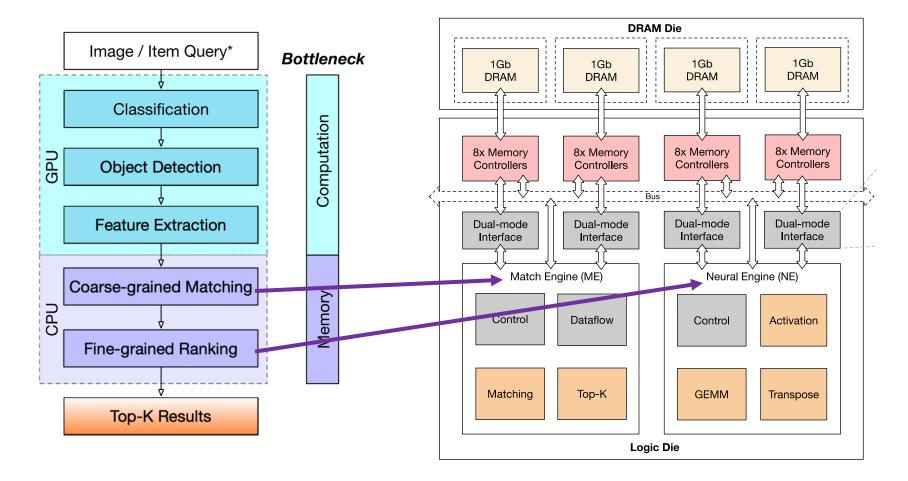

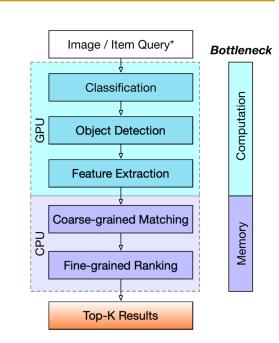

### HB-PNM: Overall Architecture (II)

Match engine and neural engine for matching and ranking in a recommendation system

# Recommendation Systems

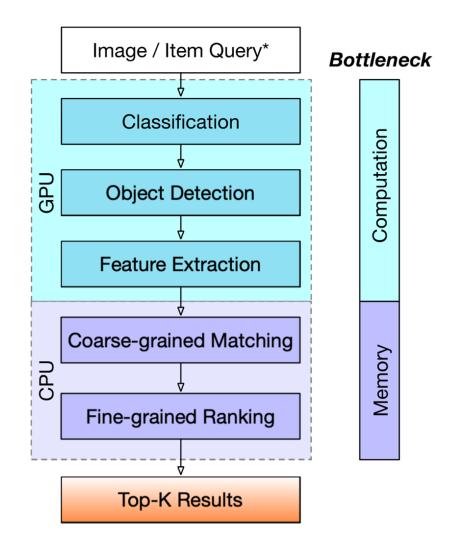

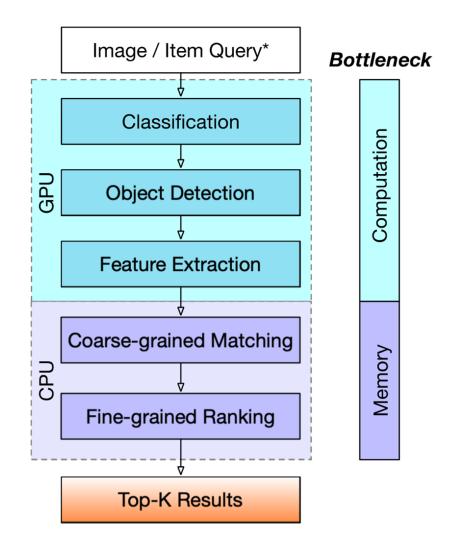

### Feature Generation + Matching & Ranking

### Recommendation system

- Feature generation

- Classification, object detection, feature extraction

- Compute-bound

- Good fit for GPU

- Matching and ranking

- Coarse-grained matching, fine-grained ranking

- Memory-bound

- Most latency (89.87%) and energy (82.97%)

- Typically run on CPU

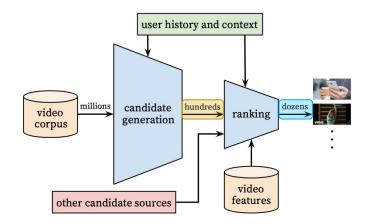

### **Recommendation Systems**

Candidate recommendations are retrieved and then ranked

Covington et al., Deep Neural Networks for YouTube Recommendations, RecSys 2016

Naumov et al., Deep Learning Recommendation Model for Personalization and Recommendation Systems, arXiv:1906.00091, 2019

Li et al., iMARS: An In-Memory-Computing Architecture for Recommendation Systems, arXiv:2202.09433, 2022

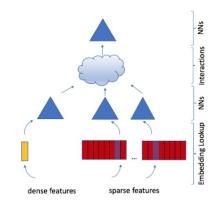

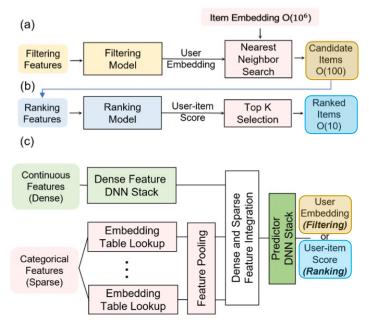

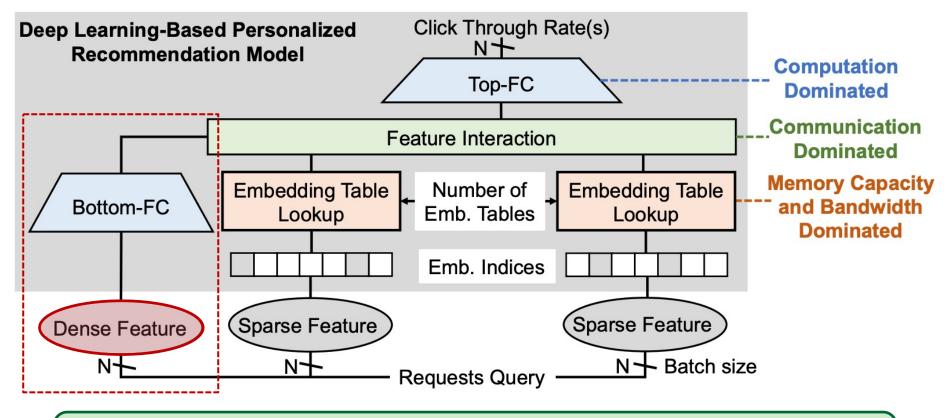

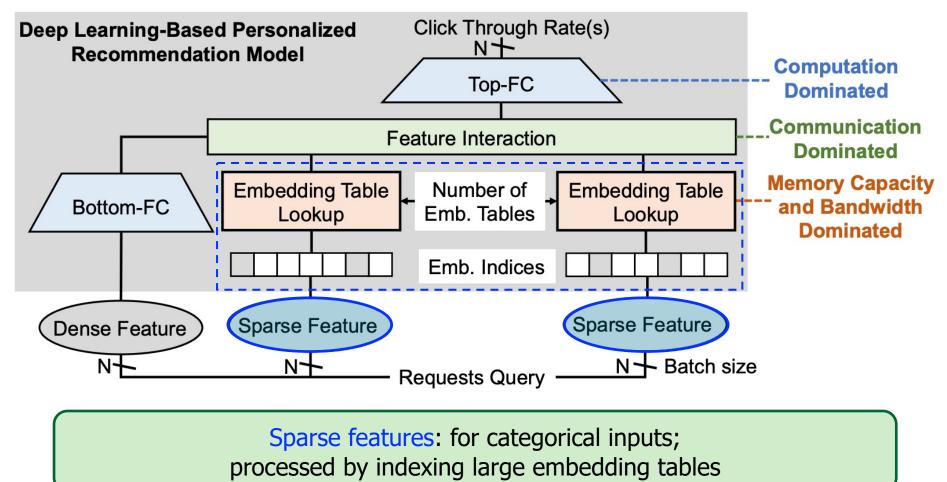

### Overview of Recommendation Models

Personalized recommendation: recommend content to users, e.g., Facebook's DLRM recommendation system

Dense features: continuous inputs in vectors and matrices are processed by typical DNN layers (e.g., fully connected layers)

### Overview of Recommendation Models

Personalized recommendation: recommend content to users, e.g., Facebook's DLRM recommendation system

### Overview of Recommendation Models

Personalized recommendation: recommend content to users, e.g., Facebook's DLRM recommendation system

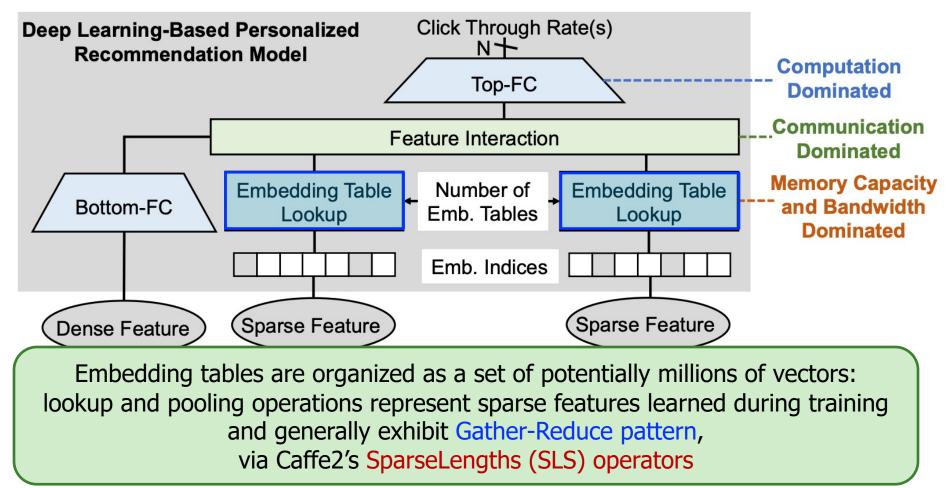

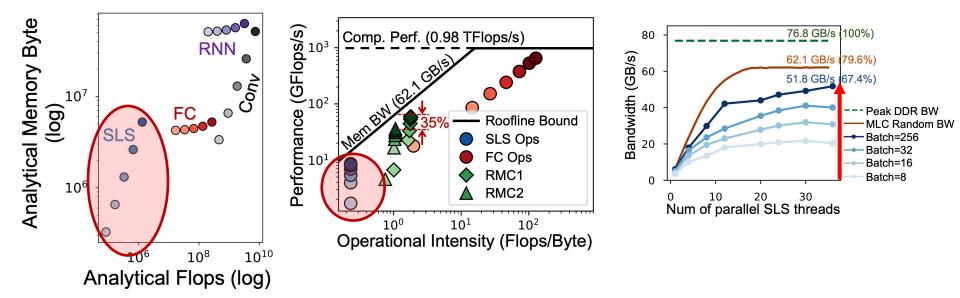

### **DLRM** Performance Characterization

#### Identifying key performance bottlenecks for the DLRM system

#### SparseLengths (SLS) operators:

- Low FP intensity

- Larger batch size:

- Higher memory footprint

- Higher memory intensity

The memory bandwidth can easily be saturated by embedding operations especially as both the batch size and the number of threads increase

### Feature Generation + Matching & Ranking

### Recommendation system

- Feature generation

- Classification, object detection, feature extraction

- Compute-bound

- Good fit for GPU

- Matching and ranking

- Coarse-grained matching, fine-grained ranking

- Memory-bound

- Most latency (89.87%) and energy (82.97%)

- Typically run on CPU

# Matching & Ranking

- Coarse-grained matching

- Binary feature vectors with 512 dimensions

- Distance calculation

- Top-1000 items selected from 40K items

- Fine-grained ranking

- Features with 8 bits x 1024 dimensions

- 3-layer MLP (2048-256-64-1) for similarity prediction

Top-100 ranking results from 1K items

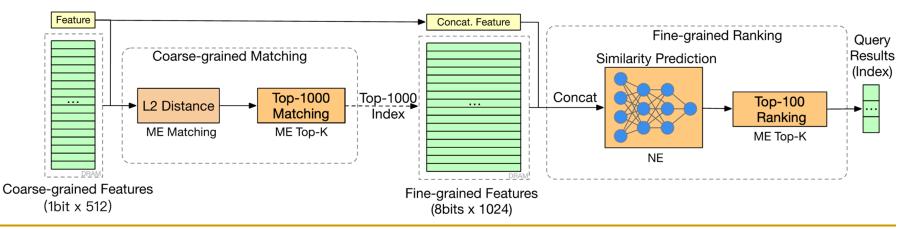

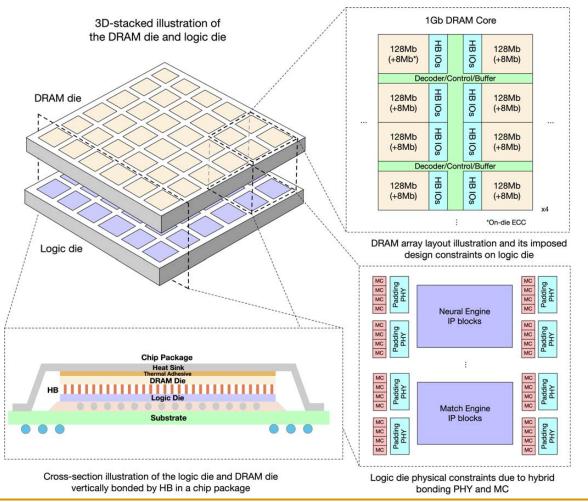

3D Logic-to-DRAM Hybrid Bonding

### HB-PNM: Overall Architecture (I)

3D-stacked logic die and DRAM die vertically bonded by hybrid bonding (HB)

## HB-PNM: Chip Implementation

- 3D Logic-to-DRAM Hybrid Bonding

- Face-to-face hybrid wafer bonding

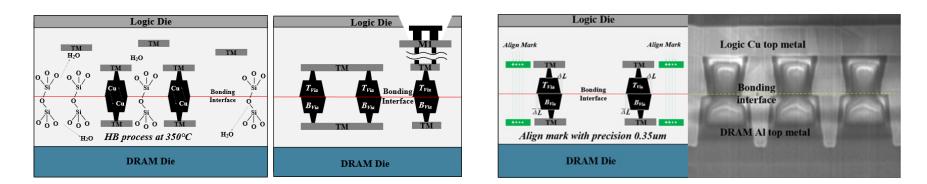

### HB-PNM: Hybrid-Bonding Interconnection

- 3D Logic-to-DRAM Hybrid Bonding

- Face-to-face hybrid wafer bonding

- Logic and memory manufactured independently: this avoids the challenges of integrating logic into memory chips

- Cu-Cu direct fusion with low bonding temperature (<350°C)</li>

- Much denser vias than other 3D-stacking technologies

- Low pitch size (3 um) vs. HBM microbumps (35 um<sup>1</sup>)

- High inter-layer bandwidth (1.38 TB/s) vs. HBM2E (460 GB/s<sup>2</sup>)

<sup>1</sup> Kim et al. Signal Integrity and Computing Performance Analysis of a Processing-In-Memory of High Bandwidth Memory (PIM-HBM) Scheme, IEEE TCPMT, 2021 <sup>2</sup> <u>https://product.skhynix.com/products/dram/hbm/hbm2e.go</u>

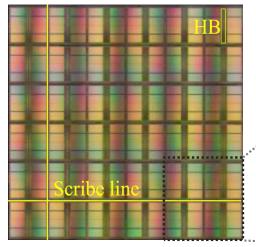

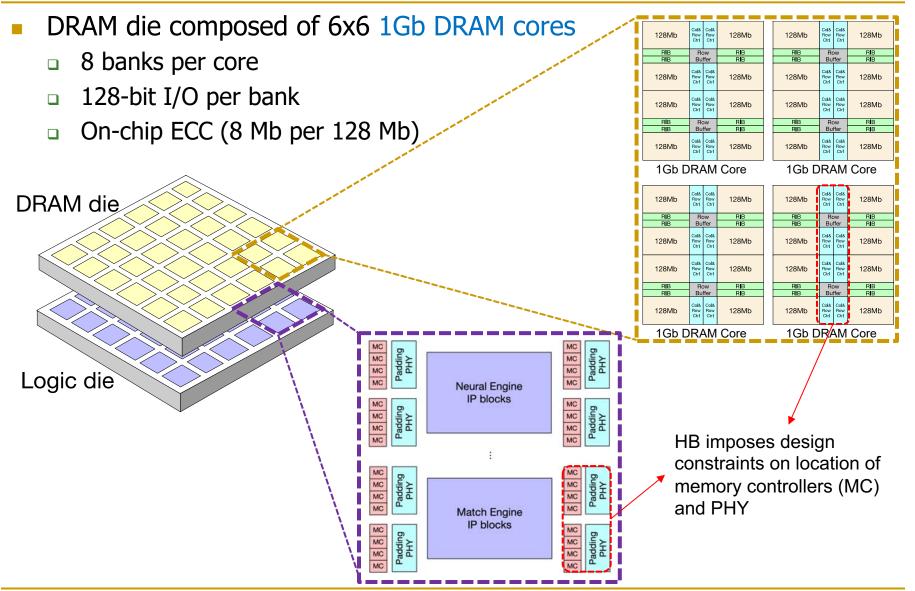

### HB-PNM: DRAM Die and Logic Die

#### DRAM die and logic die

DRAM Die Photo (36Gb)

| Neural Engine Region     |                      |       |  |  |

|--------------------------|----------------------|-------|--|--|

| MC                       | NE IP                | MC    |  |  |

| 5.90 mm <sup>2</sup> 5 E |                      |       |  |  |

|                          |                      | gieri |  |  |

| PHY                      | ME IP                | PHY   |  |  |

| мс                       | 7.02 mm <sup>2</sup> | MC    |  |  |

| DRAM Die        |                         |                        |

|-----------------|-------------------------|------------------------|

| Technology      | 25nm                    |                        |

|                 | Total*                  | 602.22 mm <sup>2</sup> |

| Area            | Neural Engine           | 32 mm <sup>2</sup>     |

|                 | Match Engine            | 32 mm²                 |

| Voltage         | 1.1 V                   |                        |

| Frequency (max) | 150 MHz                 |                        |

| Power           | 300 mW per 1Gb          |                        |

| Bandwidth**     | 153.60 GB/s / 1.38 TB/s |                        |

| Logic Die  |               |                        |  |

|------------|---------------|------------------------|--|

| Technology | 55nm          |                        |  |

|            | Total*        | 602.22 mm <sup>2</sup> |  |

| Area       | Neural Engine | 5.90 mm <sup>2</sup>   |  |

|            | Match Engine  | 7.02 mm <sup>2</sup>   |  |

| # of MC    | 16 per IP     |                        |  |

| Voltage    | 1.2 V         |                        |  |

| Frequency  | 300 MHz       |                        |  |

| Power      | 977.70 mW     |                        |  |

| Precision  | INT8          |                        |  |

# HB-PNM Architecture

### HB-PNM Architecture

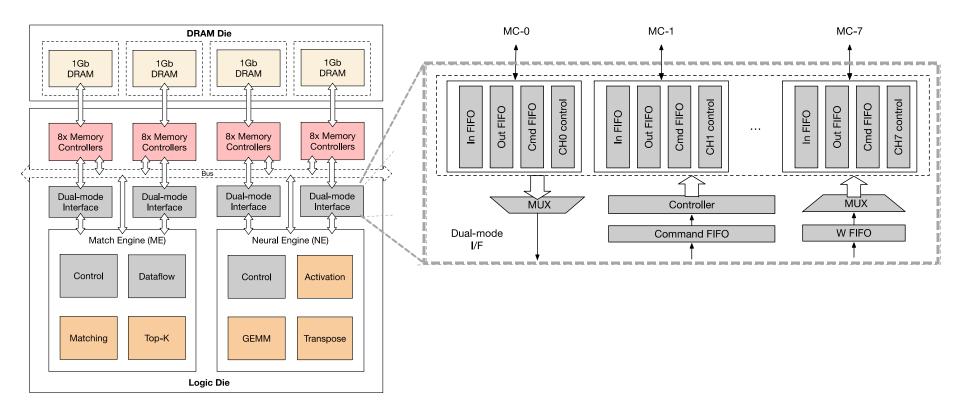

## HB-PNM: Logic Die

- Match engine and neural engine for matching and ranking in a recommendation system

- Direct access to their counterpart DRAM blocks

- Access to other DRAM blocks via on-chip bus

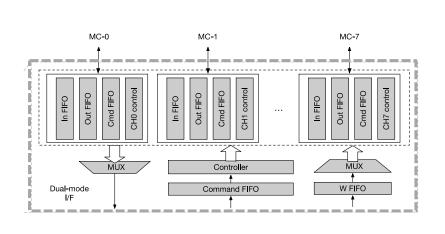

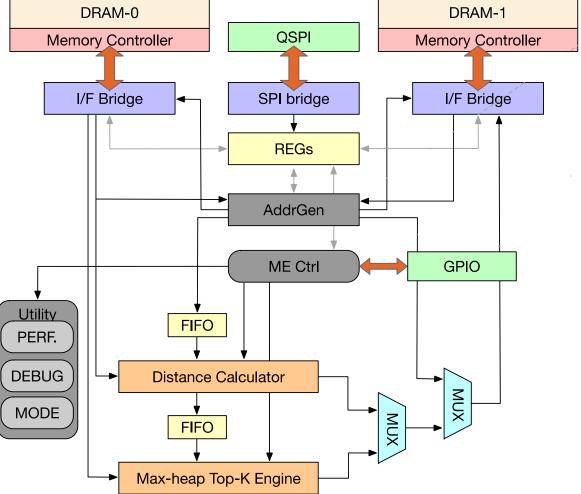

### HB-PNM Logic Die: Dual-mode Interface

- Dual-mode interface can switch between

- All 8 banks in lock-step for full bandwidth

- Single channel (1 of 8 banks)

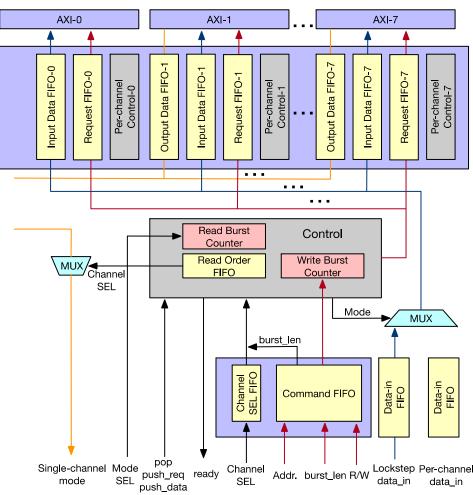

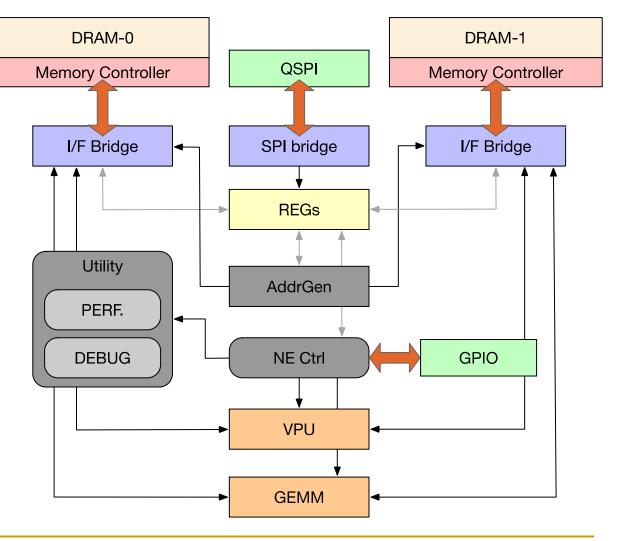

## Neural Engine: Interface Bridge

- Support for single-channel mode and lockstep mode

- Read/write counters to support burst requests

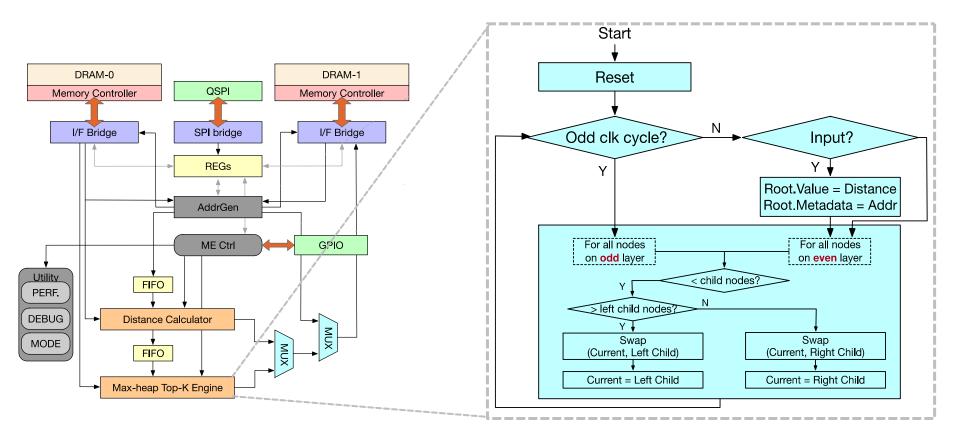

#### HB-PNM: Match Engine

#### Responsible for coarse-grained matching

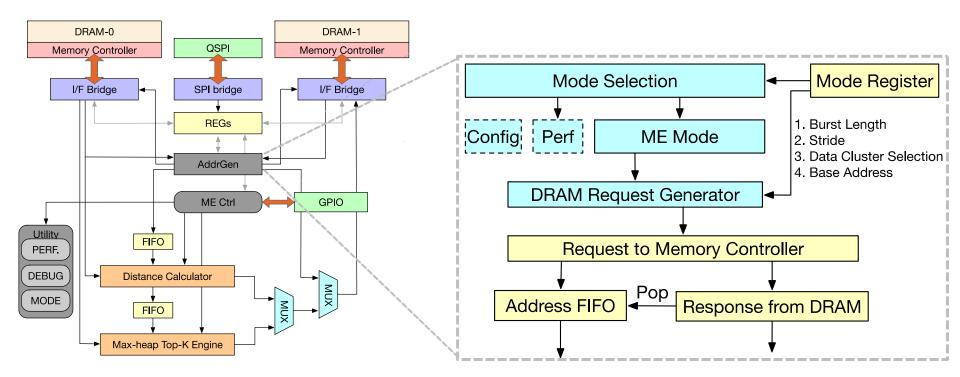

### Match Engine: Address Generator

- AddGen generates the address of the input query

- Mode selection for different access patterns

- Configurable via registers

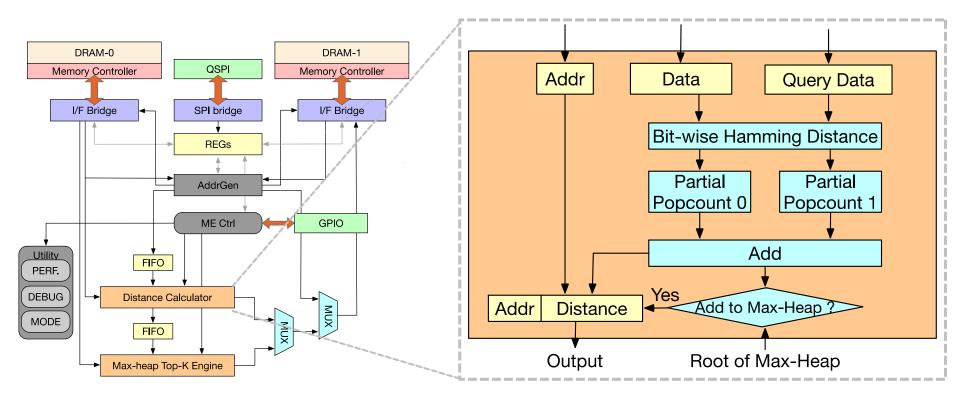

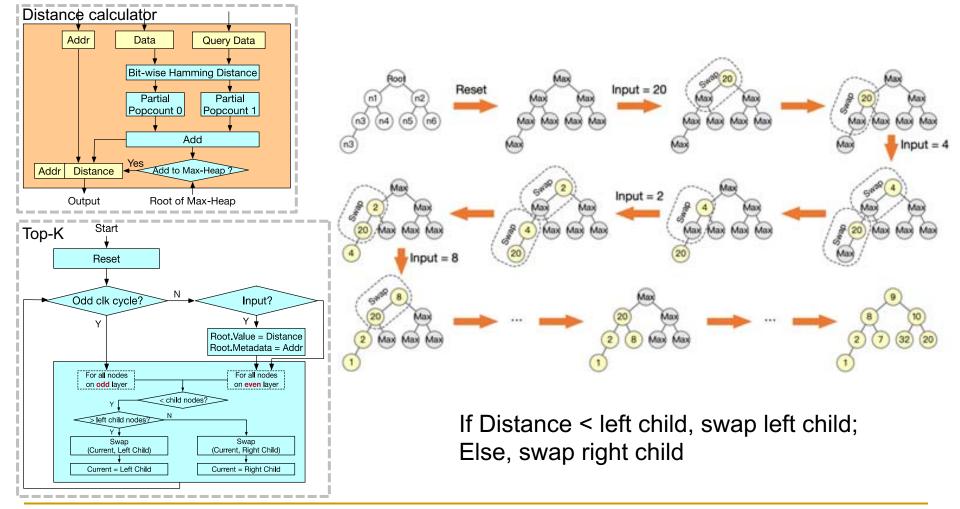

## Match Engine: Distance Calculator

- Distance calculator obtains similarity between input query and feature vectors

- It computes Hamming distance of two 512-bit vectors

- Distance is filtered by root of max-heap

## Match Engine: Top-K Engine (I)

- Max-heap hardware block and data structure with 1000 nodes <address, distance> for the 1000 shortest distances

- New input every two cycles

## Match Engine: Top-K Engine (II)

Max-heap hardware block and data structure with 1000 nodes <address, distance> for the 1000 shortest distances

#### HB-PNM: Neural Engine

Responsible for similarity prediction for fine-grained ranking

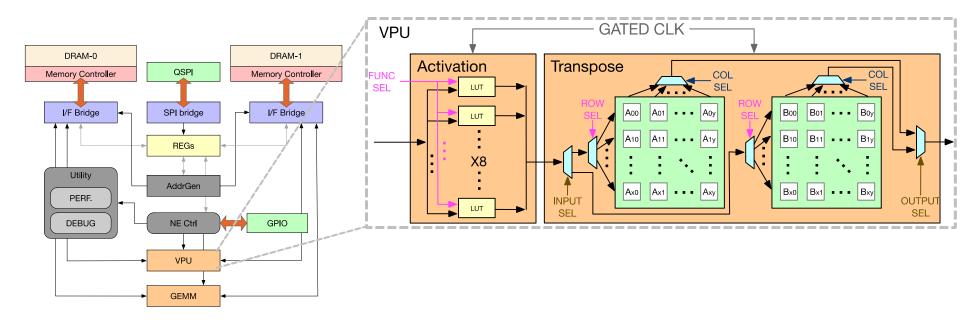

### Neural Engine: Vector Processing Unit

- Activations based on LUTs

- Support for GeLU and Exp

- Transpose

- Transpose 16x16 matrix with ping-pong array

- 2D register file array

- Row-based writes and column-based reads

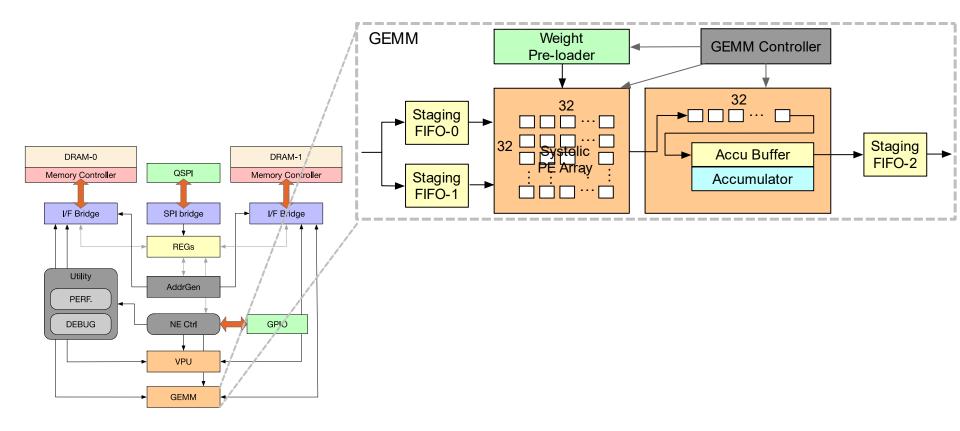

#### Neural Engine: GEMM

- 32x32 INT8 fully-pipelined systolic array

- Partial sums accumulated in INT32 accumulator

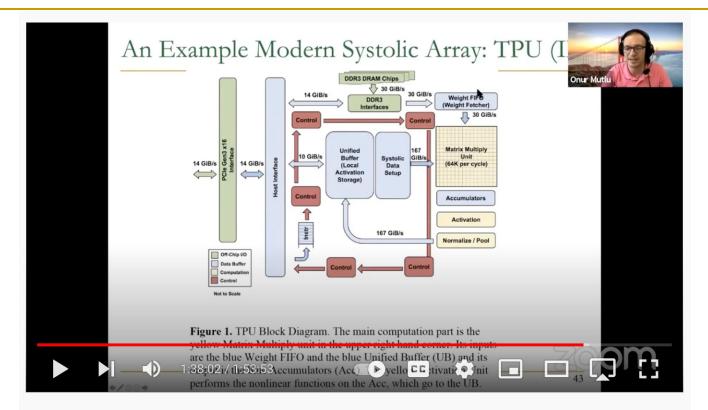

#### Lecture on Systolic Arrays

Digital Design & Computer Arch. - Lecture 19: VLIW, Systolic Arrays, DAE (ETH Zürich, Spring 2021)

#### https://youtu.be/UtLy4Yagdys?t=2948

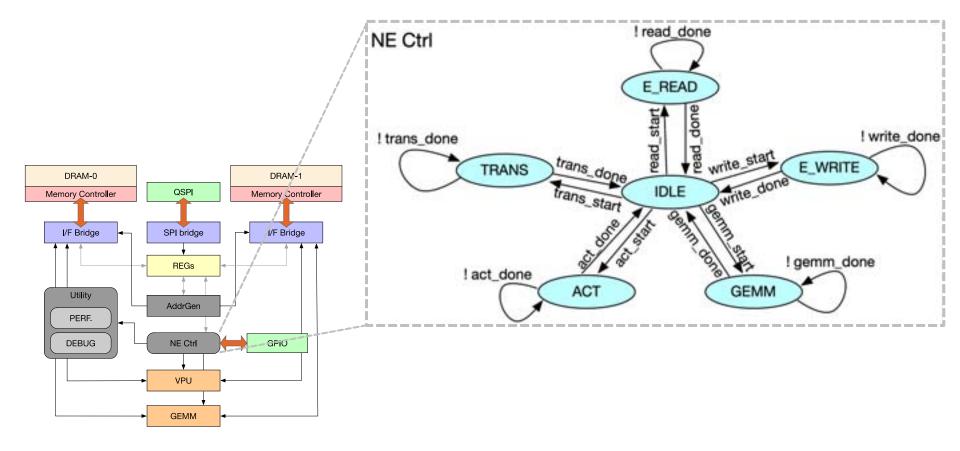

#### Neural Engine: Finite State Machine

- Five working states and one idle state

- Each working state is for one instruction

#### HB-PNM: Key Feature Summary

#### Comparison table

|                           | 2D CIM * | UPMEM PIM **   | A100 GPU *** | FIMDRAM ****     | This work      |

|---------------------------|----------|----------------|--------------|------------------|----------------|

| Type of Memory            | SRAM     | DDR4           | HBM2         | HBM2             | LPDDR4         |

| Technology (Memory/Logic) | 16nm     | 2xnm / 2xnm    | 1y# / 7nm    | 20nm / 20nm      | 25nm / 55nm    |

| Capacity                  | 4.5 Mb   | 8GB / DIMM     | 80GB         | 6GB / cube       | 4.5GB          |

| Bandwidth                 | -        | 128GB/s / DIMM | 1935GB/s     | 1200GB/s / cube# | 38.4GB/s / 1Gb |

| Frequency (Logic)         | 200MHz   | 500MHz         | 1410MHz      | 300MHz           | 300MHz         |

| Bandwidth/Capacity (a.u.) | -        | 16             | 24.2         | 200              | 307            |

| Energy                    | -        | ~25pJ/bit      | 4.47pJ/bit   | 2.75pJ/bit       | 0.88pJ/bit     |

\* H. Jia et al, ISSCC 2021.

\*\* F. Devaux et al, Hotchip 2019

\*\*\* J. Choquette et al, Hotchip 2020

\*\*\*\* Y. C. Kwon et al, ISSCC 2021

#### Processing-in-Memory Classification

### Two PIM Approaches

5.2. Two Approaches: Processing Using Memory (PUM) vs. Processing Near Memory (PNM)

Many recent works take advantage of the memory technology innovations that we discuss in Section 5.1 to enable and implement PIM. We find that these works generally take one of two approaches, which are categorized in Table 1: (1) *processing using memory* or (2) *processing near memory*. We briefly describe each approach here. Sections 6 and 7 will provide example approaches and more detail for both.

| Table 1: Summary of enabling technologies for the two approaches to |  |

|---------------------------------------------------------------------|--|

| PIM used by recent works. Adapted from [309].                       |  |

| Approach                | Enabling Technologies                                                                               |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| Processing Using Memory | SRAM<br>DRAM<br>Phase-change memory (PCM)<br>Magnetic RAM (MRAM)<br>Resistive RAM (RRAM)/memristors |  |  |

| Processing Near Memory  | Logic layers in 3D-stacked memory<br>Silicon interposers<br>Logic in memory controllers             |  |  |

**Processing using memory (PUM)** exploits the existing memory architecture and the operational principles of the memory circuitry to enable operations within main memory with minimal changes. PUM makes use Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "A Modern Primer on Processing in Memory" Invited Book Chapter in <u>Emerging</u> <u>Computing: From Devices to Systems -</u> <u>Looking Beyond Moore and Von Neumann</u>, Springer, to be published in 2021.

[Tutorial Video on "Memory-Centric Computing Systems" (1 hour 51 minutes)]

#### Similarities and Differences among Current PIM Systems

- Similarities

- Current real-world processing-in-memory architectures follow a processing-near-memory approach

- All based on DRAM memory

- Differences

- Near-bank (UPMEM, FIMDRAM, AiM, HB-PNM) vs. near-chip (AxDIMM)

- General-purpose (UPMEM) vs. special-function (FIMDRAM, AiM, HB-PNM)

- FGMT (UPMEM) vs. SIMD (FIMDRAM, AiM, AxDIMM) vs. systolic array (HB-PNM)

- Natively integer (UPMEM, HB-PNM) vs. floating point (FIMDRAM)

- FP16 (FIMDRAM) vs. BF16 (AiM) vs. FP32 (AxDIMM)

- DDR4 (UPMEM, AxDIMM) vs. LPDDR4 (HB-PNM) vs. HBM2 (FIMDRAM) vs. GDDR6 (AiM)

#### Processing-in-Memory Classification

#### ComputeDRAM: In-Memory Compute Using Off-the-Shelf DRAMs

Fei Gao feig@princeton.edu Department of Electrical Engineering Princeton University Georgios Tziantzioulis georgios.tziantzioulis@princeton.edu Department of Electrical Engineering Princeton University David Wentzlaff wentzlaf@princeton.edu Department of Electrical Engineering Princeton University

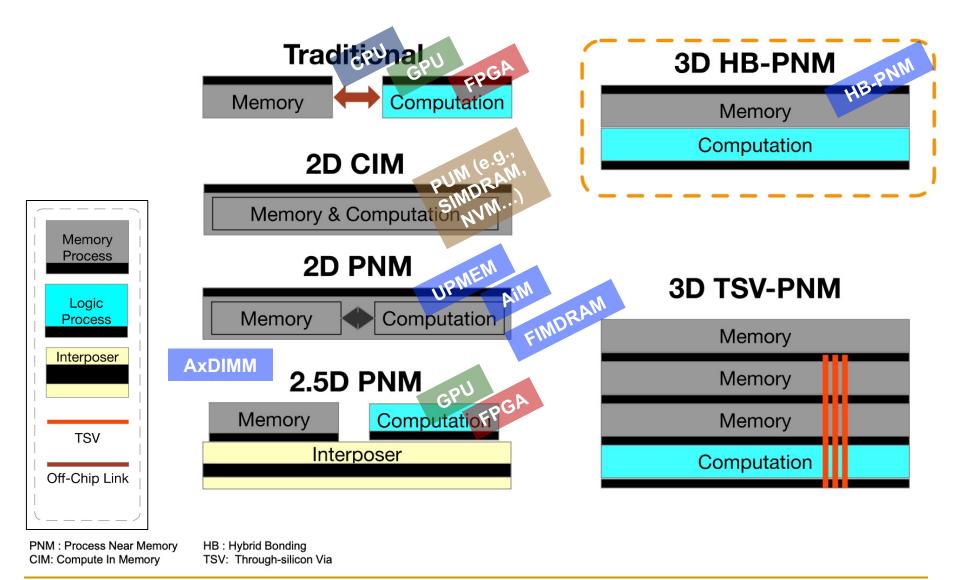

#### SoftMC: Open Source DRAM Infrastructure

Hasan Hassan et al., "<u>SoftMC:</u> <u>A Flexible and Practical</u> <u>Open-Source Infrastructure</u> <u>for Enabling Experimental</u> <u>DRAM Studies</u>," HPCA 2017

- Flexible

- Easy to Use (C++ API)

- Open-source github.com/CMU-SAFARI/SoftMC

#### RowClone & Bitwise Ops in Real DRAM Chips

#### MICRO-52, October 12-16, 2019, Columbus, OH, USA

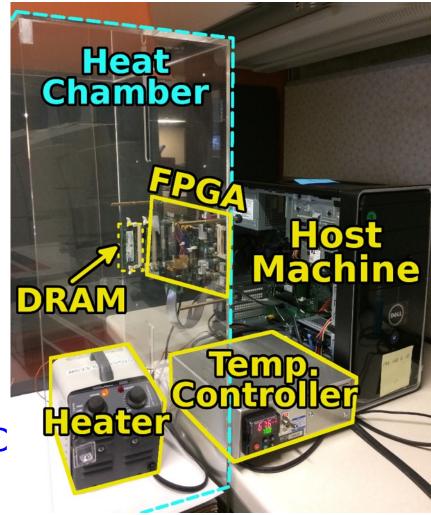

$\frac{V_{dd}}{2}$   $R_{1}$   $R_{2}$   $R_{3}$   $R_{4}$   $R_{5}$   $R_{4}$   $R_{5}$   $R_{4}$   $R_{5}$   $R_{1}$   $R_{2}$   $R_{3}$   $R_{4}$   $R_{5}$   $R_{1}$   $R_{2}$   $R_{3}$   $R_{4}$   $R_{5}$   $R_{1}$   $R_{2}$   $R_{1}$   $R_{2}$   $R_{2}$   $R_{2}$   $R_{2}$   $R_{2}$   $R_{3}$   $R_{4}$   $R_{5}$   $R_{1}$   $R_{1}$   $R_{2}$   $R_{1}$   $R_{2}$   $R_{3}$   $R_{4}$   $R_{2}$   $R_{2}$   $R_{2}$   $R_{2}$   $R_{3}$   $R_{4}$   $R_{2}$   $R_{2}$   $R_{3}$   $R_{4}$   $R_{2}$   $R_{2}$   $R_{3}$   $R_{4}$   $R_{2}$   $R_{4}$   $R_{4}$   $R_{2}$   $R_{4}$   $R_{4}$

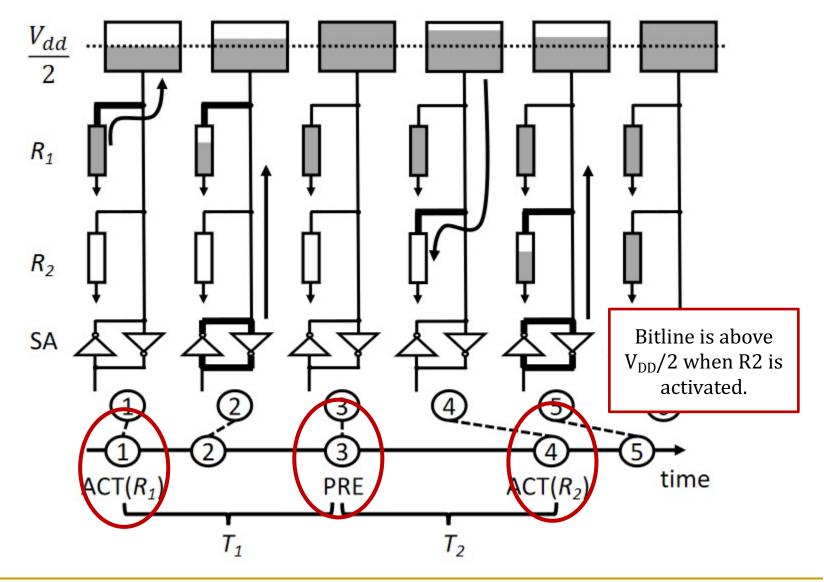

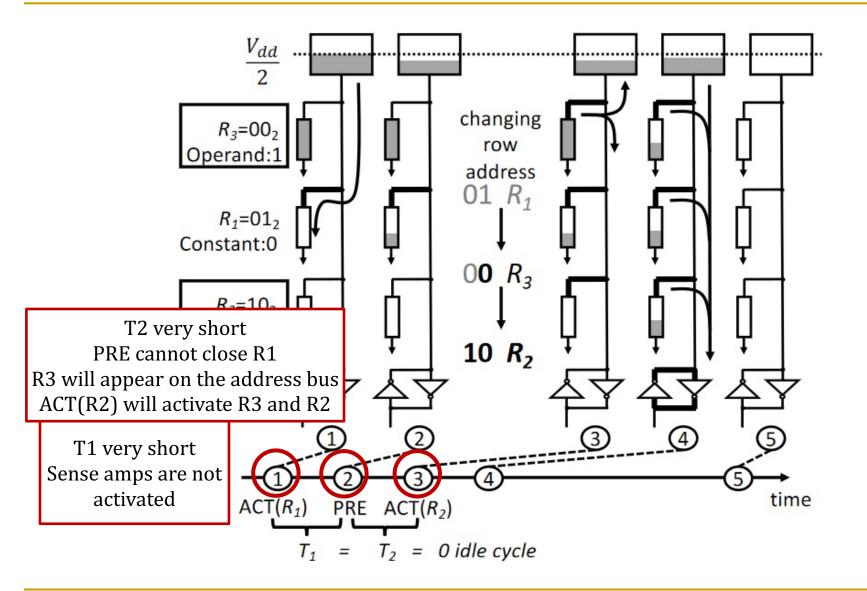

Figure 4: Timeline for a single bit of a column in a row copy operation. The data in  $R_1$  is loaded to the bit-line, and overwrites  $R_2$ .

Figure 5: Logical AND in ComputeDRAM.  $R_1$  is loaded with constant zero, and  $R_2$  and  $R_3$  store operands (0 and 1). The result (0 = 1  $\land$  0) is finally set in all three rows.

Gao et al.

### Row Copy in ComputeDRAM

### Bitwise AND in ComputeDRAM

## Experimental Methodology (I)

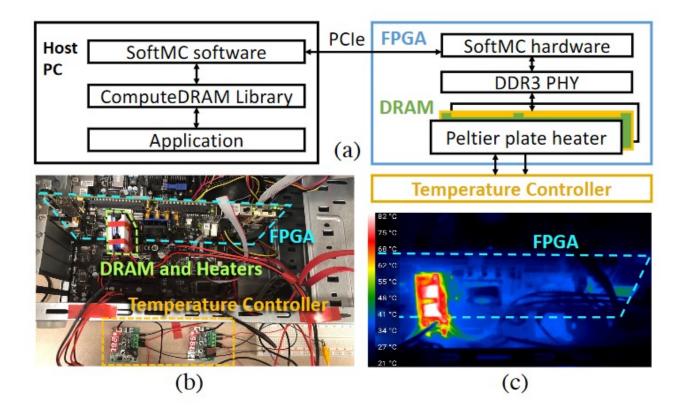

Figure 9: (a) Schematic diagram of our testing framework. (b) Picture of our testbed. (c) Thermal picture when the DRAM is heated to 80 °C.

### Experimental Methodology (II)

#### **Table 1: Evaluated DRAM modules**

| Group ID:<br>Vendor_Size_Freq(MHz) | Part Num               | # Modules |

|------------------------------------|------------------------|-----------|

| SKhynix_2G_1333                    | HMT325S6BFR8C-H9       | 6         |

| SKhynix_4C_1066                    | HMT451S6MMP8C-C7       | 2         |

| SKhynix_4                          |                        | 2         |

| SKhynix_4                          |                        | 4         |

| SKhynix_4 32 DD                    | <b>32</b> DDR3 Modules |           |

| Samsung_4                          |                        | 2         |

| Samsung_4 ~256                     | DRAM Chips             | 2         |

| Micron_2G                          | L                      | 2         |

| Micron_2G                          |                        | 2         |

| Elpida_2G_1333                     | EBJ21UE8BDS0-DJ-F      | 2         |

| Nanya_4G_1333                      | NT4GC64B8HG0NS-CG      | 2         |

| TimeTec_4G_1333                    | 78AP10NUS2R2-4G        | 2         |

| Corsair_4G_1333                    | CMSA8GX3M2A1333C9      | 2         |

## Proof of Concept (I)

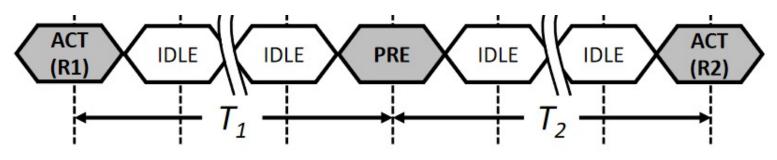

- How they test these memory modules:

- Vary  $T_1$  and  $T_2$ , observe what happens.

#### SoftMC Experiment

- 1. Select a random subarray

- 2. Fill subarray with random data

- 3. Issue ACT-PRE-ACTs with given  $T_1 \& T_2$

- 4. Read out subarray

- 5. Find out how many columns in a row support either operation

- Row-wise success ratio

## Proof of Concept (II)

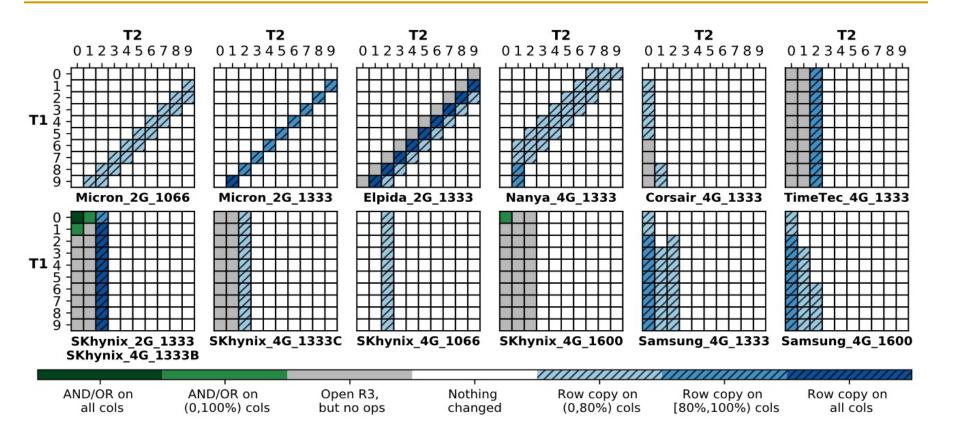

Each grid represents the success ratio of operations for a specific DDR3 module.

#### ComputeDRAM: In-Memory Compute Using Off-the-Shelf DRAMs

Fei Gao feig@princeton.edu Department of Electrical Engineering Princeton University Georgios Tziantzioulis georgios.tziantzioulis@princeton.edu Department of Electrical Engineering Princeton University David Wentzlaff wentzlaf@princeton.edu Department of Electrical Engineering Princeton University

## PnM and PuM Working Synergistically

Maciej Besta, Raghavendra Kanakagiri, Grzegorz Kwasniewski, Rachata Ausavarungnirun, Jakub Beránek, Konstantinos Kanellopoulos, Kacper Janda, Zur Vonarburg-Shmaria, Lukas Gianinazzi, Ioana Stefan, Juan Gómez-Luna, Marcin Copik, Lukas Kapp-Schwoerer, Salvatore Di Girolamo, Nils Blach, Marek Konieczny, Onur Mutlu, and Torsten Hoefler, "SISA: Set-Centric Instruction Set Architecture for Graph Mining on Processing-in-Memory Systems"

Proceedings of the <u>54th International Symposium on Microarchitecture</u> (**MICRO**), Virtual, October 2021. [Older arXiv version]

#### SISA: Set-Centric Instruction Set Architecture for Graph Mining on Processing-in-Memory Systems

Maciej Besta<sup>1</sup>, Raghavendra Kanakagiri<sup>2</sup>, Grzegorz Kwasniewski<sup>1</sup>, Rachata Ausavarungnirun<sup>3</sup>, Jakub Beránek<sup>4</sup>, Konstantinos Kanellopoulos<sup>1</sup>, Kacper Janda<sup>5</sup>, Zur Vonarburg-Shmaria<sup>1</sup>, Lukas Gianinazzi<sup>1</sup>, Ioana Stefan<sup>1</sup>, Juan Gómez Luna<sup>1</sup>, Marcin Copik<sup>1</sup>, Lukas Kapp-Schwoerer<sup>1</sup>, Salvatore Di Girolamo<sup>1</sup>, Marek Konieczny<sup>5</sup>, Onur Mutlu<sup>1</sup>, Torsten Hoefler<sup>1</sup>

<sup>1</sup> ETH Zurich <sup>2</sup> IIT Tirupati <sup>3</sup> King Mongkut's University of Technology North Bangkok <sup>4</sup> Technical University of Ostrava <sup>5</sup> AGH-UST

## Upcoming Lectures

PUM architectures and prototypes

- Case studies

- □ SpMV on UPMEM PIM architecture

- Neural network accelerators for the edge

- Hybrid transactional and analytical processing (HTAP) databases

Enabling the adoption of PIM

# **P&S Processing-in-Memory**

Real-World Processing-in-Memory Architectures: Alibaba Hybrid Bonding PNM Engine

> Dr. Juan Gómez Luna Prof. Onur Mutlu ETH Zürich Spring 2022 12 May 2022