# P&S Processing-in-Memory

Programming

Processing-in-Memory Architectures

Dr. Juan Gómez Luna

Prof. Onur Mutlu

ETH Zürich

Spring 2022

21 April 2022

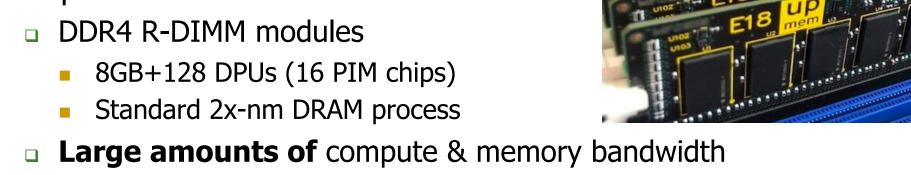

### UPMEM Processing-in-DRAM Engine (2019)

- Processing in DRAM Engine

- Includes standard DIMM modules, with a large number of DPU processors combined with DRAM chips.

- Replaces standard DIMMs

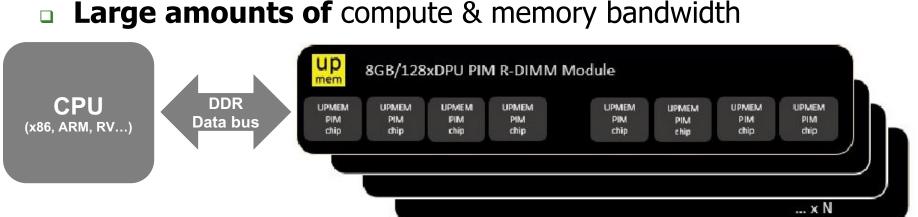

### **System Organization**

- A UPMEM DIMM contains 8 or 16 chips

- Thus, 1 or 2 ranks of 8 chips each

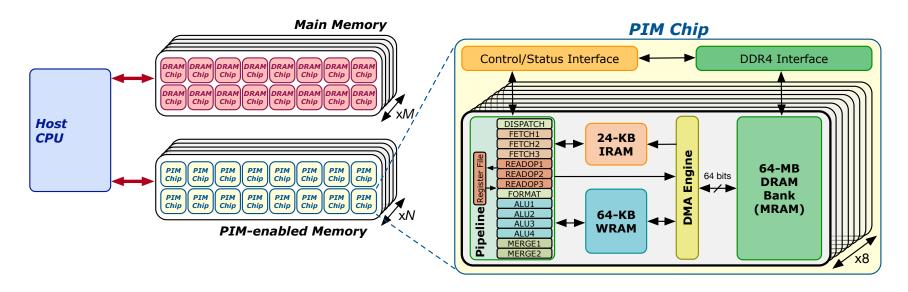

- Inside each PIM chip there are:

- 8 64MB banks per chip: Main RAM (MRAM) banks

- 8 DRAM Processing Units (DPUs) in each chip, 64 DPUs per rank

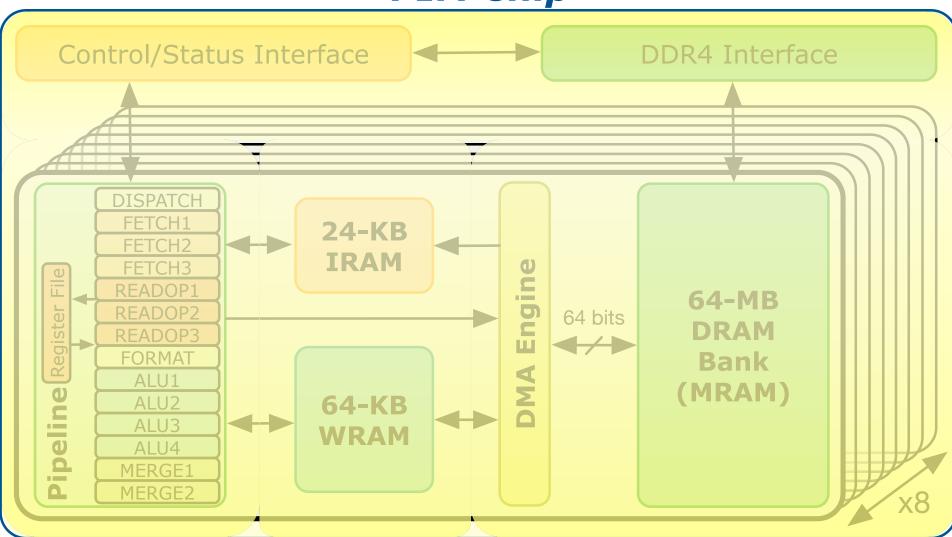

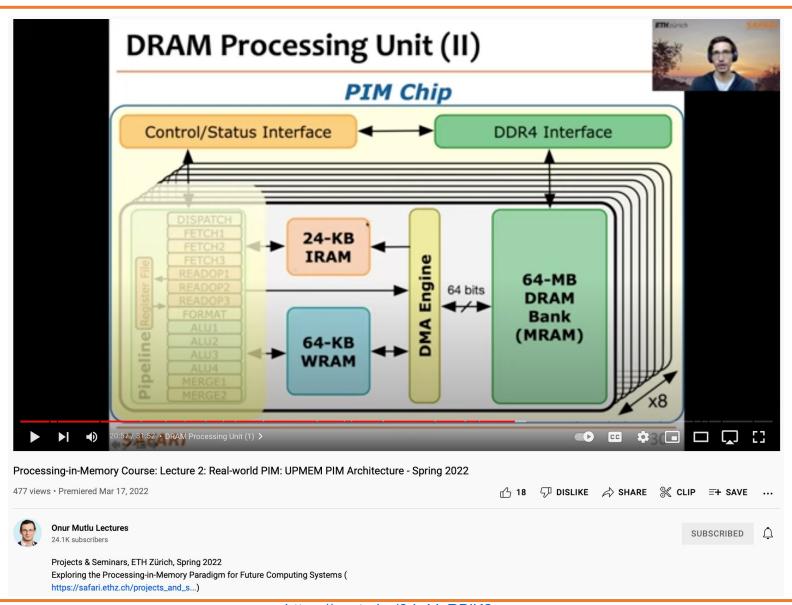

## **DRAM Processing Unit**

PIM Chip

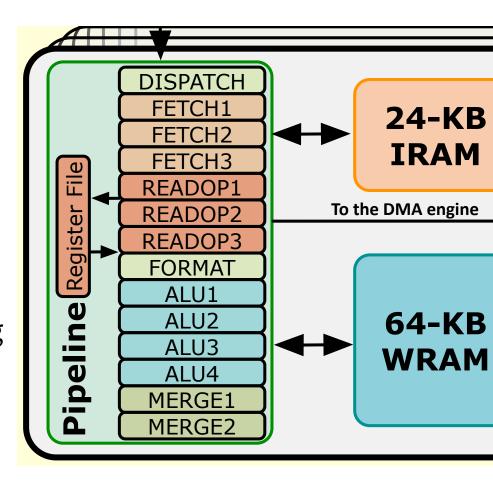

### **DPU Pipeline**

- In-order pipeline

- Up to 425 MHz \*

- Fine-grain multithreaded

- 24 hardware threads

- 14 pipeline stages

- DISPATCH: Thread selection

- FETCH: Instruction fetch

- READOP: Register file

- FORMAT: Operand formatting

- ALU: Operation and WRAM

- MERGE: Result formatting

<sup>\* 350</sup> MHz in the UPMEM-based PIM system used for the experimental results shown in this lecture

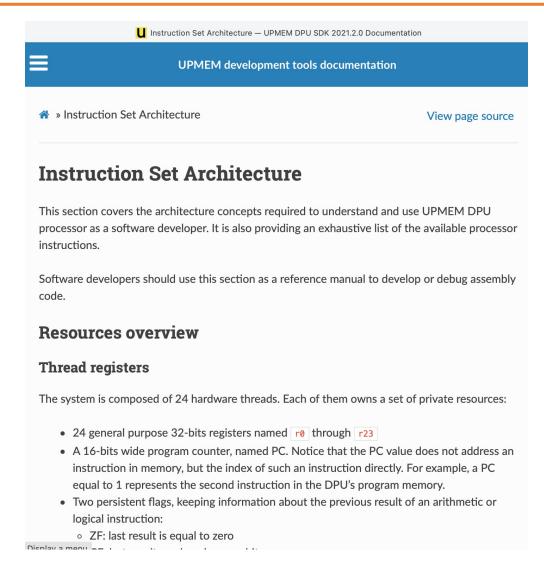

#### **DPU Instruction Set Architecture**

- Specific 32-bit ISA

- Aiming at scalar, inorder, and multithreaded implementation

- Allowing compilation of 64-bit C code

- LLVM/Clang compiler

https://sdk.upmem.com/2021.2.0/201\_IS.html#

### **UPMEM PIM Architecture: Lectures 2 & 3**

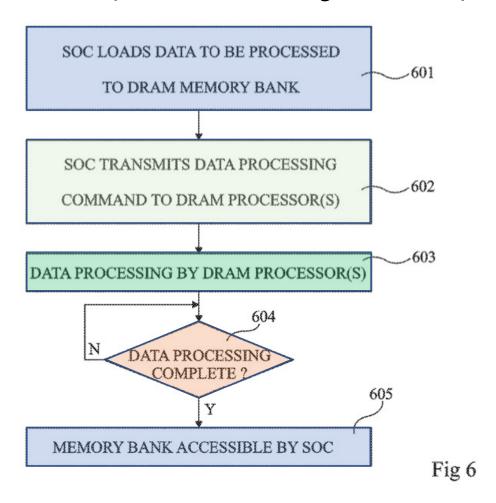

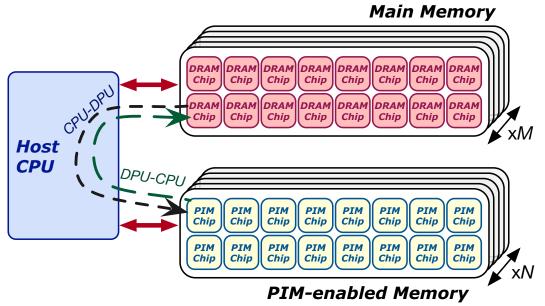

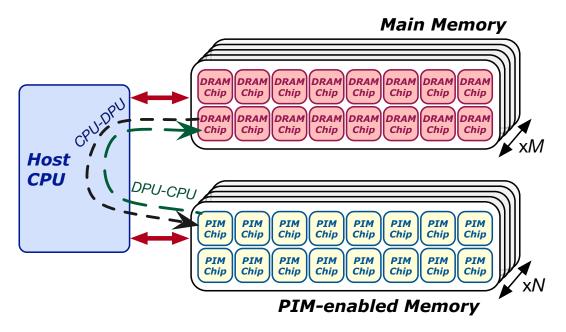

### **Accelerator Model (I)**

- UPMEM DIMMs coexist with conventional DIMMs

- Integration of UPMEM DIMMs in a system follows an accelerator model

- UPMEM DIMMs can be seen as a loosely coupled accelerator

- Explicit data movement between the main processor (host CPU) and the accelerator (UPMEM)

- Explicit kernel launch onto the UPMEM processors

- This resembles GPU computing

### **Accelerator Model (II)**

FIG. 6 is a flow diagram representing operations in a method of delegating a processing task to a DRAM processor according to an example embodiment

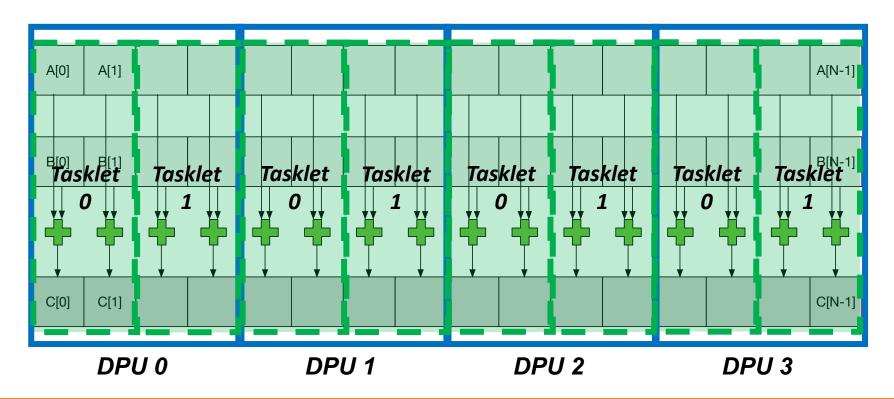

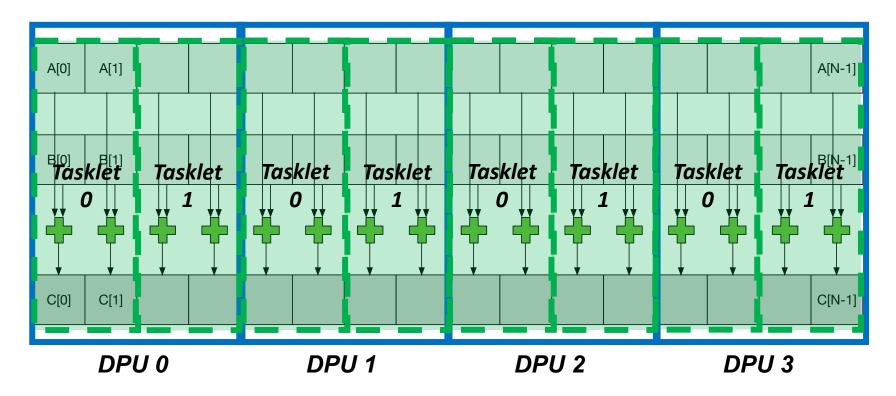

### **Vector Addition (VA)**

- Our first programming example

- We partition the input arrays across:

- DPUs

- Tasklets, i.e., software threads running on a DPU

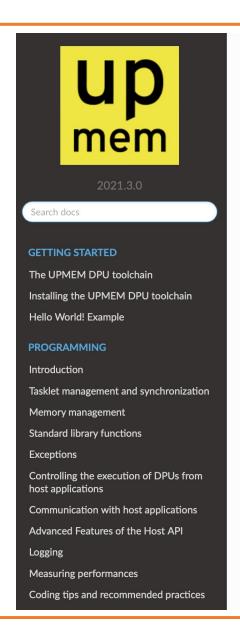

#### **UPMEM SDK Documentation**

\* » User Manual

#### **User Manual**

#### **Getting started**

- The UPMEM DPU toolchain

- Notes before starting

- The toolchain purpose

- dpu-upmem-dpurte-clang

- Limitations

- The DPU Runtime Library

- The Host Library

- dpu-lldb

- Installing the UPMEM DPU toolchain

- Dependencies

- Python

- Installation packages

- Installation from tar.gz binary archive

- Functional simulator

- Hello World! Example

- Purpose

- Writing and building the program

- Running and testing hello world

- Creating a host application to drive the program

### **General Programming Recommendations**

From UPMEM programming guide\*, presentations\*, and white papers<sup>☆</sup>

#### GENERAL PROGRAMMING RECOMMENDATIONS

- 1. Execute on the *DRAM Processing Units* (*DPUs*) **portions of parallel code** that are as long as possible.

- 2. Split the workload into **independent data blocks**, which the DPUs operate on independently.

- 3. Use **as many working DPUs** in the system as possible.

- 4. Launch at least **11** *tasklets* (i.e., software threads) per DPU.

<sup>★</sup> UPMEM, "Introduction to UPMEM PIM. Processing-in-memory (PIM) on DRAM Accelerator," White paper

<sup>\*</sup> https://sdk.upmem.com/2021.1.1/index.html

<sup>\*</sup> F. Devaux, "The true Processing In Memory accelerator," HotChips 2019. doi: 10.1109/HOTCHIPS.2019.8875680

### **DPU Allocation**

- dpu alloc() allocates a number of DPUs

- Creates a dpu set

```

struct dpu_set_t dpu_set, dpu;

uint32_t nr_of_dpus;

// Allocate DPUs

DPU_ASSERT(dpu_alloc(NR_DPUS, NULL, &dpu_set));

DPU_ASSERT(dpu_get_nr_dpus(dpu_set, &nr_of_dpus));

printf("Allocated %d DPU(s)\n", nr_of_dpus);

```

Can we allocate different DPU sets over the course of a program?

Yes, we can. We show an example next

We deallocate a DPU set with dpu free()

### DPU Allocation: Needleman-Wunsch (NW)

In NW we change the number of DPUs in the DPU set as computation progresses

```

// Top-left computation on DPUs

for (unsigned int blk = 1; blk <= (max_cols-1)/BL; blk++) {</pre>

// If nr_of_blocks are lower than max_dpus,

// set nr_of_dpus to be equal with nr_of_blocks

unsigned nr_of_blocks = blk;

if (nr_of_blocks < max_dpus) {</pre>

DPU_ASSERT(dpu_free(dpu_set));

DPU_ASSERT(dpu_alloc(nr_of_blocks, NULL, &dpu_set));

DPU_ASSERT(dpu_load(dpu_set, DPU_BINARY, NULL));

DPU_ASSERT(dpu_get_nr_dpus(dpu_set, &nr_of_dpus));

} else if (nr of dpus == max dpus) {

} else {

DPU ASSERT(dpu free(dpu set));

DPU_ASSERT(dpu_alloc(max_dpus, NULL, &dpu_set));

DPU ASSERT(dpu load(dpu set, DPU BINARY, NULL));

DPU ASSERT(dpu get nr dpus(dpu set, &nr of dpus));

```

### **Load DPU Binary**

dpu\_load() loads a program in all DPUs of a dpu\_set

```

// Define the DPU Binary path as DPU_BINARY here

#ifndef DPU_BINARY

#define DPU_BINARY "./bin/dpu_code"

#endif

// Load binary

DPU_ASSERT(dpu_load(dpu_set, DPU_BINARY, NULL));

```

Is it possible to launch different kernels onto different DPUs?

Yes, it is possible. This enables:

- Workloads with task-level parallelism

- Different programs using different DPU sets

### CPU-DPU/DPU-CPU Data Transfers

- CPU-DPU and DPU-CPU transfers

- Between host CPU's main memory and DPUs' MRAM banks

- Serial CPU-DPU/DPU-CPU transfers:

- A single DPU (i.e., 1 MRAM bank)

- Parallel CPU-DPU/DPU-CPU transfers:

- Multiple DPUs (i.e., many MRAM banks)

- Broadcast CPU-DPU transfers:

- Multiple DPUs with a single buffer

### **Serial Transfers**

- dpu\_copy\_to();

- dpu\_copy\_from();

- We transfer (part of) a buffer to/from each DPU in the dpu\_set

- DPU\_MRAM\_HEAP\_POINTER\_NAME: Start of the MRAM range that can be freely accessed by applications

- We do not allocate MRAM explicitly

```

DPU_FOREACH (dpu_set, dpu) {

DPU_ASSERT(dpu_copy_to(dpu, DPU_MRAM_HEAP_POINTER_NAME on the strength of the

```

### **Parallel Transfers**

- We push different buffers to/from a DPU set in one transfer

- All buffers need to be of the same size

- First, prepare (dpu\_prepare\_xfer);then, push (dpu\_push\_xfer)

- Direction:

- DPU XFER TO DPU

- DPU\_XFER\_FROM\_DPU

```

DPU_FOREACH(dpu_set, dpu, i) {

DPU_ASSERT(dpu_prepare_xfer(dpu, bufferA + input_size_dpu_8bytes * i))

DPU_ASSERT(dpu_push_xfer(dpu_set, DPU_XFER_TO_DPU DPU_MRAM_HEAP_POINTER_NAME, 0, input_size_dpu_8bytes * sizeof(T) DPU_XFER_DEFAULT));

DPU_FOREACH(dpu_set, dpu, i) {

DPU_ASSERT(dpu_prepare_xfer(dpu, bufferB + input_size_dpu_8bytes * i))

DPU_ASSERT(dpu_prepare_xfer(dpu, bufferB + input_size_dpu_8bytes * i))

DPU_ASSERT(dpu_push_xfer(dpu_set, DPU_XFER_TO_DPU DPU_MRAM_HEAP_POINTER_NAME, input_size_dpu_8bytes * sizeof(T) input_size_dpu_8bytes * sizeof(T) DPU_XFER_DEFAULT));

DPU_ASSERT(dpu_push_xfer(dpu_set, DPU_XFER_TO_DPU DFU_MRAM_HEAP_POINTER_NAME, input_size_dpu_8bytes * sizeof(T) DPU_XFER_DEFAULT));

DPU_ASSERT(dpu_push_xfer(dpu_set, DPU_XFER_TO_DPU DFU_MRAM_HEAP_POINTER_NAME, input_size_dpu_8bytes * sizeof(T) DPU_XFER_DEFAULT));

```

### **Broadcast Transfers**

- dpu\_broadcast\_to();

- Only CPU to DPU

- We transfer the same buffer to all DPUs in the dpu\_set

```

DPU_ASSERT(dpu_broadcast_to(dpu_set, DPU_MRAM_HEAP_POINTER_NAME, 0, bufferA, input_size_dpu * sizeof(T) DPU_XFER_DEFAULT));

Pointer to main memory Transfer size

```

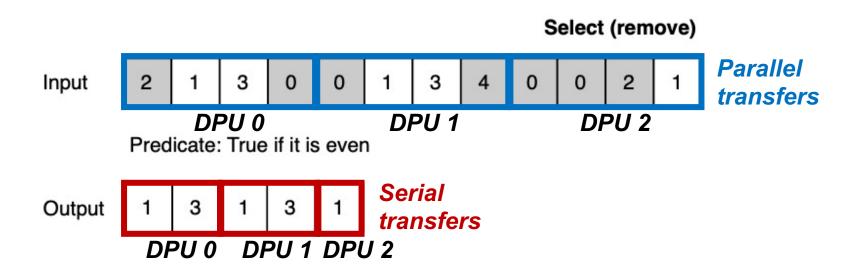

### Different Types of Transfers in a Program

- An example benchmark that uses both parallel and serial transfers

- Select (SEL)

- Remove even values

#### Inter-DPU Communication

There is no direct communication channel between DPUs

- Inter-DPU communication takes place via the host CPU using CPU-DPU and DPU-CPU transfers

- Example communication patterns:

- Merging of partial results to obtain the final result

- Only DPU-CPU transfers

- Redistribution of intermediate results for further computation

- DPU-CPU transfers and CPU-DPU transfers

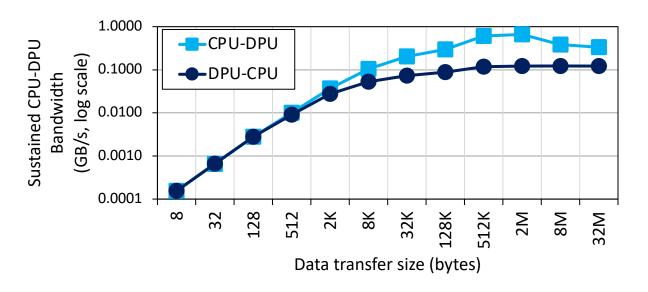

### **How Fast are these Data Transfers?**

- With a microbenchmark, we obtain the sustained bandwidth of all types of CPU-DPU and DPU-CPU transfers

- Two experiments:

- 1 DPU: variable CPU-DPU and DPU-CPU transfer size (8 bytes to 32 MB)

- 1 rank: 32 MB CPU-DPU and DPU-CPU transfers to/from a set of 1 to 64 MRAM banks within the same rank

- Preliminary experiments with more than one rank

- Channel-level parallelism

DDR4 bandwidth bounds the maximum transfer bandwidth

The cost of the transfers can be amortized, if enough computation is run on the DPUs

### CPU-DPU/DPU-CPU Transfers: 1 DPU

Data transfer size varies between 8 bytes and 32 MB

#### KEY OBSERVATION 7

**Larger CPU-DPU and DPU-CPU transfers** between the host main memory and the DRAM Processing Unit's Main memory (MRAM) banks **result in higher sustained bandwidth**.

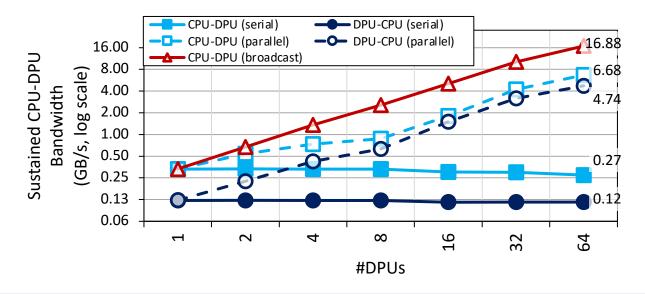

## CPU-DPU/DPU-CPU Transfers: 1 Rank (I)

- CPU-DPU (serial/parallel/broadcast) and DPU-CPU (serial/parallel)

- The number of DPUs varies between 1 and 64

#### **KEY OBSERVATION 8**

The **sustained bandwidth of parallel CPU-DPU and DPU-CPU transfers** between the host main memory and the DRAM Processing Unit's Main memory (MRAM) banks **increases with the number of DRAM Processing Units inside a rank**.

## CPU-DPU/DPU-CPU Transfers: 1 Rank (II)

- CPU-DPU (serial/parallel/broadcast) and DPU-CPU (serial/parallel)

- The number of DPUs varies between 1 and 64

#### **KEY OBSERVATION 9**

The sustained bandwidth of parallel CPU-DPU transfers is higher than the sustained bandwidth of parallel DPU-CPU transfers due to different implementations of CPU-DPU and DPU-CPU transfers in the UPMEM runtime library.

The sustained bandwidth of broadcast CPU-DPU transfers (i.e., the same buffer is copied to multiple MRAM banks) is higher than that of parallel CPU-DPU transfers (i.e., different buffers are copied to different MRAM banks) due to higher temporal locality in the CPU cache hierarchy.

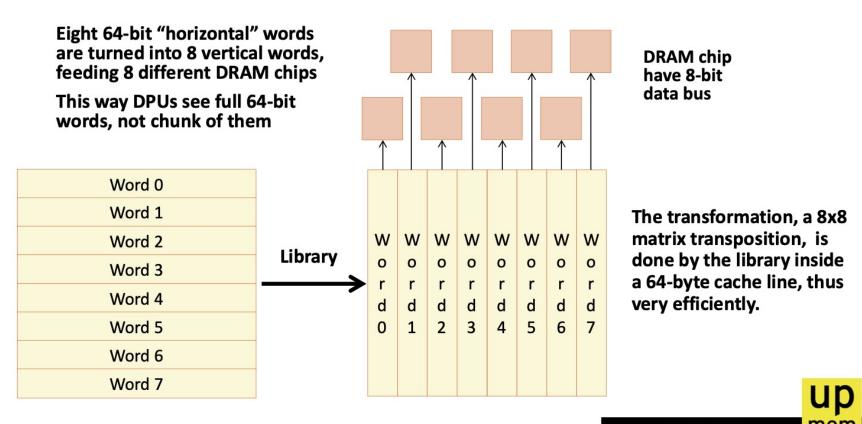

## "Transposing" Library

### The library feeds DPUs with correct data

Copyright UPMEM® 2019

**HOT CHIPS 31**

### **Microbenchmark: CPU-DPU**

CPU-DPU (serial/parallel/broadcast) and DPU-CPU (serial/parallel)

### **DPU Kernel Launch**

- dpu\_launch() launches a kernel on a dpu\_set

- DPU\_SYNCHRONOUS suspends the application until the kernel finishes

- DPU\_ASYNCHRONOUS returns the control to the application

- dpu\_sync or dpu\_status to check kernel completion

```

printf("Run program on DPU(s) \n");

// Run DPU kernel

DPU_ASSERT(dpu_launch(dpu_set, DPU_SYNCHRONOUS));

```

What does the asynchronous execution enable?

#### Some ideas:

- Task-level parallelism: concurrent execution of different kernels on different DPU sets

- Concurrent heterogeneous computation on CPU and DPUs

#### **How to Pass Parameters to the Kernel?**

- We can use serial and parallel transfers

- We pass them directly to the scratchpad memory of the DPU

- Working RAM (WRAM): We introduce it in the next slides

- This is useful for input parameters and some results

### **Recall: Vector Addition (VA)**

- Our first programming example

- We partition the input arrays across:

- DPUs

- Tasklets, i.e., software threads running on a DPU

## Programming a DPU Kernel (I)

Vector addition

```

Tasklet ID

int main_kernel1() {

Size of vector tile processed by a DPU

unsigned int tasklet_id = me()

uint32 t input size dpu bytes = DPU INPUT ARGUMENTS.size; // Input size per DPU in bytes

uint32_t input_size_dpu_bytes_transfer = DPU_INPUT_ARGUMENTS.transfer_size; // Transfer input size per DPU in bytes

// Address of the current processing block in MRAM

MRAM addresses of arrays A and B

uint32 t base tasklet = tasklet id << BLOCK SIZE LOG2;</pre>

uint32_t mram_base_addr_A = (uint32_t)DPU_MRAM_HEAP_POINTER;

uint32_t mram_base_addr_B = (uint32_t)(DPU_MRAM_HEAP_POINTER + input_size_dpu_bytes_transfer);

// Initialize a local cache to store the MRAM block

T * cache A = (T *) mem alloc(BLOCK SIZE);

WRAM allocation

T *cache B = (T *) mem alloc(BLOCK SIZE);

for(unsigned int byte_index = base_tasklet; byte_index < input_size_dpu_bytes; byte_index += BLOCK_SIZE * NR_TASKLETS){</pre>

uint32_t l_size_bytes = (byte_index + BLOCK_SIZE >= input_size_dpu_bytes) ? (input_size_dpu_bytes - byte_index) : BLOCK_SIZE;

// Load cache with current MRAM block

MRAM-WRAM DMA

mram_read((__mram_ptr void const*)(mram_base_addr_A + byte_index), cache_A, l_size_bytes);

mram_read((__mram_ptr void const*)(mram_base_addr_B + byte_index), cache_B, l_size_bytes);

transfers

vector_addition(cache_B, cache_A, l_size_bytes >> DIV); Vector addition (see next slide)

// Write cache to current MRAM block

mram_write(cache_B, (__mram_ptr void*)(mram_base_addr_B + byte_index), l_size_bytes);

WRAM-MRAM DMA transfer

return 0;

```

# Programming a DPU Kernel (II)

Vector addition

```

// vector_addition: Computes the vector addition of a cached block

static void vector_addition(T *bufferB, T *bufferA, unsigned int l_size) {

for (unsigned int i = 0; i < l_size; i++){

bufferB[i] += bufferA[i];

}

</pre>

```

## Programming a DPU Kernel (III)

- A tasklet is the software abstraction of a hardware thread

- Each tasklet can have its own memory space in WRAM

- Tasklets can also share data in WRAM by sharing pointers

- Tasklets within the same DPU can synchronize

```

- Mutual exclusion

```

```

mutex lock(); mutex unlock();

```

- Handshakes

```

handshake_wait_for(); handshake_notify();

```

- Barriers

```

barrier_wait();

```

- Semaphores

```

• sem_give(); sem_take();

```

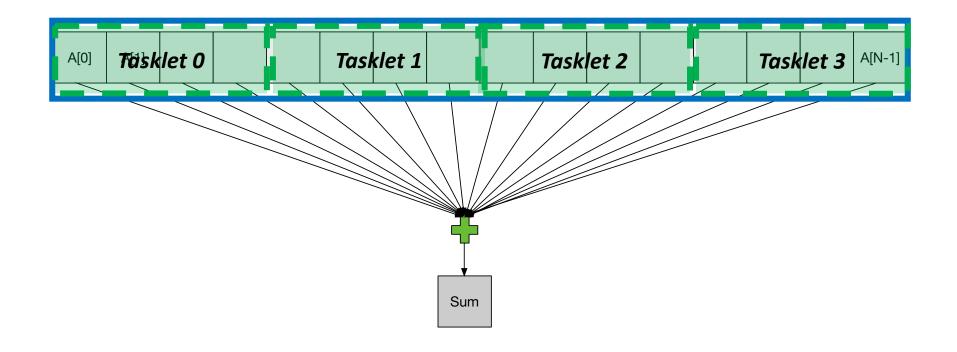

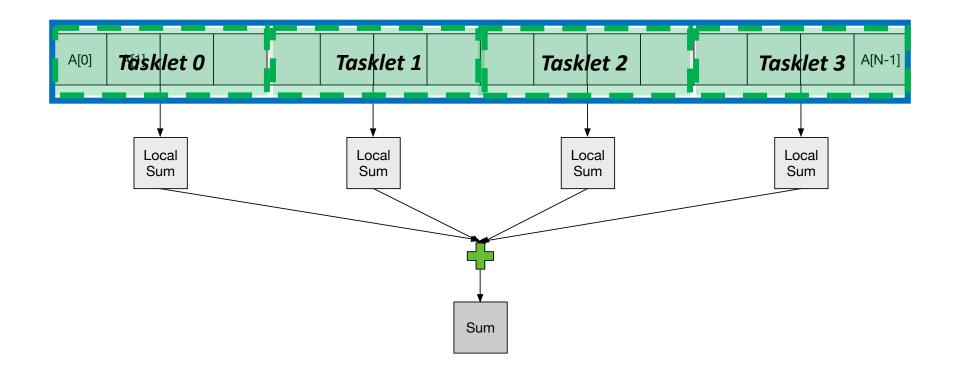

### Parallel Reduction (I)

Tasklets in a DPU can work together on a parallel reduction

## Parallel Reduction (II)

Each tasklet computes a local sum

### Parallel Reduction (III)

Each tasklet computes a local sum

```

for(unsigned int byte_index = base_tasklet; byte_index < input_size_dpu_bytes; byte_index += BLOCK_SIZE * NR_TASKLETS){

// Bound checking

uint32_t l_size_bytes = (byte_index + BLOCK_SIZE >= input_size_dpu_bytes) ? (input_size_dpu_bytes - byte_index) : BLOCK_SIZE;

// Load cache with current MRAM block

mram_read((_mram_ptr void const*)(mram_base_addr_A + byte_index), cache_A, l_size_bytes);

// Reduction in each tasklet

l_count += reduction(cache_A, l_size_bytes >> DIV); Accumulate in a local sum

// Copy local count to shared array in WRAM

message[tasklet_id] = l_count; Copy local sum into WRAM

```

## **Final Reduction**

A single tasklet can perform the final reduction

```

for(unsigned int byte_index = base_tasklet; byte_index < input_size_dpu_bytes; byte_index += BLOCK_SIZE * NR_TASKLETS){

// Bound checking

uint32_t l_size_bytes = (byte_index + BLOCK_SIZE >= input_size_dpu_bytes) ? (input_size_dpu_bytes - byte_index) : BLOCK_SIZE;

// Load cache with current MRAM block

mram_read((__mram_ptr void const*)(mram_base_addr_A + byte_index), cache_A, l_size_bytes);

// Reduction in each tasklet

l_count += reduction(cache_A, l_size_bytes >> DIV); Accumulate in a local sum

}

// Copy local count to shared array in WRAM

message[tasklet_id] = l_count; Copy local sum into WRAM

```

```

// Single-thread reduction

// Barrier

barrier_wait(&my_barrier); Barrier synchronization

if(tasklet_id == 0){

#pragma unroll

for (unsigned int each_tasklet = 1; each_tasklet < NR_TASKLETS; each_tasklet++){

message[0] += message[each_tasklet]; Sequential accumulation

}

// Total count in this DPU

result->t_count = message[0];

}

```

## Vector Reduction: Naïve Mapping

Slide credit: Hwu & Kirk

38

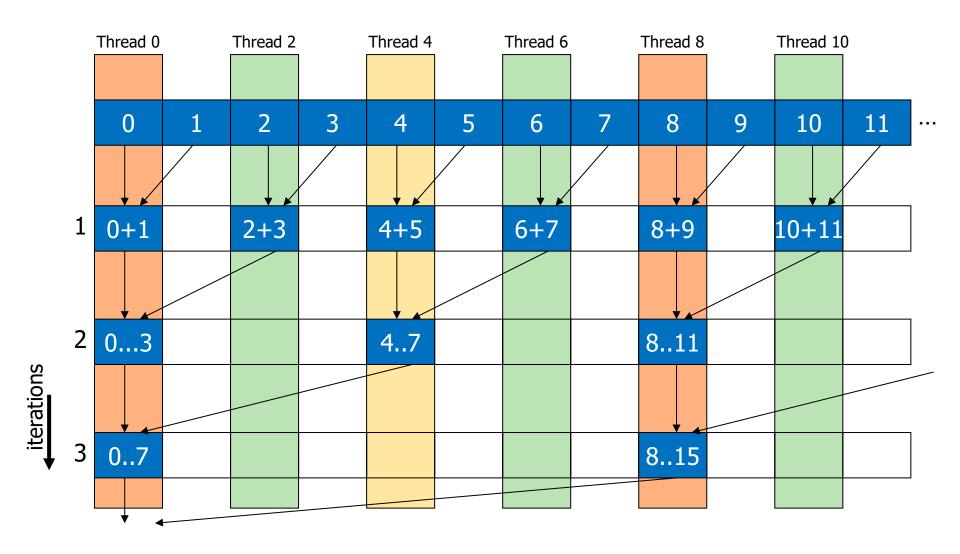

## **Using Barriers: Tree-Based Reduction**

- Multiple tasklets can perform a tree-based reduction

- After every iteration tasklets synchronize with a barrier

- Half of the tasklets retire at the end of an iteration

A handshake-based tree-based reduction is also possible. We can compare single-tasklet, barrier-based, and handshake-based versions\*

#### Parallel Reduction on GPU

#### **UPMEM SDK Documentation**

\* » User Manual

#### **User Manual**

#### **Getting started**

- The UPMEM DPU toolchain

- Notes before starting

- The toolchain purpose

- dpu-upmem-dpurte-clang

- Limitations

- The DPU Runtime Library

- The Host Library

- dpu-lldb

- Installing the UPMEM DPU toolchain

- Dependencies

- Python

- Installation packages

- Installation from tar.gz binary archive

- Functional simulator

- Hello World! Example

- Purpose

- Writing and building the program

- · Running and testing hello world

- Creating a host application to drive the program

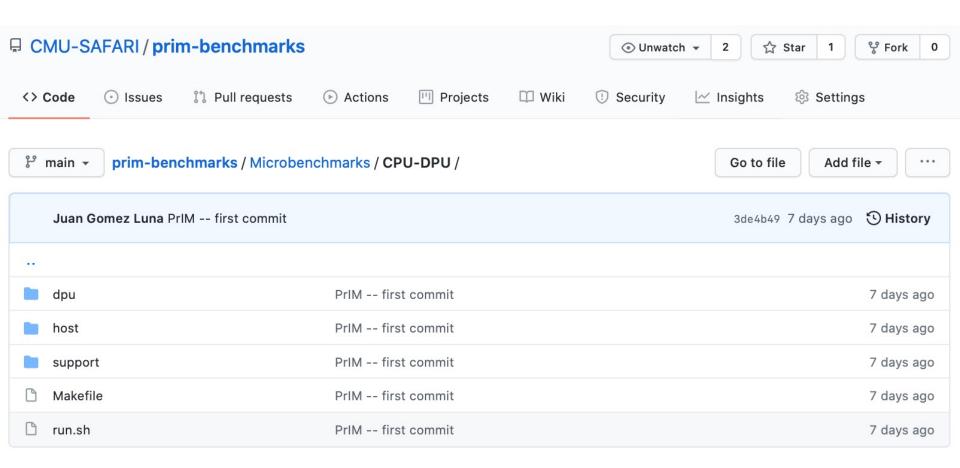

### **PrIM Benchmarks**

- Goal

- A common set of workloads that can be used to

- evaluate the UPMEM PIM architecture,

- compare software improvements and compilers,

- compare future PIM architectures and hardware

- Two key selection criteria:

- Selected workloads from different application domains

- Memory-bound workloads on processor-centric architectures

- 14 different workloads, 16 different benchmarks\*

# **PrIM Benchmarks: Application Domains**

| Domain                    | Benchmark                     | Short name |

|---------------------------|-------------------------------|------------|

| Dance linear algebra      | Vector Addition               | VA         |

| Dense linear algebra      | Matrix-Vector Multiply        | GEMV       |

| Sparse linear algebra     | Sparse Matrix-Vector Multiply | SpMV       |

| Databasas                 | Select                        | SEL        |

| Databases                 | Unique                        | UNI        |

| Data analytics            | Binary Search                 | BS         |

|                           | Time Series Analysis          | TS         |

| Graph processing          | Breadth-First Search          | BFS        |

| Neural networks           | Multilayer Perceptron         | MLP        |

| Bioinformatics            | Needleman-Wunsch              | NW         |

| lung of a pure species of | Image histogram (short)       | HST-S      |

| Image processing          | Image histogram (large)       | HST-L      |

|                           | Reduction                     | RED        |

| Parallel primitives       | Prefix sum (scan-scan-add)    | SCAN-SSA   |

|                           | Prefix sum (reduce-scan-scan) | SCAN-RSS   |

|                           | Matrix transposition          | TRNS       |

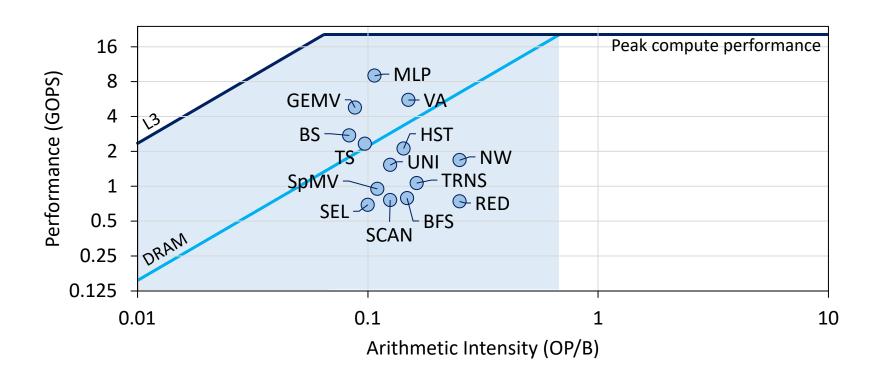

## **Roofline Model**

Intel Advisor on an Intel Xeon E3-1225 v6 CPU

All workloads fall in the memory-bound area of the Roofline

## **PrIM Benchmarks: Diversity**

- PrIM benchmarks are diverse:

- Memory access patterns

- Operations and datatypes

- Communication/synchronization

| Domain                | Benchmark                     | Short name | Memory access pattern |         |        | Computation pattern |          | Communication/synchronization |           |

|-----------------------|-------------------------------|------------|-----------------------|---------|--------|---------------------|----------|-------------------------------|-----------|

| Domain                |                               |            | Sequential            | Strided | Random | Operations          | Datatype | Intra-DPU                     | Inter-DPU |

| Dense linear algebra  | Vector Addition               | VA         | Yes                   |         |        | add                 | int32_t  |                               |           |

|                       | Matrix-Vector Multiply        | GEMV       | Yes                   |         |        | add, mul            | uint32_t |                               |           |

| Sparse linear algebra | Sparse Matrix-Vector Multiply | SpMV       | Yes                   |         | Yes    | add, mul            | float    |                               |           |

| Databases             | Select                        | SEL        | Yes                   |         |        | add, compare        | int64_t  | handshake, barrier            | Yes       |

| Databases             | Unique                        | UNI        | Yes                   |         |        | add, compare        | int64_t  | handshake, barrier            | Yes       |

| Data analytics        | Binary Search                 | BS         | Yes                   |         | Yes    | compare             | int64_t  |                               |           |

|                       | Time Series Analysis          | TS         | Yes                   |         |        | add, sub, mul, div  | int32_t  |                               |           |

| Graph processing      | Breadth-First Search          | BFS        | Yes                   |         | Yes    | bitwise logic       | uint64_t | barrier, mutex                | Yes       |

| Neural networks       | Multilayer Perceptron         | MLP        | Yes                   |         |        | add, mul, compare   | int32_t  |                               |           |

| Bioinformatics        | Needleman-Wunsch              | NW         | Yes                   | Yes     |        | add, sub, compare   | int32_t  | barrier                       | Yes       |

| Image processing      | Image histogram (short)       | HST-S      | Yes                   |         | Yes    | add                 | uint32_t | barrier                       | Yes       |

|                       | Image histogram (long)        | HST-L      | Yes                   |         | Yes    | add                 | uint32_t | barrier, mutex                | Yes       |

| Parallel primitives   | Reduction                     | RED        | Yes                   | Yes     |        | add                 | int64_t  | barrier                       | Yes       |

|                       | Prefix sum (scan-scan-add)    | SCAN-SSA   | Yes                   |         |        | add                 | int64_t  | handshake, barrier            | Yes       |

|                       | Prefix sum (reduce-scan-scan) | SCAN-RSS   | Yes                   |         |        | add                 | int64_t  | handshake, barrier            | Yes       |

|                       | Matrix transposition          | TRNS       | Yes                   |         | Yes    | add, sub, mul       | int64_t  | mutex                         |           |

### **PrIM Benchmarks: Inter-DPU Communication**

| Domain                | Benchmark                     | Short name | Memory access pattern |         |        | Computation pattern |          | Communication/synchronization |           |

|-----------------------|-------------------------------|------------|-----------------------|---------|--------|---------------------|----------|-------------------------------|-----------|

| Domain                |                               |            | Sequential            | Strided | Random | Operations          | Datatype | Intra-DPU                     | Inter-DPU |

| Dense linear algebra  | Vector Addition               | VA         | Yes                   |         |        | add                 | int32_t  |                               |           |

|                       | Matrix-Vector Multiply        | GEMV       | Yes                   |         |        | add, mul            | uint32_t |                               |           |

| Sparse linear algebra | Sparse Matrix-Vector Multiply | SpMV       | Yes                   |         | Yes    | add, mul            | float    |                               |           |

| Databases             | Select                        | SEL        | Yes                   |         |        | add, compare        | int64_t  | handshake, barrier            | Yes       |

| Databases             | Unique                        | UNI        | Yes                   |         |        | add, compare        | int64_t  | handshake, barrier            | Yes       |

| D-4                   | Binary Search                 | BS         | Yes                   |         | Yes    | compare             | int64_t  |                               |           |

| Data analytics        | Time Series Analysis          | TS         | Yes                   |         |        | add, sub, mul, div  | int32_t  |                               |           |

| Graph processing      | Breadth-First Search          | BFS        | Yes                   |         | Yes    | bitwise logic       | uint64_t | barrier, mutex                | Yes       |

| Neural networks       | Multilayer Perceptron         | MLP        | Yes                   |         |        | add, mul, compare   | int32_t  |                               |           |

| Bioinformatics        | Needleman-Wunsch              | NW         | Yes                   | Yes     |        | add, sub, compare   | int32_t  | barrier                       | Yes       |

| Image processing      | Image histogram (short)       | HST-S      | Yes                   |         | Yes    | add                 | uint32_t | barrier                       | Yes       |

|                       | Image histogram (long)        | HST-L      | Yes                   |         | Yes    | add                 | uint32_t | barrier, mutex                | Yes       |

| Parallel primitives   | Reduction                     | RED        | Yes                   | Yes     |        | add                 | int64_t  | barrier                       | Yes       |

|                       | Prefix sum (scan-scan-add)    | SCAN-SSA   | Yes                   |         |        | add                 | int64_t  | handshake, barrier            | Yes       |

|                       | Prefix sum (reduce-scan-scan) | SCAN-RSS   | Yes                   |         |        | add                 | int64_t  | handshake, barrier            | Yes       |

|                       | Matrix transposition          | TRNS       | Yes                   |         | Yes    | add, sub, mul       | int64_t  | mutex                         |           |

#### PrIM Benchmarks: Inter-DPU Communication

|                       | Benchmark                     |            | Memory access pattern |         |        | Computation pattern |          | Communication/synchronization |           |

|-----------------------|-------------------------------|------------|-----------------------|---------|--------|---------------------|----------|-------------------------------|-----------|

| Domain                |                               | Short name | Sequential            | Strided | Random | Operations          | Datatype | Intra-DPU                     | Inter-DPU |

| Dense linear algebra  | Vector Addition               | VA         | Yes                   |         |        | add                 | int32_t  |                               |           |

|                       | Matrix-Vector Multiply        | GEMV       | Yes                   |         |        | add, mul            | uint32_t |                               |           |

| Sparse linear algebra | Sparse Matrix-Vector Multiply | SpMV       | Yes                   |         | Yes    | add, mul            | float    |                               |           |

| Databases             | Select                        | SEL        | Yes                   |         |        | add, compare        | int64_t  | handshake, barrier            | Yes       |

| Databases             | Unique                        | UNI        | Yes                   |         |        | add, compare        | int64_t  | handshake, barrier            | Yes       |

| Data analytica        | Binary Search                 | BS         | Yes                   |         | Yes    | compare             | int64_t  |                               |           |

| Data analytics        | Time Series Analysis          | TS         | Yes                   |         |        | add, sub, mul, div  | int32_t  |                               |           |

| Graph processing      | Breadth-First Search          | BFS        | Yes                   |         | Yes    | bitwise logic       | uint64_t | barrier, mutex                | Yes       |

| Neural networks       | Multilayer Perceptron         | MLP        | Yes                   |         |        | add, mul, compare   | int32_t  |                               |           |

| Bioinformatics        | Needleman-Wunsch              | NW         | Yes                   | Yes     |        | add, sub, compare   | int32_t  | barrier                       | Yes       |

| Image processing      | Image histogram (short)       | HST-S      | Yes                   |         | Yes    | add                 | uint32_t | barrier                       | Yes       |

|                       | Image histogram (long)        | HST-L      | Yes                   |         | Yes    | add                 | uint32_t | barrier, mutex                | Yes       |

| Parallel primitives   | Reduction                     | RED        | Yes                   | Yes     |        | add                 | int64_t  | barrier                       | Yes       |

|                       | Prefix sum (scan-scan-add)    | SCAN-SSA   | Yes                   |         |        | add                 | int64_t  | handshake, barrier            | Yes       |

|                       | Prefix sum (reduce-scan-scan) | SCAN-RSS   | Yes                   |         |        | add                 | int64_t  | handshake, barrier            | Yes       |

|                       | Matrix transposition          | TRNS       | Yes                   |         | Yes    | add, sub, mul       | int64_t  | mutex                         |           |

#### • Inter-DPU communication

- Result merging:

- SEL, UNI, HST-S, HST-L, RED

- Only DPU-CPU transfers

- Redistribution of intermediate results:

- BFS, MLP, NW, SCAN-SSA, SCAN-RSS

- DPU-CPU and CPU-DPU transfers

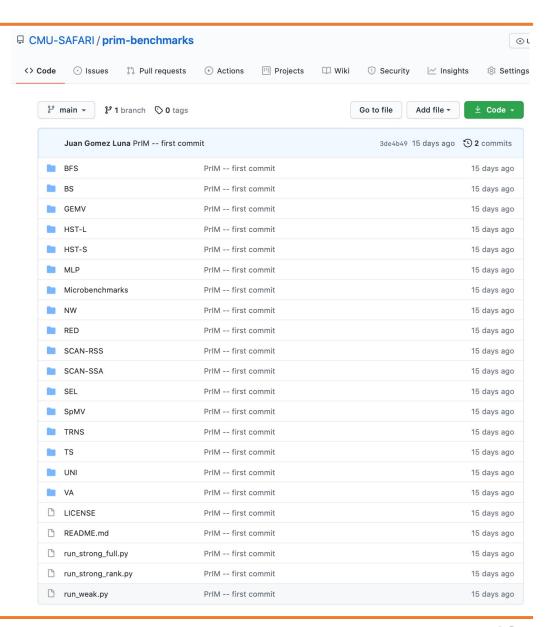

### **PrIM Benchmarks**

- 16 benchmarks and scripts for evaluation

- https://github.com/CMU-SAFARI/prim-benchmarks

## Upcoming Lectures

More real-world PIM architectures

- More on workload characterization for PIM suitability

- Benchmarking and workload suitability on the UPMEM PIM architecture

PUM architectures and prototypes

# P&S Processing-in-Memory

Programming

Processing-in-Memory Architectures

Dr. Juan Gómez Luna

Prof. Onur Mutlu

ETH Zürich

Spring 2022

21 April 2022