#### P&S Modern SSDs

Fine-Grained Mapping & Multi-Plane Operation-Aware Block Management

Dr. Jisung Park

Prof. Onur Mutlu

ETH Zürich

Spring 2022

15 April 2022

# Recap: What We Have Discussed So Far

- SSD Organization

- NAND Flash Organization and Operations

- Advanced NAND Flash Commands

- FTL: Address Translation & Garbage Collection

# Today's Agenda

Fine-Grained Mapping

Multi-plane Operation-Aware Blk. Mgmt.

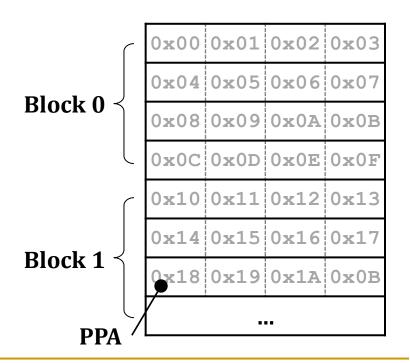

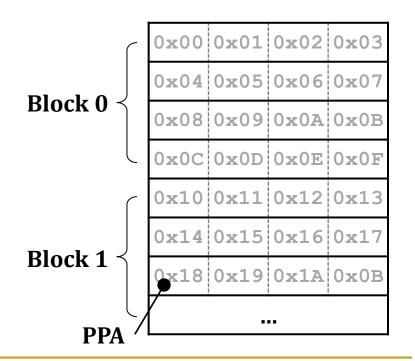

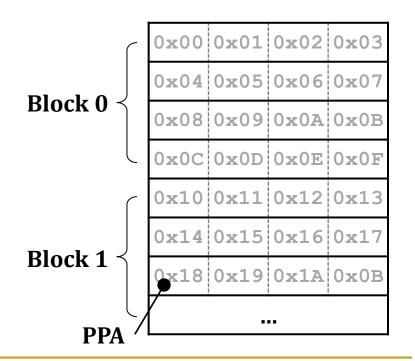

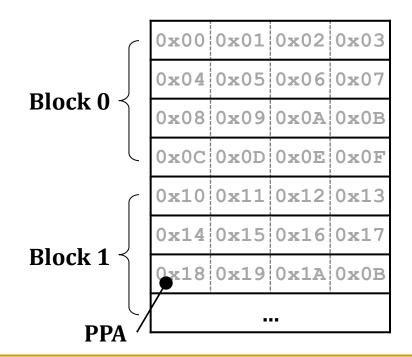

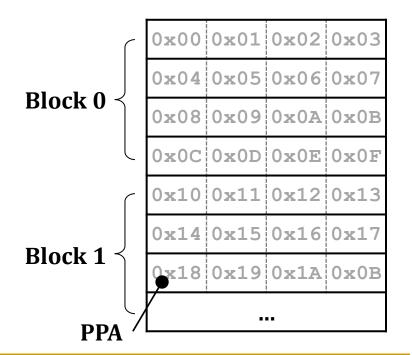

#### I/O Mismatch b/w OS and NAND Flash

- The page size (i.e., minimum I/O unit) of NAND flash memory has continuously increased.

- From 256 bytes to 16 KiB

- Low area overhead and high bandwidth (size / latency)

- The logical block (or sector) size of file systems has also increased.

- From 512 bytes to 4 KiB

- To more efficiently work with NAND flash-based SSDs

- Increasing the block size is not straightforward.

- I/O handling is closely related OS memory management.

- Memory page size = 4 KiB

- Unnecessary fetch or eviction at the page cache

Inefficiencies due to the erase-before-write property

|      | LPA  | PPA |

|------|------|-----|

| 0x00 |      | _   |

|      | 0x01 | -   |

| •    | 0x02 | _   |

| 0x03 |      | _   |

|      | 0x04 | -   |

|      | 0x05 | _   |

|      | •••  | ••• |

Inefficiencies due to the erase-before-write property

|   | LPA  | PPA |

|---|------|-----|

|   | 0x00 | _   |

|   | 0x01 | _   |

| • | 0x02 |     |

|   | 0x03 | _   |

|   | 0x04 | _   |

|   | 0x05 | _   |

|   | •••  | ••• |

Inefficiencies due to the erase-before-write property

|   | LPA  | PPA  |

|---|------|------|

|   | 0x00 | -    |

|   | 0x01 | 0x00 |

| • | 0x02 | _    |

|   | 0x03 | _    |

|   | 0x04 | -    |

|   | 0x05 | _    |

|   | •••  | •••  |

**16 KiB**

Inefficiencies due to the erase-before-write property

|   | LPA  | PPA  |

|---|------|------|

|   | 0x00 | _    |

| • | 0x01 | 0x00 |

|   | 0x02 | _    |

|   | 0x03 | -    |

|   | 0x04 | _    |

|   | 0x05 | -    |

|   | •••  | •••  |

Inefficiencies due to the erase-before-write property

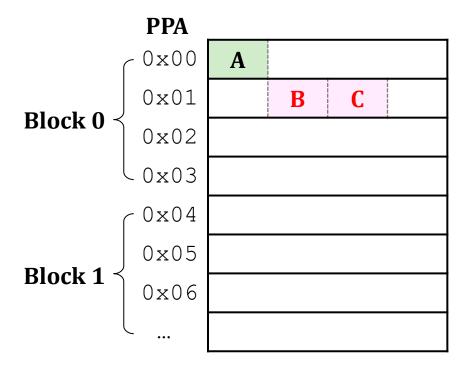

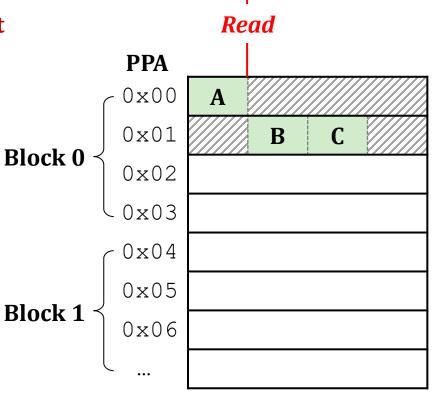

Req (LBA: 0x01, Size: 2, DIR: W, Data: B, C)

0b 0000 0000 0000 0001 16-KiB Page Number 4-KiB Offset

|   | LPA  | PPA  |  |

|---|------|------|--|

|   | 0x00 | _    |  |

| • | 0x01 | 0x00 |  |

|   | 0x02 | -    |  |

|   | 0x03 | _    |  |

|   | 0x04 | _    |  |

|   | 0x05 | _    |  |

|   | •••  |      |  |

Inefficiencies due to the erase-before-write property

Req (LBA: 0x01, Size: 2, DIR: W, Data: B, C)

0b 0000 0000 0000 0001 16-KiB Page Number 4-KiB Offset

| LPA  | PPA  |  |

|------|------|--|

| 0x00 | 0x01 |  |

| 0x01 | 0x00 |  |

| 0x02 | _    |  |

| 0x03 | _    |  |

| 0x04 | _    |  |

| 0x05 | _    |  |

|      |      |  |

Inefficiencies due to the erase-before-write property

Req (LBA: 0x01, Size: 2, DIR: W, Data: B, C)

0b 0000 0000 0000 0001 16-KiB Page Number 4-KiB Offset

| I DA       | DD4        |

|------------|------------|

| <u>LPA</u> | <u>PPA</u> |

| 0x00       | 0x01       |

| 0x01       | 0x00       |

| 0x02       | _          |

| 0x03       | -          |

| 0×04 -     |            |

| 0x05       | -          |

| •••        | •••        |

- 1. Why at the middle of the page?

- To keep the 4-KiB offset: mapping table stores only the index of the 16-KiB page!

- 2. Why not using the unused space in physical page 0x00?

- That space is already mapped to logical pages 0x05~0x07 (not written yet).

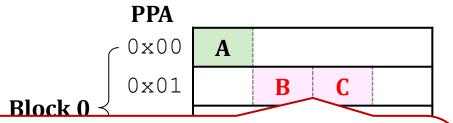

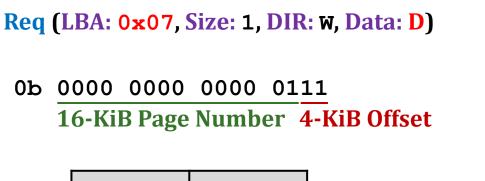

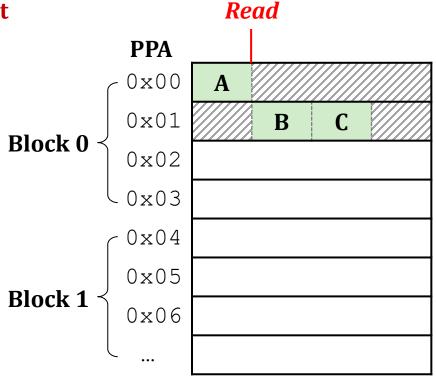

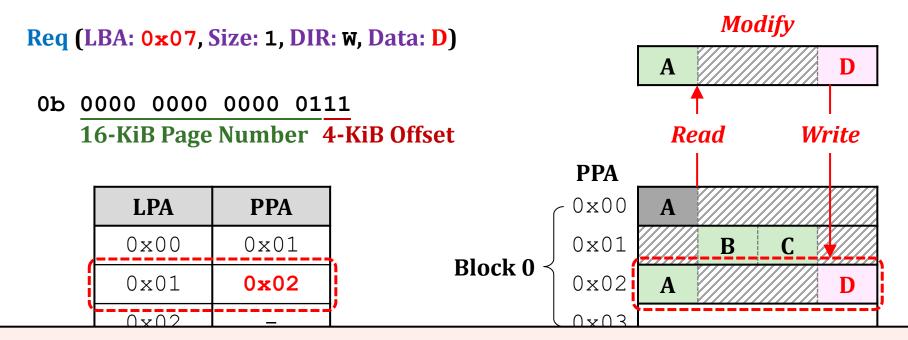

Inefficiencies due to the erase-before-write property

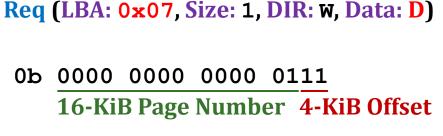

Req (LBA: 0x07, Size: 1, DIR: W, Data: D)

0b <u>0000 0000 0000 0111</u> 16-KiB Page Number 4-KiB Offset

| LPA  | PPA  |

|------|------|

| 0x00 | 0x01 |

| 0x01 | 0x00 |

| 0x02 | -    |

| 0x03 | _    |

| 0x04 | _    |

| 0x05 | ı    |

| •••  | •••  |

Q: Can we use the unused space?

A: Not likely, because

- Data randomization Cells in the unused space have been already programmed.

- Program-order constraint Re-programming physical page  $0 \times 00$  can affect the reliability of the data stored in physical page  $0 \times 01$ .

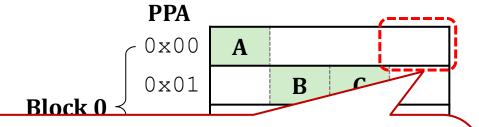

Inefficiencies due to the erase-before-write property

Reg (LBA: 0x07, Size: 1, DIR: W, Data: D) 0b 0000 0000 0000 0111 16-KiB Page Number 4-KiB Offset **Unused yet discarded PPA** 0x00 LPA **PPA** 0x000x01 0x01 B Block 0 <u>0x</u>01 0x00  $0 \times 02$

## Small writes cause waste of P/E cycles: More frequent garbage collections

→ Performance and lifetime degradation

|     |     | ,   |  |

|-----|-----|-----|--|

| ••• | ••• | ••• |  |

|     |     |     |  |

Inefficiencies due to the erase-before-write property

|   | LPA  | PPA  |

|---|------|------|

|   | 0x00 | 0x01 |

|   | 0x01 | 0x00 |

| • | 0x02 | -    |

|   | 0x03 | _    |

|   | 0x04 | _    |

|   | 0x05 | _    |

|   |      | •••  |

Inefficiencies due to the erase-before-write property

|   | LPA  | PPA  |

|---|------|------|

|   | 0x00 | 0x01 |

|   | 0x01 | 0x00 |

| • | 0x02 | -    |

|   | 0x03 | -    |

|   | 0x04 | -    |

|   | 0x05 | _    |

|   |      | •••  |

**Modify**

Inefficiencies due to the erase-before-write property

Inefficiencies due to the erase-before-write property

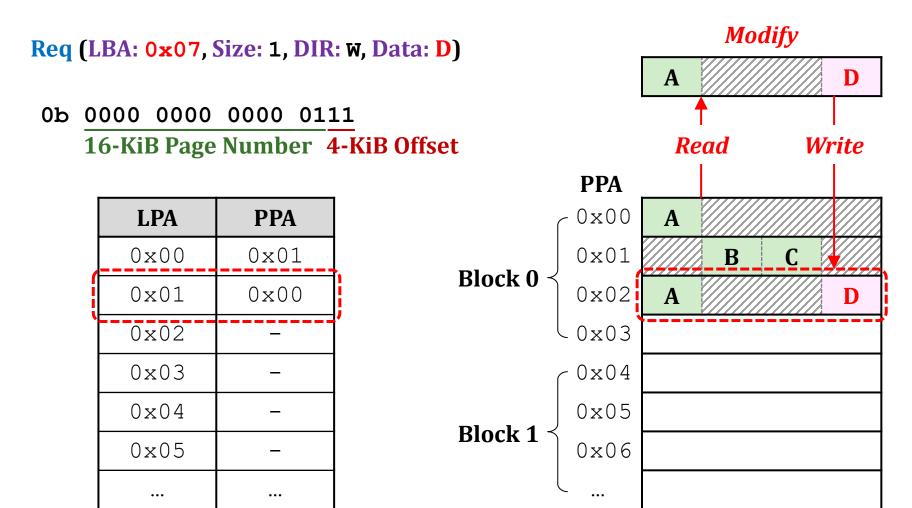

Small writes cause read-modify-writes:

Waste of P/E cycles + additional read operations

→ Performance and lifetime degradation

Write a page only when there are sufficient data blocks

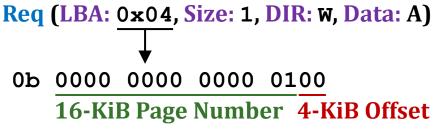

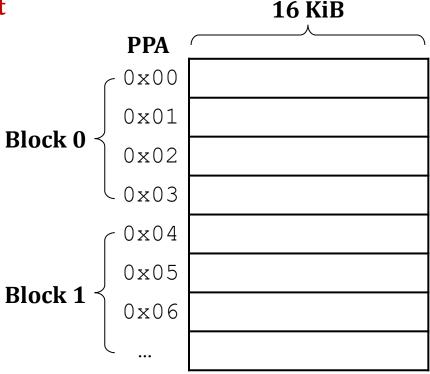

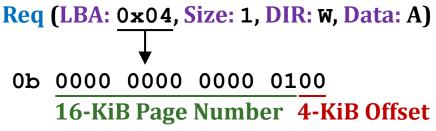

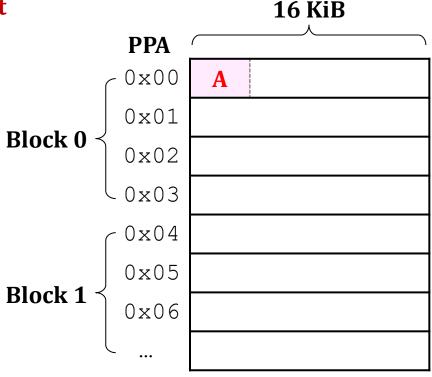

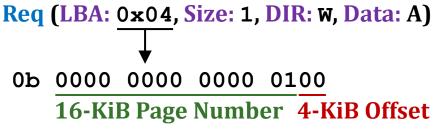

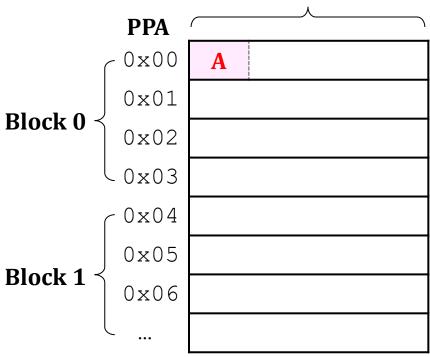

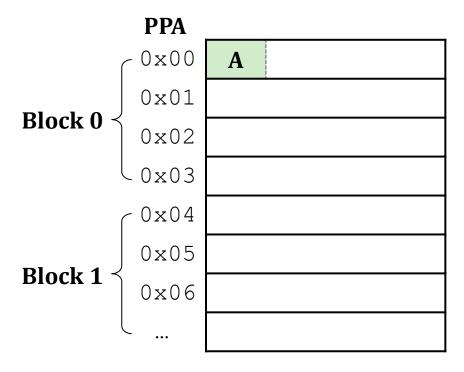

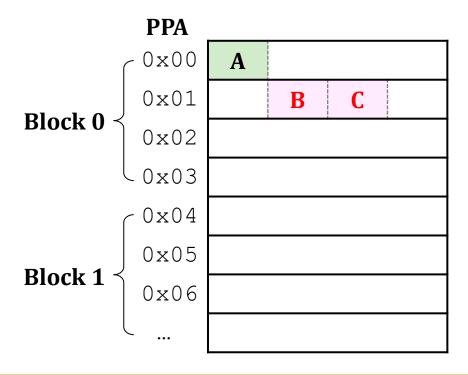

**Req** (LBA: 0x04, Size: 1, DIR: W, Data: A)

Req (LBA: 0x01, Size: 2, DIR: w, Data: B, C)

Req (LBA: 0x07, Size: 1, DIR: w, Data: D)

| O |   |   |

|---|---|---|

|   |   |   |

| i | i | i |

| İ | İ | i |

Page Buffer

|  | LPA  | PPA |

|--|------|-----|

|  | 0x00 | _   |

|  | 0x01 | _   |

|  |      | _   |

|  | 0×04 | _   |

|  |      | -   |

|  | 0x07 | -   |

|  |      |     |

Write a page only when there are sufficient data blocks

**Req** (LBA: 0x04, Size: 1, DIR: W, Data: A)

Req (LBA: 0x01, Size: 2, DIR: w, Data: B, C)

| Page 1 | Buffer |

|--------|--------|

|--------|--------|

|   | i | i | i |

|---|---|---|---|

| _ | 1 | 1 | I |

| ^ | I | 1 | I |

| A | ! | 1 | 1 |

|   | ! | ! | ! |

|   | ! | ! | ! |

|   | LPA  | PPA |

|---|------|-----|

|   | 0x00 | _   |

|   | 0x01 | _   |

|   |      | -   |

|   | 0×04 | _   |

| • |      | _   |

|   | 0x07 |     |

|   |      |     |

Write a page only when there are sufficient data blocks

**Req** (LBA: 0x04, Size: 1, DIR: W, Data: A)

Req (LBA: 0x01, Size: 2, DIR: w, Data: B, C)

| <b>Page</b> | <b>Buffer</b> |

|-------------|---------------|

|-------------|---------------|

|   | i |   | i |

|---|---|---|---|

| _ | I | 1 | I |

| ^ | 1 |   | I |

| A |   |   | I |

|   |   |   |   |

|   | ! |   | ! |

|   | LPA  | PPA  |

|---|------|------|

|   | 0x00 | _    |

|   | 0x01 | _    |

|   |      | _    |

|   | 0×04 | 0x00 |

| • |      | _    |

|   | 0x07 | _    |

|   |      |      |

Write a page only when there are sufficient data blocks

Req (LBA:  $0 \times 04$ , Size: 1, DIR: W, Data: A)

**Req** (LBA: 0x01, Size: 2, DIR: W, Data: B, C)

| Page Buffer |  |  |

|-------------|--|--|

| A           |  |  |

| LPA   | PPA  |

|-------|------|

| 0x00  | _    |

| 0x01  | _    |

| i<br> | =    |

| 0x04  | 0x00 |

| •••   | _    |

| 0x07  | _    |

|       |      |

Write a page only when there are sufficient data blocks

Req (LBA: 0x04, Size: 1, DIR: w, Data: A)

**Req** (LBA: 0x01, Size: 2, DIR: W, Data: B, C)

| Page | Buffer |

|------|--------|

|------|--------|

| Λ | D | C |  |

|---|---|---|--|

| A | В | L |  |

|          | LPA  | PPA  |

|----------|------|------|

|          | 0x00 | _    |

| <u> </u> | 0x01 | _    |

|          |      |      |

|          | 0x04 | 0x00 |

|          | •••  | _    |

|          | 0x07 | _    |

|          |      |      |

Write a page only when there are sufficient data blocks

Req (LBA: 0x04, Size: 1, DIR: W, Data: A)

**Req** (LBA: 0x01, Size: 2, DIR: W, Data: B, C)

| Page | Buffer |

|------|--------|

|------|--------|

| A | В | C |  |

|---|---|---|--|

|   |   |   |  |

|          | LPA  | PPA  |

|----------|------|------|

|          | 0x00 | -    |

|          | 0x01 | 0x01 |

| <b>\</b> | ,    | ·    |

|          | 0×04 | 0x00 |

|          | •••  | -    |

|          | 0x07 | ı    |

|          | •••  |      |

Write a page only when there are sufficient data blocks

Req (LBA: 0x04, Size: 1, DIR: W, Data: A)

Req (LBA: 0x01, Size: 2, DIR: w, Data: B, C)

| <b>Page</b> | Buffer |

|-------------|--------|

|-------------|--------|

| A | В | С |  |

|---|---|---|--|

|   | 1 |   |  |

| LPA  | PPA  |

|------|------|

| 0x00 | _    |

| 0x01 | 0x01 |

| •••  | _    |

| 0x04 | 0x00 |

|      | _    |

| 0x07 | _    |

|      |      |

Write a page only when there are sufficient data blocks

Req (LBA: 0x04, Size: 1, DIR: W, Data: A)

Req (LBA: 0x01, Size: 2, DIR: w, Data: B, C)

| Page Buffer |

|-------------|

|-------------|

|   | İ  | i |     |

|---|----|---|-----|

| Λ | D  | C | n   |

| A | B  | L | ע ו |

|   | į. | į | i   |

| LPA  | PPA  |

|------|------|

| 0x00 | _    |

| 0x01 | 0x01 |

| •••  | _    |

| 0x04 | 0x00 |

| ,    |      |

| 0x07 | _    |

|      |      |

Write a page only when there are sufficient data blocks

Reg (LBA:  $0 \times 04$ , Size: 1, DIR: W, Data: A)

Req (LBA: 0x01, Size: 2, DIR: w, Data: B, C)

| Page B | uffer |

|--------|-------|

|--------|-------|

|   | i     | i          | i |   |

|---|-------|------------|---|---|

| Α | T     | <b>)</b>   | C | D |

| A | i I   | <b>5</b> : | C | D |

|   | - 1 - | -          | _ | _ |

|   | LPA  | PPA           |  |

|---|------|---------------|--|

|   | 0x00 | _             |  |

|   | 0x01 | 0x01          |  |

|   | •••  | _             |  |

|   | 0x04 | 0x00          |  |

|   |      | _             |  |

|   | 0x07 | 0 <b>x</b> 03 |  |

| • |      |               |  |

Write a page only when there are sufficient data blocks

Req (LBA: 0x01, Size: 2, DIR: w, Data: B, C)

**Req** (LBA: 0x07, Size: 1, DIR: W, Data: D)

| LPA  | PPA  |

|------|------|

| 0x00 | -    |

| 0x01 | 0x01 |

|      | _    |

**Page Buffer**

# Fine-grained mapping significantly reduces the number of NAND flash operations: 3 writes (+1 read) → 1 writes

# Drawbacks of Fine-Grained Mapping

- Larger mapping table

- □ 16-KiB mapping  $\rightarrow$  4 bytes per 16-KiB page = 0.025%

- □ 4-KiB mapping  $\rightarrow$  4 bytes per 4-KiB page = 0.1%

- For a 2-TB SSD, 2-GB DRAM is required.

- Increases the SSD's price and power/energy consumption

- Data durability of written data

- Page buffers are implemented by using volatile memory (e.g., SRAM or DRAM).

Despites non-negligible drawbacks, fine-grained mapping is widely used in modern SSDs due to its high benefits

# Today's Agenda

Fine-Grained Mapping

Multi-plane Operation-Aware Blk. Mgmt.

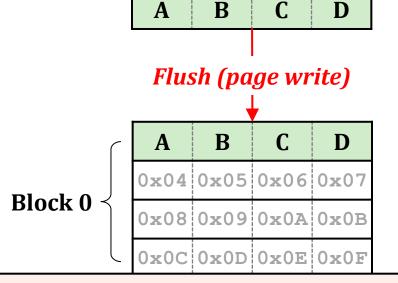

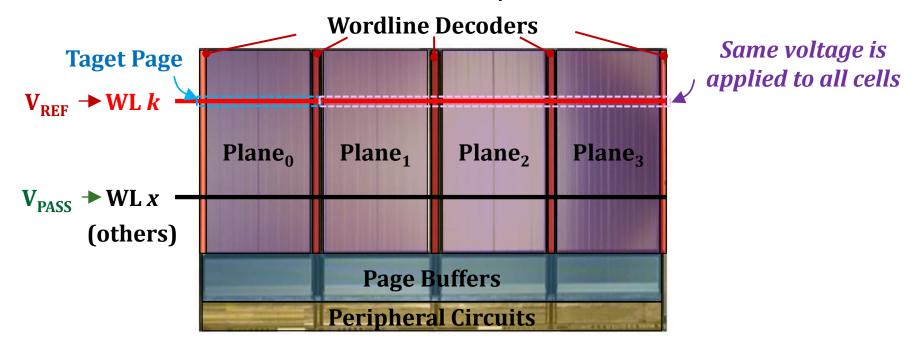

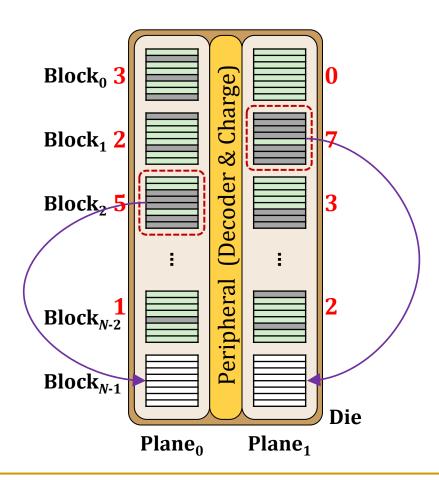

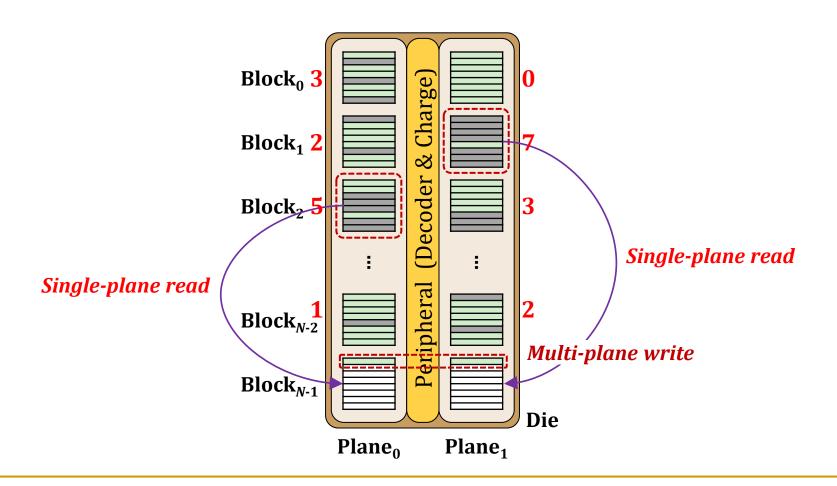

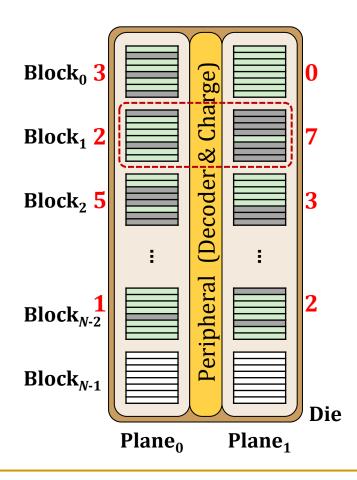

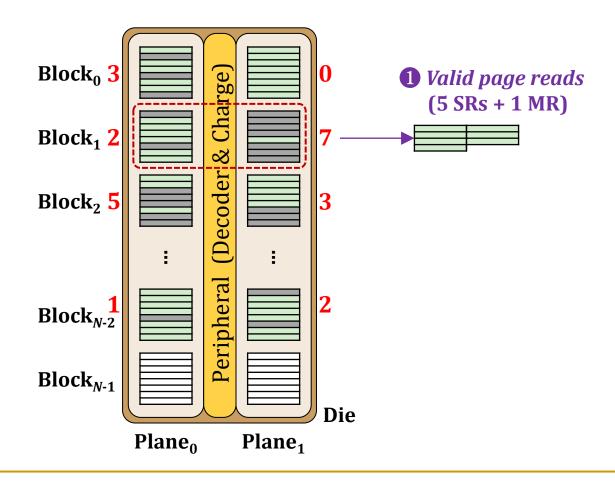

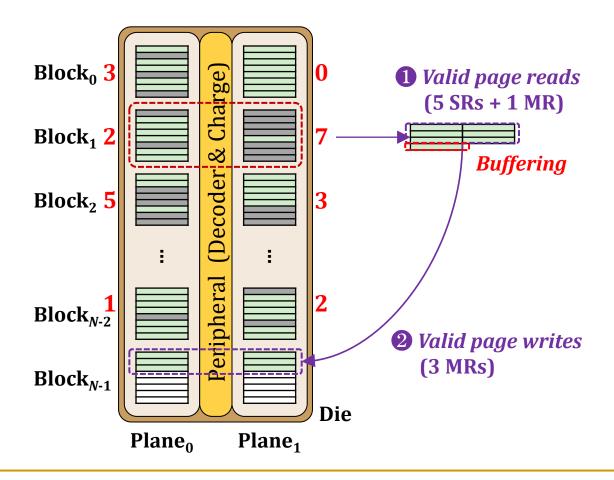

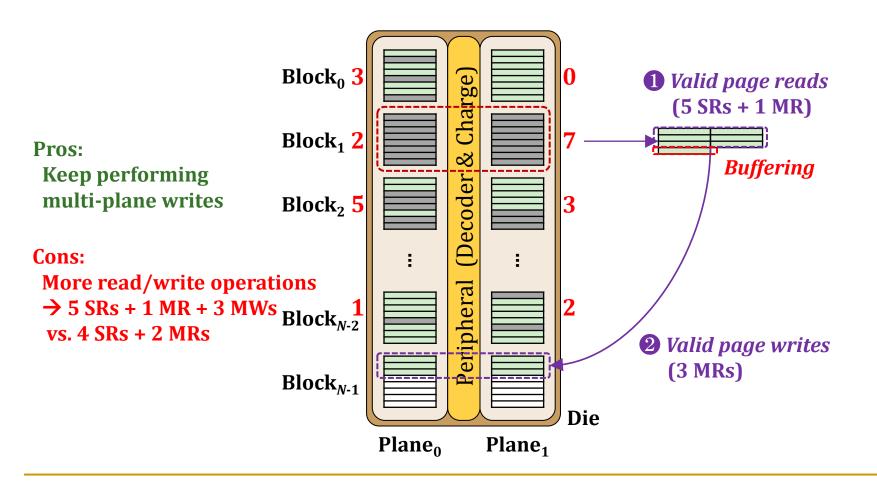

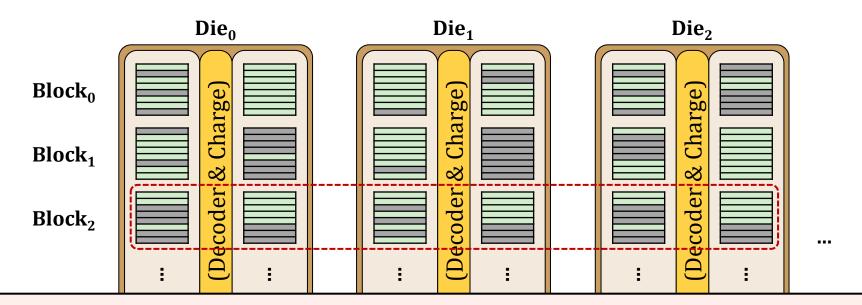

## Recap: Multi-Plane Operations

- Concurrent operations on different planes

- Recall: Planes share WLs and row/column decoders

- Opportunity: Planes can concurrently operate

- Constraints: Only for the same operations on the same page offset

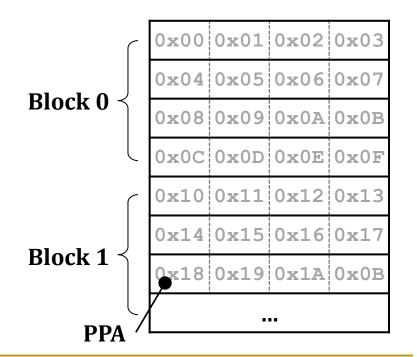

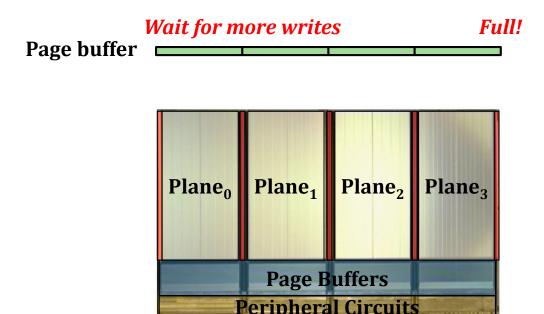

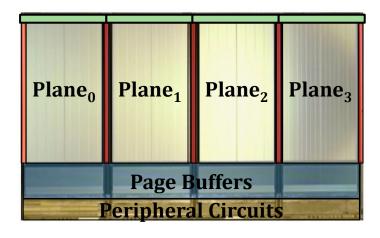

#### Multi-Plane-Aware Data Placement

- To perform as many multi-plane operations as possible

- Flush N<sub>plane</sub> pages at once after buffering them

#### Multi-Plane-Aware Data Placement

- To perform as many multi-plane operations as possible

- Flush N<sub>plane</sub> pages at once after buffering them

Page buffer

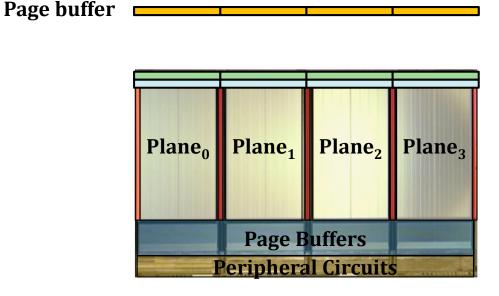

#### Multi-Plane-Aware Data Placement

- To perform as many multi-plane operations as possible

- Flush N<sub>plane</sub> pages at once after buffering them

- Need to keep the write points of all planes to be the same

- Superblock-based block management

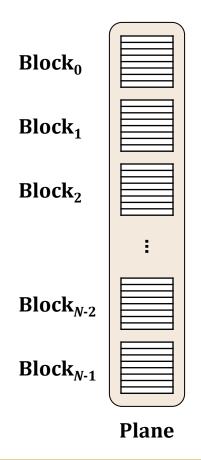

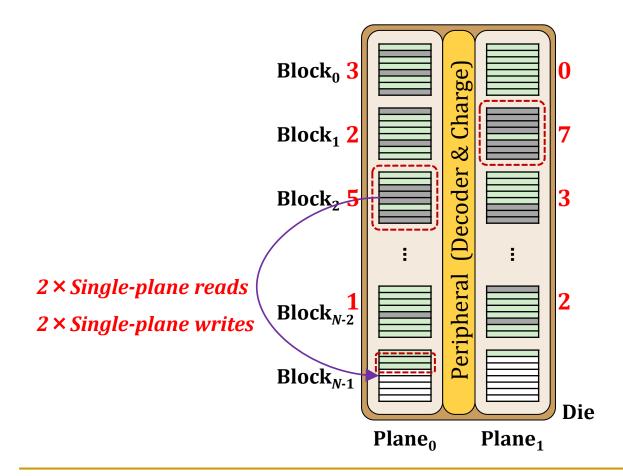

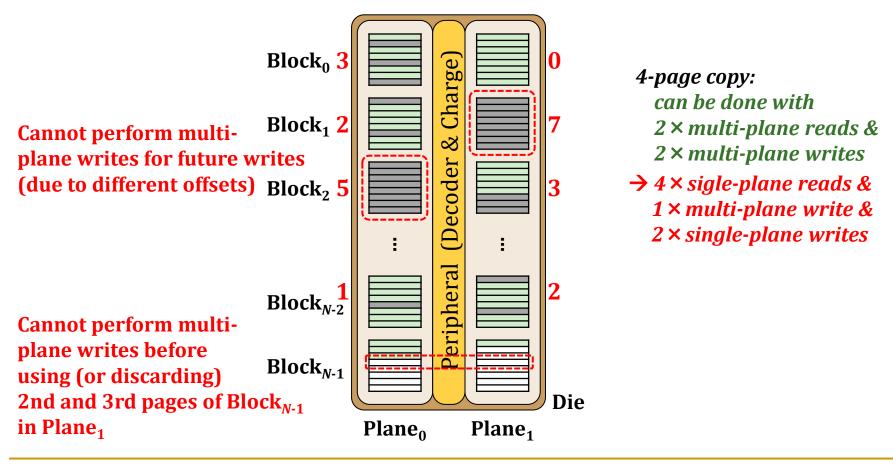

# Multi-Plane-Aware Block Management

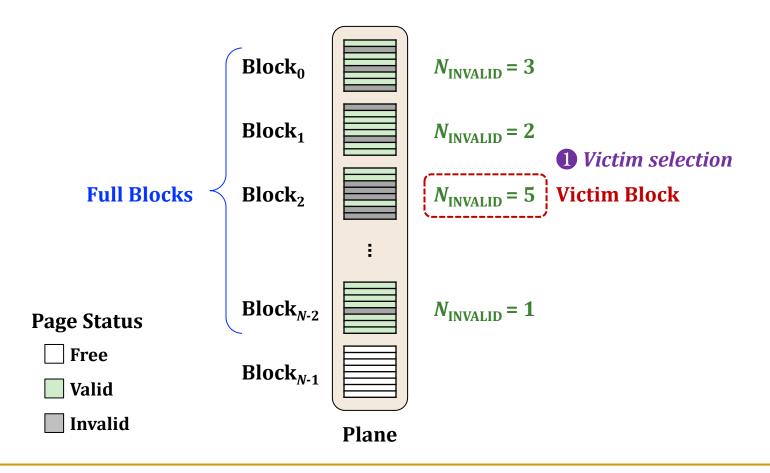

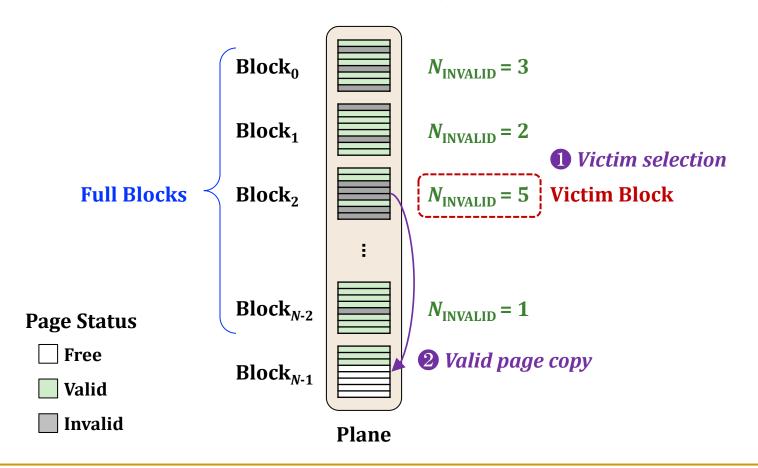

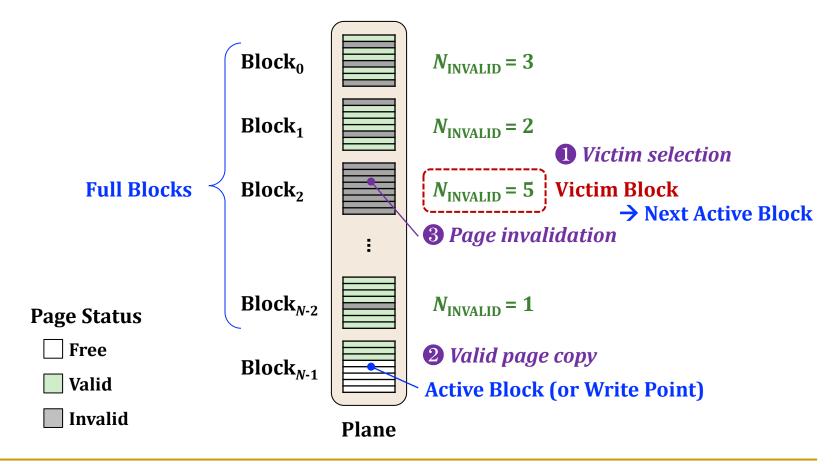

Recap: For reducing the performance overhead of garbage collection, the FTL can select the block with the largest number of invalid pages (called a greedy policy).

# Multi-Plane-Aware Block Management

Recap: For reducing the performance overhead of garbage collection, the FTL can select the block with the largest number of invalid pages (called a greedy policy).

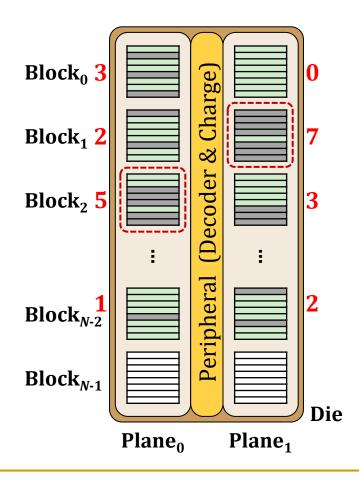

# Multi-Plane-Aware Block Management

Recap: For reducing the performance overhead of garbage collection, the FTL can select the block with the largest number of invalid pages (called a greedy policy).

Recap: For reducing the performance overhead of garbage collection, the FTL can select the block with the largest number of invalid pages (called a greedy policy).

Offset management: Die level or SSD level?

Multi-plane operations can significantly improve SSD performance, but requires proper management in FTL

#### P&S Modern SSDs

Fine-Grained Mapping & Multi-Plane Operation-Aware Block Management

Dr. Jisung Park

Prof. Onur Mutlu

ETH Zürich

Spring 2022

15 April 2022