#### P&S SoftMC

Understanding and Improving Modern DRAM Performance, Reliability, and Security with Hands-On Experiments

Hasan Hassan

Prof. Onur Mutlu

ETH Zürich

Spring 2022

8 March 2022

#### P&S SoftMC: Content

- We will learn in detail how modern DDR4 DRAM operates

- You will learn how to characterize DRAM using an FPGA-based DRAM characterization infrastructure (SoftMC)

- You will use SoftMC to develop your own DRAM experiments and gain hand-on experience in studying DRAM characteristics

## P&S SoftMC: Key Takeaways

- This P&S is aimed at improving your

- Knowledge in Computer Architecture and Memory Systems

- Technical skills in running DRAM experiments using real devices

- Critical thinking and analysis

- Interaction with a nice group of researchers

- Familiarity with key research directions

- Technical presentation of your project

P&S SoftMC: Key Goal

(Learn how to) study real memory devices using an FPGA-based DRAM infrastructure to gain new insights on DRAM behavior

## Prerequisites of the Course

- Digital Design and Computer Architecture (or equivalent course)

- Familiarity with FPGA programming

- Interest in low-level hacking and memory

- Interest in discovering why things do or do not work and solving problems

## Course Info: Who Are We? (I)

#### Onur Mutlu

- Full Professor @ ETH Zurich ITET (INFK), since September 2015

- □ Strecker Professor @ Carnegie Mellon University ECE/CS, 2009-2016, 2016-...

- PhD from UT-Austin, worked at Google, VMware, Microsoft Research, Intel, AMD

- https://people.inf.ethz.ch/omutlu/

- omutlu@gmail.com (Best way to reach me)

- https://people.inf.ethz.ch/omutlu/projects.htm

#### Research and Teaching in:

- Computer architecture, computer systems, hardware security, bioinformatics

- Memory and storage systems

- Hardware security, safety, predictability

- Fault tolerance

- Hardware/software cooperation

- Architectures for bioinformatics, health, medicine

- **..**

## Course Info: Who Are We? (II)

- Lead Supervisor:

- Hasan Hassan

- Supervisors:

- Giray Yaglikci

- Ataberk Olgun

- Haocong Luo

- Minesh Patel

- Jeremie Kim

- Get to know us and our research

- https://safari.ethz.ch/group-members

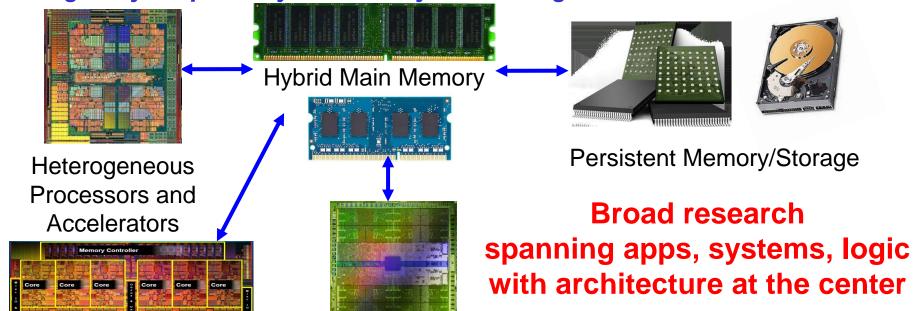

## Onur Mutlu's SAFARI Research Group

#### Computer architecture, HW/SW, systems, bioinformatics, security, memory

https://safari.ethz.ch/safari-newsletter-april-2020/

Think BIG, Aim HIGH!

#### Current Research Focus Areas

#### Research Focus: Computer architecture, HW/SW, bioinformatics

- Memory and storage (DRAM, flash, emerging), interconnects

- Heterogeneous & parallel systems, GPUs, systems for data analytics

- System/architecture interaction, new execution models, new interfaces

- Energy efficiency, fault tolerance, hardware security, performance

- Genome sequence analysis & assembly algorithms and architectures

- Biologically inspired systems & system design for bio/medicine

#### Course Info: How About You?

- Let us know your background, interests

- Why did you join this P&S?

- Please submit HW0

## Course Requirements and Expectations

- Attendance required for all meetings

- Study the learning materials

- Each student will carry out a hands-on project

- Build, implement, code, and design with close engagement from the supervisors

- Participation

- Ask questions, contribute thoughts/ideas

- Read relevant papers

We will help in all projects!

If your work is really good, you may get it published!

#### Course Website

- https://safari.ethz.ch/projects\_and\_seminars/doku.php?id=softmc

- Useful information about the course

- Check your email frequently for announcements

## Meeting 1

#### Required materials:

SoftMC Tutorial Video: <a href="https://youtu.be/909uTQu0lbA">https://youtu.be/909uTQu0lbA</a>

SoftMC lecture: <a href="https://www.youtube.com/watch?v=tnSPEP3t-Ys">https://www.youtube.com/watch?v=tnSPEP3t-Ys</a>

Paper describing SoftMC: <a href="https://people.inf.ethz.ch/omutlu/pub/softMC">https://people.inf.ethz.ch/omutlu/pub/softMC</a> hpca17.pdf

Example RowHammer study using SoftMC: <a href="https://people.inf.ethz.ch/omutlu/pub/Revisiting-RowHammer\_isca20.pdf">https://people.inf.ethz.ch/omutlu/pub/Revisiting-RowHammer\_isca20.pdf</a>

#### Recommended materials:

Example security attack study using SoftMC: <a href="https://people.inf.ethz.ch/omutlu/pub/rowhammer-TRRespass">https://people.inf.ethz.ch/omutlu/pub/rowhammer-TRRespass</a> ieee security privacy20.pdf

Example neural network acceleration study using SoftMC: <a href="https://people.inf.ethz.ch/omutlu/pub/EDEN-efficient-DNN-inference-with-approximate-memory-micro19.pdf">https://people.inf.ethz.ch/omutlu/pub/EDEN-efficient-DNN-inference-with-approximate-memory-micro19.pdf</a>

Example random number generation study using SoftMC: <a href="https://people.inf.ethz.ch/omutlu/pub/drange-dram-latency-based-true-random-number-generator-hpca19.pdf">https://people.inf.ethz.ch/omutlu/pub/drange-dram-latency-based-true-random-number-generator-hpca19.pdf</a>

Example physical unclonable function study using SoftMC: <a href="https://people.inf.ethz.ch/omutlu/pub/dram-latency-puf">https://people.inf.ethz.ch/omutlu/pub/dram-latency-puf</a> <a hr

The original RowHammer study using SoftMC: <a href="https://people.inf.ethz.ch/omutlu/pub/dram-row-hammer\_isca14.pdf">https://people.inf.ethz.ch/omutlu/pub/dram-row-hammer\_isca14.pdf</a>

# Meeting 2 (TBD)

- We will announce the projects and will give you some description about them

- You will have a week to submit your project preferences

- The supervisors would like to help you with selecting a project that matches your interests, skills, and background

- It is important that you study the learning materials before our next meeting!

## Tentative Weekly Schedule

- Week 1 Logistics & Intro to DRAM and SoftMC [HPCA'17]

- Week 2 Revisiting RowHammer [ISCA'20] | Available Projects

- Week 3 Deeper Look Into RowHammer's Sensitivies [MICRO'21] | PU

- Week 4 TRRespass [S&P'20] | Uncovering in-DRAM TRR [MICRO'21] | PU

- Week 5 QUAC-TRNG [ISCA'21] | PU

- Week 6 The Reach Profiler (REAPER) [ISCA'17] | PU

- Week 7 PiDRAM [arXiv'21] | PU

- Week 8+ PU

- **PU** = Project Updates

- How about meeting every Tuesday at 11:00?

#### Performance Assessment

#### We expect you to:

- Learn how DRAM operates and how to perform DRAM characterization using FPGAs

- Achieve the goals of your project

- Deliver your code and results with sufficient documentation

- Prepare a final presentation and present your work to SAFARI

# An Introduction to DRAM and SoftMC

#### **SoftMC**

# A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

<u>Hasan Hassan</u>, Nandita Vijaykumar, Samira Khan, Saugata Ghose, Kevin Chang, Gennady Pekhimenko, Donghyuk Lee, Oguz Ergin, Onur Mutlu

**HPCA 2017**

# Executive Summary

- Two critical problems of DRAM: Reliability and Performance

- Recently-discovered bug: RowHammer

- Characterize, analyze, and understand DRAM cell behavior

- We design and implement SoftMC, an FPGA-based DRAM testing infrastructure

- Flexible and Easy to Use (C++ API)

- Open-source (<u>github.com/CMU-SAFARI/SoftMC</u>)

- We implement two use cases

- A retention time distribution test

- An experiment to validate two latency reduction mechanisms

- SoftMC enables a wide range of studies

#### Outline

- 1. DRAM Basics & Motivation

- 2. SoftMC

- 3. Use Cases

- Retention Time Distribution Study

- Evaluating Recently-Proposed Ideas

- 4. Future Research Directions

- 5. Conclusion

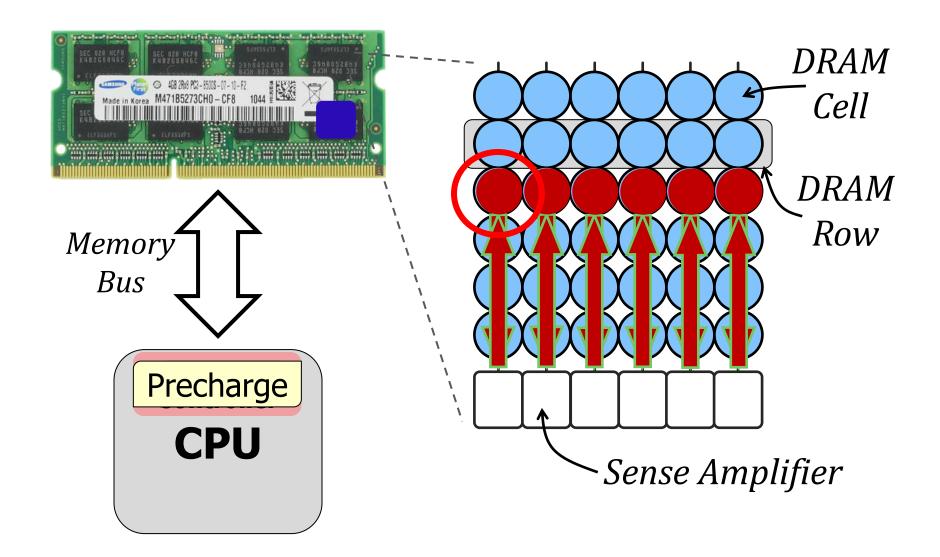

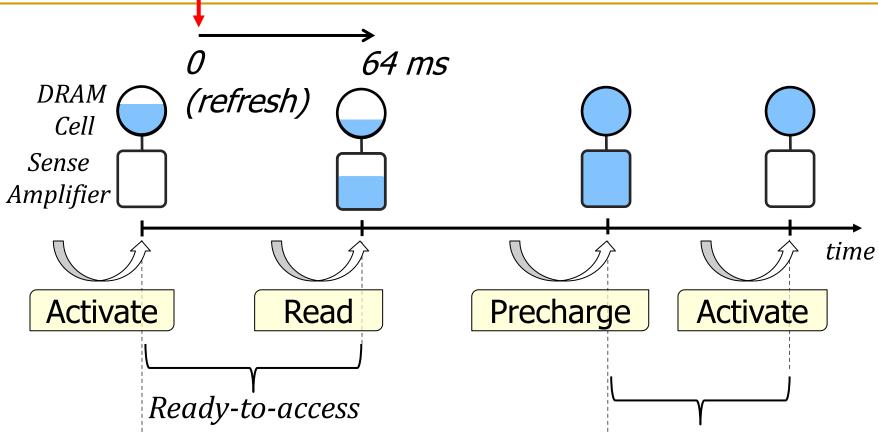

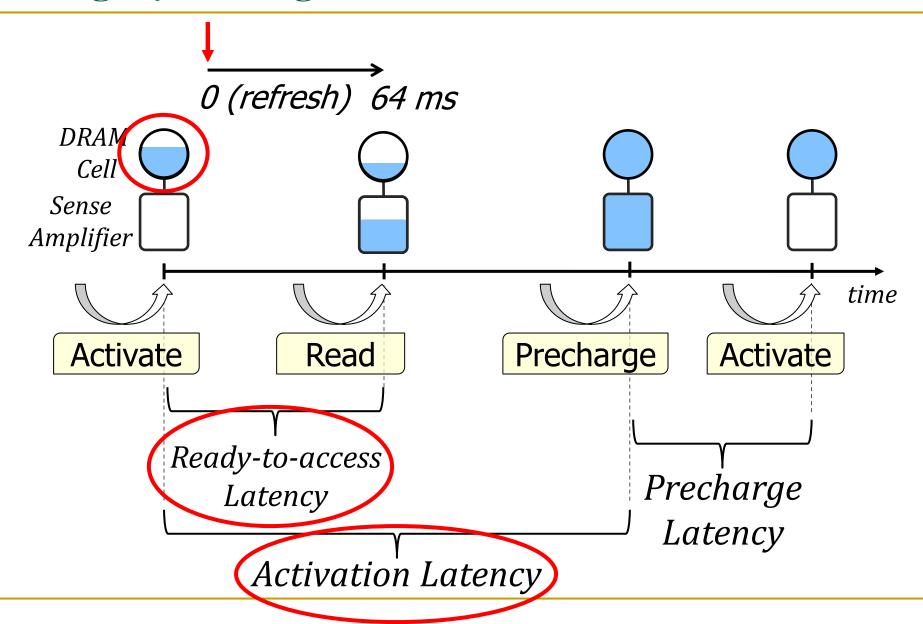

## DRAM Operations

### DRAM Latency

Retention Times. The interval during which the data is retained correctly ain the DRAM cell without accessing it

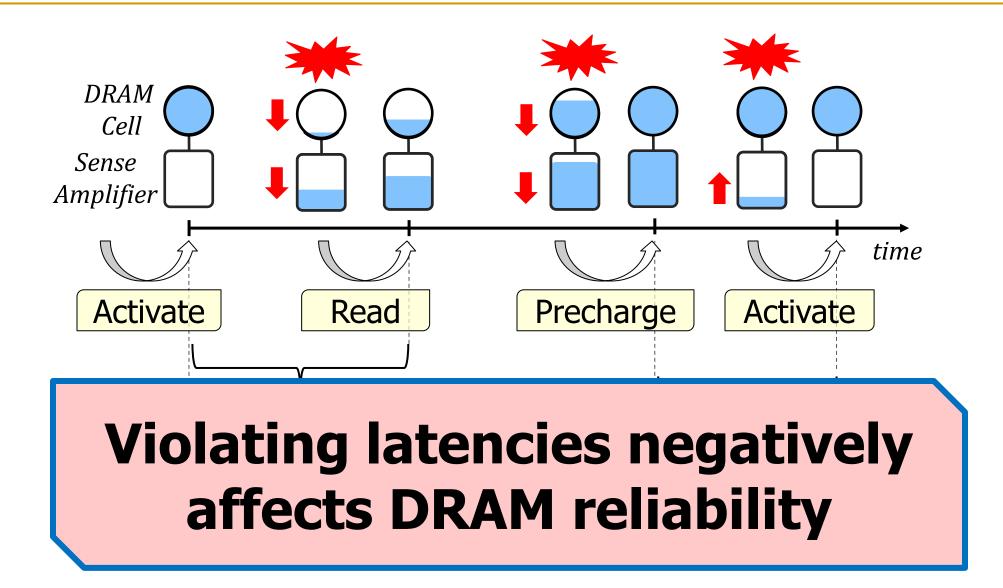

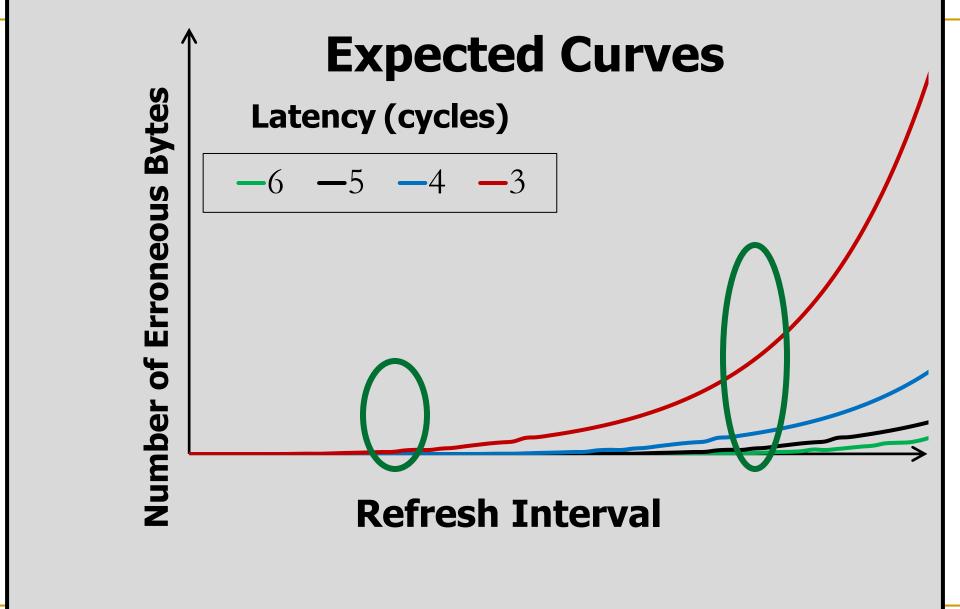

# Latency vs. Reliability

## Other Factors Affecting Reliability and Latency

- Temperature

- Voltage

- Inter-cell Interference

- Manufacturing Process

- Re

To develop new mechanisms improving reliability and latency, we need to better understand the effects of these factors

## Characterizing DRAM

Many of the factors affecting DRAM reliability and latency cannot be properly modeled

We need to perform experimental studies of *real* DRAM chips

#### Outline

#### 1. DRAM Basics & Motivation

- 2. SoftMC

- 3. Use Cases

- Retention Time Distribution Study

- Evaluating Recently-Proposed Ideas

- 4. Future Research Directions

- 5. Conclusion

# Goals of a DRAM Testing Infrastructure

## Flexibility

- Ability to test any DRAM operation

- Ability to test any combination of DRAM operations and custom timing parameters

#### Ease of use

- Simple programming interface (C++)

- Minimal programming effort and time

- Accessible to a wide range of users

- who may lack experience in hardware design

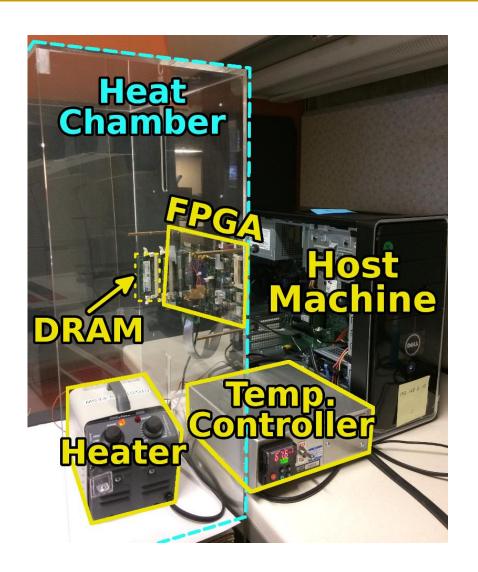

# SoftMC: High-level View

FPGA-based memory characterization infrastructure

Prototype using *Xilinx ML605*

Easily programmable using the C++ API

# SoftMC: Key Components

## 1. SoftMC API

- 2. PCIe Driver

- 3. SoftMC Hardware

## SoftMC API (Old)

#### Writing data to DRAM:

```

InstructionSequence iseq;

iseq.insert(genACT(bank, row));

iseq.insert(genWAIT(tRCD));

iseq.insert(genWR(bank, col, data));

iseq.insert(genWAIT(tCL + tBL + tWR))

iseq.insert(genPRE(bank));

iseq.insert(genWAIT(tRP));

iseq.insert(genEND());

iseq.execute(fpga);

```

Instruction generator functions

## SoftMC API (New)

#### SoftMCPlatform:

- execute() starts execution of a SoftMC program

- receiveData() gets data from PCIe

#### Program:

- add\_inst() adds an instruction

- add\_branch() adds a branch instruction

- add\_label() adds a branch target

#### SoftMC Instructions:

- Arithmetic & Logic: AND, OR, XOR, ADD, SUB, LI, MV, ...

- Scratchpad Memory: LD, ST

- DRAM Commands: ACT, PRE, READ, WRITE, REF, ...

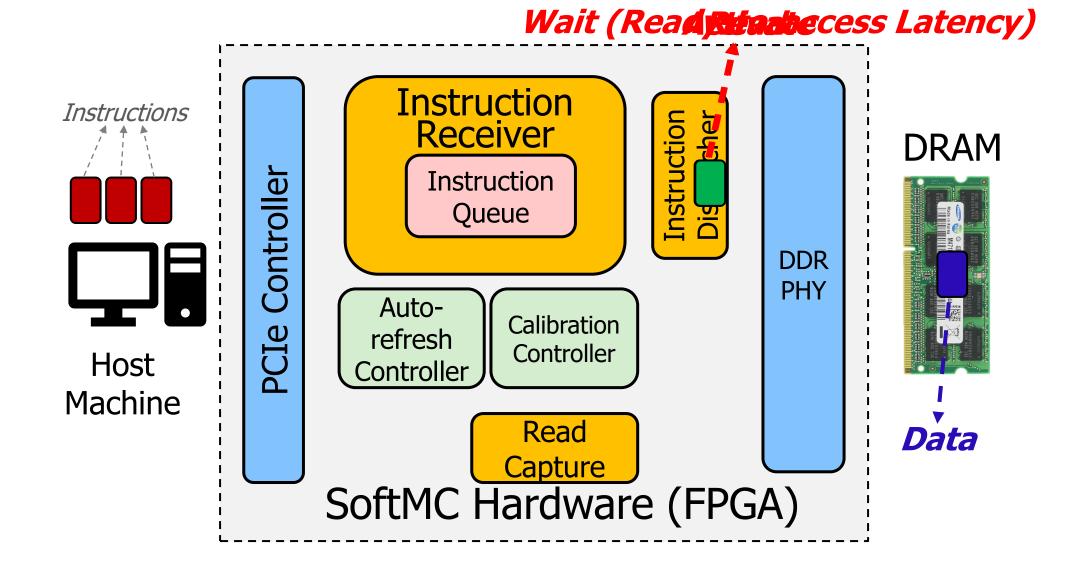

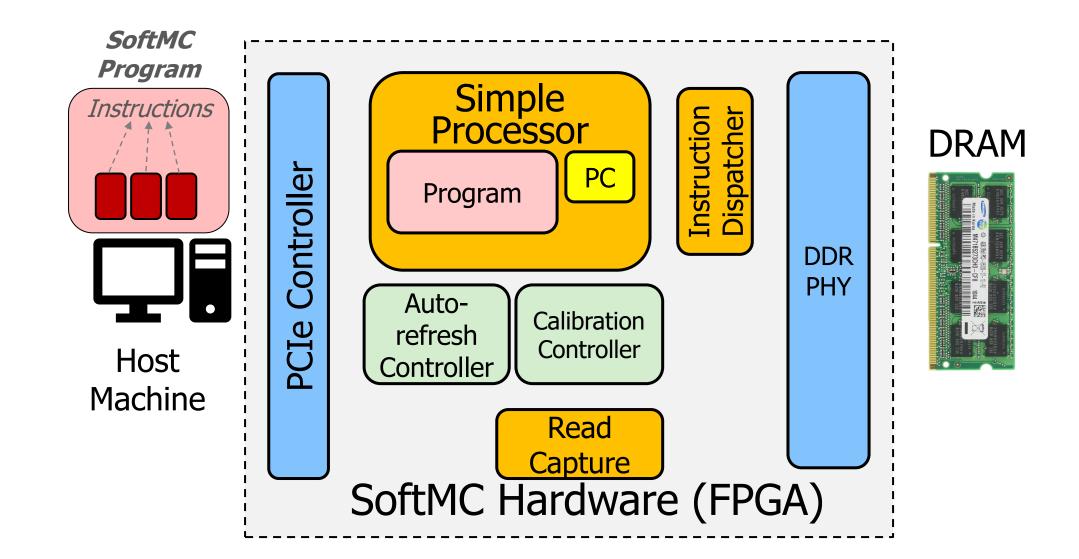

# SoftMC: Key Components

#### 1. SoftMC API

#### 2. PCIe Driver\*

Communicates raw data with the FPGA

#### 3. SoftMC Hardware

<sup>\*</sup> Jacobsen, Matthew, et al. "RIFFA 2.1: A reusable integration framework for FPGA accelerators." TRETS, 2015

## SoftMC Hardware (Old)

# SoftMC Hardware (New)

#### Outline

- 1. DRAM Basics & Motivation

- 2. SoftMC

- 3. Use Cases

- Retention Time Distribution Study

- Evaluating Recently-Proposed Ideas

- 4. Future Research Directions

- 5. Conclusion

## Retention Time Distribution Study

```

InstructionSequence iseq;

2  iseq.insert(genACT(bank, row));

3  iseq.insert(genWAIT(tRCD));

4  for(int col = 0; col < COLUMNS; col++){

5    iseq.insert(genWR(bank, col, data));

6    iseq.insert(genWAIT(tBL));

7  }

8  iseq.insert(genWAIT(tCL + tWR));

9  iseq.insert(genPRE(bank));

10  iseq.insert(genWAIT(tRP));

11  iseq.insert(genEND());

12  iseq.execute(fpga));</pre>

```

Can be implemented with just ~100 lines of code

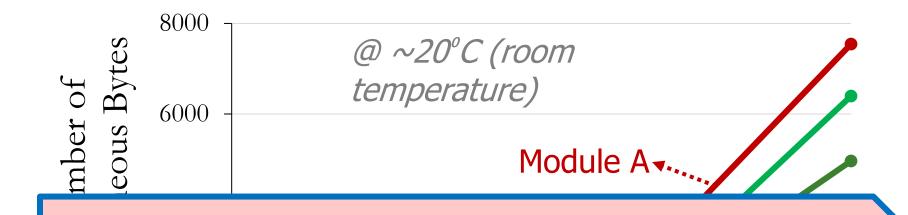

#### Retention Time Test: Results

# Validates the correctness of the SoftMC Infrastructure

## Outline

- 1. DRAM Basics & Motivation

- 2. SoftMC

- 3. Use Cases

- Retention Time Distribution Study

- Evaluating Recently-Proposed Ideas

- 4. Future Research Directions

- 5. Conclusion

# Accessing Highly-charged Cells Faster

NUAT ChargeCache

(Shin+, HPCA 2014) (Hassan+, HPCA 2016)

A highly-charged cell can be accessed with low latency

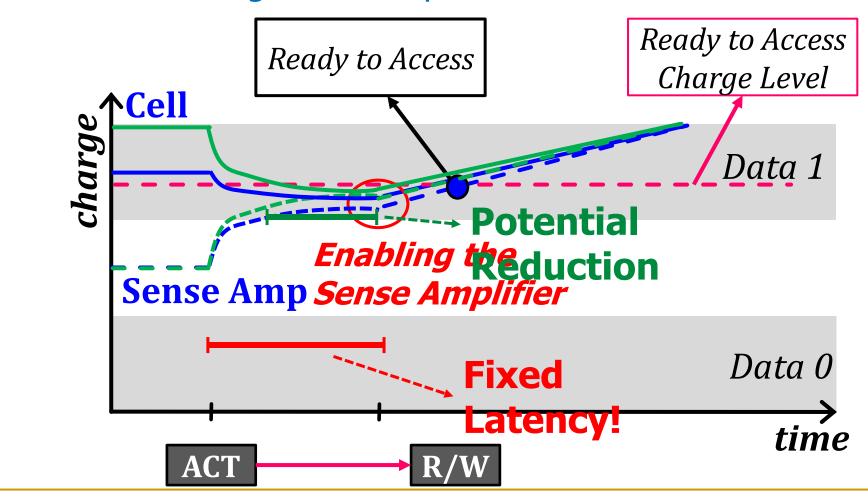

# How a Highly-Charged Cell Is Accessed Faster?

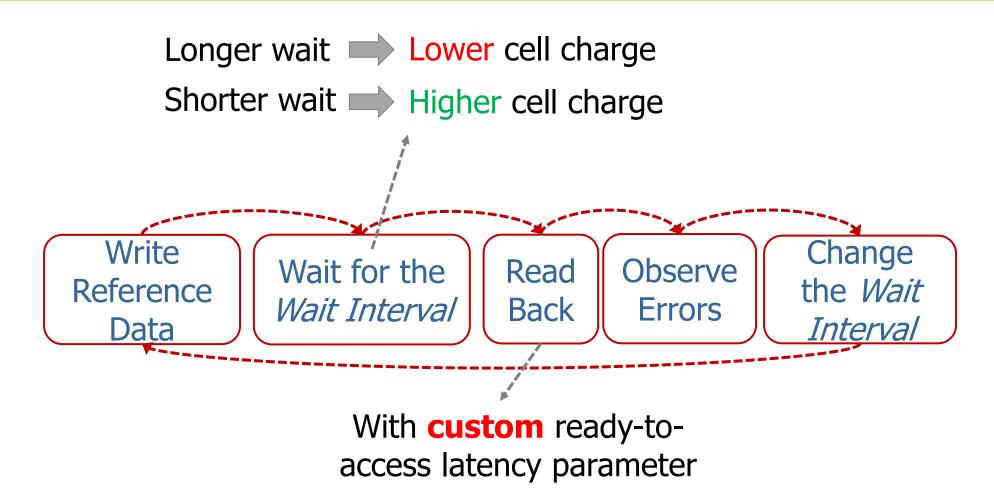

# Ready-to-access Latency Test

Can be implemented with just ~150 lines of code

Ready-to-access Latency: Results

# Why Don't We See the Latency Reduction Effect?

The memory controller cannot externally control when a sense amplifier gets enabled in existing DRAM chips

# Outline

- 1. DRAM Basics & Motivation

- 2. SoftMC

- 3. Use Cases

- Retention Time Distribution Study

- Evaluating Recently-Proposed Ideas

- 4. Future Research Directions

- 5. Conclusion

#### Future Research Directions

- More Characterization of DRAM

- How are the cell characteristics changing with different generations of technology nodes?

- What types of usage accelerate aging?

- Characterization of Non-volatile Memory

- Extensions

- Memory Scheduling

- Workload Analysis

- Testbed for in-memory Computation

#### Outline

- 1. DRAM Basics & Motivation

- 2. SoftMC

- 3. Use Cases

- Retention Time Distribution Study

- Evaluating Recently-Proposed Ideas

- 4. Future Research Directions

- 5. Conclusion

## Conclusion

- SoftMC: First publicly-available FPGA-based DRAM testing infrastructure

- Flexible and Easy to Use

- Implemented two use cases

- Retention Time Distribution Study

- Evaluation of two recently-proposed latency reduction mechanisms

- SoftMC can enable many other studies, ideas, and methodologies in the design of future memory systems

- Download our first prototype

github.com/CMU-SAFARI/SoftMC

#### **SoftMC**

# A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

<u>Hasan Hassan</u>, Nandita Vijaykumar, Samira Khan, Saugata Ghose, Kevin Chang, Gennady Pekhimenko, Donghyuk Lee, Oguz Ergin, Onur Mutlu

**HPCA 2017**

## P&S SoftMC

Understanding and Improving Modern DRAM Performance, Reliability, and Security with Hands-On Experiments

Hasan Hassan

Prof. Onur Mutlu

ETH Zürich

Spring 2022

8 March 2022