#### P&S SoftMC

Understanding and Improving Modern DRAM Performance, Reliability, and Security with Hands-On Experiments

Hasan Hassan

Prof. Onur Mutlu

ETH Zürich

Spring 2022

22 March 2022

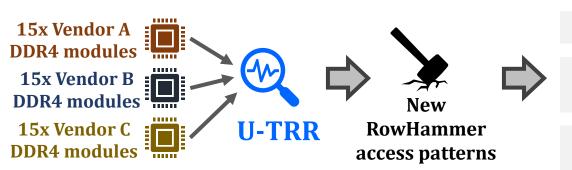

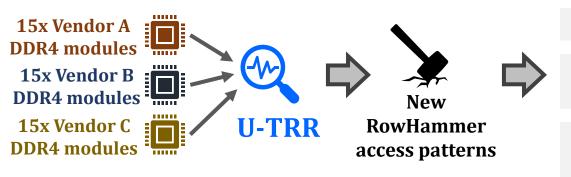

### U-TRR

**Uncovering in-DRAM RowHammer Protection Mechanisms:** A New Methodology, Custom RowHammer Patterns, and Implications

#### Hasan Hassan

Yahya Can Tugrul Jeremie S. Kim Victor van der Veen Kaveh Razavi Onur Mutlu

## Summary

DRAM **RowHammer** vulnerability leads to critical reliability and security issues

#### Target Row Refresh (TRR):

a set of obscure, undocumented, and proprietary RowHammer mitigation techniques

Is TRR fully secure? How can we validate its security guarantees?

**U-TRR**

A new methodology that leverages *data retention failures* to uncover the inner workings of TRR and study its security

High-Level Operation

- 1) Profile the retention time of a row R

- 2) Find when TRR refreshes R to understand the underlying TRR mechanism

All 45 modules we test are vulnerable

**99.9% of rows** in a DRAM bank experience at least one RowHammer bit flip

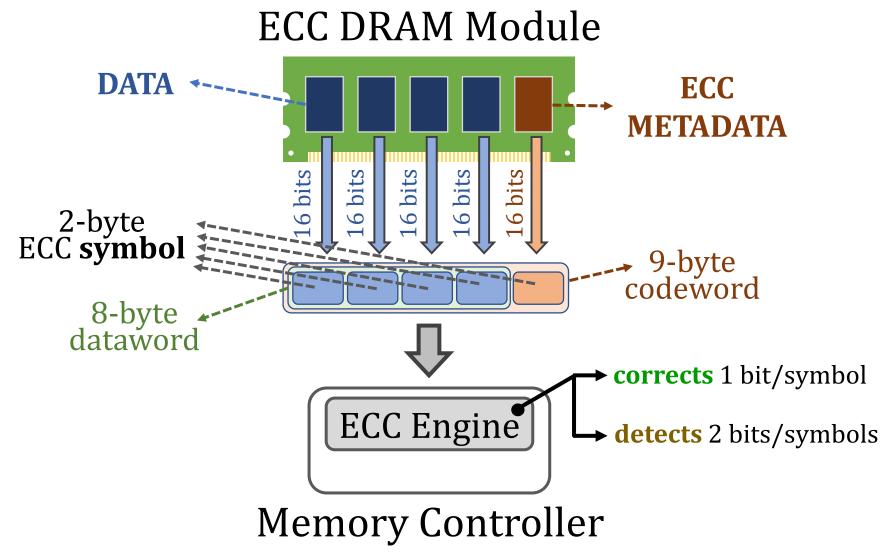

Up to **7** RowHammer **bit flips** in an 8-byte dataword, **making ECC ineffective**

U-TRR can enable **more secure** RowHammer solutions

### Outline

- 1. DRAM Operation Basics

- 2. RowHammer & Target Row Refresh

- 3. The U-TRR Methodology

- 4. Observations & New RowHammer Access Patterns

- 5. RowHammer Bit Flip Analysis

- 6. Takeaways and Conclusion

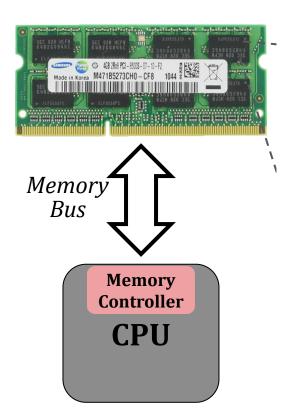

## **DRAM Organization**

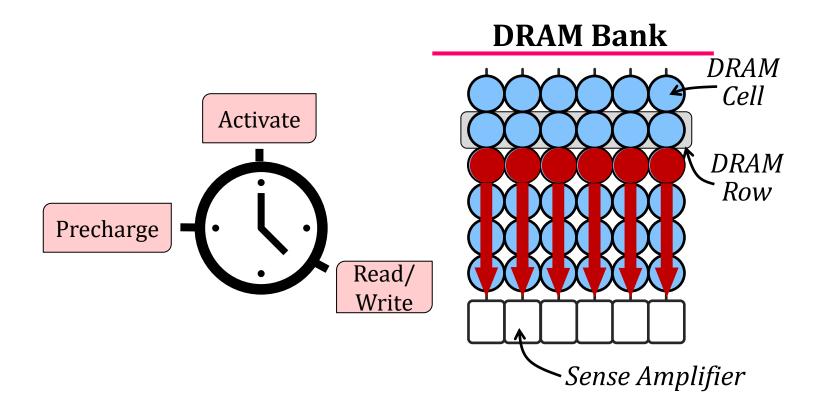

## **Accessing DRAM**

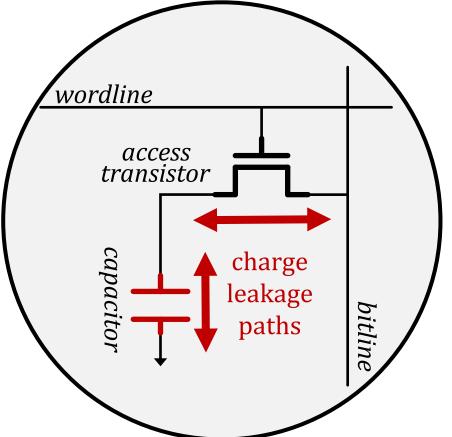

## DRAM Cell Leakage

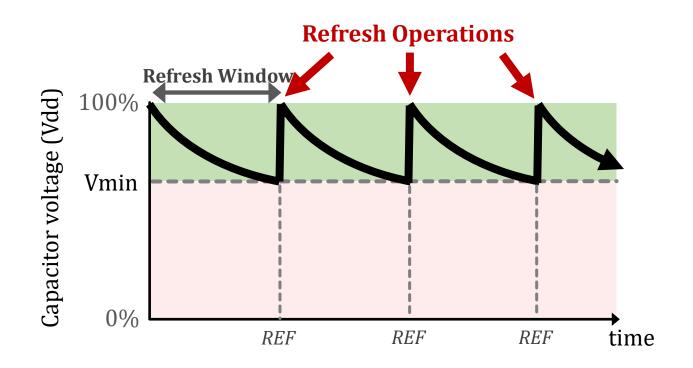

Each cell encodes information in **leaky** capacitors

Stored data is **corrupted** if too much charge leaks (i.e., the capacitor voltage degrades too much)

### **DRAM Refresh**

Periodic refresh operations preserve stored data

### Outline

- 1. DRAM Operation Basics

- 2. RowHammer & Target Row Refresh

- 3. The U-TRR Methodology

- 4. Observations & New RowHammer Access Patterns

- 5. RowHammer Bit Flip Analysis

- 6. Takeaways and Conclusion

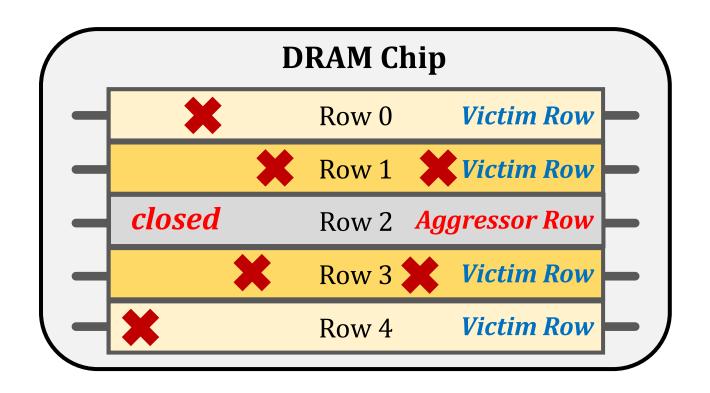

## The RowHammer Vulnerability

Repeatedly **opening** (activating) and **closing** (precharging) a DRAM row causes **RowHammer bit flips** in nearby cells

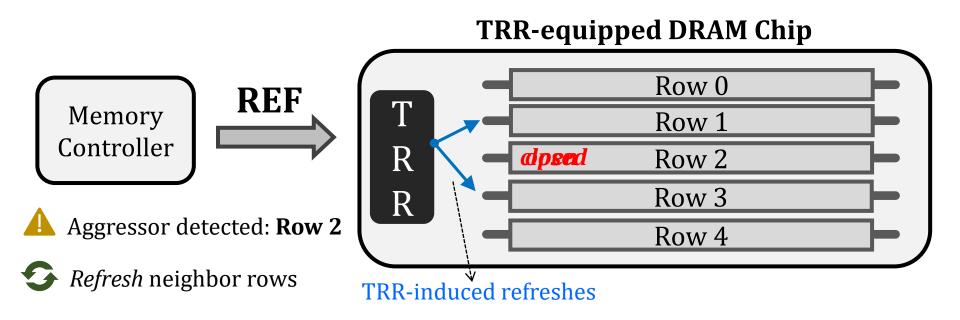

## Target Row Refresh (TRR)

DRAM vendors equip their DRAM chips with a *proprietary* mitigation mechanisms known as **Target Row Refresh (TRR)**

Key Idea: TRR refreshes nearby rows upon detecting an aggressor row

### The Problem with TRR

TRR is obscure, undocumented, and proprietary

We cannot easily study the security properties of TRR

### Goal

#### Study in-DRAM TRR mechanisms to

1 understand how they operate

2 assess their security

3 secure DRAM completely against RowHammer

### Outline

- 1. DRAM Operation Basics

- 2. RowHammer & Target Row Refresh

- 3. The U-TRR Methodology

- 4. Observations & New RowHammer Access Patterns

- 5. RowHammer Bit Flip Analysis

- 6. Takeaways and Conclusion

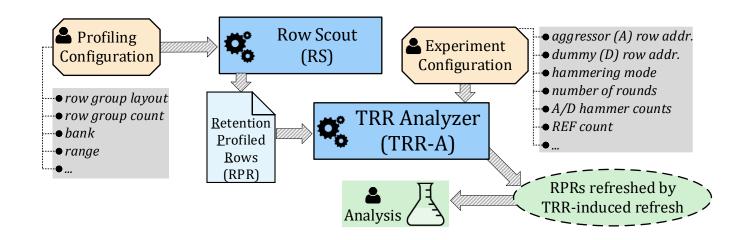

### Overview of U-TRR

**U-TRR:** A new methodology to uncover the inner workings of TRR

**Key idea:** Use data retention failures as a side channel to detect when a row is refreshed by TRR

## **High-Level U-TRR Operation**

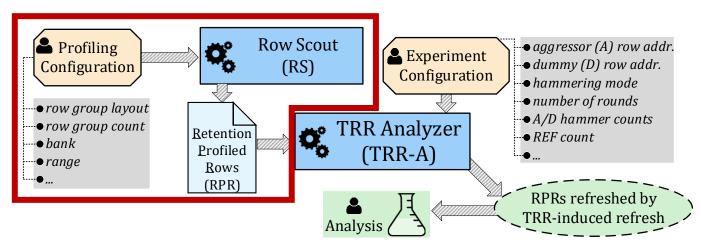

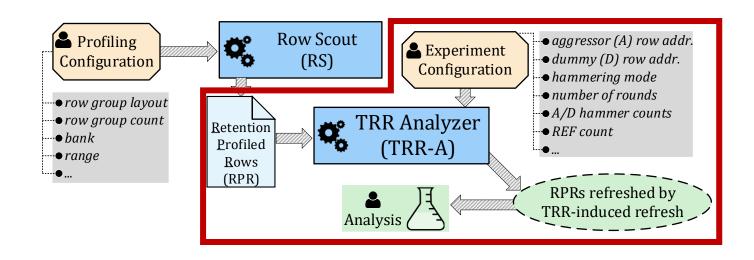

# U-TRR has two main components: Row Scout (RS) and TRR Analyzer (TRR-A)

**Row Scout:** finds a **set of DRAM rows** that meet certain requirements as needed by TRR-A and **identifies the data retention times** of these rows

TRR Analyzer: uses RS-provided rows to distinguish between TRR-induced and regular refreshes, and thus builds an understanding of the underlying TRR mechanism

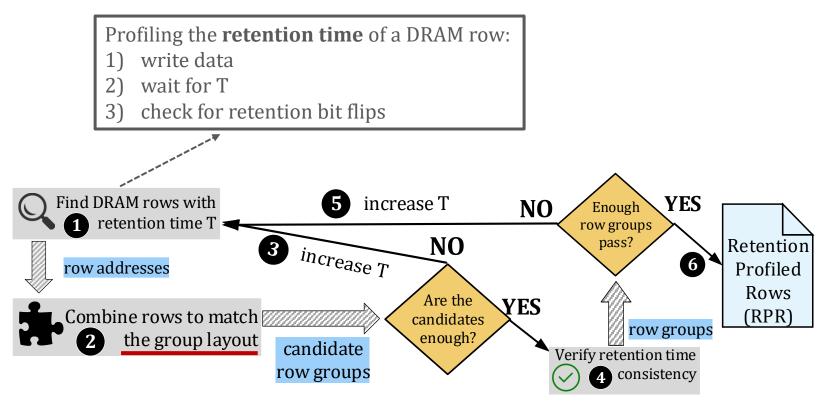

## Row Scout (RS)

**Goal:** Identify a list of *useful* DRAM rows and their *retention times* Row Scout **must** find:

- ✓ Rows with **consistent\*** retention times

- > To correctly infer whether a row has been refreshed

- ✓ **Multiple rows** that are located at *certain configurable distances* and have the *same retention time* (i.e., Row Group)

- To observe whether TRR can refresh multiple rows at the same time

\* The retention time of a DRAM row may change over time due to Variable Retention Time (VRT) effects

## Row Scout (RS) Operation

Row Group: V V V

## TRR Analyzer (TRR-A)

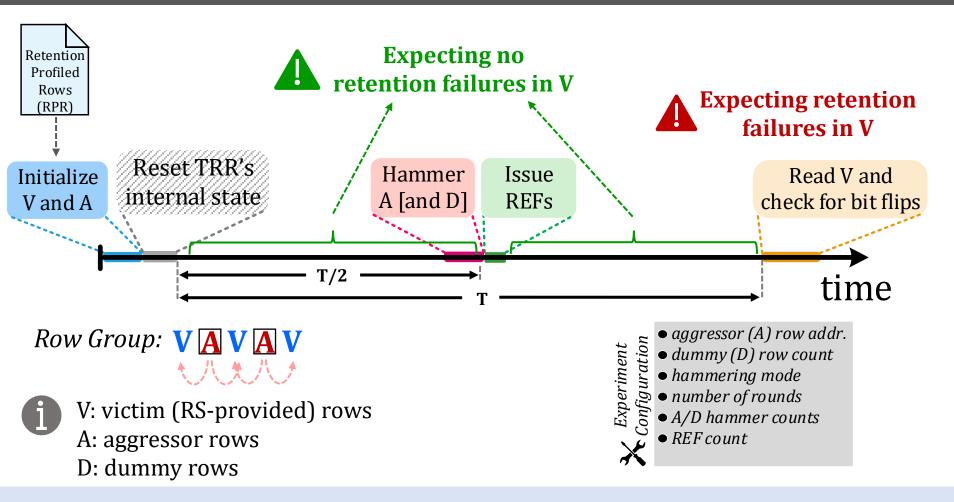

**Goal:** Use RS-provided rows to determine when TRR refreshes a victim row

#### **High-level Operation:**

- 1) Run a certain DRAM access pattern (i.e., RowHammer attack)

- 2) Monitor retention failures in RS-provided rows to determine when TRR refreshes any of these rows

- 3) Develop an understanding of the underlying TRR operation

## TRR Analyzer (TRR-A) Operation

TRR-A helps to understand how TRR operates based on when Retention Profiled Rows are refreshed by TRR

### Outline

- 1. DRAM Operation Basics

- 2. RowHammer & Target Row Refresh

- 3. The U-TRR Methodology

- 4. Observations & New RowHammer Access Patterns

- 5. RowHammer Bit Flip Analysis

- **6.** Takeaways and Conclusion

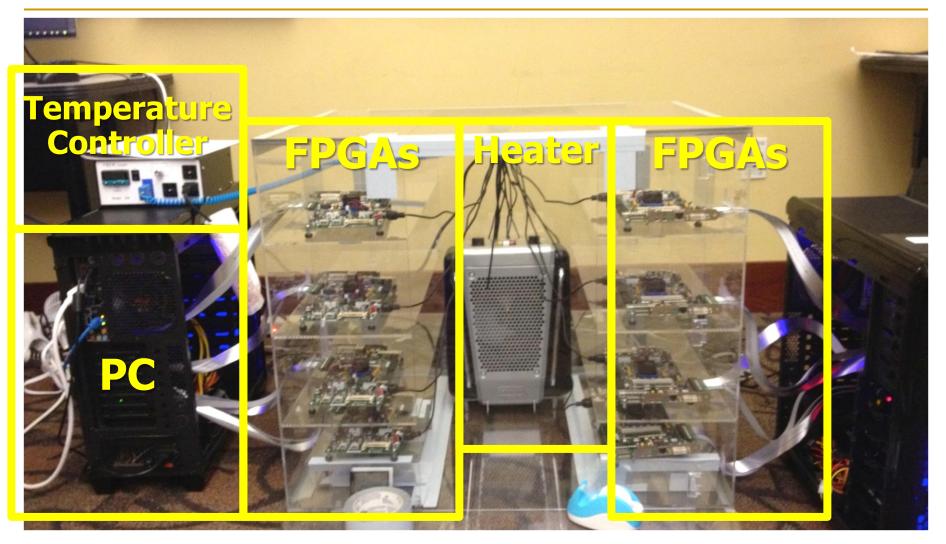

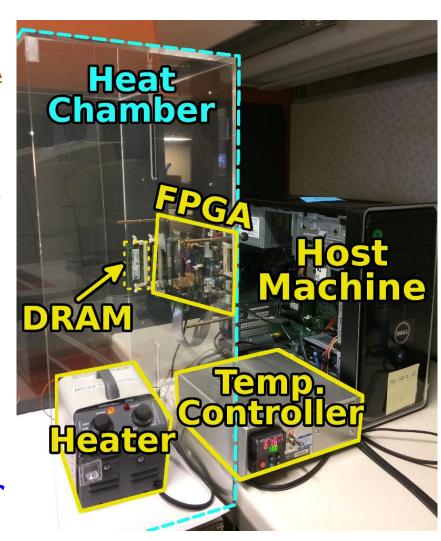

## DRAM Testing Infrastructure

We implement U-TRR using FPGA-based *SoftMC* [Hassan+, HPCA'18] modified to support DDR4 DRAM

|        |                 |                           | _            |       | _    |                        |                                      |                        |                       | _               |                     |                        |                            | 7 0 7 1                               |  |

|--------|-----------------|---------------------------|--------------|-------|------|------------------------|--------------------------------------|------------------------|-----------------------|-----------------|---------------------|------------------------|----------------------------|---------------------------------------|--|

| Module | Date<br>(yy-ww) | Chip<br>Density<br>(Gbit) | Organization |       |      |                        | Our Key TRR Observations and Results |                        |                       |                 |                     |                        |                            |                                       |  |

|        |                 |                           | Ranks        | Banks | Pins | $HC_{first}^{\dagger}$ | Version                              | Aggressor<br>Detection | Aggressor<br>Capacity | Per-Bank<br>TRR | TRR-to-REF<br>Ratio | Neighbors<br>Refreshed | % Vulnerable<br>DRAM Rows† | Max. Bit Flips<br>per Row per Hammer† |  |

| A0     | 19-50           | 8                         | 1            | 16    | 8    | 16K                    | $A_{TRR1}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 4                      | 73.3%                      | 1.16                                  |  |

| A1-5   | 19-36           | 8                         | 1            | 8     | 16   | 13K-15K                | $A_{TRR1}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 4                      | 99.2% - 99.4%              | 2.32 - 4.73                           |  |

| A6-7   | 19-45           | 8                         | 1            | 8     | 16   | 13K-15K                | $A_{TRR1}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 4                      | 99.3% - 99.4%              | 2.12 - 3.86                           |  |

| A8-9   | 20-07           | 8                         | 1            | 16    | 8    | 12K-14K                | $A_{TRR1}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 4                      | 74.6% - 75.0%              | 1.96 - 2.96                           |  |

| A10-12 | 19-51           | 8                         | 1            | 16    | 8    | 12K-13K                | $A_{TRR1}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 4                      | 74.6% - 75.0%              | 1.48 - 2.86                           |  |

| A13-14 | 20-31           | 8                         | 1            | 8     | 16   | 11K-14K                | $A_{TRR2}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 2                      | 94.3% - 98.6%              | 1.53 - 2.78                           |  |

| B0     | 18-22           | 4                         | 1            | 16    | 8    | 44K                    | $B_{TRR1}$                           | Sampling-based         | 1                     | Х               | 1/4                 | 2                      | 99.9%                      | 2.13                                  |  |

| B1-4   | 20-17           | 4                         | 1            | 16    | 8    | 159K-192K              | $B_{TRR1}$                           | Sampling-based         | 1                     | ×               | 1/4                 | 2                      | 23.3% - 51.2%              | 0.06 - 0.11                           |  |

| B5-6   | 16-48           | 4                         | 1            | 16    | 8    | 44K-50K                | $B_{TRR1}$                           | Sampling-based         | 1                     | ×               | 1/4                 | 2                      | 99.9%                      | 1.85 - 2.03                           |  |

| B7     | 19-06           | 8                         | 2            | 16    | 8    | 20K                    | $B_{TRR1}$                           | Sampling-based         | 1                     | ×               | 1/4                 | 2                      | 99.9%                      | 31.14                                 |  |

| B8     | 18-03           | 4                         | 1            | 16    | 8    | 43K                    | $B_{TRR1}$                           | Sampling-based         | 1                     | ×               | 1/4                 | 2                      | 99.9%                      | 2.57                                  |  |

| B9-12  | 19-48           | 8                         | 1            | 16    | 8    | 42K-65K                | $B_{TRR2}$                           | Sampling-based         | 1                     | ×               | 1/9                 | 2                      | 36.3% - 38.9%              | 16.83 - 24.26                         |  |

| B13-14 | 20-08           | 4                         | 1            | 16    | 8    | 11K-14K                | $B_{TRR3}$                           | Sampling-based         | 1                     | ✓               | 1/2                 | 4                      | 99.9%                      | 16.20 - 18.12                         |  |

| C0-3   | 16-48           | 4                         | 1            | 16    | x8   | 137K-194K              | $C_{TRR1}$                           | Mix                    | Unknown               | ✓               | 1/17                | 2                      | 1.0% - 23.2%               | 0.05 - 0.15                           |  |

| C4-6   | 17-12           | 8                         | 1            | 16    | x8   | 130K-150K              | $C_{TRR1}$                           | Mix                    | Unknown               | ✓               | 1/17                | 2                      | 7.8% - 12.0%               | 0.06 - 0.08                           |  |

| C7-8   | 20-31           | 8                         | 1            | 8     | x16  | 40K-44K                | $C_{TRR1}$                           | Mix                    | Unknown               | ✓               | 1/17                | 2                      | 39.8% - 41.8%              | 9.66 - 14.56                          |  |

| C9-11  | 20-31           | 8                         | 1            | 8     | x16  | 42K-53K                | $C_{TRR2}$                           | Mix                    | Unknown               | ✓               | 1/9                 | 2                      | 99.7%                      | 9.30 - 32.04                          |  |

| C12-14 | 20-46           | 16                        | 1            | 8     | x16  | 6K-7K                  | $C_{TRR3}$                           | Mix                    | Unknown               | ✓               | 1/8                 | 2                      | 99.9%                      | 4.91 - 12.64                          |  |

**Table 1 in our paper** provides more information about the analyzed modules

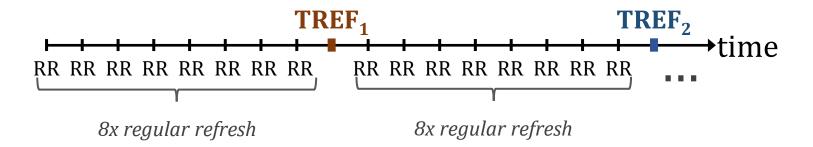

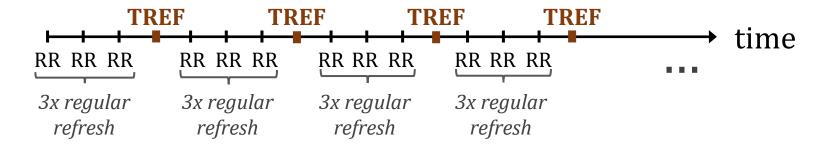

## **Key Observations: Vendor A**

#### Refresh Types:

- Regular Refresh (RR)

- TRR-capable Refresh (TREF<sub>1</sub> and TREF<sub>2</sub>)

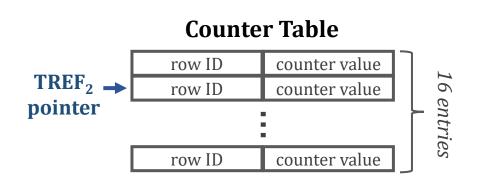

**Observation:** TRR tracks potentially aggressor rows using a Counter Table

**TREF**<sub>1</sub>: Refreshes the victims of **row ID** with the **largest counter value**

**TREF**<sub>2</sub>: Refreshes the victims of **row ID** that TREF<sub>2</sub> pointer refers to

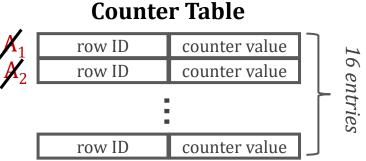

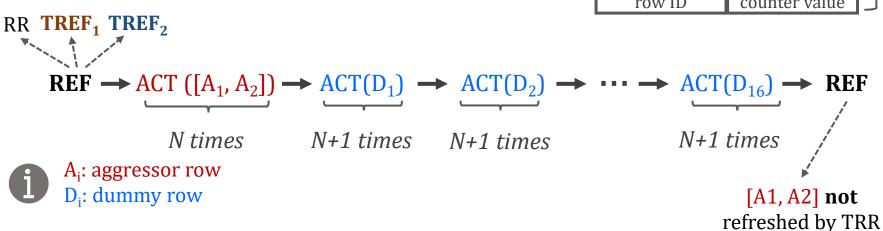

## Circumventing Vendor A's TRR

**Approach: Ensure** an aggressor row is **discarded** from the *Counter Table* **prior** to a REF command

This RowHammer access pattern requires synchronizing accesses with REF commands

Circumventing Vendor A's TRR by discarding the actual aggressor rows from the Counter Table

## **Key Observations: Vendor B**

#### Refresh Types:

- Regular Refresh (RR)

- TRR-capable Refresh (TREF)

**Observation 1:** TRR *probabilistically* samples the address of an activated row

**Observation 2:** A newly-sampled row overwrites the previously-sampled one

**TREF:** Refreshes the victims of the **last sampled row**

## Circumventing Vendor B's TRR

**Approach:** Maximize the **dummy** row hammers **after** hammering the **aggressor** rows and **before** the next **TREF**

TREF

$$\rightarrow$$

ACT ([A<sub>1</sub>, A<sub>2</sub>])  $\rightarrow$  ACT(D<sub>1</sub>)  $\rightarrow$  TREF

N times

[A1, A2] not refreshed by TRR

Circumventing Vendor B's TRR by making it replace a sampled aggressor row by sampling a dummy row

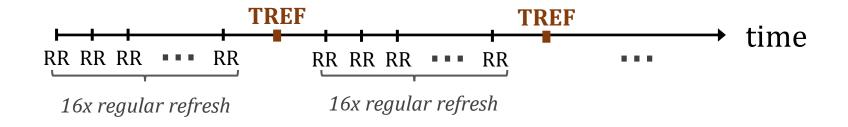

## **Key Observations: Vendor C**

#### Refresh Types:

- Regular Refresh (RR)

- TRR-capable Refresh (TREF)

**Observation 1:** TRR detects an aggressor row only among the first 2K ACT commands issued after a **TREF**

**Observation 2:** Rows activated earlier within the 2K ACT commands are more likely to be detected by TRR

**TREF:** Detects an aggressor row only among the first 2K ACT commands while favoring the earlier activations more

## Circumventing Vendor C's TRR

**Approach:** Hammer dummy rows before aggressor rows to maximize the probability of TRR detecting a dummy row

TREF

$$\rightarrow$$

ACT(D<sub>1</sub>)  $\rightarrow$  ACT([A<sub>1</sub>, A<sub>2</sub>])  $\rightarrow$  TREF

N times

M times

[A1, A2] not refreshed by TRR

Circumventing Vendor C's TRR by first hammering dummy rows to make aggressor rows less likely to be detected

### Outline

- 1. DRAM Operation Basics

- 2. RowHammer & Target Row Refresh

- 3. The U-TRR Methodology

- 4. Observations & New RowHammer Access Patterns

- **5.** RowHammer Bit Flip Analysis

- **6.** Takeaways and Conclusion

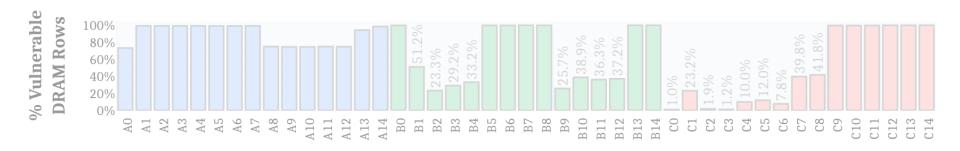

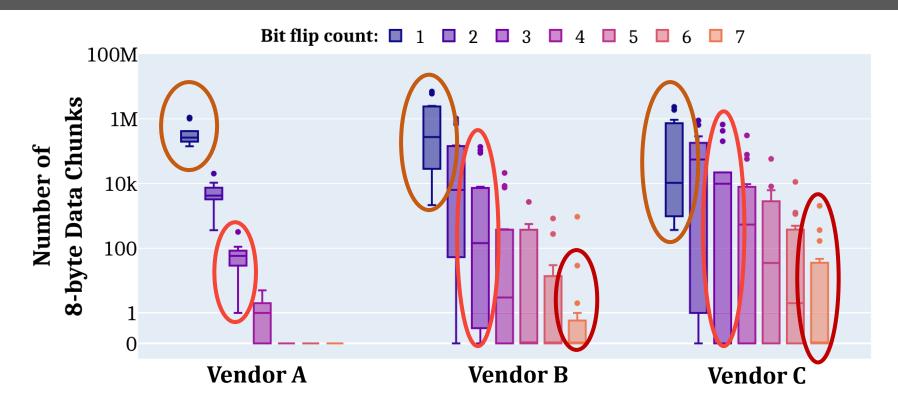

#### **Bypassing TRR with New RowHammer Access Patterns**

We craft new RowHammer access patterns that circumvent TRR of three major DRAM vendors

On the **45** DDR4 modules we test, the new access patterns cause a large number of RowHammer bit flips

#### **Effect on Individual Rows**

All 45 modules we tested are vulnerable to our new RowHammer access patterns

Our RowHammer access patterns cause bit flips in more than 99.9% of the rows

Why are some modules less vulnerable?

- 1) Fundamentally less vulnerable to RowHammer

- 2) Different TRR mechanisms

- 3) Unique row organization

### **Effect on Individual Rows**

All 45 modules we tested are vulnerable to our new RowHammer access patterns

Our RowHammer access patterns cause bit flips in more than 99.9% of the rows

Our access patterns successfully circumvent the TRR implementations of all three major DRAM vendors

3) Unique row organization

#### Can ECC Protect Against Our Access Patterns?

#### Bypassing ECC with New RowHammer Patterns

Modules from all three vendors have many 8-byte data chunks with 3 and more (up to 7) RowHammer bit flips

Conventional DRAM ECC cannot protect against our new RowHammer access patterns

#### Other Observations and Results in the Paper

- More observations on the TRRs of the three vendors

- Detailed description of the crafted access patterns

- Hammers per aggressor row sensitivity analysis

- Observations and results for individual modules

• ...

|        |                 |                           | •            |       | •    |                        |                                      |                        |                       | _               |                     |                        |                            |                                       |  |

|--------|-----------------|---------------------------|--------------|-------|------|------------------------|--------------------------------------|------------------------|-----------------------|-----------------|---------------------|------------------------|----------------------------|---------------------------------------|--|

| Module | Date<br>(yy-ww) | Chip<br>Density<br>(Gbit) | Organization |       |      |                        | Our Key TRR Observations and Results |                        |                       |                 |                     |                        |                            |                                       |  |

|        |                 |                           | Ranks        | Banks | Pins | $HC_{first}^{\dagger}$ | Version                              | Aggressor<br>Detection | Aggressor<br>Capacity | Per-Bank<br>TRR | TRR-to-REF<br>Ratio | Neighbors<br>Refreshed | % Vulnerable<br>DRAM Rows† | Max. Bit Flips<br>per Row per Hammer† |  |

| A0     | 19-50           | 8                         | 1            | 16    | 8    | 16 <i>K</i>            | $A_{TRR1}$                           | Counter-based          | 16                    | /               | 1/9                 | 4                      | 73.3%                      | 1.16                                  |  |

| A1-5   | 19-36           | 8                         | 1            | 8     | 16   | 13K-15K                | $A_{TRR1}$                           | Counter-based          | 16                    | /               | 1/9                 | 4                      | 99.2% - 99.4%              | 2.32 - 4.73                           |  |

| A6-7   | 19-45           | 8                         | 1            | 8     | 16   | 13K-15K                | $A_{TRR1}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 4                      | 99.3% - 99.4%              | 2.12 - 3.86                           |  |

| A8-9   | 20-07           | 8                         | 1            | 16    | 8    | 12K-14K                | $A_{TRR1}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 4                      | 74.6% - 75.0%              | 1.96 - 2.96                           |  |

| A10-12 | 19-51           | 8                         | 1            | 16    | 8    | 12K-13K                | $A_{TRR1}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 4                      | 74.6% - 75.0%              | 1.48 - 2.86                           |  |

| A13-14 | 20-31           | 8                         | 1            | 8     | 16   | 11K-14K                | $A_{TRR2}$                           | Counter-based          | 16                    | ✓               | 1/9                 | 2                      | 94.3% - 98.6%              | 1.53 - 2.78                           |  |

| B0     | 18-22           | 4                         | 1            | 16    | 8    | 44K                    | $B_{TRR1}$                           | Sampling-based         | 1                     | Х               | 1/4                 | 2                      | 99.9%                      | 2.13                                  |  |

| B1-4   | 20-17           | 4                         | 1            | 16    | 8    | 159K-192K              | $B_{TRR1}$                           | Sampling-based         | 1                     | ×               | 1/4                 | 2                      | 23.3% - 51.2%              | 0.06 - 0.11                           |  |

| B5-6   | 16-48           | 4                         | 1            | 16    | 8    | 44K-50K                | $B_{TRR1}$                           | Sampling-based         | 1                     | ×               | 1/4                 | 2                      | 99.9%                      | 1.85 - 2.03                           |  |

| B7     | 19-06           | 8                         | 2            | 16    | 8    | 20K                    | $B_{TRR1}$                           | Sampling-based         | 1                     | X               | 1/4                 | 2                      | 99.9%                      | 31.14                                 |  |

| B8     | 18-03           | 4                         | 1            | 16    | 8    | 43K                    | $B_{TRR1}$                           | Sampling-based         | 1                     | X               | 1/4                 | 2                      | 99.9%                      | 2.57                                  |  |

| B9-12  | 19-48           | 8                         | 1            | 16    | 8    | 42K-65K                | $B_{TRR2}$                           | Sampling-based         | 1                     | X               | 1/9                 | 2                      | 36.3% - 38.9%              | 16.83 - 24.26                         |  |

| B13-14 | 20-08           | 4                         | 1            | 16    | 8    | 11K-14K                | $B_{TRR3}$                           | Sampling-based         | 1                     | ✓               | 1/2                 | 4                      | 99.9%                      | 16.20 - 18.12                         |  |

| C0-3   | 16-48           | 4                         | 1            | 16    | x8   | 137K-194K              | $C_{TRR1}$                           | Mix                    | Unknown               | ✓               | 1/17                | 2                      | 1.0% - 23.2%               | 0.05 - 0.15                           |  |

| C4-6   | 17-12           | 8                         | 1            | 16    | x8   | 130K-150K              | $C_{TRR1}$                           | Mix                    | Unknown               | ✓               | 1/17                | 2                      | 7.8% - 12.0%               | 0.06 - 0.08                           |  |

| C7-8   | 20-31           | 8                         | 1            | 8     | x16  | 40K-44K                | $C_{TRR1}$                           | Mix                    | Unknown               | ✓               | 1/17                | 2                      | 39.8% - 41.8%              | 9.66 - 14.56                          |  |

| C9-11  | 20-31           | 8                         | 1            | 8     | x16  | 42K-53K                | $C_{TRR2}$                           | Mix                    | Unknown               | ✓               | 1/9                 | 2                      | 99.7%                      | 9.30 - 32.04                          |  |

| C12-14 | 20-46           | 16                        | 1            | 8     | x16  | 6K-7K                  | $C_{TRR3}$                           | Mix                    | Unknown               | ✓               | 1/8                 | 2                      | 99.9%                      | 4.91 - 12.64                          |  |

### Outline

- 1. DRAM Operation Basics

- 2. RowHammer & Target Row Refresh

- 3. The U-TRR Methodology

- 4. Observations & New RowHammer Access Patterns

- 5. RowHammer Bit Flip Analysis

- 6. Takeaways and Conclusion

#### Conclusion

#### **Target Row Refresh (TRR):**

a set of obscure, undocumented, and proprietary RowHammer mitigation techniques

We cannot easily study the security properties of TRR

Is TRR fully secure? How can we validate its security guarantees?

**U-TRR**

A new methodology that leverages *data retention failures* to uncover the inner workings of TRR and study its security

All 45 modules we test are vulnerable

**99.9% of rows** in a DRAM bank experience at least one RowHammer bit flip

Up to **7** RowHammer **bit flips** in an 8-byte dataword, **making ECC ineffective**

TRR does not provide security against RowHammer

U-TRR can facilitate the development of **new RowHammer attacks** and **more secure RowHammer protection** mechanisms

#### U-TRR

**Uncovering in-DRAM RowHammer Protection Mechanisms:** A New Methodology, Custom RowHammer Patterns, and Implications

#### Hasan Hassan

Yahya Can Tugrul Jeremie S. Kim Victor van der Veen Kaveh Razavi Onur Mutlu

# TRRespass

#### RowHammer in 2020

Pietro Frigo, Emanuele Vannacci, Hasan Hassan, Victor van der Veen, Onur Mutlu, Cristiano Giuffrida, Herbert Bos, and Kaveh Razavi, "TRRespass: Exploiting the Many Sides of Target Row Refresh" Proceedings of the 41st IEEE Symposium on Security and Privacy (S&P), San Francisco, CA, USA, May 2020.

[Slides (pptx) (pdf)]

[Talk Video (17 minutes)]

Source Code

[Web Article]

Best paper award.

# TRRespass: Exploiting the Many Sides of Target Row Refresh

Pietro Frigo\*† Emanuele Vannacci\*† Hasan Hassan§ Victor van der Veen¶ Onur Mutlu§ Cristiano Giuffrida\* Herbert Bos\* Kaveh Razavi\*

\*Vrije Universiteit Amsterdam

§ETH Zürich

¶Oualcomm Technologies Inc.

#### TRRespass

- First work to show that TRR-protected DRAM chips are vulnerable to RowHammer in the field

- Mitigations advertised as secure are not secure

- Introduces the Many-sided RowHammer attack

- Idea: Hammer many rows to bypass TRR mitigations (e.g., by overflowing proprietary TRR tables that detect aggressor rows)

- (Partially) reverse-engineers the TRR and pTRR mitigation mechanisms implemented in DRAM chips and memory controllers

- Provides an automatic tool that can effectively create manysided RowHammer attacks in DDR4 and LPDDR4(X) chips

41

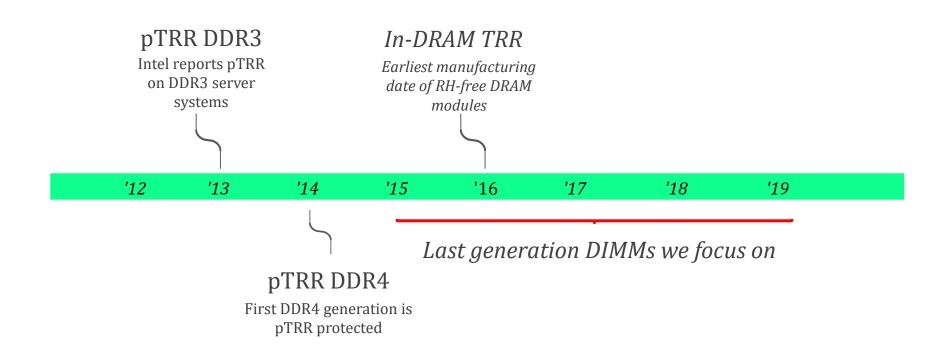

## Target Row Refresh (TRR)

- How does it work?

- 1. Track activation count of each DRAM row

- 2. Refresh neighbor rows if row activation count exceeds a threshold

- Many possible implementations in practice

- Security through obscurity

- In-DRAM TRR

- Embedded in the DRAM circuitry, i.e., not exposed to the memory controller

#### Timeline of TRR Implementations

#### Our Goals

Reverse engineer in-DRAM TRR to demystify how it works

- Bypass TRR protection

- A Novel hammering pattern: The Many-sided RowHammer

- Hammering up to 20 aggressor rows allows bypassing TRR

- Automatically test memory devices: TRRespass

- Automate hammering pattern generation

#### Infrastructures to Understand Such Issues

Kim+, "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," ISCA 2014.

#### SoftMC: Open Source DRAM Infrastructure

Hasan Hassan et al., "SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies," HPCA 2017.

- Flexible

- Easy to Use (C++ API)

- Open-source

github.com/CMU-SAFARI/SoftMC

46

#### SoftMC

https://github.com/CMU-SAFARI/SoftMC

# SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

```

Hasan Hassan Nandita Vijaykumar Samira Khan Saugata Ghose Kevin Chang Gennady Pekhimenko Donghyuk Lee^{6,3} Oguz Ergin Onur Mutlu Onur Mutlu

```

```

<sup>1</sup>ETH Zürich <sup>2</sup>TOBB University of Economics & Technology <sup>3</sup>Carnegie Mellon University <sup>4</sup>University of Virginia <sup>5</sup>Microsoft Research <sup>6</sup>NVIDIA Research

```

47

#### Components of In-DRAM TRR

#### Sampler

- Tracks aggressor rows activations

- Design options:

- Frequency based (record every N<sup>th</sup> row activation)

- Time based (record first N row activations)

- Random seed (record based on a coin flip)

- Regardless, the sampler has a limited size

#### Inhibitor

- Prevents bit flips by refreshing victim rows

- The latency of performing victim row refreshes is squeezed into slack time available in tRFC (i.e., the latency of regular Refresh command)

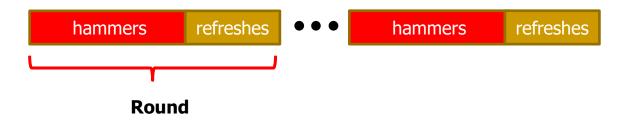

#### How big is the sampler?

- Pick N aggressor rows

- Perform a series of hammers (i.e., activations of aggressors)

- 8K activations

- After each series of hammers, issue R refreshes

- 10 Rounds

1. The TRR mitigation acts on a refresh command

- 2. The mitigation can sample more than one aggressor per refresh interval

- 3. The mitigation can refresh only a single victim within a refresh operation

4. Sweeping the number of refresh operations and aggressor rows while hammering reveals the sampler size

## Many-Sided Hammering

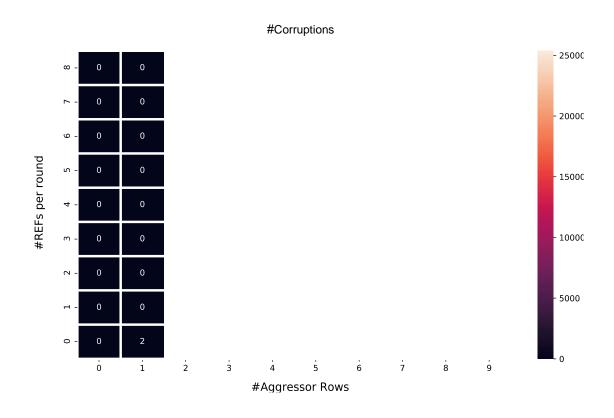

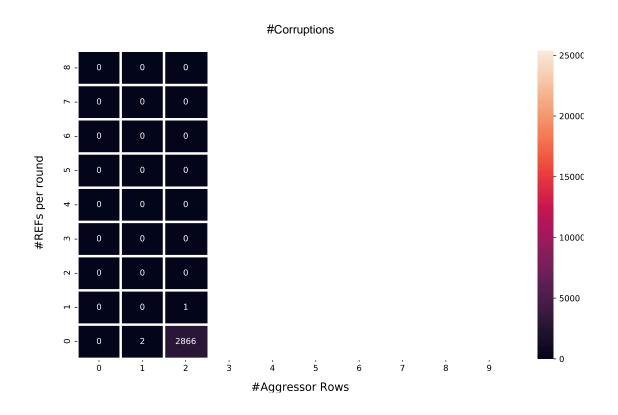

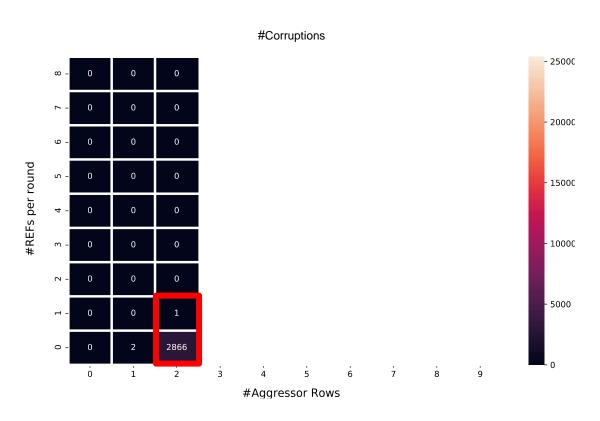

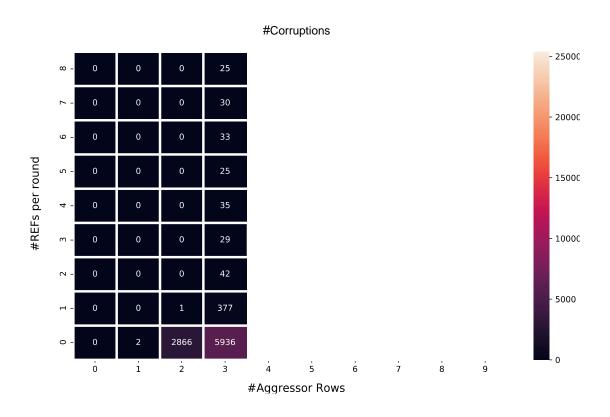

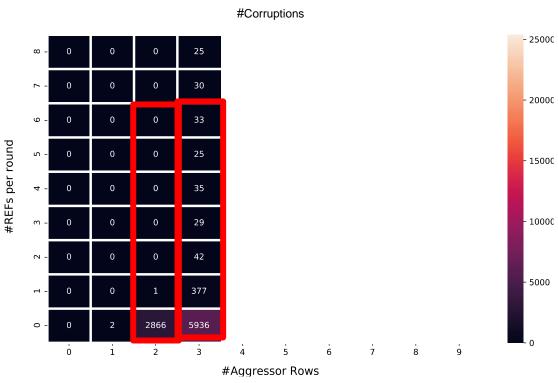

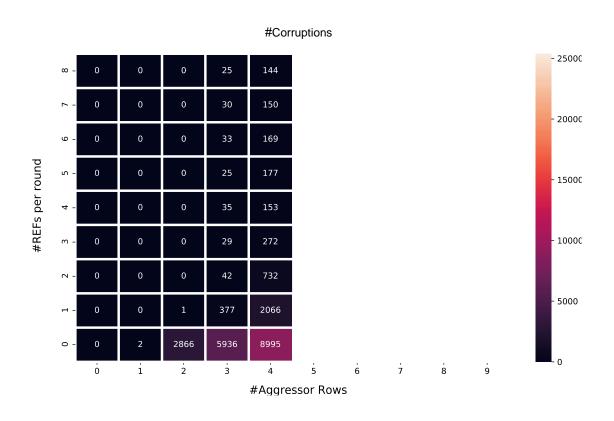

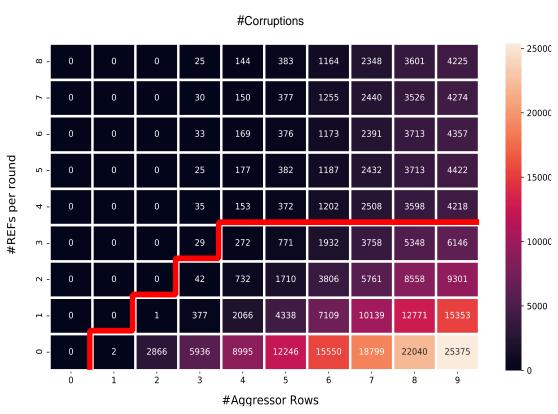

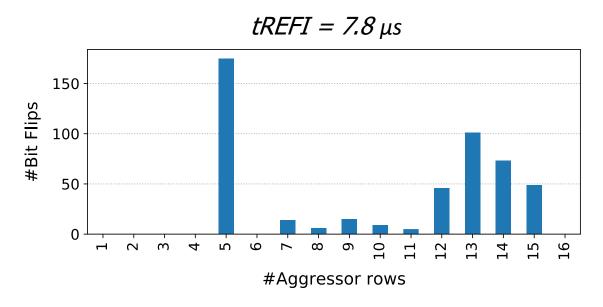

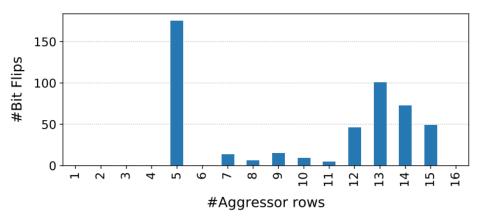

Fig. 9: Refreshes vs. Bit Flips. Module  $C_{12}$ : Number of bit flips detected when sending r refresh commands to the module. We report this for different number of aggressor rows (n). For example, when hammering 5 rows, followed by sending 2 refreshes, we find 1,710 bit flips. This figure shows that the number of bit flips stabilizes for  $r \geq 4$ , implying that the size of the sampler may be 4.

#### Some Observations

**Observation 1:** The TRR mitigation acts (i.e., carries out a targeted refresh) on **every** refresh command.

**Observation 2:** The mitigation can sample more than one aggressor per refresh interval.

**Observation 3:** The mitigation can refresh only a **single** victim within a refresh operation (i.e., time tRFC).

**Observation 4:** Sweeping the number of refresh operations and aggressor rows while hammering reveals the sampler size.

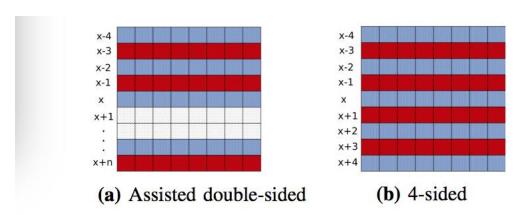

Fig. 12: Hammering patterns discovered by *TRRespass*. Aggressor rows are in red ( ) and victim rows are in blue ( ).

#### Hammering using the default refresh rate

## BitFlips vs. Number of Aggressor Rows

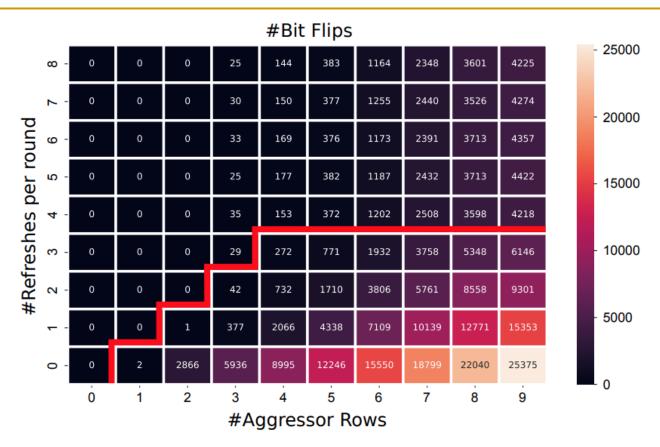

Fig. 10: Bit flips vs. number of aggressor rows. Module  $\mathcal{C}_{12}$ : Number of bit flips in bank 0 as we vary the number of aggressor rows. Using SoftMC, we refresh DRAM with standard tREFI and run the tests until each aggressor rows is hammered 500K times.

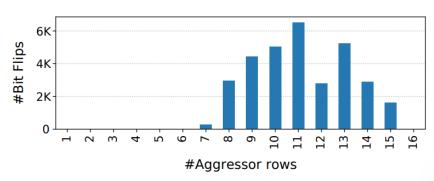

Fig. 11: Bit flips vs. number of aggressor rows. Module  $\mathcal{A}_{15}$ : Number of bit flips in bank 0 as we vary the number of aggressor rows. Using SoftMC, we refresh DRAM with standard tREFI and run the tests until each aggressor rows is hammered 500K times.

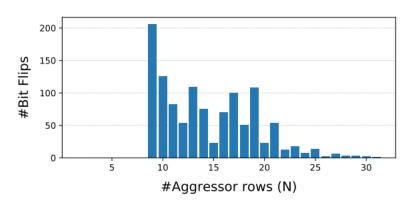

Fig. 13: Bit flips vs. number of aggressor rows. Module  $A_{10}$ : Number of bit flips triggered with *N-sided* RowHammer for varying number of *N* on Intel Core i7-7700K. Each aggressor row is one row away from the closest aggressor row (i.e., VAVAVA... configuration) and aggressor rows are hammered in a round-robin fashion.

#### TRRespass Key Results

- 13 out of 42 tested DDR4 DRAM modules are vulnerable

- From all 3 major manufacturers

- □ 3-, 9-, 10-, 14-, 19-sided attacks needed

- 5 out of 13 mobile phones tested vulnerable

- From 4 major manufacturers

- With LPDDR4(X) DRAM chips

- These results are scratching the surface

- TRRespass tool is not exhaustive

- There is a lot of room for uncovering more vulnerable chips and phones

# RowHammer is still an open problem

Security by obscurity is likely not a good solution

#### More on TRRespass

Pietro Frigo, Emanuele Vannacci, Hasan Hassan, Victor van der Veen, Onur Mutlu, Cristiano Giuffrida, Herbert Bos, and Kaveh Razavi, "TRRespass: Exploiting the Many Sides of Target Row Refresh" Proceedings of the 41st IEEE Symposium on Security and Privacy (S&P), San Francisco, CA, USA, May 2020.

[Slides (pptx) (pdf)]

[Talk Video (17 minutes)]

Source Code

Web Article

Best paper award.

# TRRespass: Exploiting the Many Sides of Target Row Refresh

Pietro Frigo\*† Emanuele Vannacci\*† Hasan Hassan§ Victor van der Veen¶ Onur Mutlu§ Cristiano Giuffrida\* Herbert Bos\* Kaveh Razavi\*

\*Vrije Universiteit Amsterdam

§ETH Zürich

¶Oualcomm Technologies Inc.

#### P&S SoftMC

Understanding and Improving Modern DRAM Performance, Reliability, and Security with Hands-On Experiments

Hasan Hassan

Prof. Onur Mutlu

ETH Zürich

Spring 2022

22 March 2022